### Characterization of a 16-Channel LArASIC for the Front-end Read-out Electronics System at DUNE Experiment

Eaglekumar G. Tarpara On behalf of the DUNE collaboration

Brookhaven National Laboratory, NY, USA

### Contents

- Introduction

- Deep Underground Neutrino Experiment (DUNE)

- Liquid Argon Time Projection Chamber (LArTPC) Cold Electronics (CE)

- Liquid Argon ASIC (LArASIC) P5B

- LArASIC Quality Control (QC)

- QC requirements, QC items, QC procedures

- Dual-DUT test board and its capabilities

- LArASIC QC tests and results

- Summary

- Future R&D

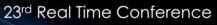

#### Long Baseline Neutrino Program: LBNF/DUNE

#### **DUNE Science Collaboration**

- ~1400 Collaborators

- ~200 Instituites

- ~30 Contries + CERN

Primary science goals

Neutrino/antineutrino oscillations – Search for the origin of matter

Supernova Neutrino Bursts – Learn about neutron stars and black holes

Proton decay - shed light on the unification of nature's forces

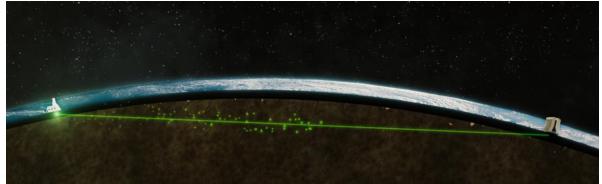

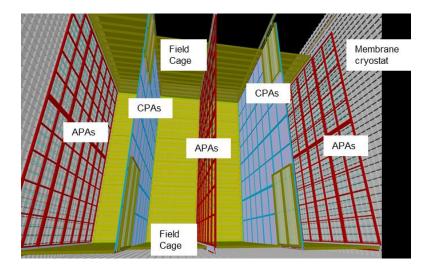

#### **Single-Phase LArTPC for the DUNE Far Detector Modules**

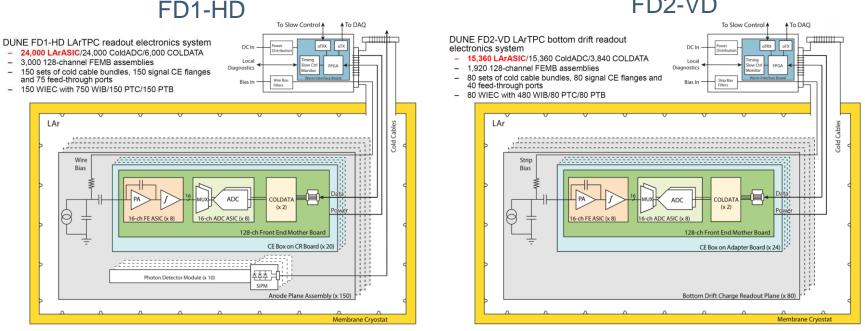

#### DUNE first 17 kt Far Detector LArTPC CE

- 150 APA units

- 384,000 channels

- 24,000 FE ASICs/24,000 ADC ASICs

- 6,000 COLDATA ASICs

- 3,000 Front End Mother Board assemblies

- Aim for 30 years of operation without replacement and maintenance

# LArTPC CE

#### FD2-VD

#### ProtoDUNE-II

- The plan is to install and operate the FD1-HD and FD2-VD production components in ProtoDUNE-II during 2022/2023. ٠

- This will be used to validate both the detector components and the processes put in place to construct and install them

- ProtoDUNE-II HD

- 4 APAs (2560 CH/APA)

- Two upper DUNE APAs CE will be installed at top

- Two lower DUNE APAs CE will be installed at bottom

- 20 Xilinx Zyng+ WIBs

- 4 WIECs

- 80 FEMBs (CE boxes) for ProtoDUNE-II HD

- 640 LArASIC + 640 ColdADC + 160 ColdDATA chips

- 48 FEMBs (CE boxes) for ProtoDUNE-II VD

- 384 LArASIC + 384 ColdADC + 96 ColdDATA chips

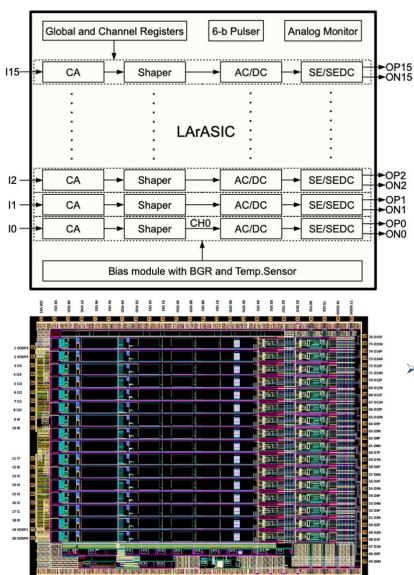

# LArASIC P5B

44 V050 43 V050 42 V55 41 V55 39 C5 39 C5 39 C5 39 C5 39 C5 31 V55 31 V55 31 V55 31 V55 31 V55 32 V55 32 V55 32 V55

| Technology                               | 100 mm CMOC                                               | 1 males C m   |                          |             |       |           |

|------------------------------------------|-----------------------------------------------------------|---------------|--------------------------|-------------|-------|-----------|

| Technology                               | 180 nm CMOS – 1-poly, 6-metal, MiM cap, sil blk resistors |               |                          |             |       |           |

| Supply Voltage                           | 1.8 V                                                     |               |                          |             |       |           |

| Temperature Range                        | 77 – 300 K (-19                                           | 6 – 27 °C) op | ptim                     | ized for 87 | 7k (- | 186 °C)   |

| Number of Channels                       | 16                                                        |               |                          |             |       |           |

| Max Single-Ended Output<br>Swing         | 1.4 V peak to peak (0.2 – 1.6 V)                          |               |                          |             |       |           |

| Gain Selection (mV/fC)                   | 4.7                                                       | 7.8           |                          | 14          |       | 25        |

| Full-Scale Input Charge (fC)             | 300                                                       | 180           |                          | 100         |       | 56        |

| Baseline selection                       | 200 mV (collection mode)                                  |               | 900 mV (induction mode)  |             |       |           |

| Charge Preamplifier Polarity             | Negative (collection mode)                                |               | Bipolar (induction mode) |             |       |           |

| Adaptive-Reset Current<br>Selection (nA) | 0.1                                                       | 0.5           |                          | 1           |       | 5         |

| Shaper Peaking Time<br>Selection (μs)    | 0.5                                                       | 1             |                          | 2           |       | 3         |

| Output Coupling                          | AC (100 µs HPF time-<br>constant)                         |               | DC                       |             |       |           |

| Output Selection                         | Shaper                                                    |               | SE                       | buffer      | SE    | DC buffer |

| Total Channel Settings                   | 1024                                                      |               |                          |             |       |           |

| Integrated Test Capacitor                | 200 fF                                                    |               |                          |             |       |           |

| Temperature Sensor                       | 0.8728 V @ 25°C + 2.868 mV/°C                             |               |                          |             |       |           |

| Integrated Pulse Generator               | 6-bit DAC based                                           |               |                          |             |       |           |

| Configuration Control                    | SPI interface with 144 register bits                      |               |                          |             |       |           |

#### Goal of P5B LArASIC

- Remove RQI subtraction to fix a few non-operational channels in LN2 (Success)

- Modify SEDC buffer for stable and low noise operation (Success)

- Modify Test Charge Injection Pulser DAC in terms of its linearity (Success)

- Retain improvements achieved in P4 (ledge effect elimination, bandgap cold startup) (Success)

- Apply Enhance ESD protection scheme to tolerate higher discharge (Success)

25 VSG 25 VSS 24 VDG 23 VDG 23 VSS

# LArASIC QC

- LArASIC is designed to operate in liquid Argon (87K)

- Appropriate design rules for operation in cryogenic liquids are used to ensure LArASIC will operate with minimal losses of channels throughout the expected lifetime of the DUNE experiment (~30 years)

- FEMBs in a cryostat (liquid Argon) is not accessible for repair or replacement

- We will be using around 1024, 24000 and 15360 LArASIC (P5B version) packaged chips for ProtoDUNE-II, DUNE FD1-HD and DUNE FD2-VD experiments, respectively.

- The systematic characterization and performance testing of the LArASIC chip at cryogenic temperature is vital for the quality and reliability of detectors at ProtoDUNE-II and DUNE experiments.

- The TPC electronics consortium plan involves having multiple sites using the same QC procedure.

- The plan assumes each chip passing the warm test will be tested at LN2 to assure the cold yield

# **LArASIC QC Items Recommendation**

| Items                                                             | Description                                                                                                                                                                                                                |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power consumption                                                 | Each LArASIC has 3 power rails (VDDP, VDDA, VDDO) of which voltage and current are recorded under 3 configurations (default, SE on, and SEDC on)                                                                           |

| Power cycle                                                       | Pulse response checking in each power cycle (3 cycles)                                                                                                                                                                     |

| SPI checkout test                                                 | Write and read to LArASIC register                                                                                                                                                                                         |

| Charge pulse direct to input                                      | To check that input is connected to preamplifier (rare case)                                                                                                                                                               |

| Channel pulse response checkout (pulsing from internal DAC)       | <ul> <li>To check that output pins are proper connected with packaged pin</li> <li>Baseline measurements (200mV/900mV)</li> <li>Pulse response with different peaking time</li> </ul>                                      |

| Monitoring                                                        | <ul> <li>Check response from each channel (through test pad)</li> <li>Baseline measurements (through commercial ADC)</li> <li>BGR voltage measurement</li> </ul>                                                           |

| BL restore test                                                   | Check the baseline after 200mV to 900mV baseline configuration and vice versa                                                                                                                                              |

| Noise measurements                                                | With different peaking time and buffer configuration                                                                                                                                                                       |

| Full chain linearity measurements (LArASIC+ColdADC)               | <ul> <li>Input from internal DAC</li> <li>Direct input from external pulse generator</li> <li>Input from test pin and through internal calibration capacitor</li> <li>Gain, linearity and pedestal measurements</li> </ul> |

| Cross-talk measurements                                           | Cross-talk between each channel using direct input from external pulser                                                                                                                                                    |

| DAC Linearity measurements                                        | DNL/INL of DAC with different gain settings                                                                                                                                                                                |

| Channel pulse response with different<br>leakage current settings | Baseline measurements and channel pulse response                                                                                                                                                                           |

| Pulser response with different gain settings                      | Baseline measurements and channel pulse response                                                                                                                                                                           |

| Pole-zero cancellation test                                       | Measure the P-Z of each channel by external pulser                                                                                                                                                                         |

| Internal Calibration capacitor measurements                       | All 1pF on-board caps are calibrated with LCR meter to measure the internal cap                                                                                                                                            |

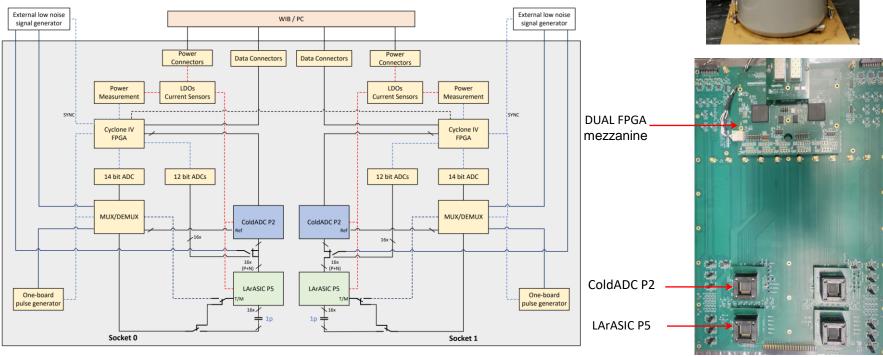

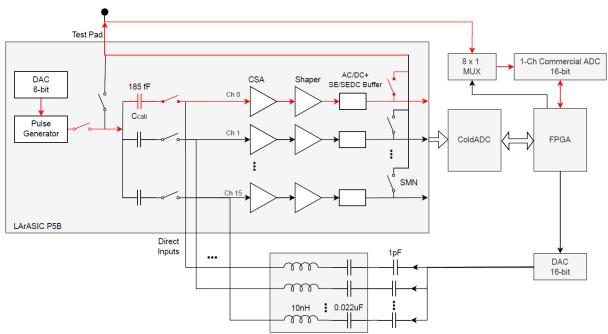

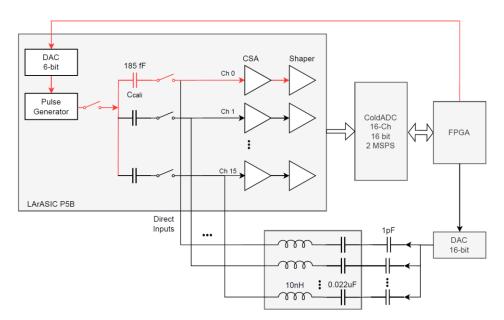

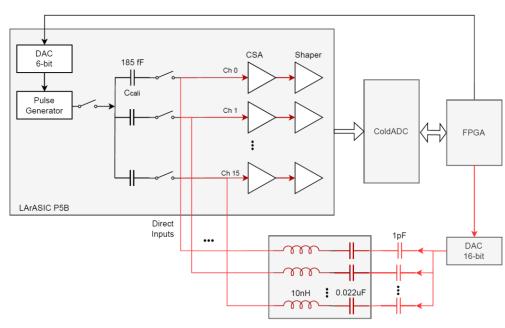

# **Dual-DUT Test Board**

- FM + Test Motherboard + 2 DUTs

- Can characterize LArASIC thoroughly

- The assembly will be submerged in LN2

- Interface:

- Data is readout through UDP interface of Dual FPGA mezzanine

- Can be readout by WIB as well (require FW update)

- Support LArASIC/ColdADC characterization

Cold Test Setup: CTS

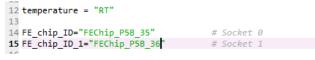

### **QC Procedures**

- Python script has been used to characterize the LArASIC

- Operators need to enter the Temp. and chips #

• Run 'QC\_DUAL\_DUT\_test.bat'

| :: socket 0                                                                                                                                                                                                |                                                                                    |                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------|

| python FE_adc_init.py                                                                                                                                                                                      | 0                                                                                  |                            |

| python FE_ADC_Power.py                                                                                                                                                                                     | 0                                                                                  |                            |

| python FE_parameter_test.py                                                                                                                                                                                | 0 0                                                                                |                            |

| <pre>python FE_baseline_restore_test.py</pre>                                                                                                                                                              | 0                                                                                  |                            |

| python adc_test_cfg.py<br>python FE_Channel_Response_all.py                                                                                                                                                | CMOS SDC_OFF DB_OFF Single-Ended 16 SHA<br>30us 14mVfC PLS_DIS 200mV BUF_OFF DC di |                            |

| python adc_test_cfg.py<br>python FE_Channel_Response_all.py                                                                                                                                                | CMOS SDC_OFF DB_OFF Diff 16 SHAinput 0<br>30us 14mVfC PLS_DIS 200mV BUF_OFF DC di  |                            |

| python adc_test_cfg.py<br>python FE_Channel_Response_EX_pulse_FPGA                                                                                                                                         | CMOS SDC_OFF DB_OFF Single-Ended 16 SHA<br>A_DAC.py 20us 14mVfC PLS_DIS 200mV BUF_ |                            |

| python FE_gain_measure_acq.py 05us 14mV4<br>python FE_gain_measure_acq.py 10us 14mV4<br>python FE_gain_measure_acq.py 20us 14mV4<br>python FE_gain_measure_acq.py 30us 14mV4                               | FC PLS_EN 200mV BUF_OFF DC Internal SDD<br>FC PLS_EN 200mV BUF_OFF DC Internal SDD | OFF False 0<br>OFF False 0 |

| python FE_gain_measure_acq.py 05us 14mV4<br>python FE_gain_measure_acq.py 10us 14mV4<br>python FE_gain_measure_acq.py 20us 14mV4<br>python FE_gain_measure_acq.py 30us 14mV4<br>python FE gain fit plot.py | FC PLS_EN 900mV BUF_OFF DC Internal SDD<br>FC PLS_EN 900mV BUF_OFF DC Internal SDD | OFF False 0<br>OFF False 0 |

| python FE_noise_acq_all.py                                                                                                                                                                                 | 20us 14mVfC PLS_DIS 200mV BUF_OFF DC di                                            | sable SDD_OFF 0            |

| python Dual_dut_QC_pdf.py                                                                                                                                                                                  | 0                                                                                  |                            |

- For a single chip run, it will execute around 8-9 tests and generate a single PDF.

- · Also saves all the test results into .csv file

- One chip test take around ~7 minutes (Dual chip take ~14 min)

#### Generated Summary of LArASIC QC (1<sup>st</sup> Page) LArASIC Test Summary Date & Time: 2022-01-14 12:33:49 Temperature: LN ColdADC Chip ID: ColdADC P2 60 Board ID: DUAL DUT FE Chip ID: FEChip P5B 42 Summary: Power Measurement Passed FE parameter measurement Passed BL Restore Test Passed Channel Response (Internal DAC) @SDD\_OFF Passed Channel Response (Internal DAC) @SDD\_ON Passed Channel Response (Ext Pulse) @ Passed FE gain plot (DAC pulsing) Passed

Database Interface

FE Noise

- All test data will be stored in BNL local database used in ProtoDUNE-I (Later we can store/transfer to the direct hardware database)

- Plan to develop a database template which can help user to monitor and archive the QC test results

Passed

#### **10** 08/05/2022

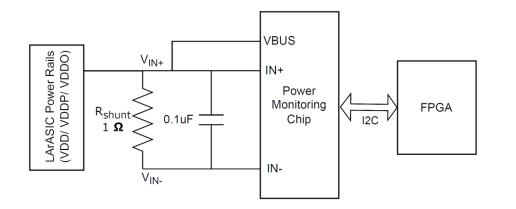

#### **Power Measurements**

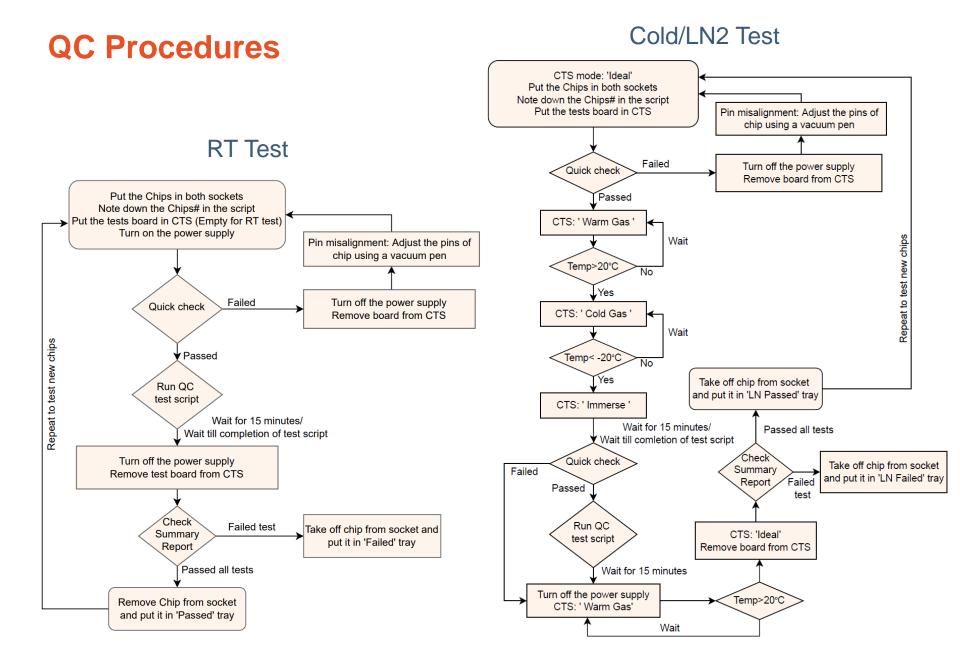

- Power monitoring chip is used to monitor voltage/current/power of LArASIC power rails

- · Measurement at different LArASIC buffer settings

- LArASIC power rails: VDDP, VDD, VDDO

- ColdADC power rails: VDDA2P5, VDDD2P5, VDDIO, VDDD1P2

- · Save results on .csv file

| LAIA            | SIC PSB #08 ( | WKI          |

|-----------------|---------------|--------------|

| SE=OFF SEDC=OFF | 900 mV (BL)   |              |

| Power Rail      | Voltages (V)  | Current (mA) |

| VDDP            | 1.86          | 31.11        |

| VDD             | 1.86          | 18.63        |

| VDDO            | 1.88          | 0            |

| Power (mW/Ch)   | 5.8           |              |

|                 |               |              |

| SE=ON SEDC=OFF  | 900 mV (BL)   |              |

| Power Rail      | Voltages (V)  | Current (mA) |

| VDDP            | 1.86          | 30.85        |

| VDD             | 1.86          | 43.2         |

| VDDO            | 1.87          | 9.4          |

| Power (mW/Ch)   | 9.73          |              |

|                 |               |              |

| SE=OFF SEDC=ON  | 900 mV (BL)   |              |

| Power Rail      | Voltages (V)  | Current (mA) |

| VDDP            | 1.86          | 30.75        |

| VDD             | 1.86          | 49.71        |

| VDDO            | 1.87          | 18.65        |

| Power (mW/Ch)   | 11.56         |              |

|                 |               |              |

| SE=OFF SEDC=OFF | 200 mV (BL)   |              |

| Power Rail      | Voltages (V)  | Current (mA) |

| VDDP            | 1.86          | 31.09        |

| VDD             | 1.86          | 18.63        |

| VDDO            | 1.88          | 0            |

| Power (mW/Ch)   | 5.79          |              |

| . ,             |               |              |

| SE=ON SEDC=OFF  | 200 mV (BL)   |              |

| Power Rail      | Voltages (V)  | Current (mA) |

| VDDP            | 1.86          | 30.84        |

| VDD             | 1.86          | 43.18        |

| VDDO            | 1.87          | 9.39         |

| Power (mW/Ch)   | 9.73          |              |

| . ,             |               |              |

| SE=OFF SEDC=ON  | 200 mV (BL)   |              |

| Power Rail      | Voltages (V)  | Current (mA) |

| VDDP            | 1.86          | 30.75        |

| VDD             | 1.86          | 49.69        |

| VDDO            | 1.87          | 18.64        |

| Power (mW/Ch)   | 11.56         |              |

| . ,             |               |              |

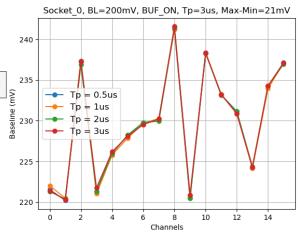

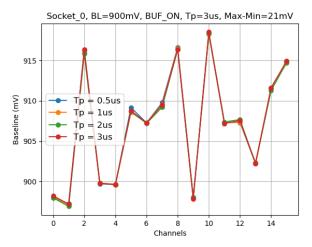

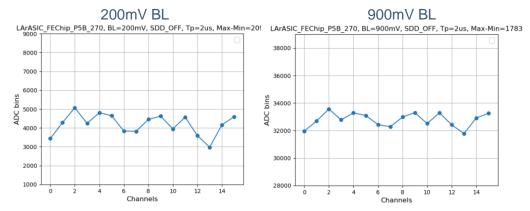

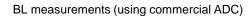

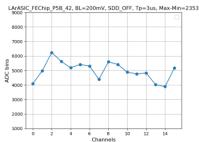

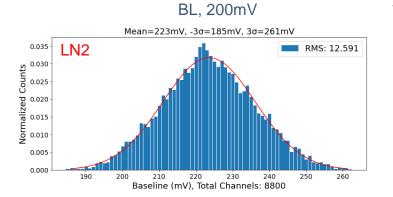

### **LArASIC Baseline Measurements**

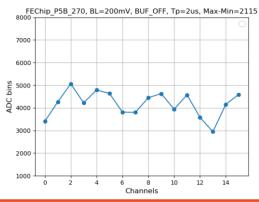

#### 200 mV BL @LN2

- · Commercial ADC: 14 bit, 4.5 MSPS is used

- Baseline measurements from LArASIC monitoring pin and through commercial ADC for all 16 channels (to bypass ColdADC)

- Band gap reference voltage (VBGR) and temperature sensor voltage is also measured

- FE settings:

- Tp = 0.5/1/2/3us , Pulse = Disable, Gain = 14 mV/fC , RQI = 500 pA, BL = 200 mV / 900mV, Buffer = OFF, SEDC = OFF

- Baseline measurement results are consistent with the previous measurement done by multimeter on the LArASIC single chip test board

#### 900 mV BL @LN2

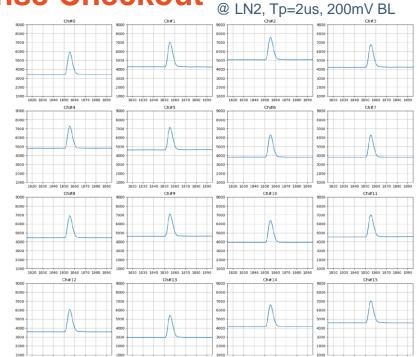

### **LArASIC Channel Pulse Response Checkout**

- Used FE internal DAC pulse for channel pulse response checkout

- · Plots of pulse responses for all 16 channels

- Plots of baseline dispersion for all 16 channels (FE Input disable)

- Different configuration settings are used:

- Baseline: 200 mV/900mV

- SE Buffer condition: BUF\_ON/BUF\_OFF

- Peak time: 0.5/1/2/3 us

#### Baseline dispersion (FE LArASIC P5B + ColdADC P2)

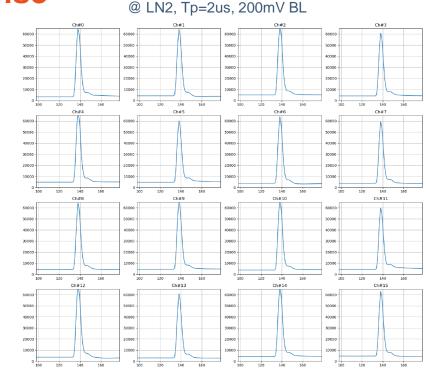

#### LArASIC Channel Pulse Response (External Pulser)

- Used External DAC pulse for channel pulse response checkout

- Useful to check the proper wire connections between the packaged pin

and die

- Plots of pulse responses for all 16 channels

- Plots of baseline dispersion for all 16 channels (FE Input disable)

- Different configuration settings are used:

- Baseline: 200 mV

- SE Buffer condition: BUF\_ON/BUF\_OFF

- Peak time: 2 us

Baseline dispersion (FE LArASIC P5B + ColdADC P2)

200mV BL

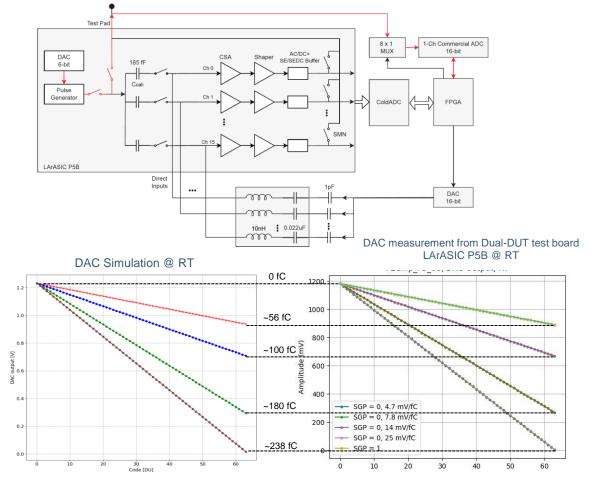

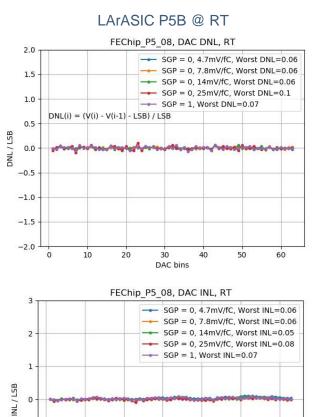

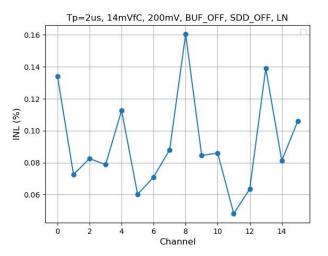

## **DAC Linearity Measurement**

- The DAC performance can be characterized on the Dual-DUT test board

- Commercial ADC, 14 bit is used to digitize DAC output

- Plots of DAC amplitude with different gain settings

- Gain: 4.7/7.8/14/25 mV/fC and SGP=1

- DAC has acceptable measured DNL of < 0.1 LSB and INL of < 0.08 LSB</li>

INL(i) = DNL(0) + DNL(1) + ... + DNL(i-1)

20

30

DAC bins

10

$^{-1}$

-2 -

-3 ++ 0

40

50

60

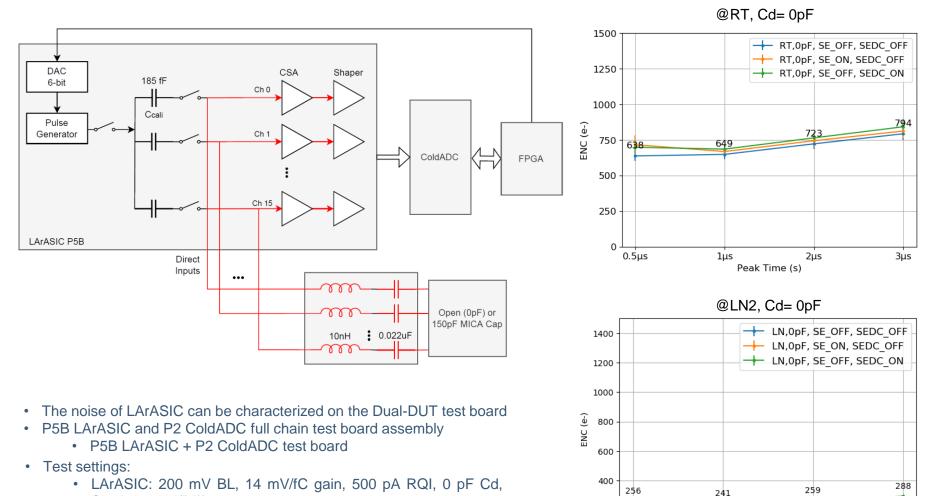

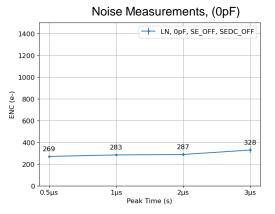

# **LArASIC Noise Measurements**

200

0 0.5μs

- Single-ended/DiffColdADC: SDC off, DB off, Single-ended/Diff

- Note: These are the preliminary noise results as QC setup and test board are not capable of measuring precise noise

2µs

3µs

1µs

Peak Time (s)

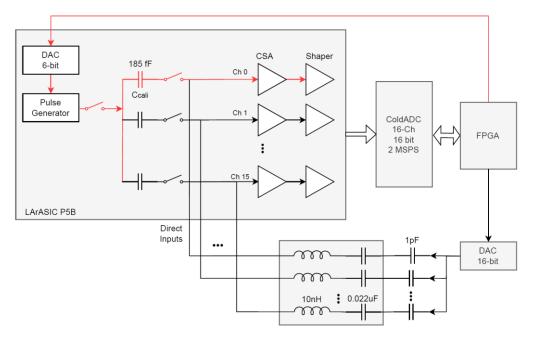

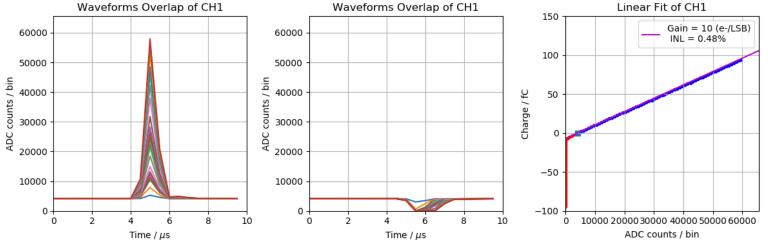

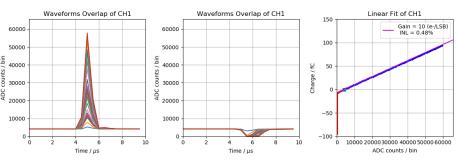

### **LArASIC Linearity Measurement (1)**

#### Using Internal pulser

- Full chain linearity is measured which includes the nonlinearities of

- Internal DAC + LArASIC P5B+ColdADC P2

- Settings:

- FE : BL=200mV, Gain =14mV/fC, Tp=2us,

- FE Buffer: SE=OFF, SEDC= OFF

- ColdADC: CMOS Ref, SDC\_OFF, DB\_OFF, Single-Ended

- Linearity measurements for the different combinations of BL (200mV/900mV) and peaking time (0.5us/1us/2us/3us)

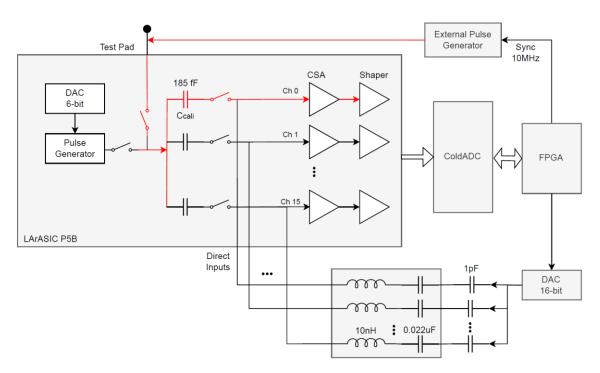

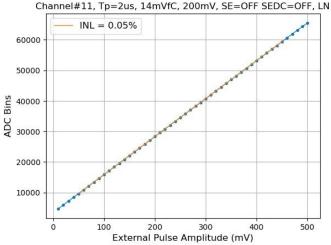

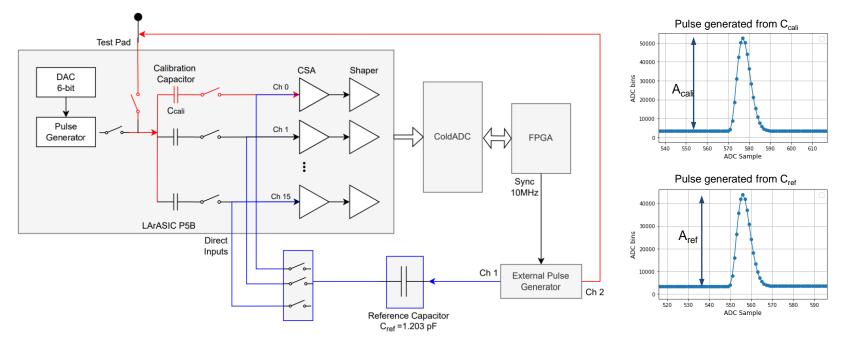

### **LArASIC Linearity Measurement (2)**

#### Using external pulser (Through test pin and internal calibration cap)

- For the precise linearity measurements, we used the external pulse generator and also implemented phased delay logic for the precise amplitude peak detection

- One by one channel was enabled to avoid cross-talk between individual channels

- Synchronized external pulse generator using FPGA 10 MHz clock

- Pulse setting: Freq: 1kHz, Amplitude = 10mV-500mV, Pulse width=50us, Edge= 5ns, Phase=variable (Fixed at maximum amplitude after calibration)

- Full chain linearity: LArASIC P5B + ColdADC P2

- FE : BL=200mV, Gain =14mV/fC, Tp=2us,

- ColdADC: CMOS Ref, SDC\_OFF, DB\_OFF, Single-Ended

- Internal DAC + LArASIC P5B+ColdADC P2

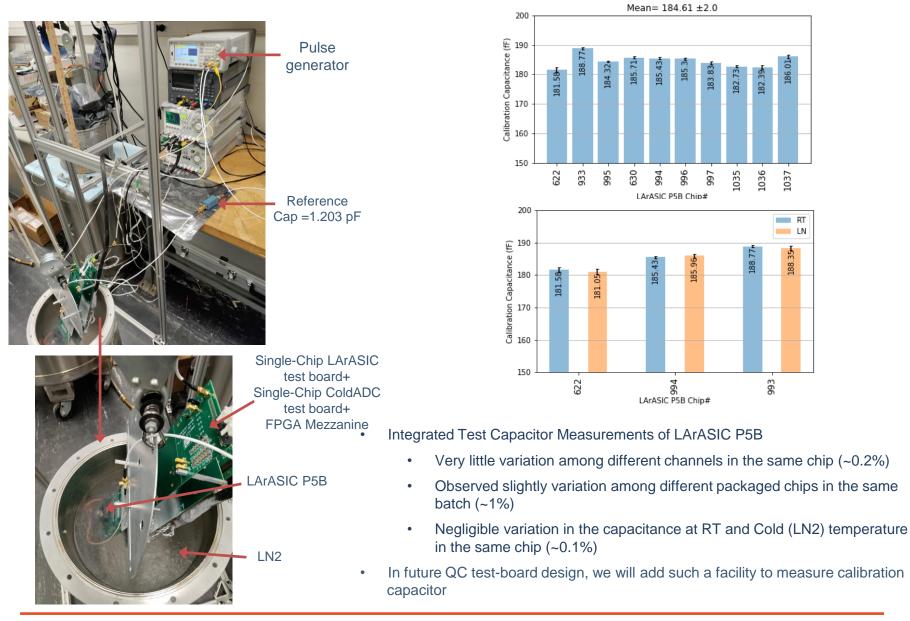

### **Calibration Capacitor Measurements**

- The current Dual-DUT board doesn't have the capability to measure the calibration capacitor

- Single test chip test boards have been used to measure the calibration cap

- C<sub>ref</sub> =1.203 pF is calibrated by standard 1.0pF and LCR meter

- C<sub>ref</sub> is always put in room temp.

- Since input pulse amplitude is constant,

- $C_{cali}$ :  $C_{ref} = A_{cali}$ :  $A_{ref}$

### **Calibration Capacitor Measurements**

# **QC Results**

- 200mV BL

--- 900mV BL

11 -

Ε

Power

SE=OFF, SEDC=OFF

9.580

SE=ON, SEDC=OFF

Buffer Status

Base

FEChip P5B 42, BL=200mV, BUF ON, Tp= lus, Max-Min=15mV

6 8 Channels 10 12 14

#### BL measurements (using ColdADC)

#### Channel Responses (BL=200mV, Tp=3us) Ch#0 Ch#3 Ch#4 Ch#5 Ch#6 Ch#7 1290 1300 1310 1320 1330 1310 1320 1330 1310 1320 1330 134 Ch#8 Ch#9 Ch#10 Ch#11 3000 -Ch#12 Ch#13 Ch#14 Ch#15 3000 · 1290 1300 1310 1320 1330 1340 1350

11.390

SE=OFF, SEDC=ON

E 236

ò

The acquired results satisfy all the required DUNE specifications for LArASIC quality control.

#### Gain, Linearity Measurements

# LArASIC P5B: Yield

#### **RT test setup**

- We have finished the testing of all LArASIC P5B chips at RT

- Cold screening of LArASIC P5B is going on

- Two CTS are being used for cold screening

#### Cold test setup

| LArASIC<br>Chips | Temp.    | Tested Chips# | Good #<br>(All channels<br>are normal) | Yield    |

|------------------|----------|---------------|----------------------------------------|----------|

| P5B              | RT       | 1786          | 1767                                   | ~99.0 %  |

| P5B              | Cold/LN2 | 617           | 613                                    | ~99.35 % |

- > At RT: 19 chips have failed at RT

- > At LN2: Four chips have failed at LN2 which works fine at RT

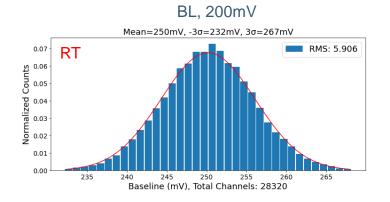

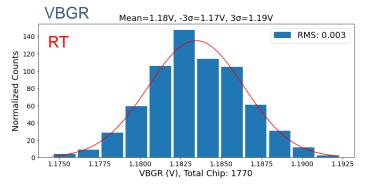

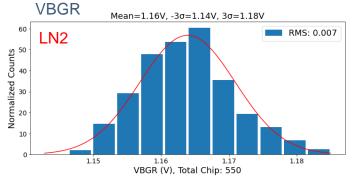

# **Preliminary Data Analysis**

- Number of channels

- @RT: 28320

- @LN2: 8800

| LArASIC Parameter       | Mean (RT/LN2)   | SD (RT/LN2)   |

|-------------------------|-----------------|---------------|

| BL, 200mV (mV)          | 250 / 223       | 5.9 / 12.6    |

| BL, 900mV (mV)          | 933 / 903       | 4.04 / 8.65   |

| Power, (mW/Ch)          | 6.1 / 5.37      | 0.13 / 0.19   |

| BGR voltage(V)          | 1.18 / 1.16     | 0.003 / 0.007 |

| Noise, Tp=0.5us (ENC)   | 622.29 / 281.94 | 34.9 / 41.21  |

| Noise, Tp=1us (ENC)     | 686.50 / 280.58 | 42.3 / 32.68  |

| Noise, Tp=2us (ENC)     | 711.67 / 279.61 | 48.9 / 35.82  |

| Noise, Tp=3us (ENC)     | 766.51 / 319.59 | 56.16 / 45.81 |

| Linearity, Tp=1us (INL) | 0.29 / 0.51     | 0.15 / 0.4    |

# Summary

- In QC setups for LArASIC characterization for ProtoDUNE-II, a Dual-DUT board has been used for the parallel testing of two chips in a single thermal cycle.

- This successful attempt of systematic testing of LArASIC characterization is intended to emphasize the preliminary technical steps for a successful and well-structured procedure for future large-batch QA/QC production testing of LArASIC chips for cryogenic operation in DUNE.

- Finished the QC testing of all LArASIC P5B chips at RT

- #1767 chips have passed the RT screening test, and achieved yield is ~99%

- #19 chips (~1%) chips have failed at RT

- #6 chips are completely failed, #13 chips have a unique failure issue

- No abnormal leakage current for any QC failed channels, No ESD damaged channel so far

- The Cold screening is LArASIC P5B is going on

- #613 chips have passed the cold screening test, and achieved yield is ~99.3%

- #4 chips (~0.65%) have abnormal pulse responses and baseline at 200mV BL settings

- No complete dead channels at Cold/LN2

### **Future R&D**

- As large batches of cold chips in the future need more cold screening and to reduce thermal cycle testing time, a DUNE ASIC test (DAT) board hosting multiple chips (#8 chips) is under design and the cryogenic procedures for QC of the multichip test are being evaluated.

- Can perform QC testing for 8x LArASIC, 8x ColdADC and 2x COLDATA at both RT and LN2 with MSU's new RTS

- Aim for DUNE FD1 & FD2 ASIC QC carried out in several test sites

- In addition, robotic designs for automated LArASIC/cold chip tests are also being considered to further reduce human interference with the QC procedure.

# **Thank You**

# **Back up slides**

# **Summary of Failed Chips**

#### **RT** Failed Chips

| Chip#  | Comments                                                                                   |

|--------|--------------------------------------------------------------------------------------------|

| 269    | Ch#15, Control register of Ch#15 can't configure correctly, produces only default results  |

| 198    | Ch#06, BL~0V for DC coupling, BL is normal for AC coupling, no pulse response              |

| 1366   | All Ch, 200 mV BL settings: Pulse is bad, BL is almost 0, ~50mV                            |

| 1685   | Ch#01, Dead channel with Tp =2us and Tp =3us peaking time                                  |

| 788    | Ch#05, Dead channel with Tp =3us peaking time                                              |

| 1027   | Ch#07, Dead channel with Tp =0.5us and Tp =1us peaking time                                |

| 929    | Ch#12, No pulse response, 200mV is ok, 900mV BL is abnormal                                |

| 1611   | All Ch, BL is ok, No pulse response for any settings                                       |

| 967    | Ch#02, Complete dead for all settings, leakage current is ok                               |

| 1677   | Ch#12, pulsing from the external source failed. Pin connection with die is completely open |

| 601    | Ch#0, BL is abnormal when SE buffer=OFF                                                    |

| 1518   | VDDP Bus consumes less current for any buffer settings, ~3.2mA                             |

| 1387   | Ch#09. BL and pulse response are abnormal                                                  |

| Others | Complete fail at RT, couldn't characterize it                                              |

#### Cold/LN2 Failed Chips

| Chip# | Comments                                                              |

|-------|-----------------------------------------------------------------------|

| 18    | 13 channels has abnormal BL and pulse responses at 200mV BL settings  |

| 800   | All channels has abnormal BL and pulse responses at 200mV BL settings |

| 824   | Ch#12 has abnormal BL and pulse responses at 200mV BL settings        |

| 815   | BL is slightly higher than expected value at 200mV BL settings        |