# CAEN DEScoverv Electronic Instrumentation

#### Future perspective of Digital DAO

Yuri Venturini (y.venturini@caen.it) IEEE Real Time conference – Aug 2nd-6th, 2022

**Real Time readout:**

>Continuous downstream A/D conversion  $\rightarrow$  Hardware: flash ADC, ASIC-based

>High throughput data transfer  $\rightarrow$  Which communication protocols?

>Buffering and data selection  $\rightarrow$  Which online analysis?

>Event building and DAQ  $\rightarrow$  Integration with which software tools?

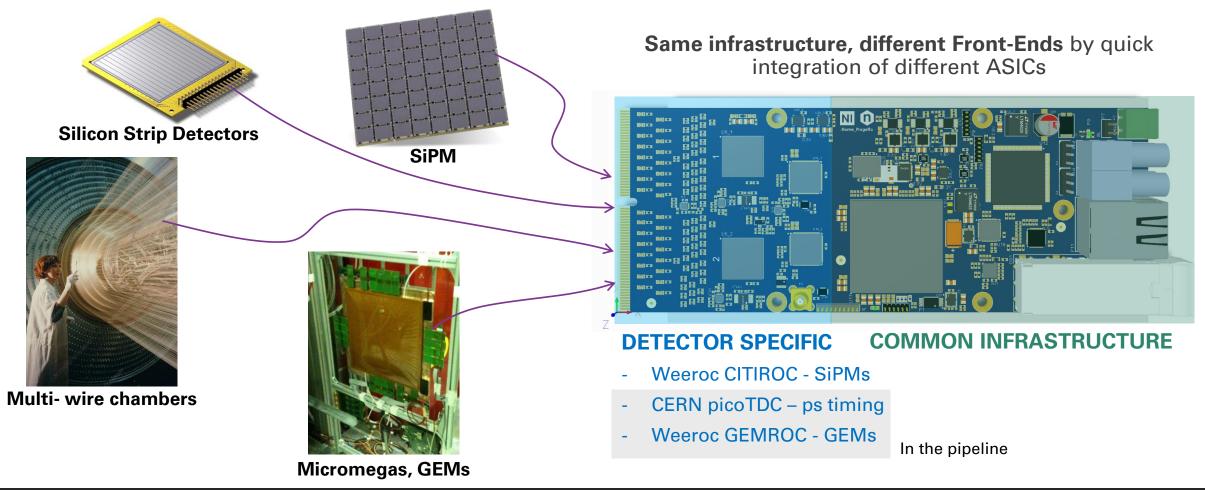

# New hardware to be flexible

CAEN **always drives to develop** new hardware and to improve its products with new firmware and software tools.

- more channels for denser systems

- faster communication links → high sustainable rate for downstream flow

- from MB to GB on-board memory → storage, middleware running onboard, complex online analysis

- improved FPGA with embedded ARM and OpenFPGA → customizable data processing and selection

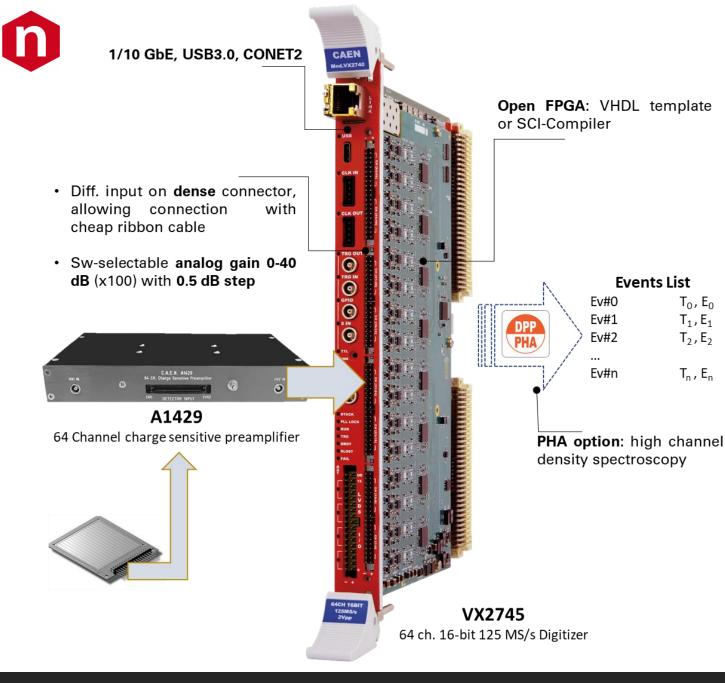

### 2740/2745 Digitizer

#### 64 channel, 125 MS/s, 16 - bit waveform digitizer

- Good fit for neutrino and dark matter experiments

- Selected by *DarkSide* and *Numen* experiments (SiC, Si-strips, GEMs, Scintillators)

- **Dynamics**: V2740  $\rightarrow$  2 Vpp fixed , V2745  $\rightarrow$  40mV  $\div$  4Vpp

- Multiple readout interfaces

- Open FPGA to provide flexibility in the pulse processing algorithm

- DPP functionalities: PHA, QDC, PSD, CFD, Zero Suppression

- Embedded Linux ARM

Events List

$T_0, E_0$

T<sub>1</sub>, E<sub>1</sub>

$T_2, E_2$

T<sub>n</sub> , E<sub>n</sub>

Ev#0

Ev#1

Ev#2

Ev#n

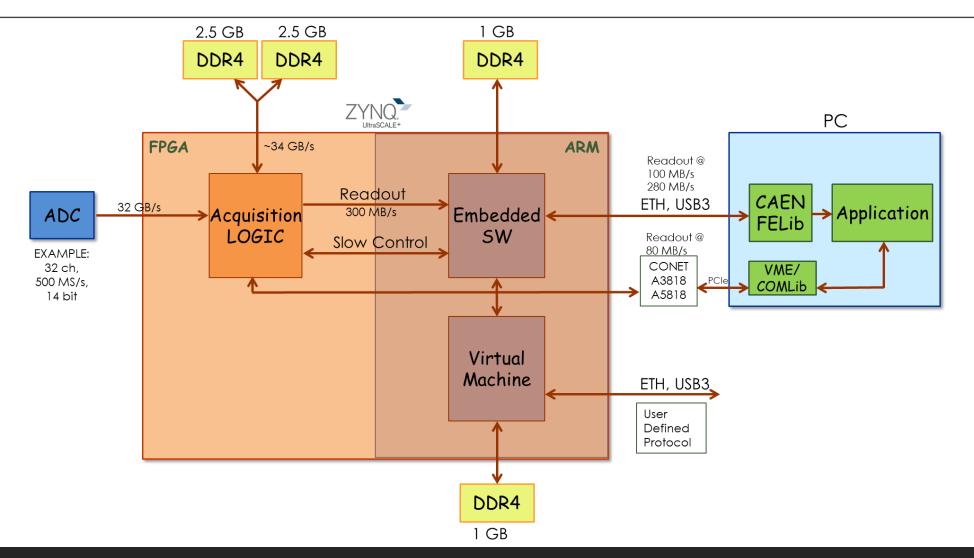

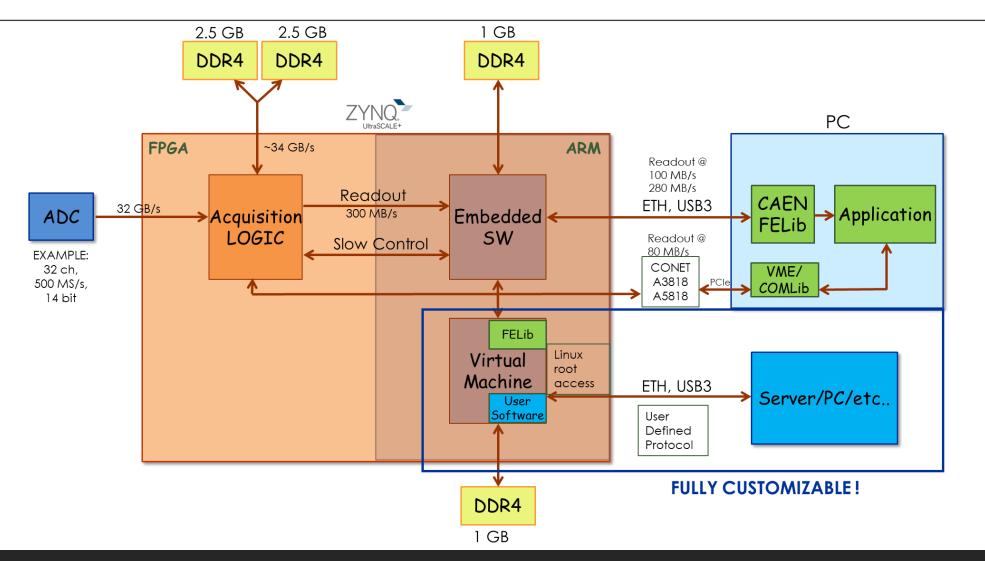

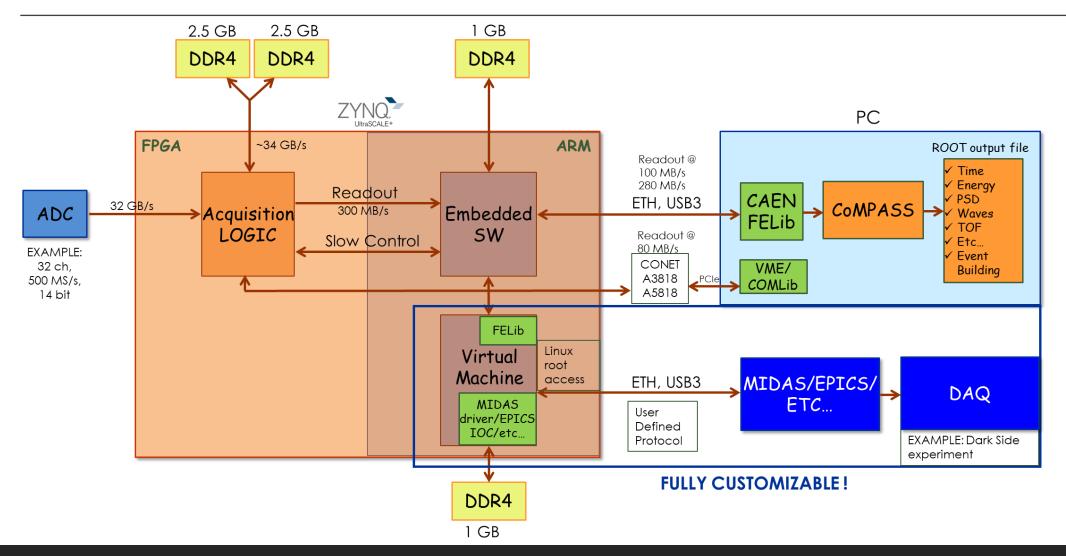

# The Digitizer architecture

## Focus on the embedded Virtual Machine

n

# Examples of Applications

n

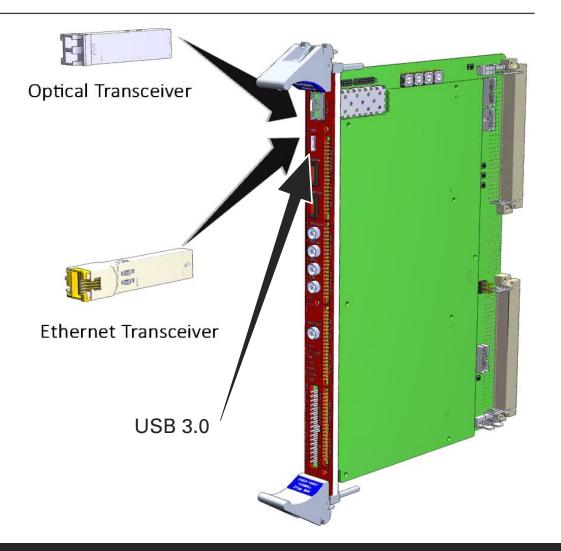

### Readout interfaces

n

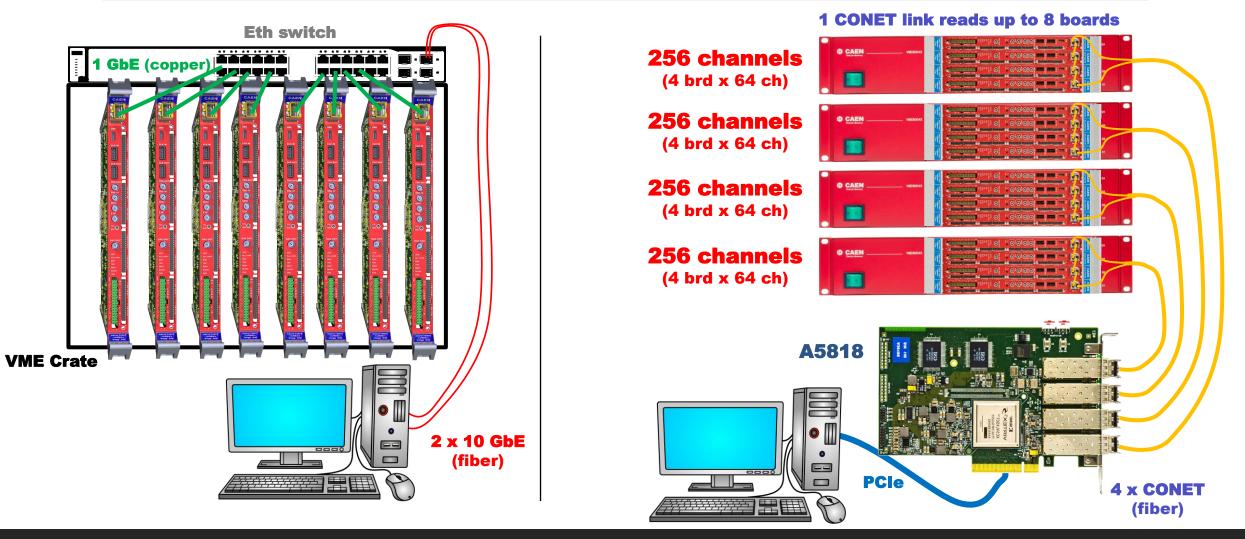

- 10 Gb Ethernet: Bandwidth = ~280 MB/s

- 1 Gb Ethernet: Bandwidth = ~100 MB/s

- USB 3.0: Bandwidth = ~280 MB/s

- USB 2.0: Bandwidth = ~30 MB/s

- PCle: via optical links, daisy chainable.

Aggregate Bandwidth = ~320 MB/s

- VME: legacy from the past... being dismissed

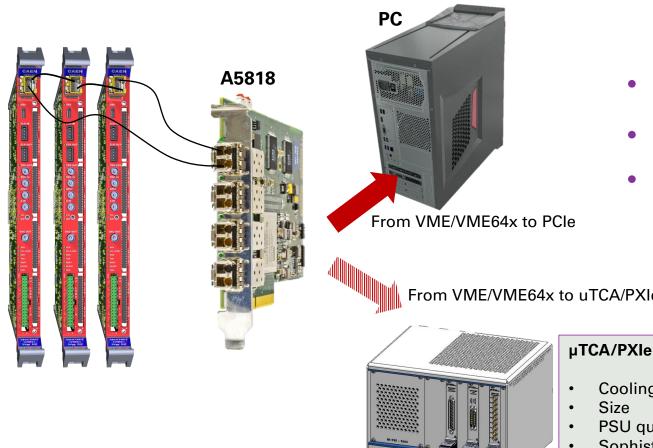

#### n **CONET2/PCIe readout**

- **Backplane free** policy: VME is kept for power only

- Arrangement in Desktop form factor easily

- A5818 into PCIe slot, but possibility of expansion to uTCA/PXIe

From VME/VME64x to uTCA/PXIe

µTCA/PXIe form factor for A5818.

- Cooling

- **PSU** quality

- Sophisticated remote monitoring and control

#### Multiboard Readout – Ethernet vs. CONET2

REPRODUCTION, TRANSFER, DISTRIBUTION OF PART OR ALL OF THE CONTENTS IN THIS DOCUMENT IN ANY FORM WITHOUT PRIOR WRITTEN PERMISSION OF CAEN S.P.A. IS PROHIBITED.

n

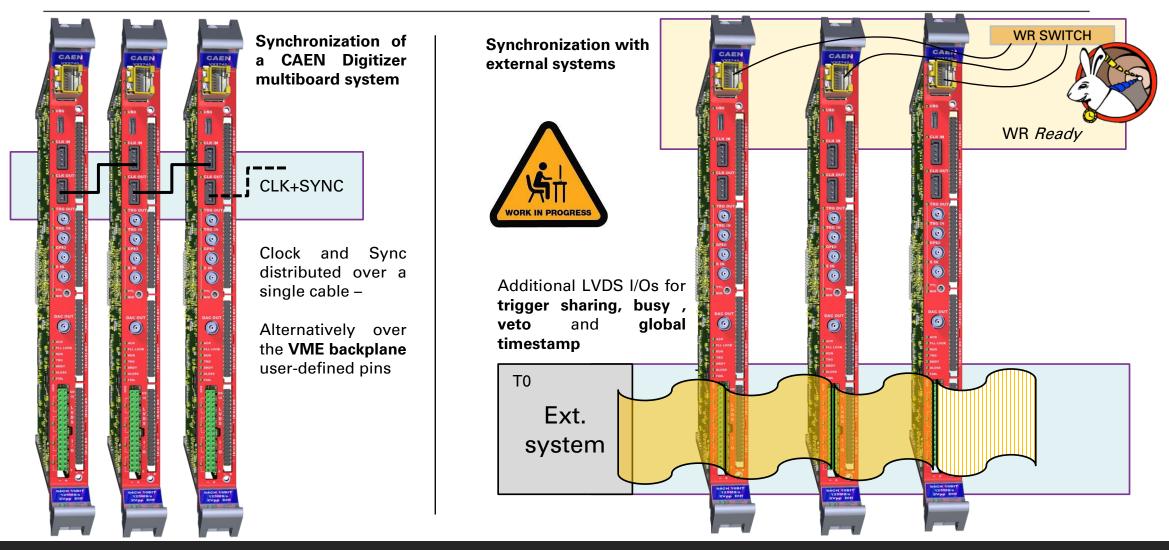

# Digitizers Synchronization

n

٠

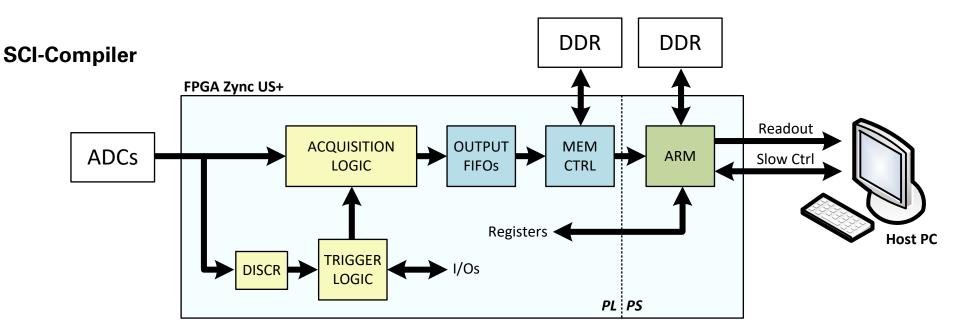

- User can access the **yellow boxes** of the PL to customize Acquisition Logic, Discrimination and Trigger Logic to build **his own Digital Pulse Processing**

- FPGA programming:

- Firmware Development Kit (FDK), made of a firmware template and VHDL examples released upon request to skilled users

### Open FPGA : alternative for transitional R&D

REPRODUCTION, TRANSFER, DISTRIBUTION OF PART OR ALL OF THE CONTENTS IN THIS DOCUMENT IN ANY FORM WITHOUT PRIOR WRITTEN PERMISSION OF CAEN S.P.A. IS PROHIBITED.

n

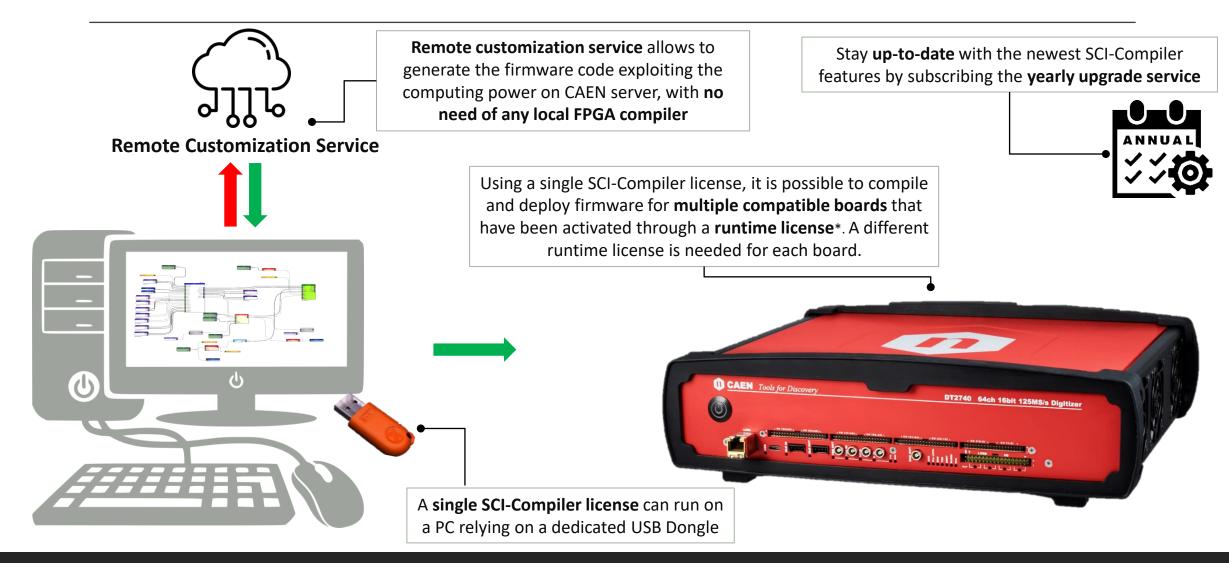

### SCI-Compiler: 100+ virtual blocks for physics

LOGIC GATE

TRAPEZOIDAL

FILTER

I/O INTERFACE

Control Digital and Analog Input/Output of the hardware devices

functions, Gate and Delay, counters, timers, scaler, frequency meters, array of bit manipulation

Trapezoidal filter allows to

achieve the optimum resolution on HpGE and PMT detectors

#### $\bigcirc$

IMAGING

Online image processing capabilities.

#### TDC AND TIMESTAMPING

Timestamp events with 0.5 ns resolution and calculate ToT. Digital CFD increase 10x the timing resolution on analog signals

Pulse Shape Discrimination algorithm to allows for particle identification.

**PSD**

#### OSCILLOSCOPE

Probe signals of each acquiring channel, even in the middle of the processing chain.

#### **ONLINE SPECTRUM**

Energy/Time Spectrum can be calculated onboard.

ANALOG SHAPER

High pass and Low pass realtime filter can be combined to emulate a traditional analog shaping chain.

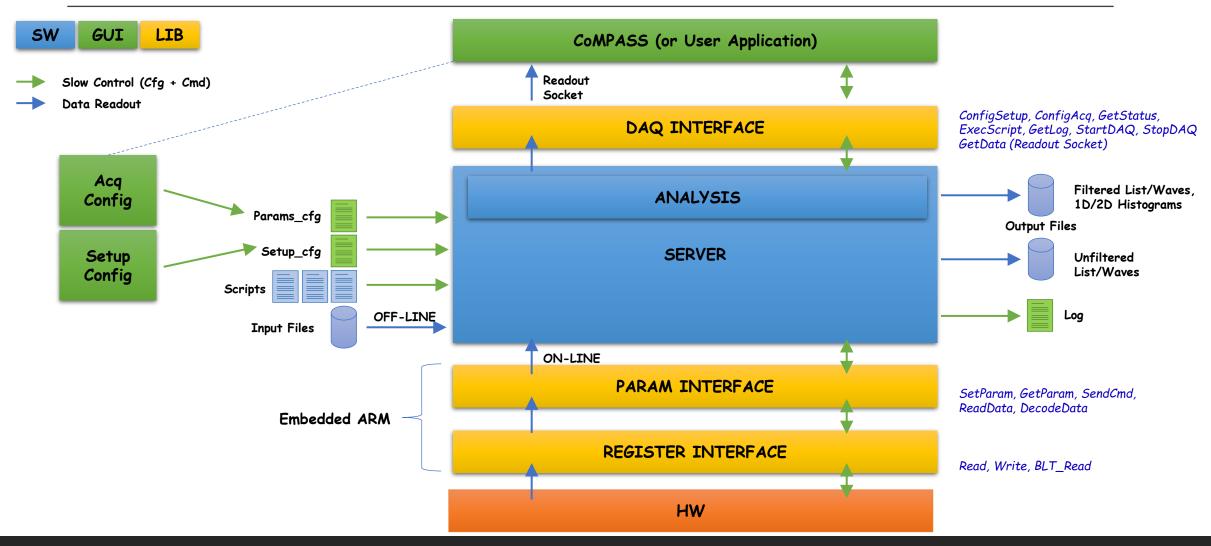

>High throughput data transfer  $\rightarrow$  Which communication protocols?

Several options, we can be standard (GbE, WR ready) or proprietary (CONET, TDLink) – and we can interface with other crate-based protocols like uTCA/PXIe

> Buffering and data selection  $\rightarrow$  Which online analysis?

Open FPGA and ARM gives much flexibility to run custom analysis onboard

>Event building and DAQ  $\rightarrow$  Integration with which software tools?

Both new Digitizers and FERS Concentrator Board are ready to handle non-CAEN framework and interface with custom DAQ software

# Thank you for your attention

Any question/curiosity?

### Backup slides

# In-built sparse event readout

n

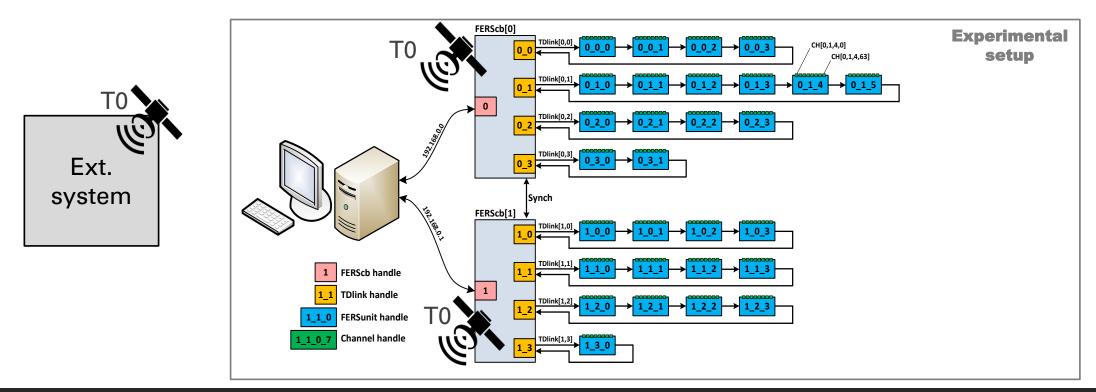

# A5202: readout modes

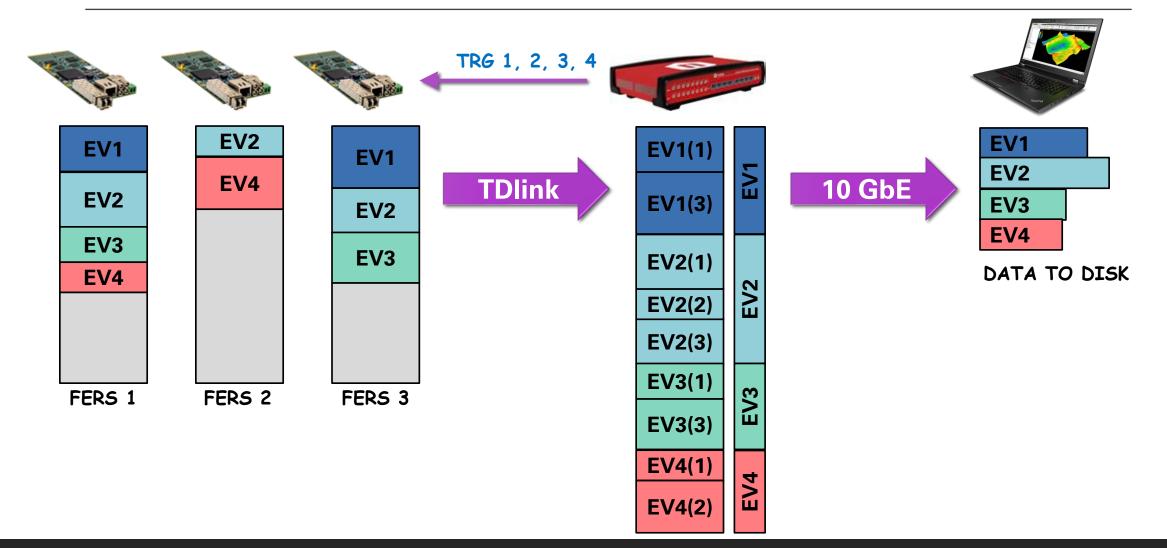

- Common Trigger Mode

- FERS units: generate a trigger request (typically OR of channel discriminators)

- Data Concentrators: receive and combine requests from all units and generate the Global Trigger

- Event Building and data reduction takes place in the ARM processor of the Data Concentrator

- Trigger-less Mode (independent channel acquisition)

- **FERS units**: each channel pushes data asynchronously, typically at different rates

- No trigger and data correlation in HW. Events reconstruction in DAQ.

- ARM processor running Linux and local DDR memory available in Data Concentrator

- High throughput data transfer to host computers via 10 GbE or USB 3.0

- Users can run custom routines for data handling in the embedded ARM

Stand Alone version for Evaluation => scale up to 10k/100k channels with same electronics

- Easy-scalability of systems through daisy-chain of fibers

FERS unit = 64/128 ch

Concentrator = 8k/16k channels

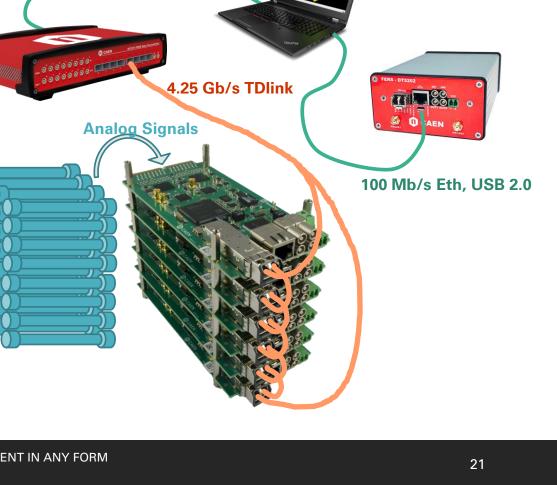

- Dedicated protocol developed for distributed systems

- **Compact** and **dense** FERS units based on **ASICs**: front-end + digital

- Modular readout of large arrays of detectors

1/10 Gb/s Eth, USB 3.0

**Off-the-shelf front-end ASIC** for scientific instrumentation.

Readout of **SiPMs**, **Si strips**, **GEMs**, PIN diodes, microMegas, MA-PMTs, ..... for spectroscopy, PSD, timing applications.

Custom solutions for HEP experiments, with expertise in **rad-hard** design

Design of high-end readout electronics and power supply for HEP and NP

We distribute Weeroc worldwide and Nalu Scientific in the U.S. for the scientific community.

Integration expertise – FERS-5200 and others

A compact and flexible architecture supports a wide range of potential applications:

- Proprietary protocol TDlink: 4.25 Gb/s over fiber providing *Readout, Slow Control, Sync* and *Clock* at once

- Allows alignment of the timestamps with external systems too for example GPS

### SCI-Compiler: more than a software