## Michael Goodrich , Carl Timmer, Vardan Gyurjyan, David Lawrence , Graham Hayes ( JLAB ) Yatish Kumar , Stacey Sheldon (ESnet)

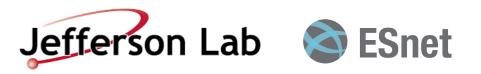

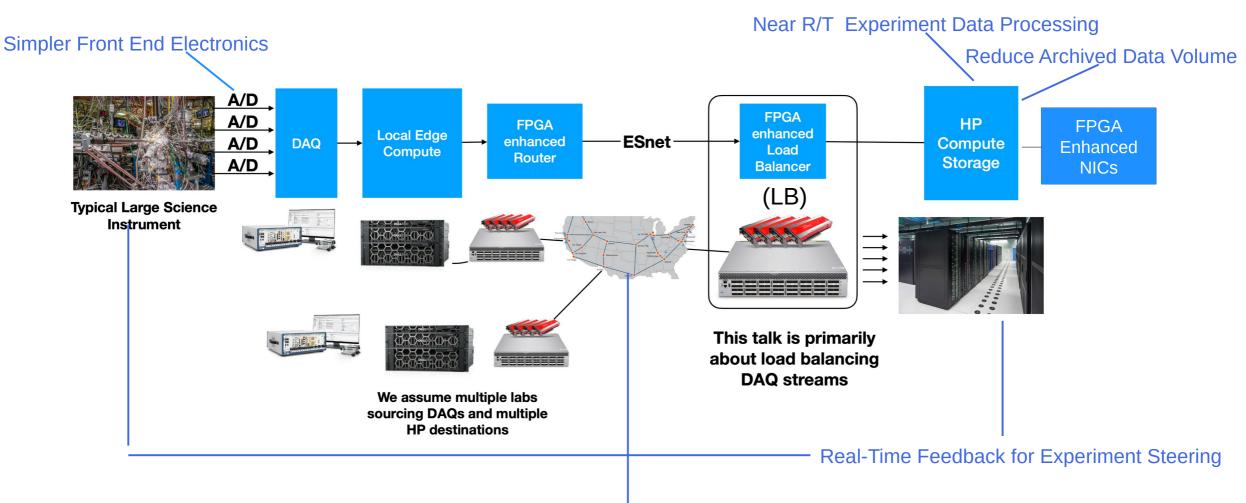

#### **EJFAT** = Edge to Core System Architecture to Support High Throughput Experiment Workflows Steered by AI/ML

# LB: Xilinx U280 FPGA (PCIe) + Host

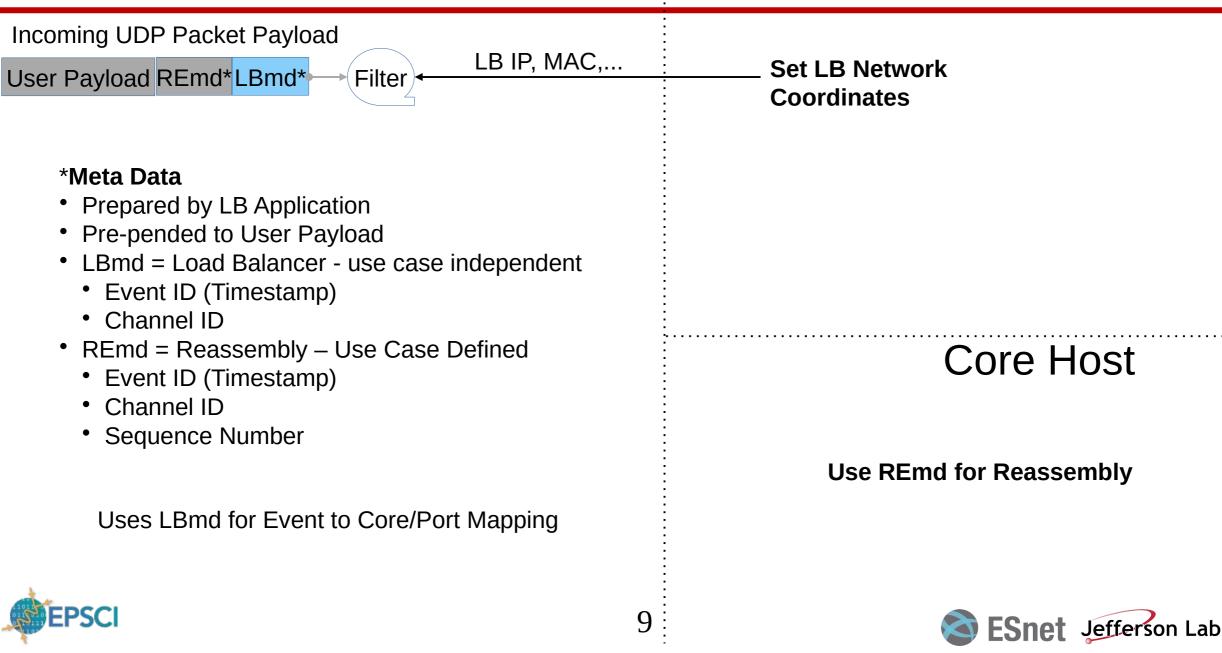

- **Data Plane** (DP): FPGA FW = RTL + P4

- Packet Filtering, ARP, Ping

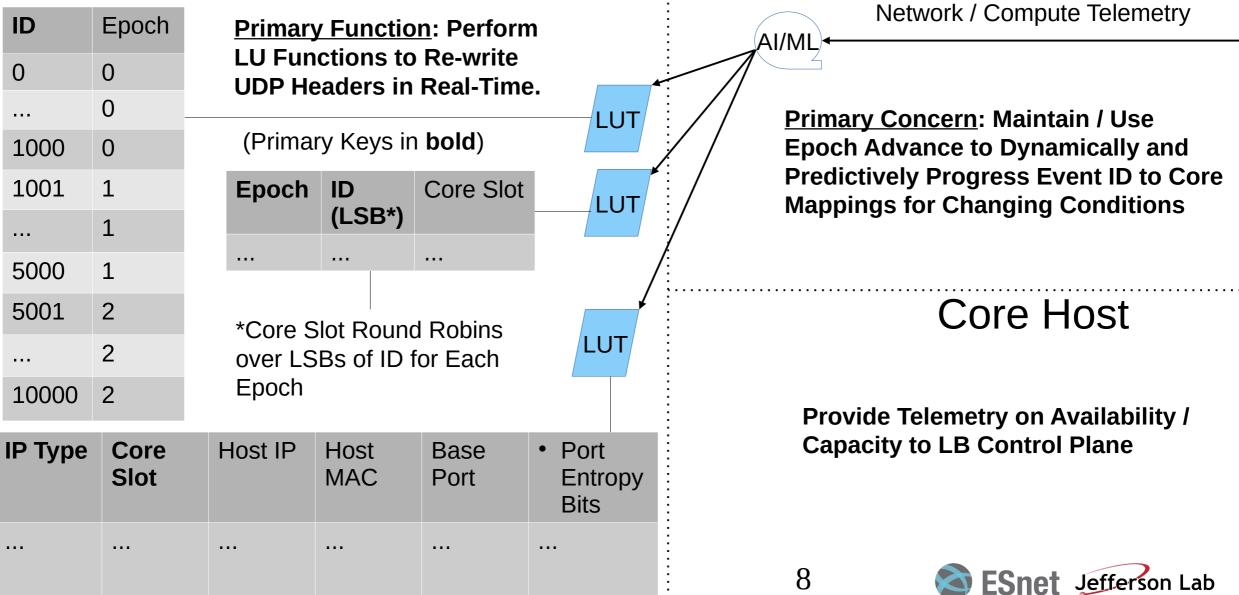

- P4: Data Base for UDP Hdr Rewrites

- **Control Plane** (CP): Host

- DP DB Maintenance

FPSC

- Monitor Network / Core Telemetry

- AI/ML Steerage / Feedback

- Upstream: Experiment / DAQ

- Downstream: Core Computing

- Core Resource Provisioning

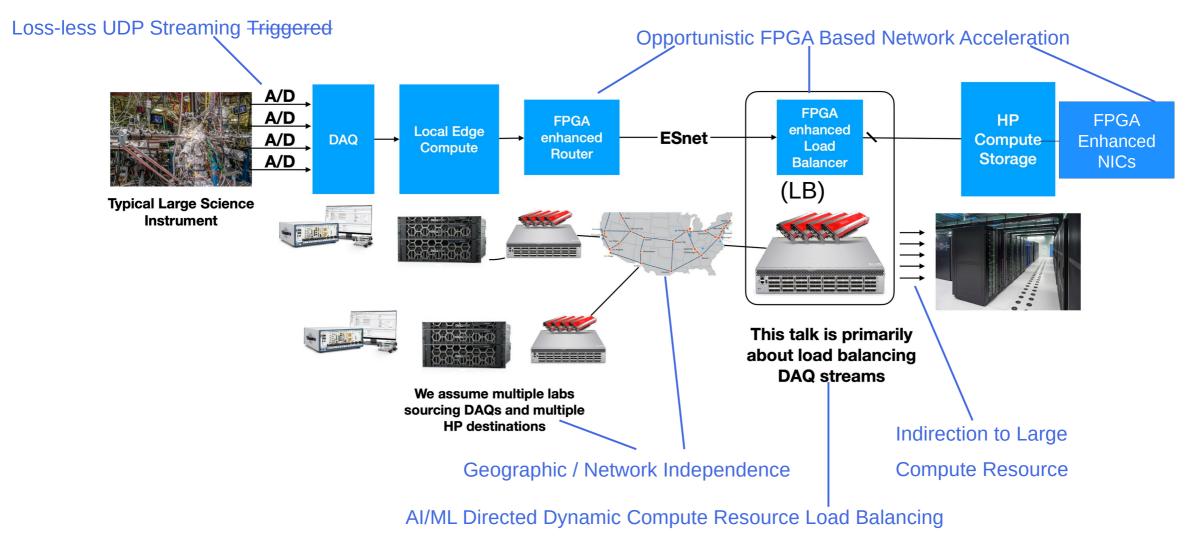

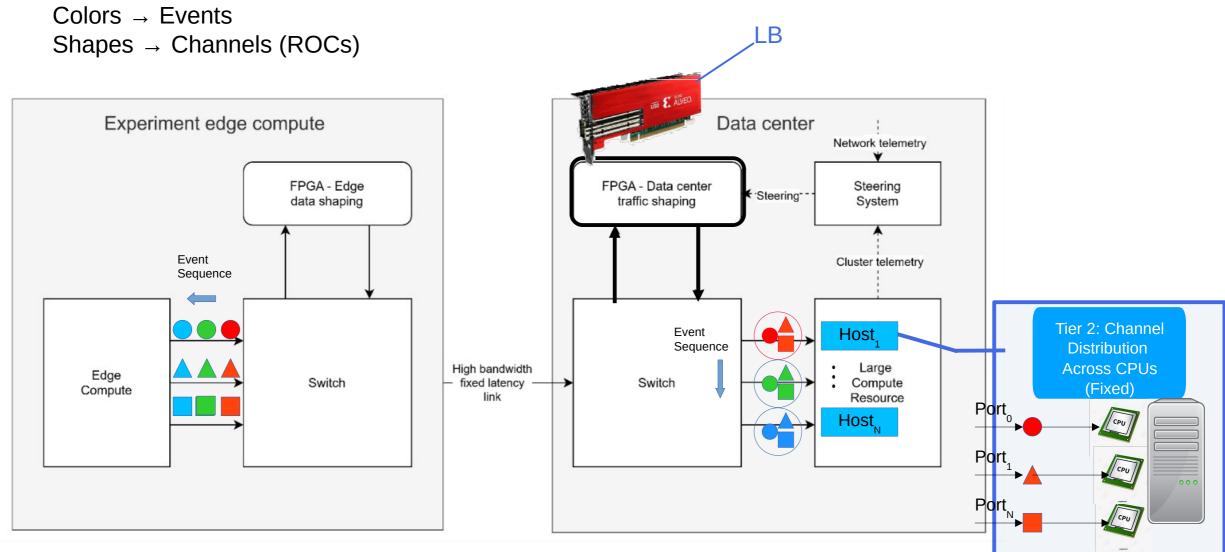

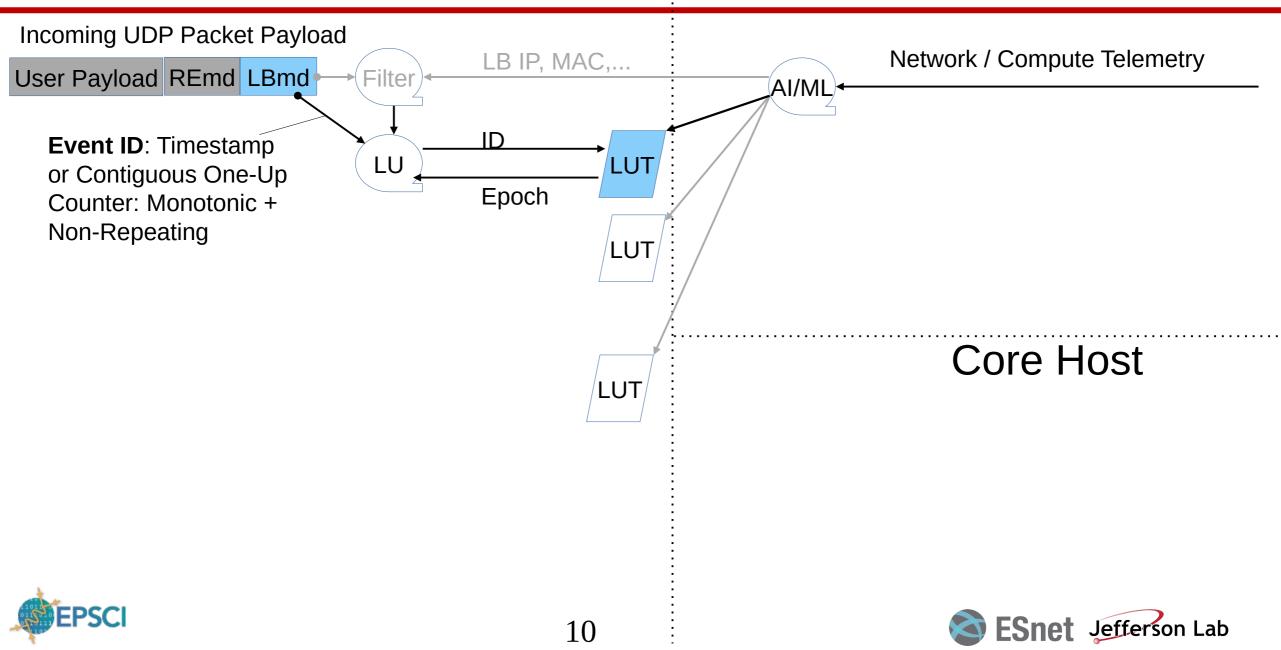

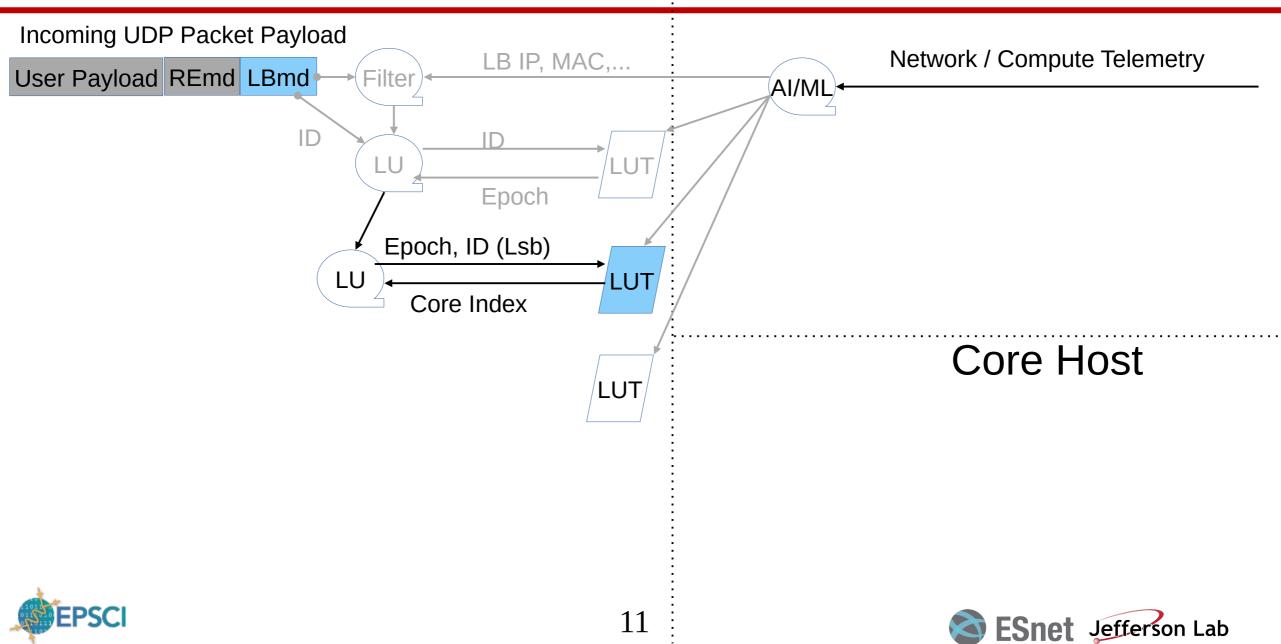

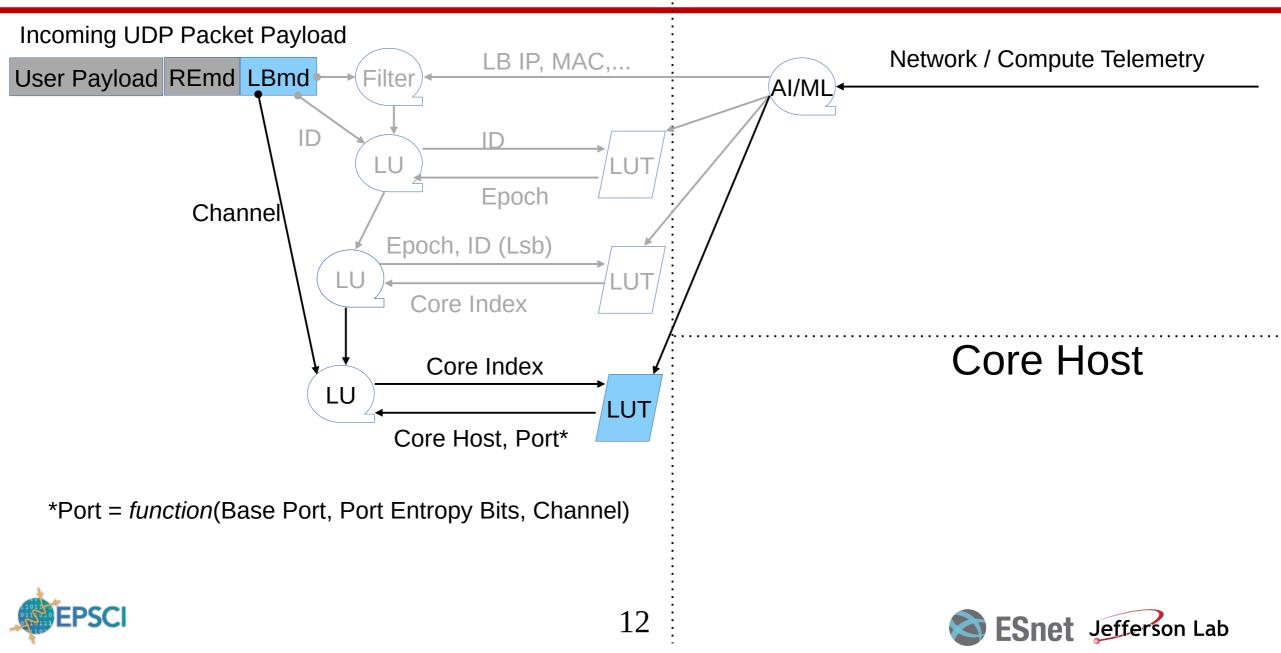

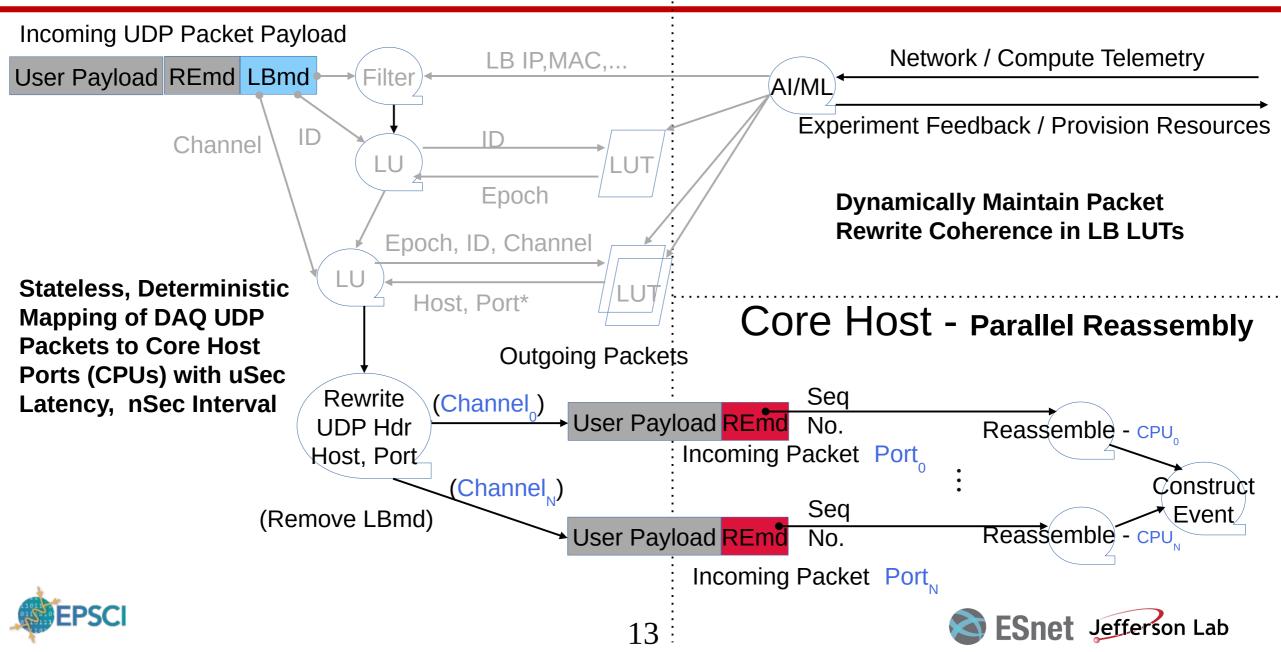

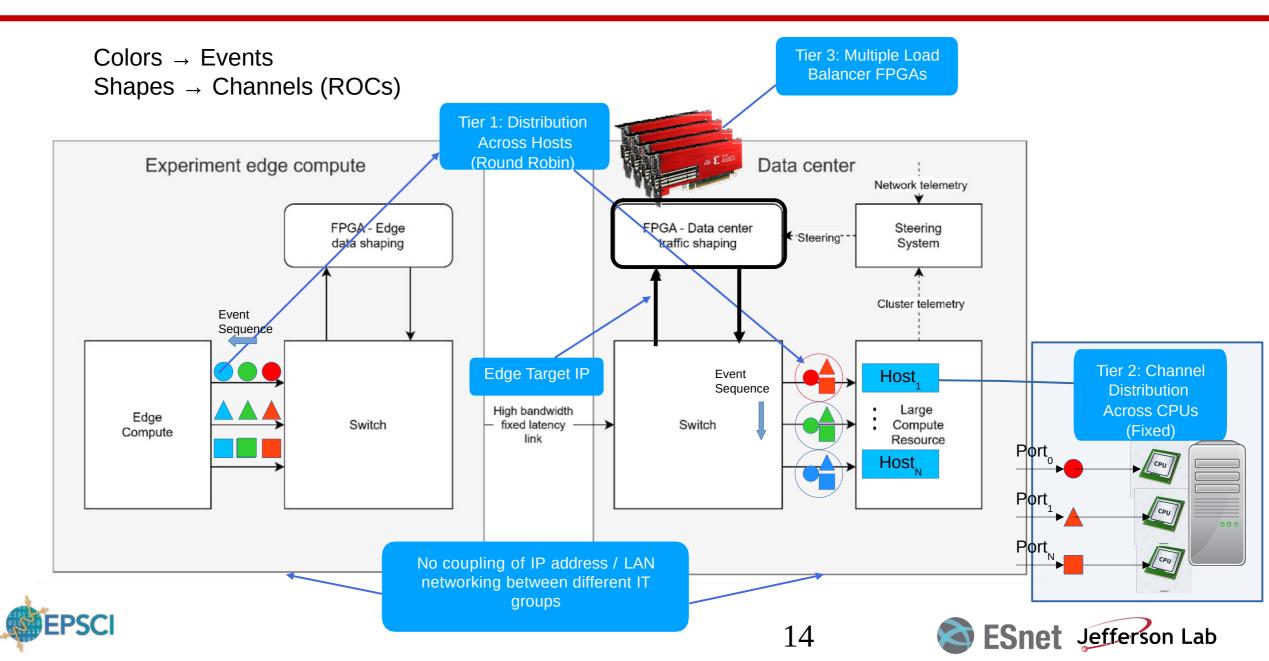

#### Load Balancing = Data Channel Aggregation + Tiered Horizontal Scaling

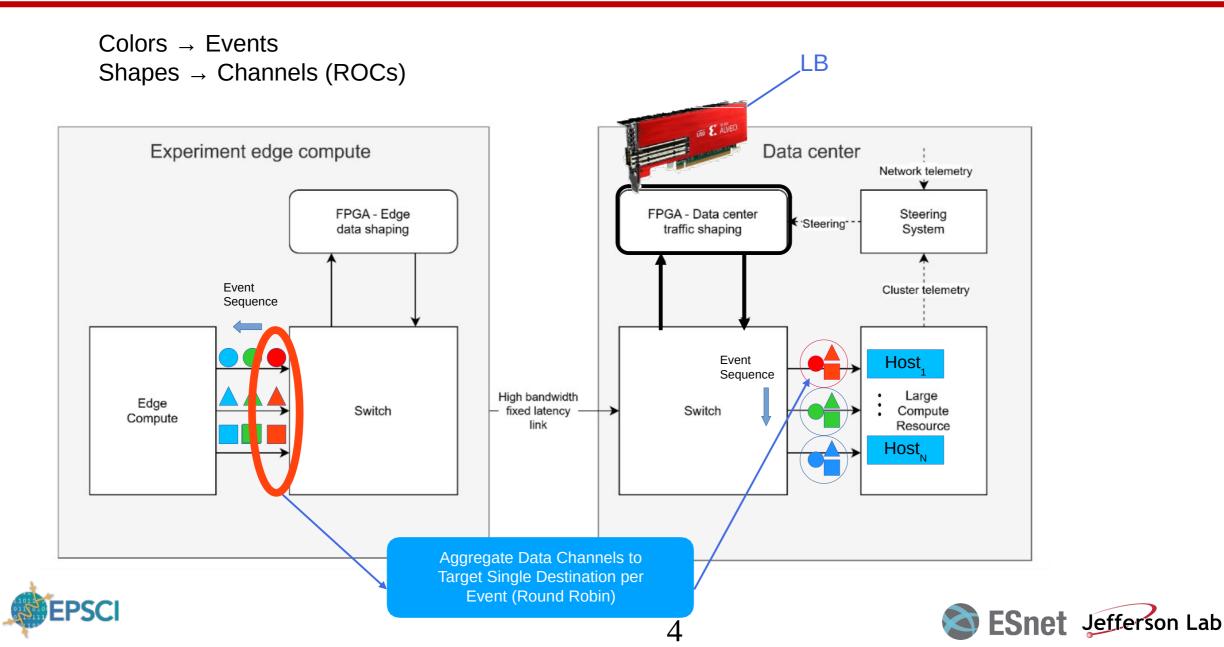

#### Tiered Horizontal Scaling: Tier-1 – Across Hosts

#### Tiered Horizontal Scaling: Tier-2 – Across Host CPUs via Ports

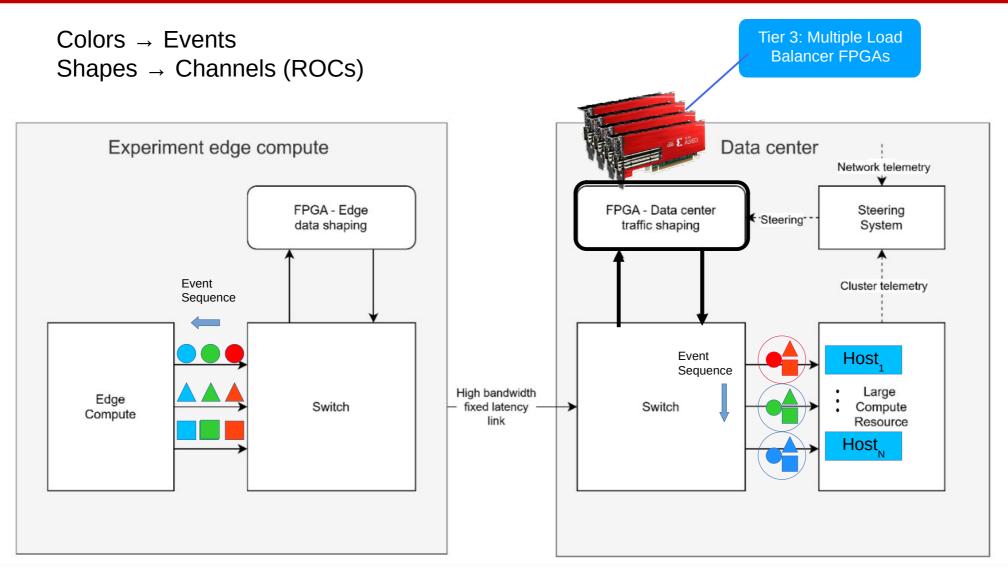

#### Tiered Horizontal Scaling: Tier-3 – Across LBs

## LB Control Plane

#### Epoch: Contiguous Event ID Subspace

## **Control Plane Host**

#### **Control Plane Host**

#### **Control Plane Host**

#### Summary : Channel Aggregation + Three Tier Horizontal Scaling

## Benefits

Facilitates Data Centers Supporting Multiple Labs and Experiments (Reduced Power, Cost)

EJFAT

# Questions ?