1

# Preliminary Design of CDEX-100 DAQ Achitecture

Jingjun Wen, Tao Xue, Lin Jiang, Jianmin Li, Yinong Liu

Tsinghua University On behalf of the CDEX Collaboration

August 1<sup>st</sup> 2022

23<sup>rd</sup> Virtual IEEE Real Time Conference

#### OUTLINE

#### Introduction

- CDEX-100 Experiment

- Current Structure of DAQ System

- Hardware and PCB layout

- Readout and Clock Architecture

- Signal Integrity and Clock Distribution Test

- Status and Plans

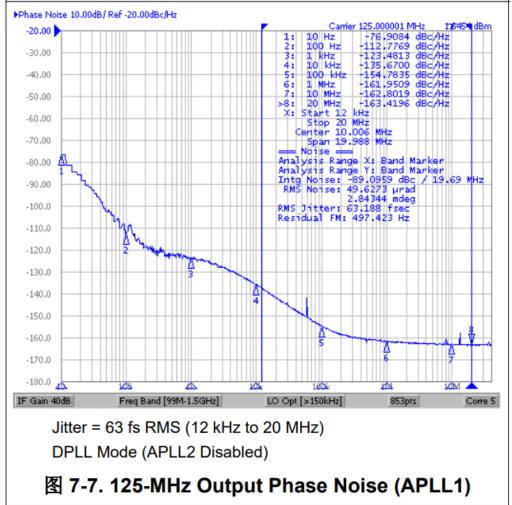

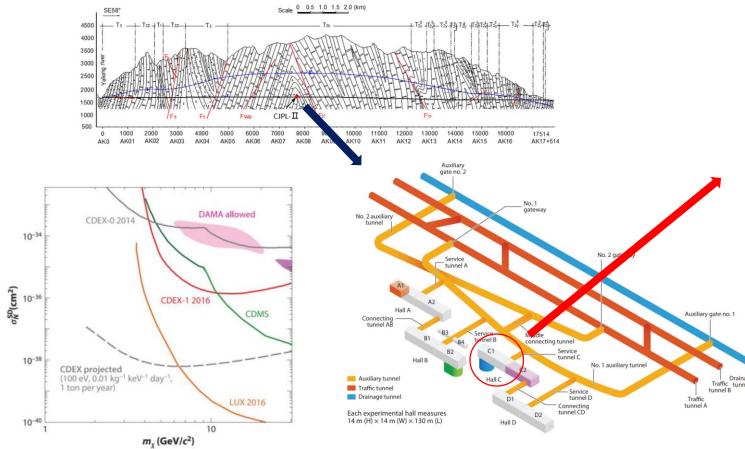

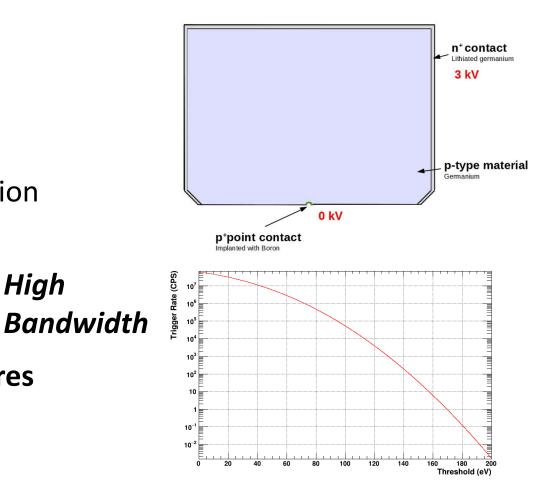

## **CDEX-100** -- China Dark matter EXperiment

- Direct detection of cold dark matter with 100-kg PCGe

- 100 PCGe (1 kg / detector)

- Located in CJPL-II (2400 m underground)

Drainag

# **CDEX-100** -- China Dark matter EXperiment

- **Readout Requirement for DAQ System**

- **300** Sampling channels

- 100 PCGe (3 channels/detector)

- **High sampling resolution**

- Better energy resolution & PSD efficiency -

- Sample Rate 125 MSPS and 16 bits resolution

- Support **ultra-low trigger threshold** (~120 eV)

- ~3kHz @(120 eV threshold)

- Long record time (~120 us each trigger)

- Low-threshold rare case search still requires high transmission bandwidth

- Synchronization system

High

#### Introduction

- CDEX-100 Experiment

- Current Structure of DAQ System

- Hardware

- Readout and Clock Architecture

- Signal Integrity and Clock Distribution Test

- Status and Plans

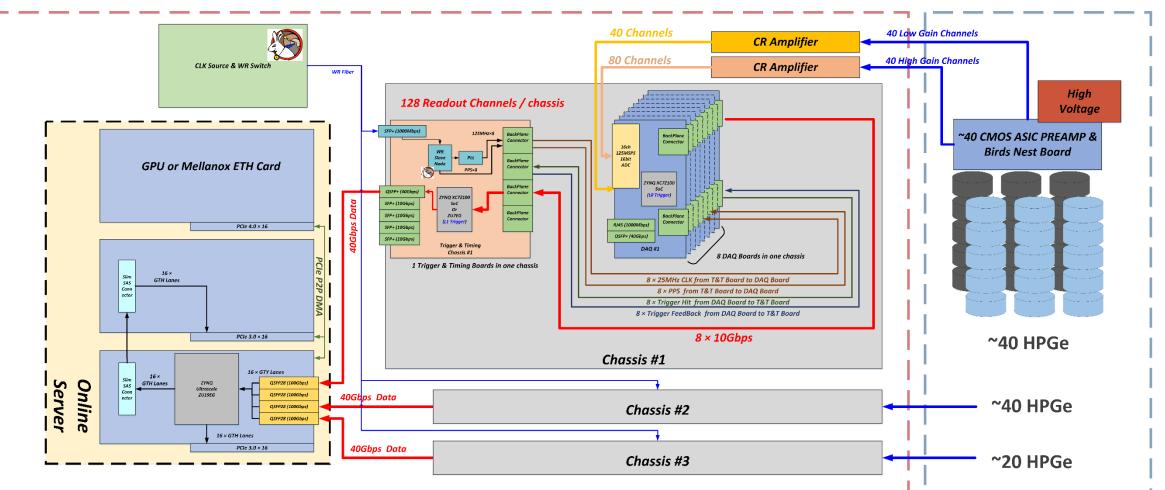

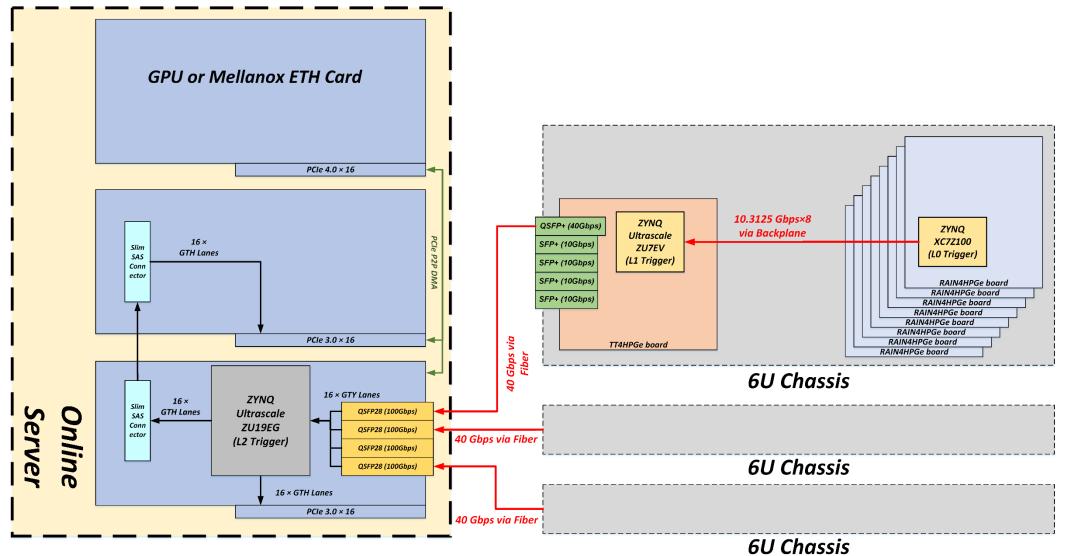

## **Current DAQ System Block Schematic**

- Data Transfer: Backplane + Fiber + PCIe

- Clock Sync: White Rabbit

WARM

COLD

6

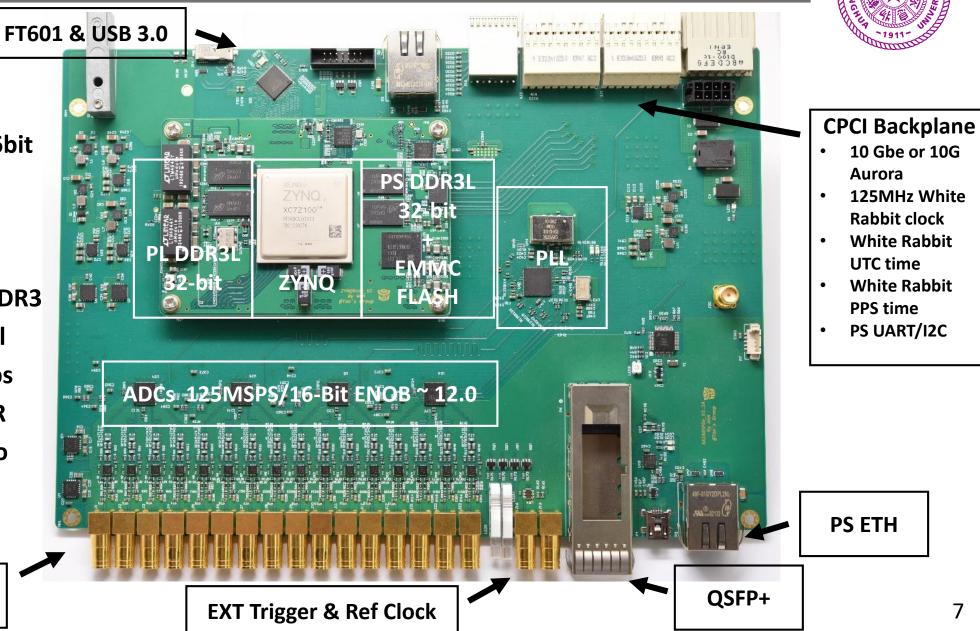

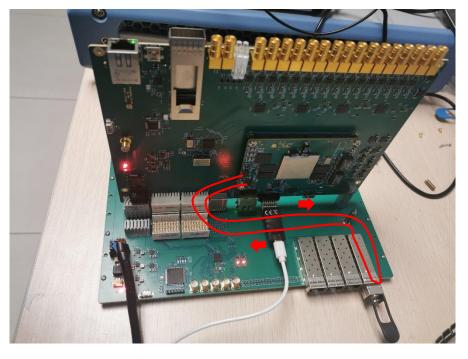

# **Readout Unit : RAIN4HPGe Hardware**

- Provide 16 sample channels 125M/16bit ENOB > 12.0 bits

- ZYNQ XC7Z100 SoC as readout unit

- 32-bit, 1GBytes DDR3 as deep buffer pool

- Backplane 10Gbps

- Using DS125BR

250 Redriver to

guarantee SI

- QSFP 40 Gbps

16 analog inputs

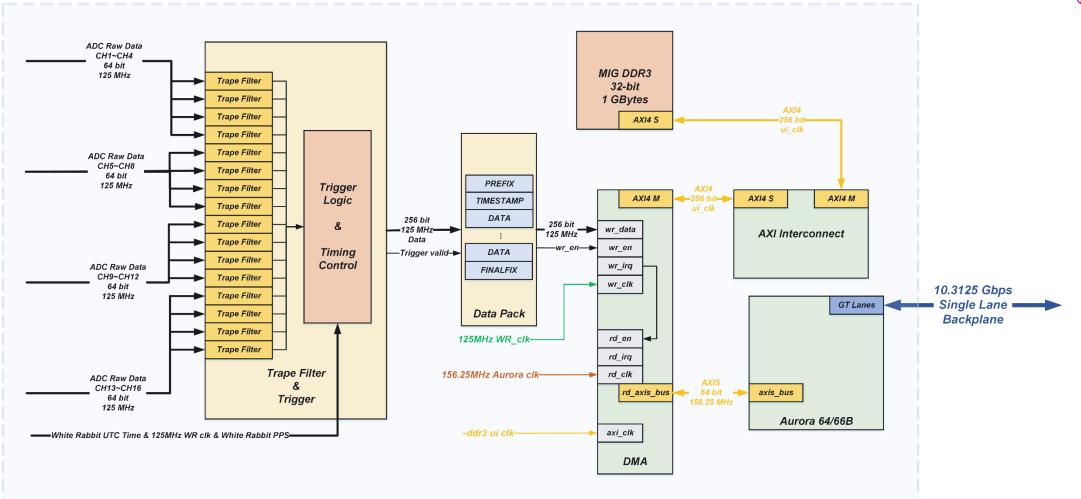

#### Readout Unit : RAIN4HPGe block & Firmware

#### **Clock Distribution Tree**

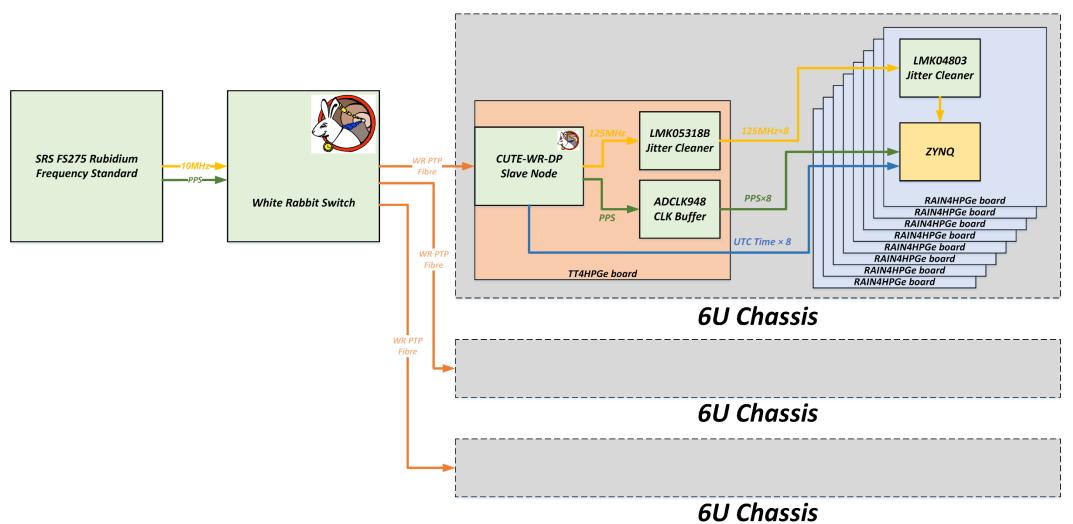

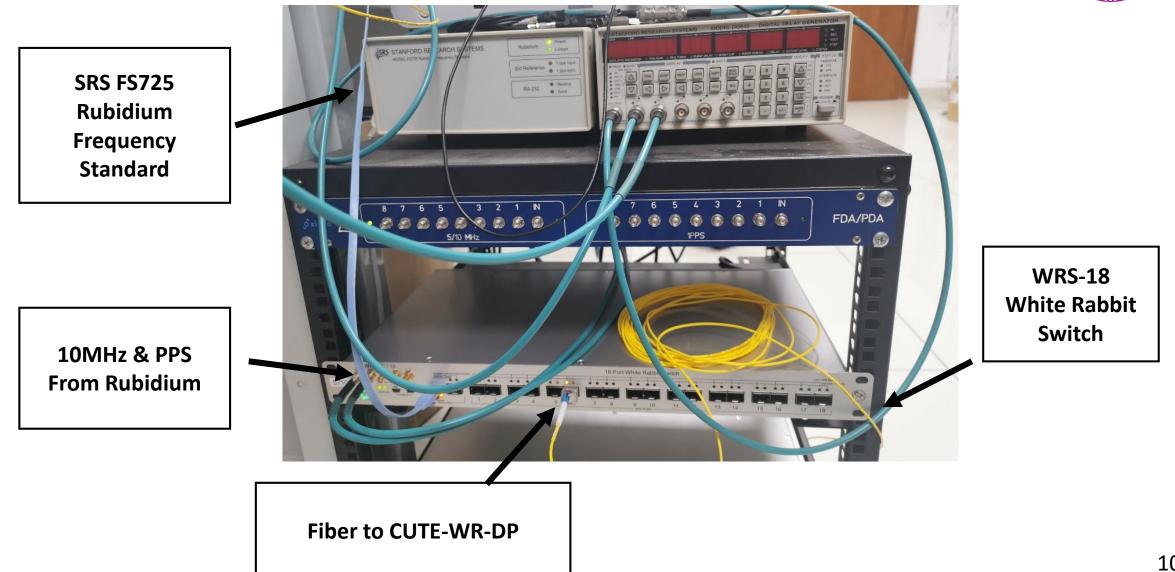

#### **WR Switch and Clock Source**

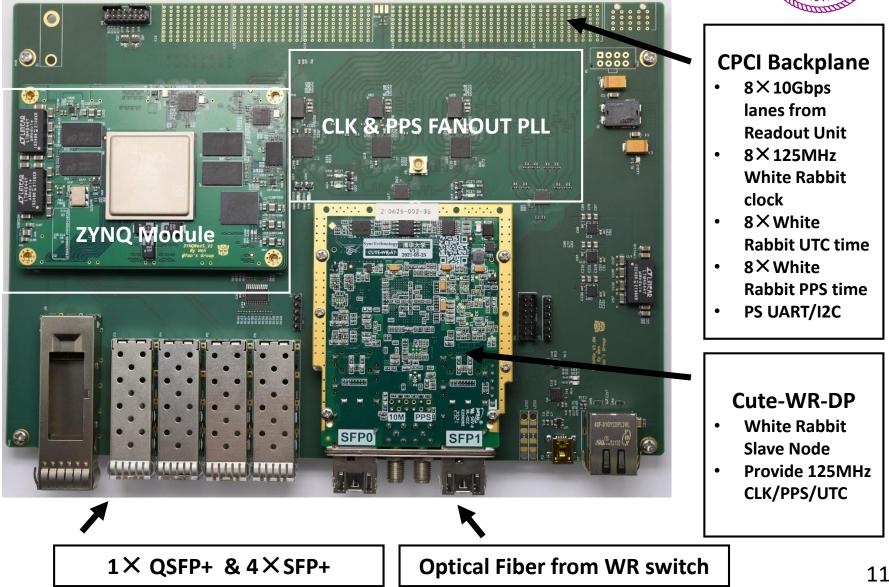

# **Trigger & Timing Unit : TT4HPGe Hardware**

- Cute-WR-DP provide

sync clock/PPS/UTC

- On board PLL & Jitter Cleaner fanout clock/ PPS to Readout Unit

- Receive the data from 8 Readout Unit

- L1 Trigger & Upload via

QSFP+ & SFP+

- 32-bit, 1GBytes DDR3 /64-bit, 4Gbytes DDR4 as deep buffer pool

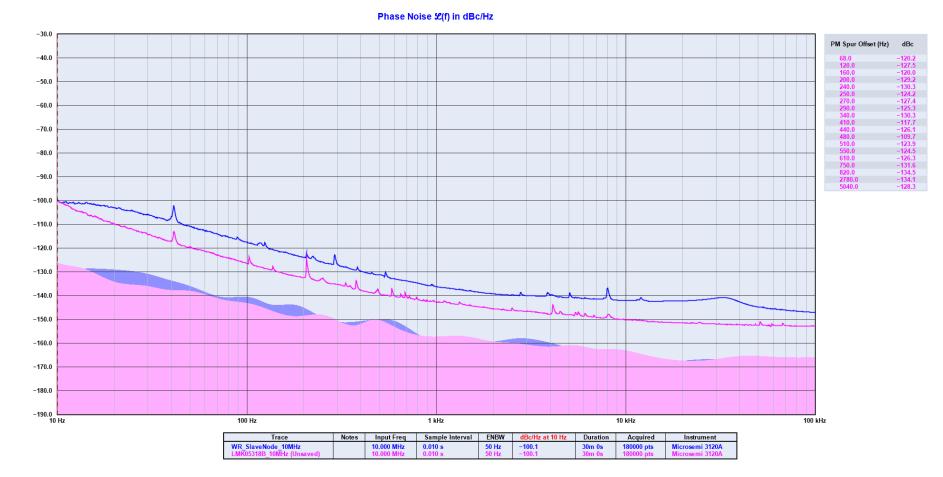

# **Clock Distribution Test**

• Phase Noise

- Blue Line : 10 MHz from CUTE-WR-DP

- Red Line : 10 MHz fanout by LMK05318B PLL (clk source CUTE-WR-DP)

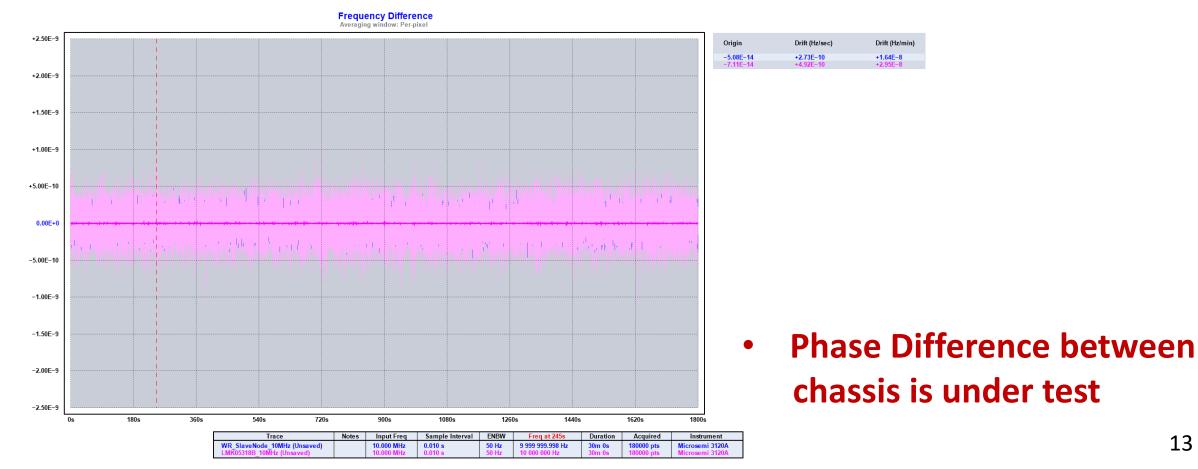

# **Clock Distribution Test**

**Frequency Difference**

- Blue Line : 10 MHz from CUTE-WR-DP

- **Red Line : 10 MHz fanout by LMK05318B PLL (clk source CUTE-WR-DP)**

#### **Readout Data Collection Tree**

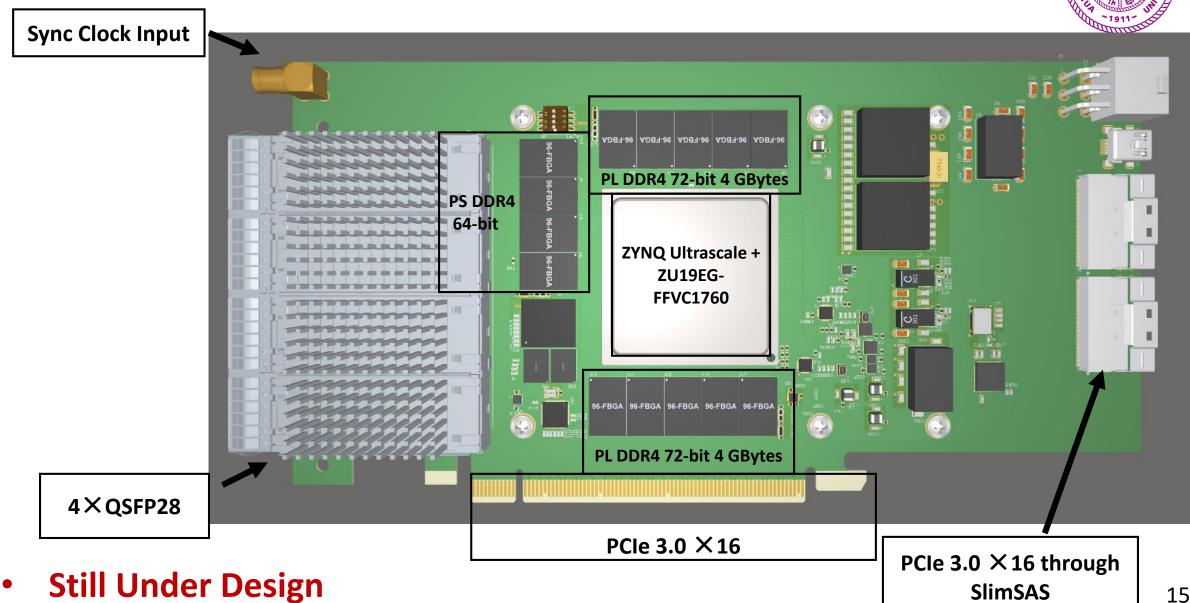

## **PCIe Network Unit :**

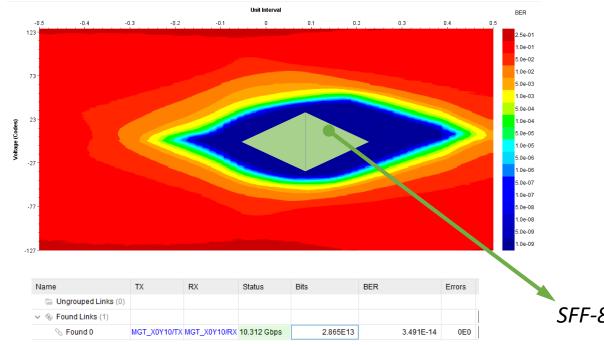

# **Signal Integrity Test**

- SI Test was carried on a Test Backplane

- Long trace loop (~17 inch), through Readout Unit/B2B

Connector/Backplane Connector/Backplane

- Lane Speed : 10.3125 Gbps

- Coding Style : PRIBS-31

*BER < 1E-13*

SFF-8418 Minimum eye diagram at the receiver

### OUTLINE

#### Introduction

- CDEX-100 Experiment

- Current Structure of DAQ System

- Hardware and PCB layout

- Readout and Clock Architecture

- Signal Integrity and Clock Distribution Test

- Status and Plans

# **Status and Plans**

• Hardware

- Readout Unit & Trigger/Timing Unit & Backplane is verified

- PCIe Network Unit is in design

- Firmware

- Firmware of the Readout Unit/Trigger/Timing Unit has alpha version released and is under testing

- Firmware of the PCIe Network Unit is still under developing

- Joint Test of the Readout Unit and Trigger/Timing Unit is running

- Lossless data compression algorithm is also under study

# Thank you for your attention!

23<sup>rd</sup> Virtual IEEE Real Time Conference

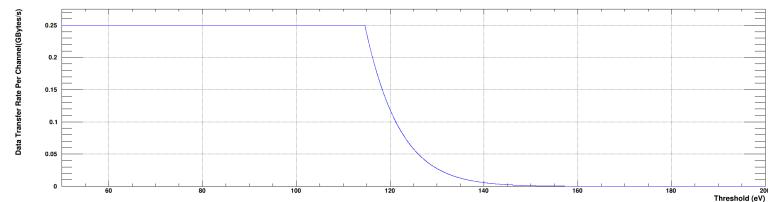

#### BACKUP

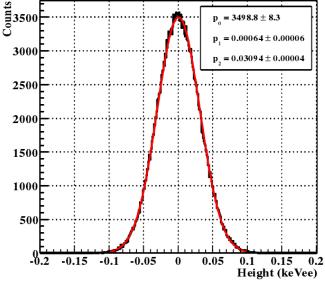

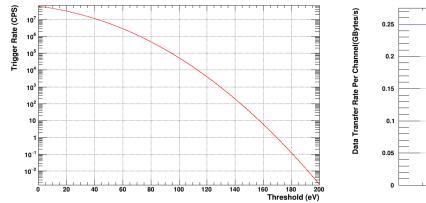

- **Trigger threshold v.s. Data transfer rate**

- **CDEX-1B system noise** \_

- $\mu = 0 eV, \sigma = 30 eV$ \_

- The number of points whose value exceeds x<sub>m</sub> -

Counts =

$$f_s \times \int_{x_m}^{+\infty} P(x) dx$$

where  $P(x) = \frac{1}{\sqrt{2\pi\sigma}} \cdot e^{-\frac{1}{2}\left(\frac{x-\mu}{\sigma}\right)^2}$

**Record 120 us (Once trigger)** \_

**CDEX-1B** System Noise  $\sigma = 30 \text{eV}$

#### BACKUP

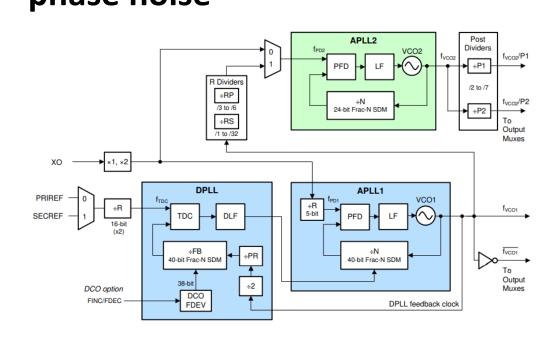

- Clock phase noise v.s. Jitter cleaner

- LMK05318B

- Use DPLL to clean jitter

- APLL use BAW VCO to achieve phase noise