**Atmospheric Neutron Effects**

in Advanced Microelectronics

An introduction and a Real-Time concern

Jean-Luc Leray

Consultant, formerly CEA, France

jean-luc.leray@ieee.org

# Radiations are pervading everywhere! Focus on particles with largest ionizing rate (dE/dx)

- Nature

- Galactic Cosmic Rays

- Solar Flares

- Radiation Belts

- In large space stations as ISS

- Atmosphere

- Ground

- From underground (U and Th decay)

## Human made

- Radiotherapy/target areas

- Fission

- Fusion research

- HEP/Experimental areas/tunnels

neutrons?Or else../ions.../p, e, light ions.../p and esome, because of spacecraft structure massyes, peak at 18kmalong with hadron, mesons, muons(-), ..yes,mostly with muons (-)/mostly alphas

#### <mark>Yes</mark>

Yes (usually confined in water-filled vessels) More or less/Heavy shield around plasma vessel Yes Natural atmospheric neutron flux spectrum at ground level after interactions in the atmosphere (O and N)

3

3

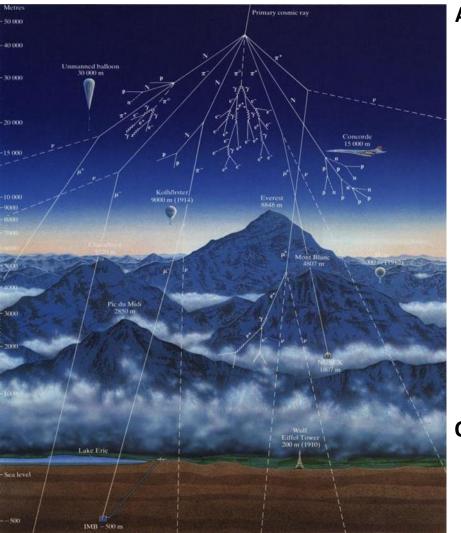

#### Geophysics of cosmic natural radiation in the atmosphere and at gound level

## => Concerns: Global safety of transportation

#### Atmospheric:

#### Aircraft builders Reliability in time Certification Authorities Stingent safety specifications Plane: < 1 event per 10<sup>7</sup> flightxhours

#### Main parts providers

Reliability in time Certification Authorities Stingent specification Flight computer, Autopilot, Engine Controlers < 1 event per 10<sup>7</sup> flight hour

=> Electronic device < 1 event per 10<sup>9</sup> flightxhours

#### Other concerns at Ground level:

- More electric automotive

- More Information Technology dependable systems

- Internet backbone

- high-end servers and computers

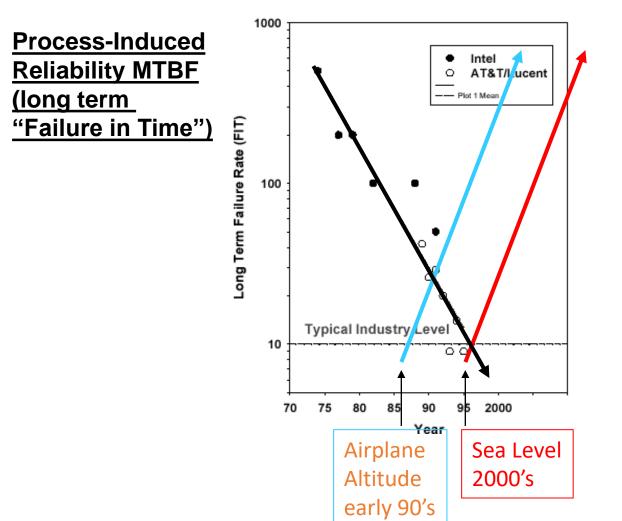

CMOS reliability continously improved by manufacturing tremendous progress (if we disregard radiation radiation effects)

Historical IC Failure Rates

#### **Conversely, the Effects of Additional Radiation Became clearly visible.**

#### BUT

due ever increasing circuit sensitivity to natural particle environment

Especially visible in Everyday Vehicles or High Security Business (Airplanes, Automotives, Railways, Internet Routers..)

INTERNATIONAL RELIABILITY PHYSICS SYMPOSIUM 2002 Reliability Issues for Advanced IC Technologies Anthony S. Oates

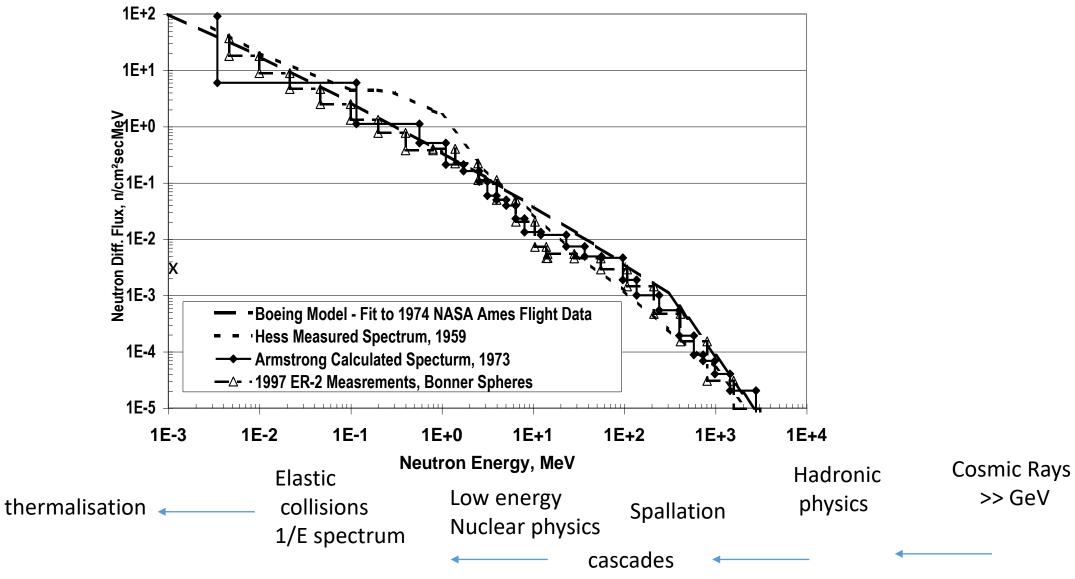

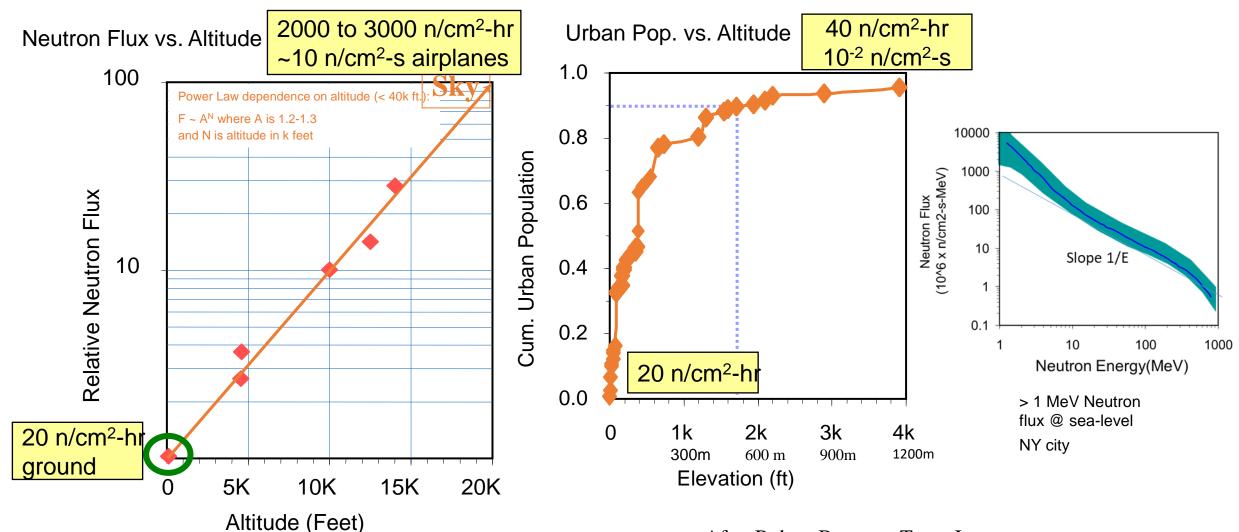

#### Atmospheric Neutron flux

at Ground level = where Consumer electronics runs and population is living

After Robert Bauman, Texas Instrument RADECS CONFERENCE SHORT COURSE, Sept. 2001

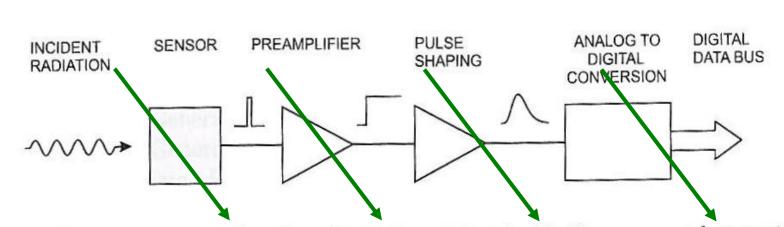

# Where in <u>Real Time Effects in a detection chain ?</u>

DETECTOR SYSTEMS OVERVIEW

FIG. 1.2. Basic detector functions: Radiation is absorbed in the sensor and converted into an electrical signal. This low-level signal is integrated in a preamplifier, fed to a pulse shaper, and then digitized for subsequent storage and analysis.

2

More digital and high bandwidth (Single Event Upsets, Single Event Rate, Single Event Functional Interupts) SEU SER SEFI

More analog and S/N ratio is critical ( Single Event Transient)

# First mention of a « Soft Error » 43 years ago (1979)

- In Dynamic Memory (1kb)

- Single bit at a time, random)

- Related to single alpha particle random emission from ceramic packaging

- Related to U and Th content (contaminants

- Anticipated to occur in arrays such as early SRAMS and CCDS's

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. ED-26, NO. 1, JANUARY 1979

#### Alpha-Particle-Induced Soft Errors in Dynamic Memories

TIMOTHY C. MAY, MEMBER, IEEE, AND MURRAY H. WOODS

Abstract-A new physical soft error mechanism in dynamic RAM's and CCD's is the upset of stored data by the passage of alpha particles through the memory array area. The alpha particles are emitted by the radioactive decay of uranium and thorium which are present in partsper-million levels in packaging materials. When an alpha particle penetrates the die surface, it can create enough electron-hole pairs near a storage node to cause a random, single-bit error. Results of experiments and measurements of alpha activity of materials are reported and a physical model for the soft error is developed. Implications for the future of dynamic memories are also discussed.

#### I. INTRODUCTION

THE SEMICONDUCTOR industry has seen a continuing trend toward higher levels of integration in memory circuits. Random-access memories (RAM's) have progressed from the 1K dynamic RAM with a 3-transistor cell, introduced

tion that the sources mentioned above have been eliminated. The significance of this mechanism is that it cannot be eliminated by standard noise-reduction procedures; only proper design of the memory device itself can eliminate these soft errors.

Dynamic memories store data as the presence or absence of minority carrier charge on storage capacitors. Refresh is required to maintain the stored charge. For n-channel MOS RAM's and CCD's the charges are electrons, and capacitors take the form of potential wells in the p-type silicon under positively charged polysilicon gate electrodes. The amount of charge which can be stored is typically in the range of 300 000 to 3 000 000 electrons. However, the number of electrons which differentiates between "empty" and "full" wells is reduced from the above amounts by such effects as:

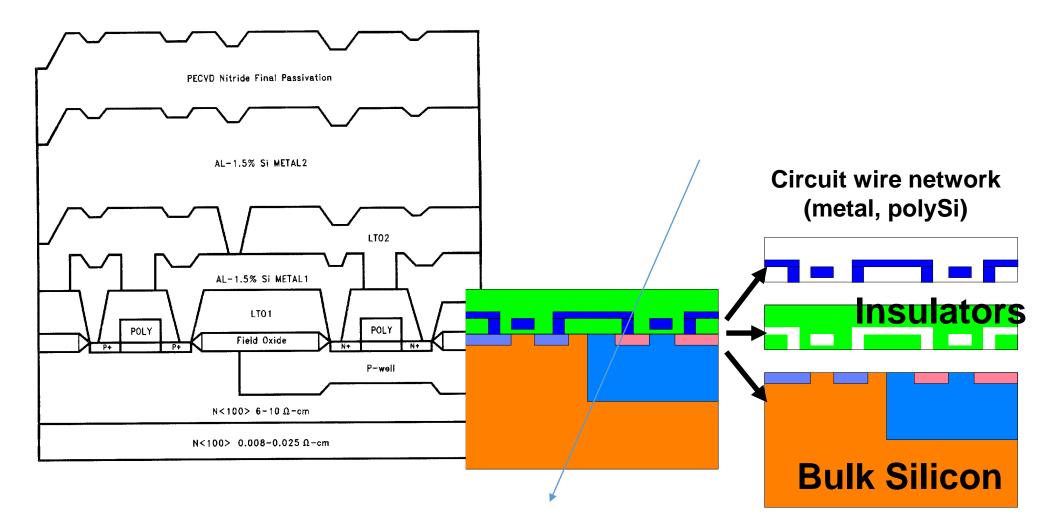

## Interactions in a typical IC in the 70's

#### FACT<sup>™</sup> 54ACxx 2 µm CMOS

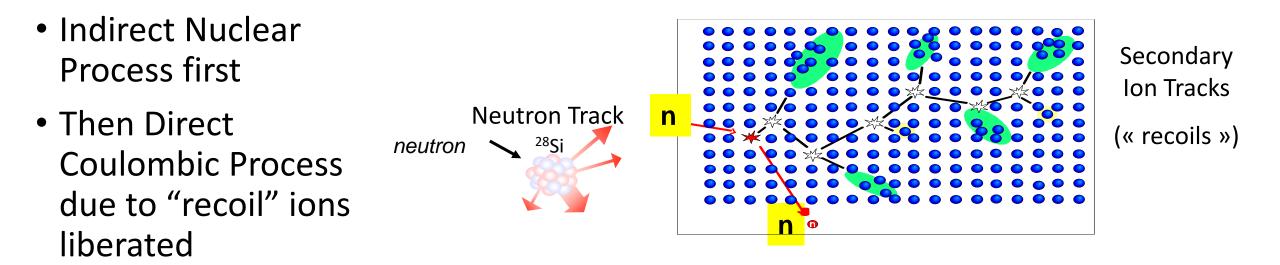

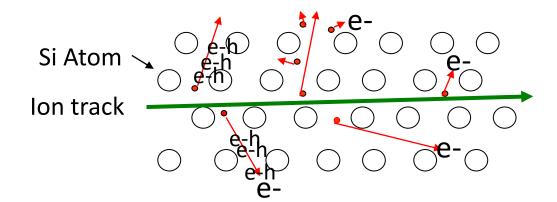

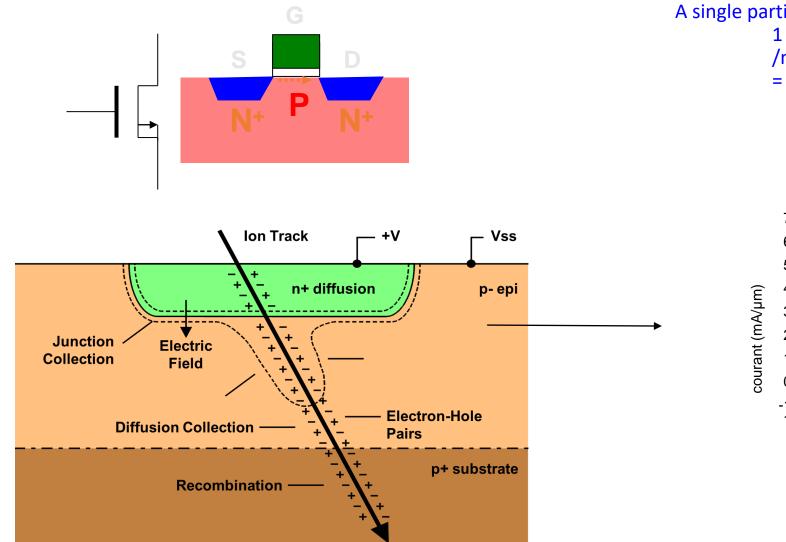

# Silicon Devices as Particle Detectors of neutrons

e-h = electron hole pair

=> Ioniziation: up to 10 fC/µm along the track

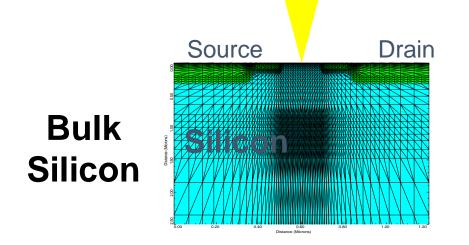

# We go back of the basic of a transistor

#### Mostly a $\Delta E$ mode detector

Vastly sort of pixelized in a 2D if not 3D array

## Effect of one charged particle Radiation and Hard or Soft Errors

A single particle hit excites between 1 000 and 100 000 electrons and holes /micron in a typical semiconductor = 0.16 to 16 1<sup>E</sup>-15 coulomb/µm

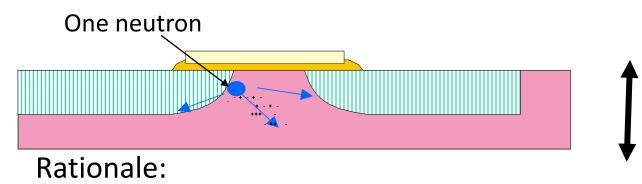

## SCALING - Orders of magnitude in case of atmospheric neutrons

Sensitive Layer 1 µm approx

- Probability that a neutron hit a silicon atom near a transistor and randomly generate recoils witch trigger a signal

- Assumptions

- $\sigma_{nuclear}$ , order of magnitude 1 barn ;

- 28Si (10B as a dopant to silicon also is of concern for thermal neutrons)

- Active layer in silicon wafer ~ a layer of 1  $\mu m$  where the transistors stan

## => Probability of a signal ~ approx. 10<sup>-5</sup> per incoming neutron

Consequence, a serious Reliability Issue..

- at sea level: 10 neutron/cm<sup>2</sup>/hour

- $\Rightarrow$ 10 x 10<sup>-5</sup> = 10<sup>-4</sup> transient per hour per cm<sup>2</sup> of circuit

- at airplane Altitude: 10 000 neutron/cm<sup>2</sup>/hour

upper limit of one transient per 10 hours of flight per cm<sup>2</sup> of circuit

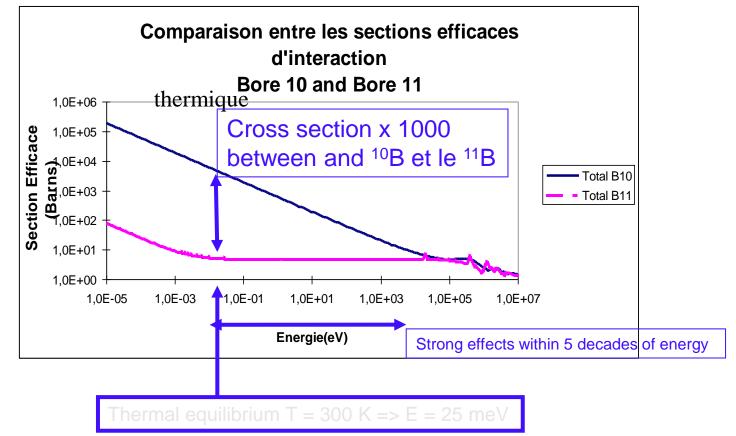

#### 10B isotope in electronic devices

Boron is a commonly used as dopant or softener of glass oxide in silicon devices. Its content and repartition near sensitive volumes is generally unknown. It may be absent.

Nuclear capture breaks 10B and gives highly ionizing alpha particle recoils of single energy 1.5 MeV

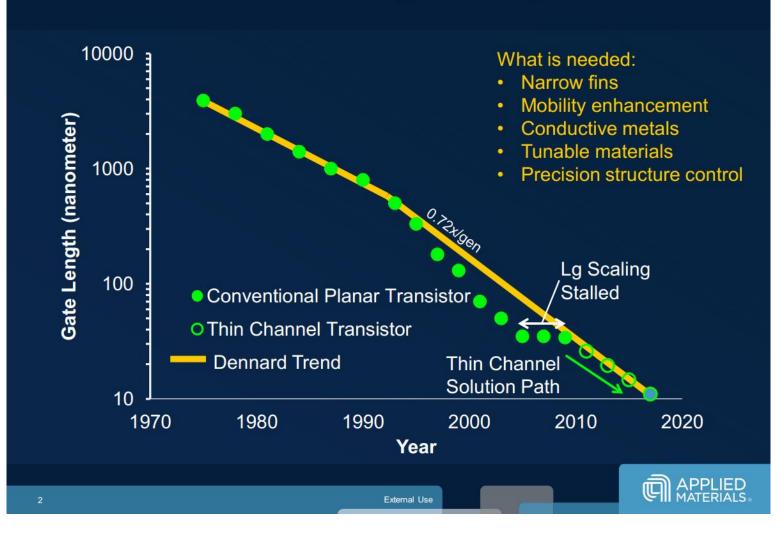

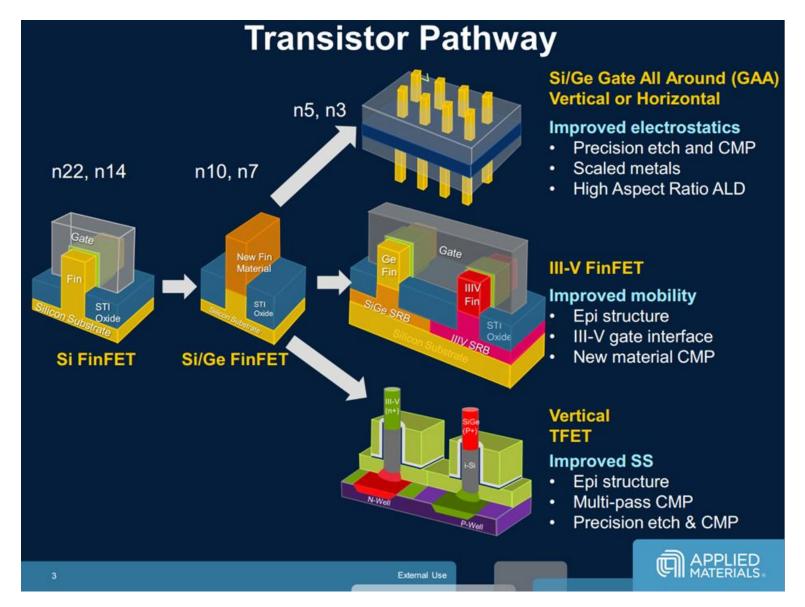

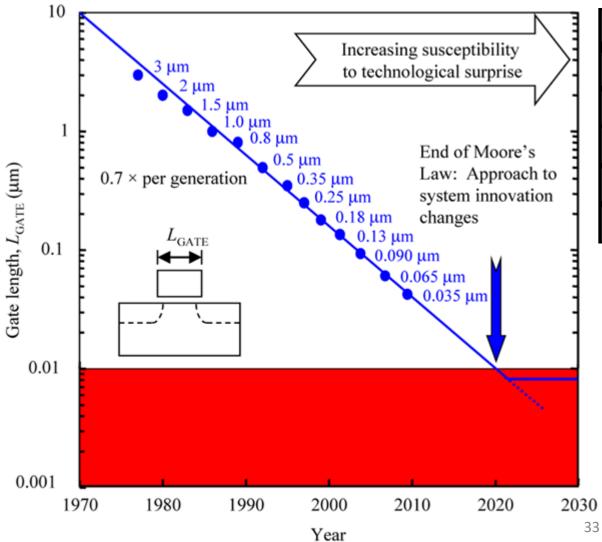

#### **Continue The Lg Scaling Path**

## Soft Error Rate trends – Linked to the stored Charge in a bit Cell

# Planar Electronics is becoming 3D with a stratospheric number of transistors on one cm2

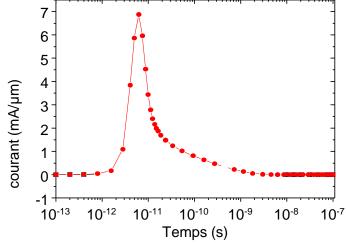

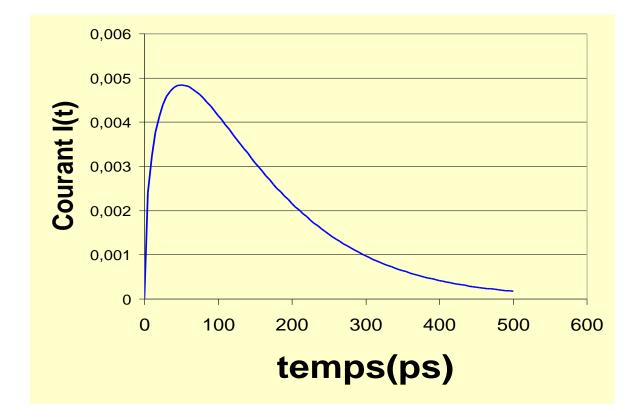

# Current shape

$$I(t) = \frac{2}{T\sqrt{\pi}} \sqrt{\frac{t}{T}} \exp(-\frac{t}{T})$$

Radiation Effects in Electronics for Nuclear and Physics Instrumentation – II

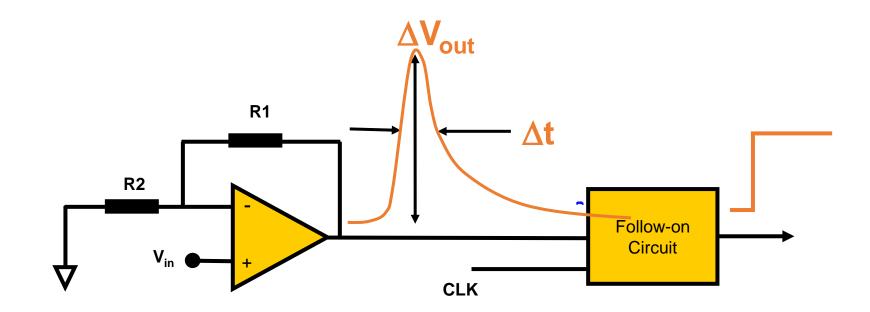

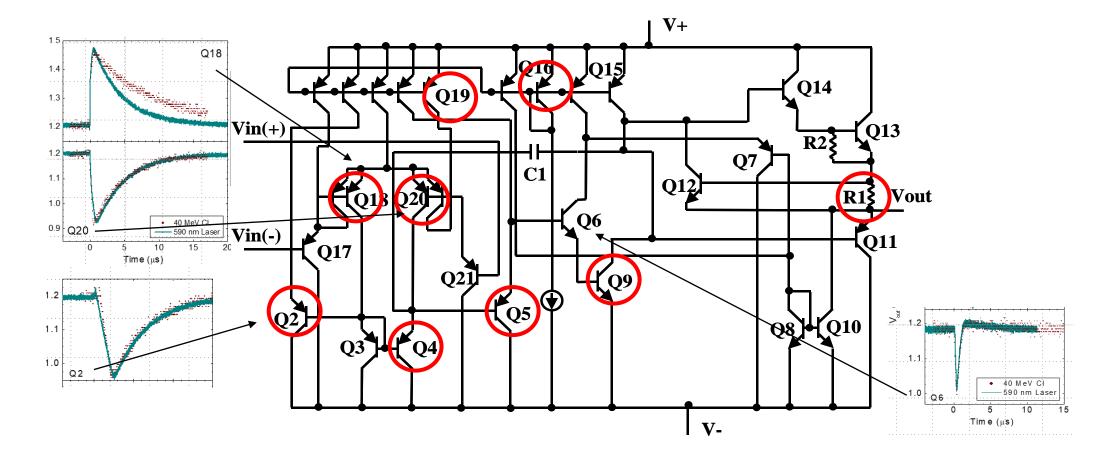

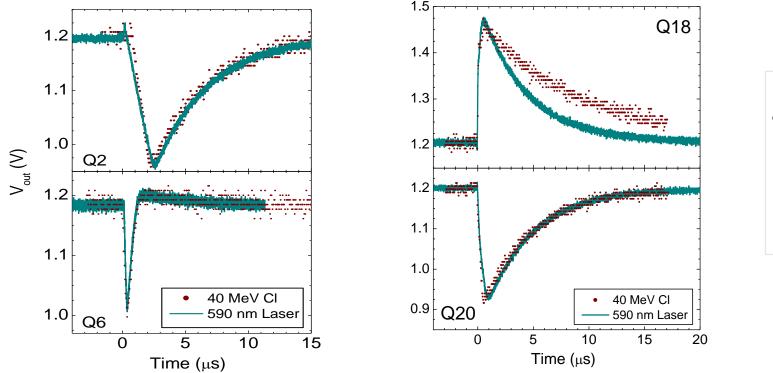

# Single Event in an analog circuit

# Example on an amplifier (LM124), various strike location

**Bipolar transistors are particularly sensitive because of current gain In CMOS technology**

Dale McMorrow, NRL, USA

# **Single Event Transients**

$\frac{LM124}{Inverting}$ Configuration:  $V_{dd} = +/-6 V$  $V_{in} = 60 mV$

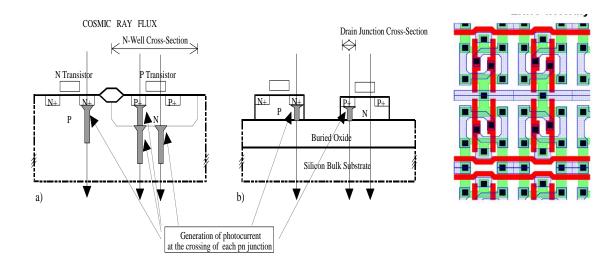

MOREOVER, in a CMOS circuit, any NPN and PNP are hiden in the mesh of N and P doping. They are used in isolation and are supposed to be off, but they are not mute under radiation. They can lock (latch a CMOS device supposed without bipolar:

Buchner, et al., <u>50</u>, IEEE Trans on Nucl. Science, Dec. 2003

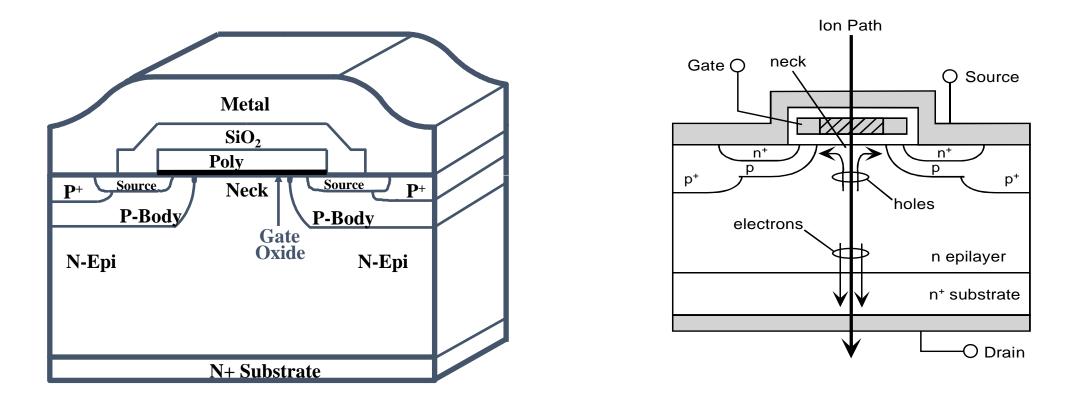

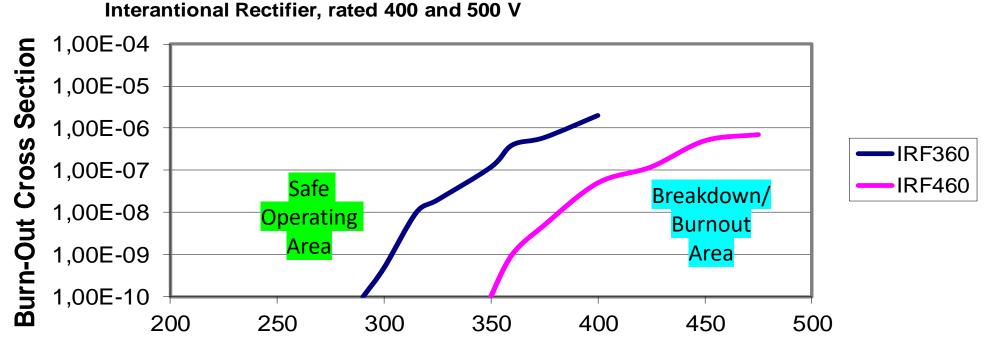

## Power electronics (from 50V to 5kV in silicon) Single Event Breakdown depending on gate and drain to source voltages

Here displayed : typical of space applications, dE/dx between 1 and 100 fC/ $\mu$ m) ~ 50.000 e-h pair per  $\mu$ m

# Safe Operation Area may need a derating of 50 to 70% of the max service drain voltage

POWER MOS BREAKDOWN VOLTAGE

Applied Drain-Source Vds (under gate voltage VGS = 0 V)

TYPE IRF360 (400V) IRF460 (500V) Breakdown voltage threshold 280V 330V

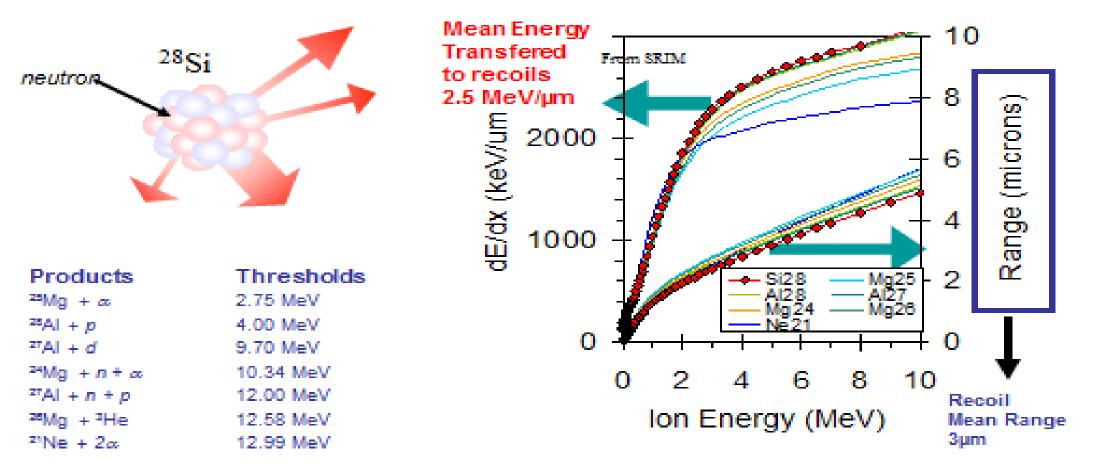

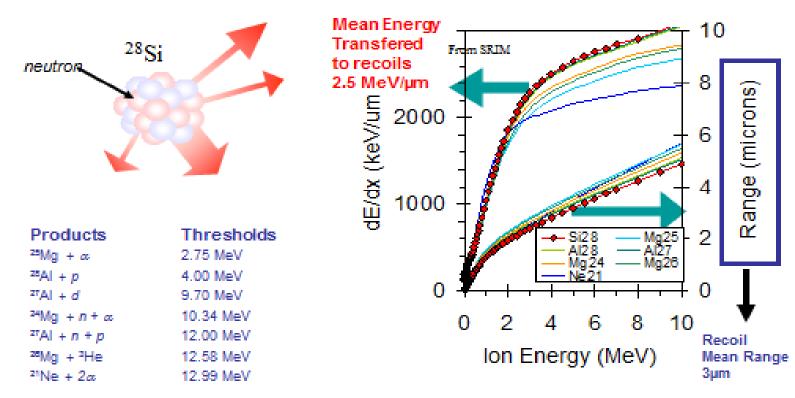

## Back to the basic of Neutron => Silicon

#### Neutron => Silicon Recoil Range = 10µm

Reaction table from F. Wrobel et al., IEEE Trans. Nucl. Phys., Vol. 47, No. 6, Dec. 2000

## **COMPLEX CMOS CIRCUITS**

3. Many Transistor in a circuit 'pixelization' increases complexity **Response on vertical and surface layout**

#### 2. MOS Transistors, 2 or more junctions

Ion strike

Bitline at VDD

Drain of the strud

at V

NMOS

Gates at

/cm3

+1.797e+20

+4.921e+13

+1.348e+07 +3.692e+00

MOS sources and

ll contact (Vpp)

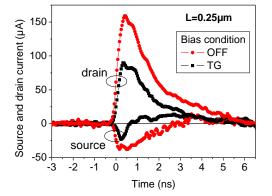

Short transient currents measured at the source and drain electrodes of a 0.25 µm NMOS transistor

35 MeV chlorine ion => Collected Charge 1 to 100 femtoCoulombs => 0.1 to 10 V in 10 femtofarads

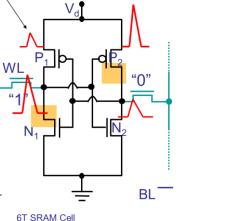

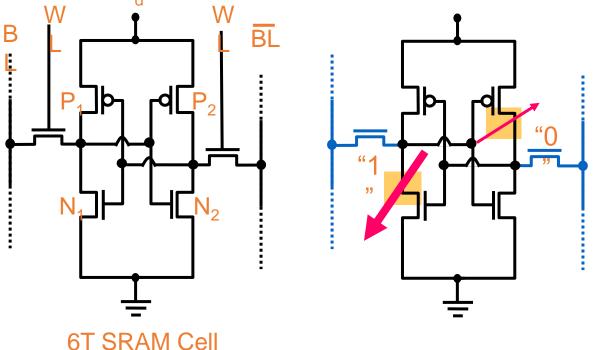

#### 4. Circuit response (SRAM 6-T cell)

Amplitude according to the location of the ion strike

Circuit impulse rtesponse: willi flip? Will it remain stable? Single Event Upset **Single Event rate**

"

BL

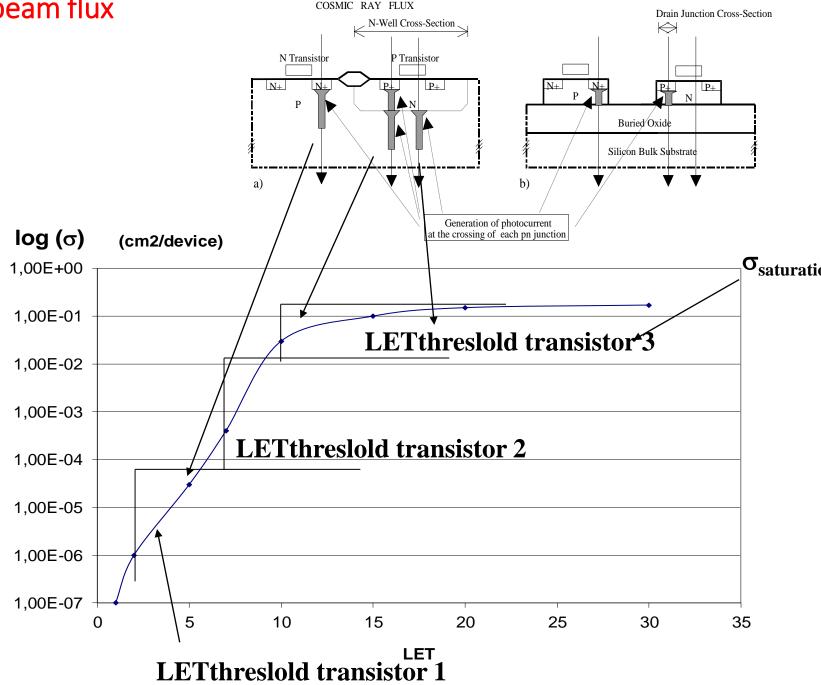

#### Metric is generally related to the beam flux and ionizing particle dE/dx (LET Linear Energy Threshold)

Graph is build up with a succession

of experiments or simulations

(single isotope beamand monoenergetic Energy)

<mark>At each step</mark>

$\sigma_{\text{SEE}}$  (LET)=  $N_{\text{event}} / \phi_{\text{flux (energy E)}}$ In case of a spectrum one expects  $N_{\text{event}} = \int \sigma_{\text{SEE}}$  (LET)  $\phi_{\text{differential flux}} d\text{LET}$

NOTE that  $\sigma_{SEE}$  is a complex mix of nuclear cross section  $\sigma_{nuc}$  and of circuit response with a threshold on the delivered ionization

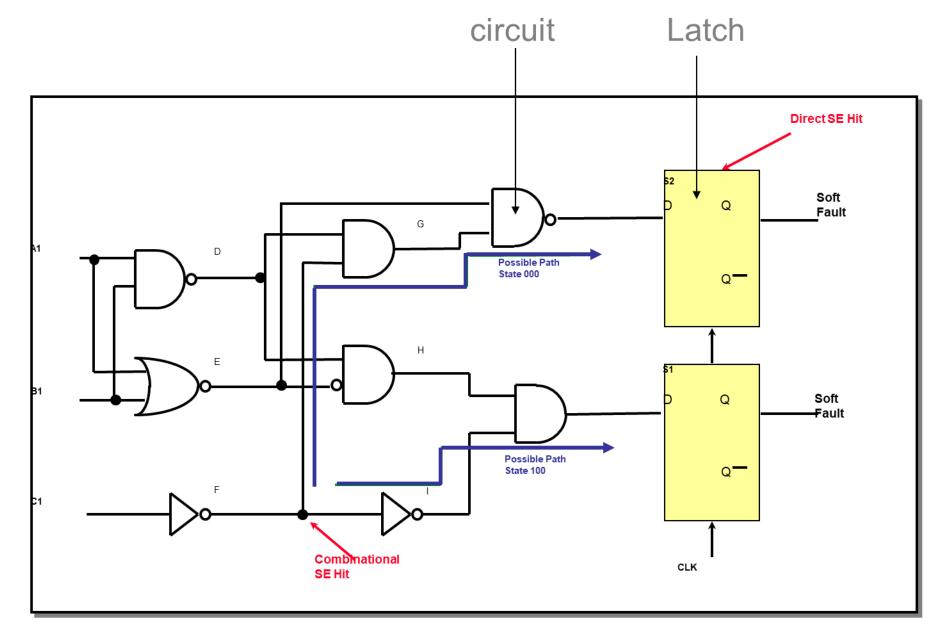

#### Single Event Transient Propagation vs Masking

#### Single Event Rate.

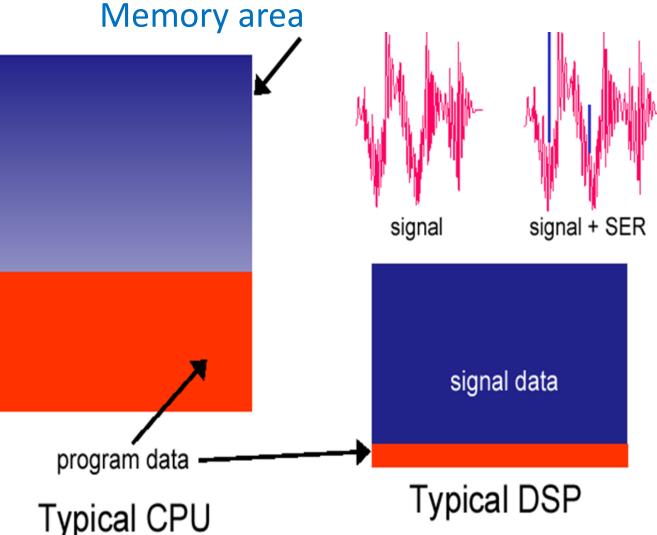

CPU, DSP, ADC, etc... differ An issue for radiation testing standardization. A matter of reserch papers. Memory

« test as you run it » ?

Test standards references at the end of the talk

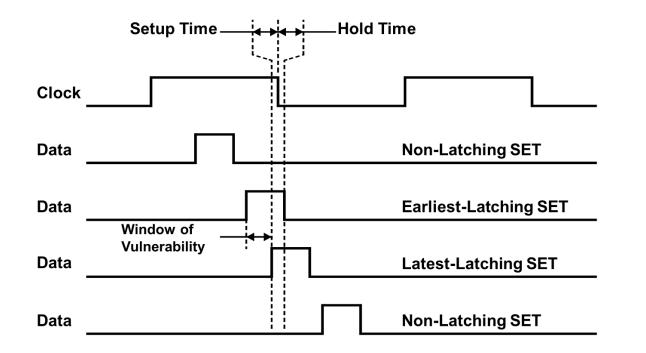

## Window of vulnerability

## a linear dependence is observed of the Single Event Rate with the clock frequency

Clock rate increase makes the transient capture more probable during the setup and hold time

## Lets go back to Electronics scaling in DIGITAL CIRCUITS LET's have a look at SRAMS, used in Cache and some FPGA, etc...

• In SRAM, bit-flip can occur if the transient meets the feed back condition.

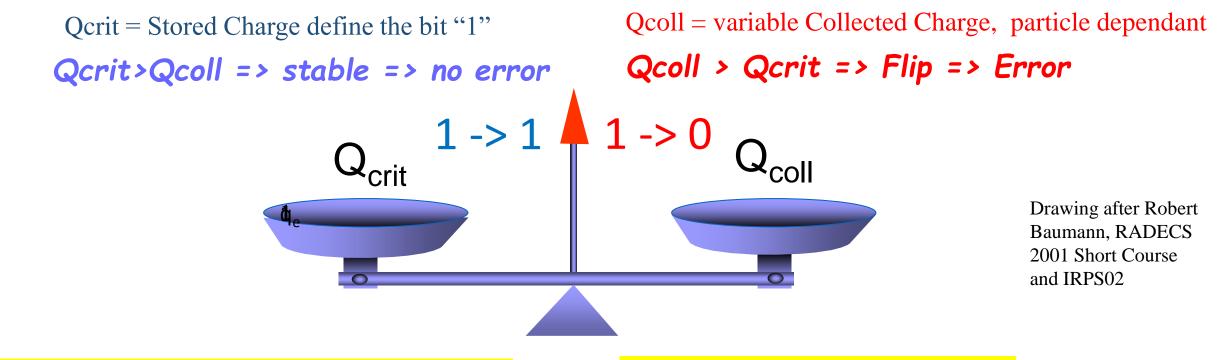

• Data is corrupted if Qinjected > Qstored

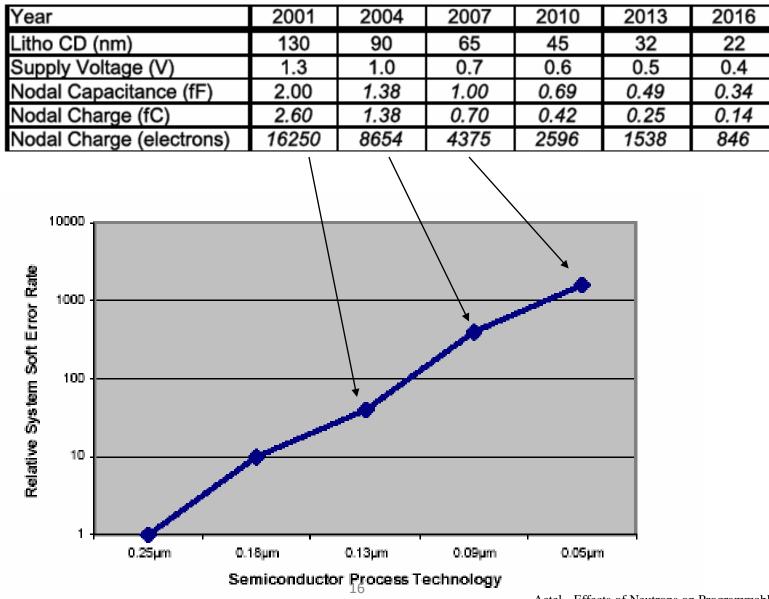

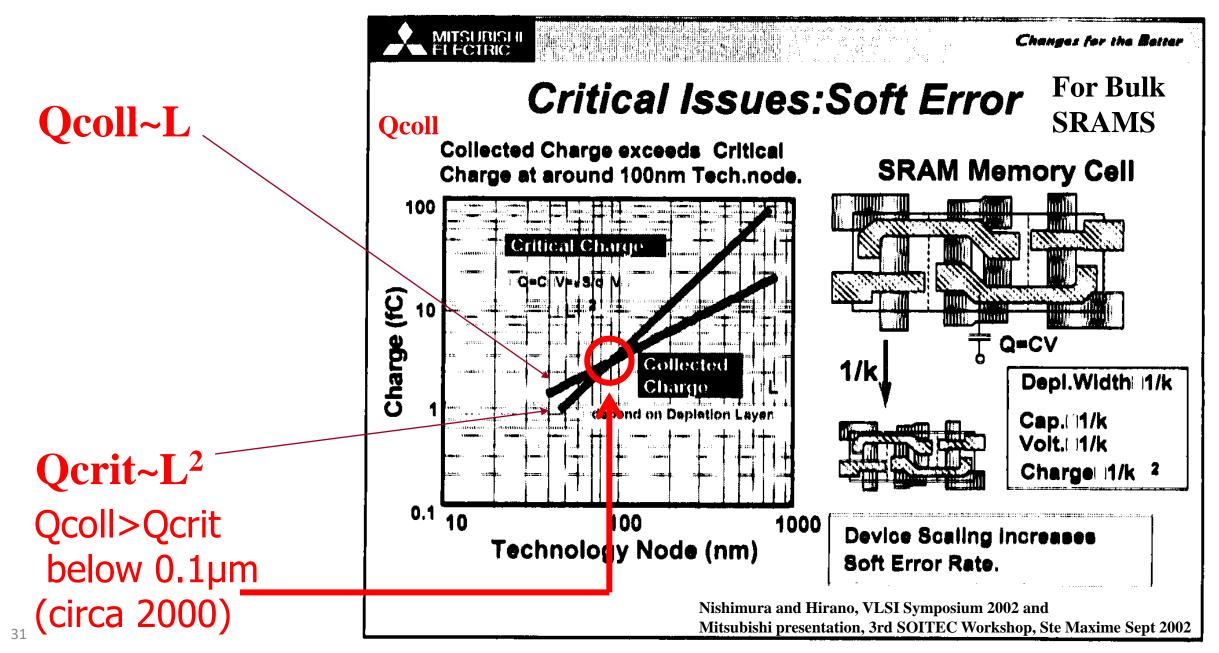

## A clever remark (2002): A transition between 0.25µm and 0.1µm technology Nodes

# We shall illustrate this using a simple "STATIC" model

Single Event Upset at an electrical node in a SRAM or a DRAM

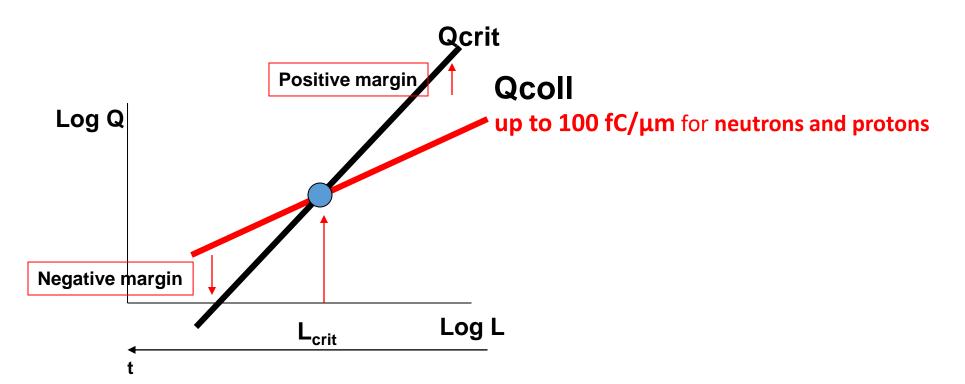

### <mark>Qcrit ~ C V ~ (ε) (W.L) / t ~ (ε) (L<sup>2</sup>) / t</mark>

= Stored charge on all the capacitances (

- V = Supply voltage of the cell t, equivalent thickness of materials

- $\epsilon$ , weighted dielectric constant (Si, SiO2) in the cell

## Qcoll ~ (q<sub>e</sub>/ w) (dE/dx) (L<sup>1</sup>)

L = Collection Length by drift and diffusion

- $q_e$  = electron charge

- w = ionization yield of the cell as a radiation detector(PN junctions and transistors=

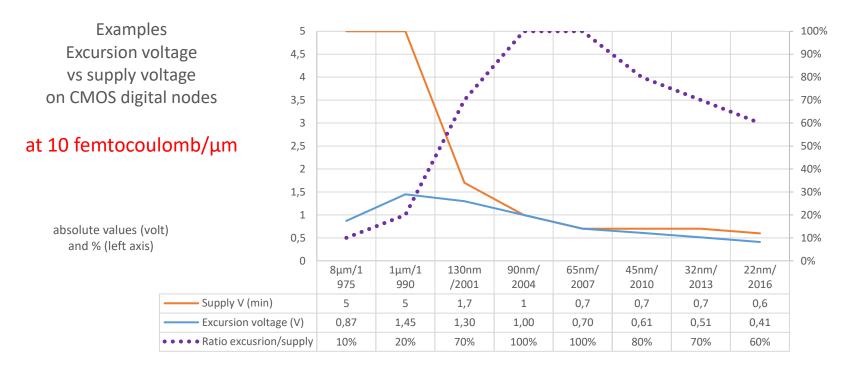

# Consequence of scaling

| Year                     | 2001  | 2004 | 2007 | 2010 | 2013 | 2016 |

|--------------------------|-------|------|------|------|------|------|

| Litho CD (nm)            | 130   | 90   | 65   | 45   | 32   | 22   |

| Supply Voltage (V)       | 1.3   | 1.0  | 0.7  | 0.6  | 0.5  | 0.4  |

| Nodal Capacitance (fF)   | 2.00  | 1.38 | 1.00 | 0.69 | 0.49 | 0.34 |

| Nodal Charge (fC)        | 2.60  | 1.38 | 0.70 | 0.42 | 0.25 | 0.14 |

| Nodal Charge (electrons) | 16250 | 8654 | 4375 | 2596 | 1538 | 846  |

Any SRAM (cache), Registers sensitivity, DRAM (main memory, dramatically evoved with characteristic length of CMOS (Lgate, e.g.)

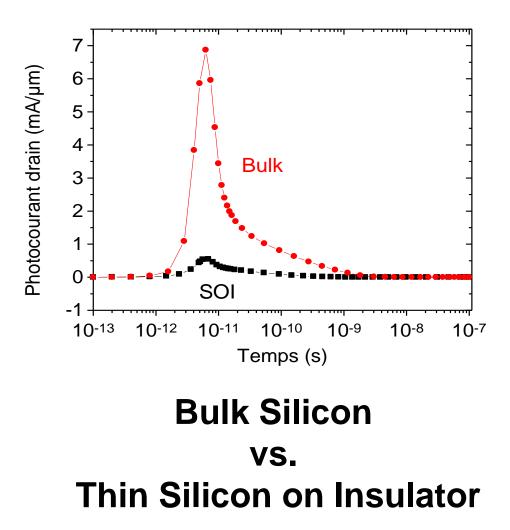

## Basic of Neutron Effect => REMAIN THE SAME on Silicon for a neutron, dE/dx remains the same! REGARDLESS OF THE TECHNOLOGY NODE

#### Neutron => Silicon Recoil Range = 10µm

Reaction table from F. Wrobel et al., IEEE Trans. Nucl. Phys., Vol. 47, No. 6, Dec. 2000 Application

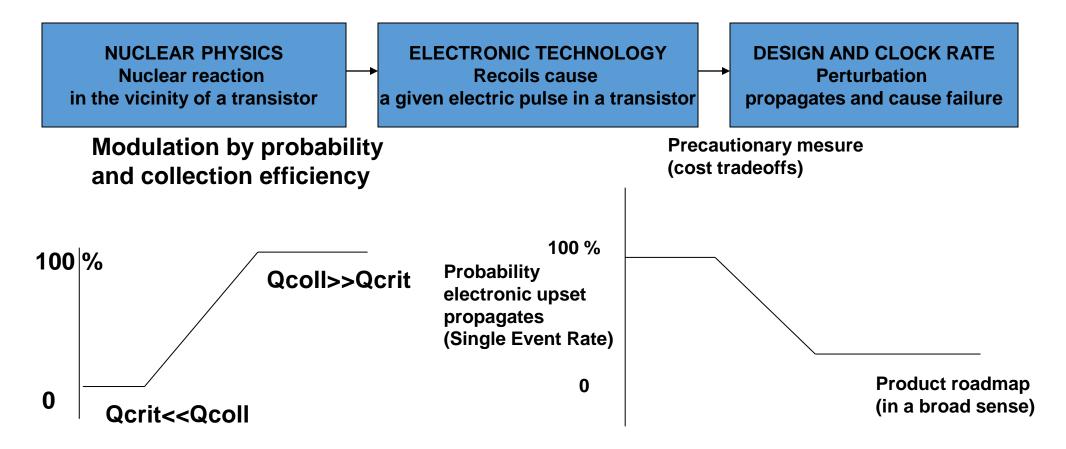

- •Qcrit~ CV ~  $\varepsilon_{ox}$ S/t<sub>ox</sub> V ~ L<sup>2</sup>

- •Qcoll~ Diffusion length (or chord length) ~ L

True for a given type of technology (SOI, doping...)

and design (transistor and circuitry surfaces)

=> Differs from manufacturer to another

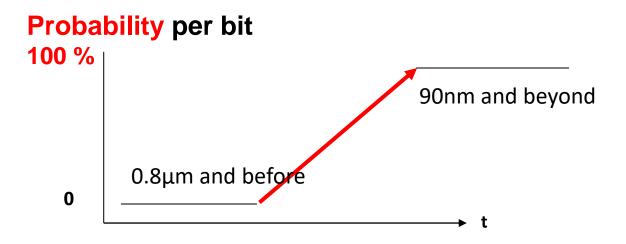

## Since digital node ~1 micron and below (~1990) All digital curcuits became prone to upset

| Year                     | 2001  | 2004 | 2007 | 2010 | 2013 | 2016 |

|--------------------------|-------|------|------|------|------|------|

| Litho CD (nm)            | 130   | 90   | 65   | 45   | 32   | 22   |

| Supply Voltage (V)       | 1.3   | 1.0  | 0.7  | 0.6  | 0.5  | 0.4  |

| Nodal Capacitance (fF)   | 2.00  | 1.38 | 1.00 | 0.69 | 0.49 | 0.34 |

| Nodal Charge (fC)        | 2.60  | 1.38 | 0.70 | 0.42 | 0.25 | 0.14 |

| Nodal Charge (electrons) | 16250 | 8654 | 4375 | 2596 | 1538 | 846  |

Conclusion 1 After 0.5µm and downward any technology became vulnerable

As remarked by many workers, SRAM Sensitivity per bit stabilizes

But Megabit, Giga, Terabit size increases

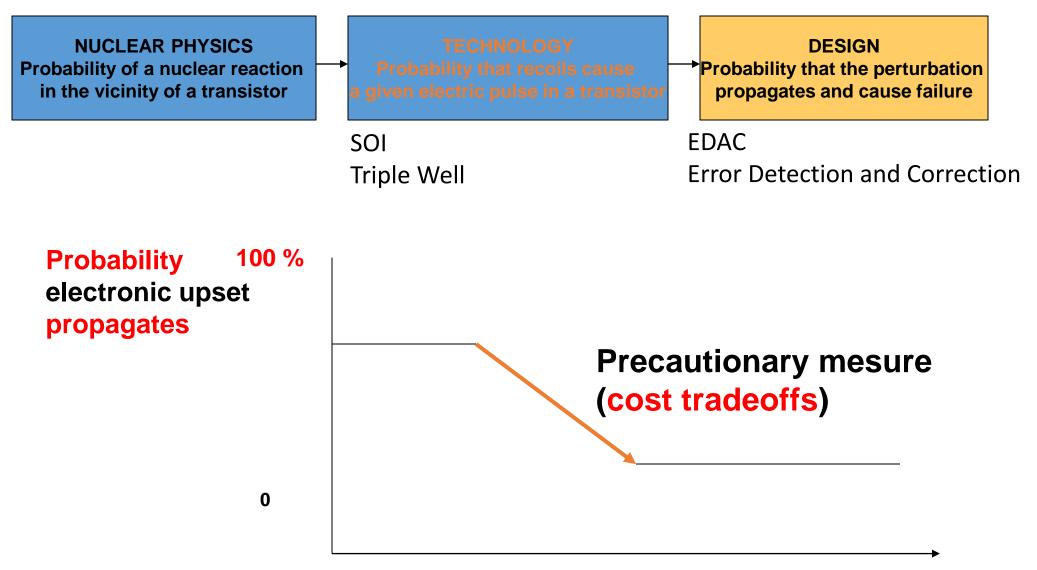

# **Mitigations Issues and methods**

Product roadmap (in a broad sense)

## Conclusion 2. Mitigation Chain: A Multi-Scale Effort

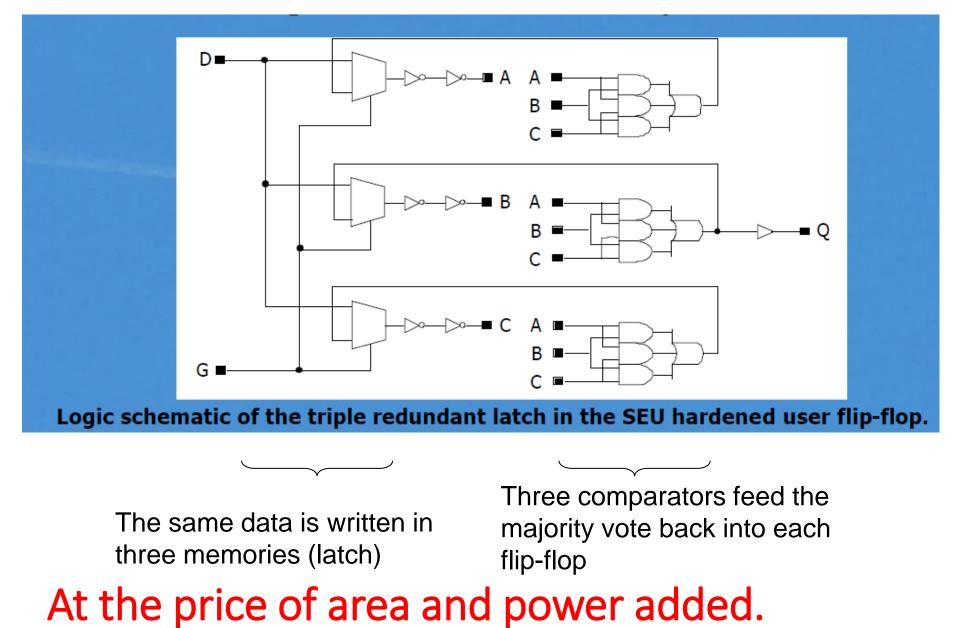

# Many scheme of EDAC. Eg, for a flip-flop

### Atmospheric neutrons effects Wrap-Up and Documentation .

- Upset Rate increases for three causes:

- Information and data more sensitive:

- Critical Charge downscaling according to Moore's Trend and I.T. progresses

- Frequency increase

- System complexity upscaling

- Protective circuit at low design level only and cumbersome

- To know more

- Flash-based FPGAs in space, design guidelines and trade-off for critical Applications

- "Soft Errors From Particles to Circuits, Jean-Luc Autran and Daniella Monteanu", CRC Press, 2015

- Robert Baumann, Consultant, Radiosity Inc https://radiositysolutions.com/, in several IEEE Nuclear and Space Radiation Effects Conference Short Courses, eg "Landmarks in Terrestrial Single-Event Effects", Invited Talk, Invited Short-Course, NSREC 2013

#### Some Standardization and Methods

• Gound level, Manufacturers:

JEDEC Test Specification JESD-89 issued 2001, updated 2006, 2021 "Measurement and Reporting Of Alpha Particle and Terrestrial Cosmic Ray Induced Soft Errors in Semiconductor Devices"

JESD89-1B "TEST METHOD FOR REAL-TIME SOFT ERROR RATE"

• Atmospheric, avionics:

IEC TC107 – 62396 TS – 2004 "STANDARD FOR THE ACCOMODATION OF ATMOSPHERIC RADIATION EFFECTS VIA SINGLE EVENT EFFECTS WITHIN AVIONICS EQUIPMENTS"

• Space Electronics:

ESA "SCC basic specification no 22900", issue 4, April 1995 and seq.

# Conclusions and some thoughts (Single Event Effects)

- Radiation Single Event Transient is a sort of 'back-door' command with risk of malfunction or hard failure.

- 2. The chip or circuit behavior is a category of a Real Time issue in an asynchronous mode:

- Single Event Transient randomly occurs out of order at any time and node in the 'space of configuration' of the 'machine'.

- And only the design team or house knows the precise chip layout and has a model of 'machine.

- It is hard to find a worst case and test strategy is cornerstone.

- 3. At several circuit and system levels, the best is to include a 'design for testability', and a 'hardening by design'.

- 4. Radiation effects on circuit and system are rather a mystery, but the firm grounds are in physics.

Knowledge can be shared by convergence of interest in physics, technology and real-time

- Reliability and safety in Space Electronics and Transportation industries

- Dependability and performance in Research Physics Instrumentation (Experimental Astrophysics and and High Energy Colliders)

- Emerging large facilities for Fusion Research Reactors (a lot of electronics involved in the plasma diagnistics and command control).

- Limited design approaches Test standards exist in some of these areas: Avionics, Space Electronics