## 3D-Double-side Double-Type Column detector status at FBK

#### <u>E.Vianello<sup>b</sup></u>, <u>G. Giacomini<sup>b</sup></u>, A. Bagolini<sup>b</sup>, M. Boscardin<sup>b</sup>, L. Bosisio<sup>c</sup>, G.-F. Dalla Betta<sup>a</sup>, C. Piemonte<sup>b</sup>, M. Povoli<sup>a</sup>, N. Zorzi<sup>b</sup>

<sup>a</sup> INFN and University of Trento, 38123 Povo di Trento (TN), Italy

<sup>b</sup> Fondazione Bruno Kessler (FBK-irst), 38123 Povo di Trento, Italy

<sup>c</sup> INFN and University of Trieste, 34127 Trieste, Italy

## Outline

- Introduction

- •3D DDTC detectors (non passing through columns)

- •3D-DDTC<sup>+</sup> (passing through columns)

- -Technology

- -Preliminary results

- Conclusions

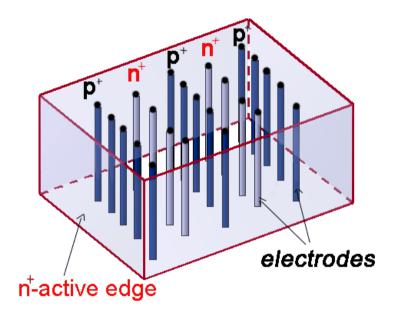

## 3D detectors – state of the art

First proposed by S. Parker et. al. in NIMA 395 (1997), 328

Best result: 66% of the original signal after 8.8x10<sup>15</sup> cm<sup>-2</sup> 1-MeV n<sub>eq.</sub> fluence

C. Da Via et. al. NIMA 604 (2009) 504

#### **ADVANTAGES:**

- Electrode distance and substrate thickness decoupled:

- low depletion voltage

- high speed

- good charge collection efficiency

→ High radiation hardness

-Active edges:

- Dead area reduced up to few microns from the edge

#### **DISADVANTAGES:**

- Non uniform response due to electrodes

- Complicated technology

- Higher capacitance with respect to planar

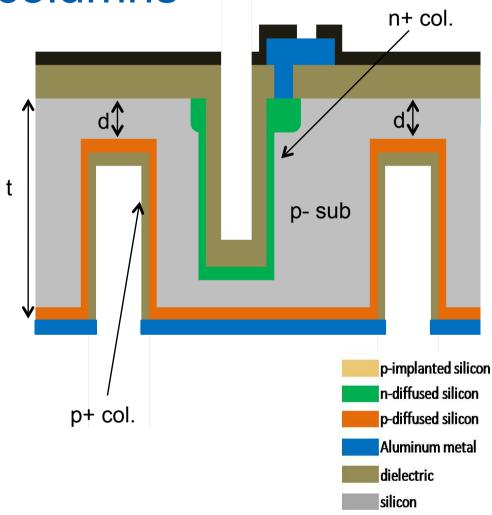

# 3D-DDTC with non passing through columns

#### SIMPLIFIED FABRICATION PROCESS

- columns stop at a distance d from the opposite surface

- no support wafers

- double-sided process

- holes (~10 μm diam.) are

"empty" (no poly-Si)

PECVD overglass

# 3D-DDTC with non passing through columns: pros and con

- fabrication process reasonably simple

- good process yield

- even with non optimized gap "d", good performance up to irradiation fluence of  $10^{15} n_{eq}/cm^2$

- column depth difficult to control and to reproduce

- insufficient performance after very large irradiation fluences if "d" is too large

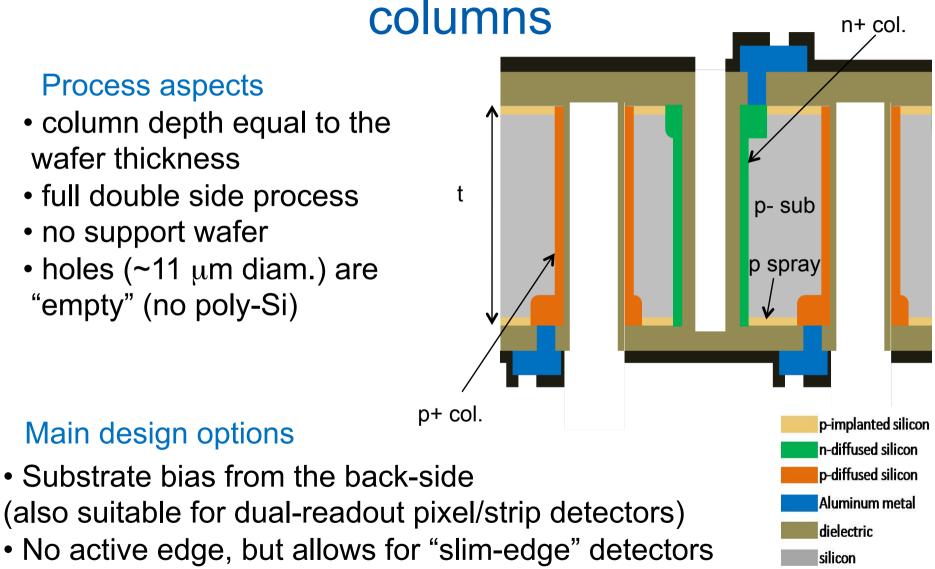

Modified 3D-DDTC process with passing through columns

## **3D-DDTC** with passing through columns

#### **Process aspects**

- column depth equal to the wafer thickness

- full double side process

- no support wafer

Main design options

• holes (~11  $\mu$ m diam.) are "empty" (no poly-Si)

PECVD overglass

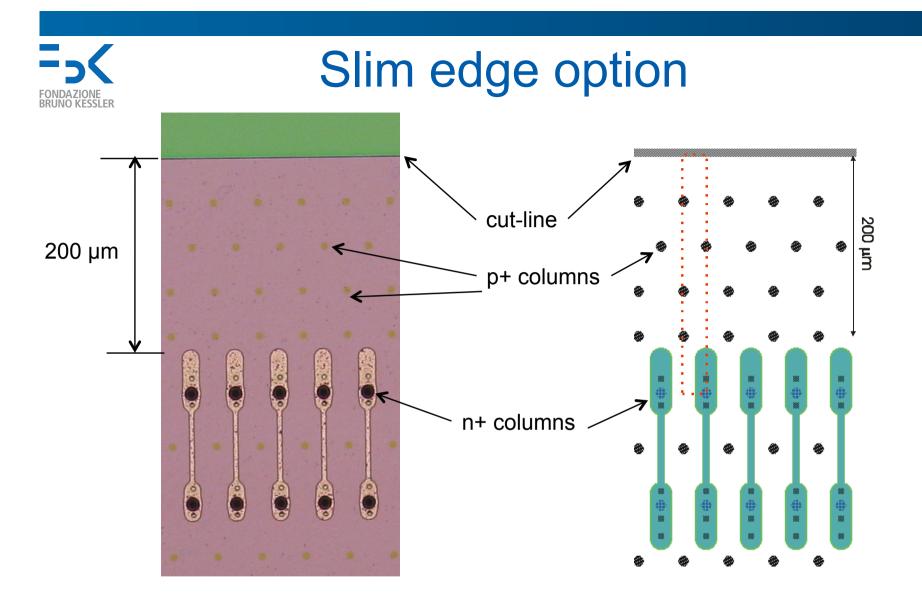

Technology of choice at FBK for ATLAS IBL prototypes

- multiple Ohmic fence termination

- dead area ~ 200  $\mu m$

- no leakage current drawn from highly damaged cut region

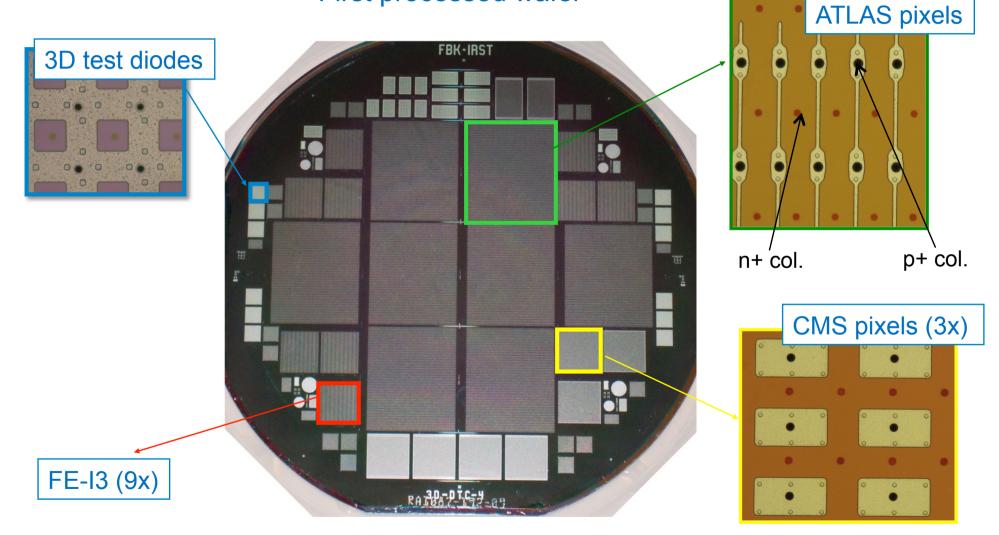

## **3D-DTC-4** some pictures

FE-I4 (8x)

#### First processed wafer

## Future technological developments

- •We have 10 wafers almost ready for the electrical characterization (at the metal back)

- Process steps developments: new DRIE recipes for holes with higher aspect ratio, p-spray optimization, poly-Si filling of the holes

- •Development of 3D detectors with passing through columns and active edge (with support wafer)

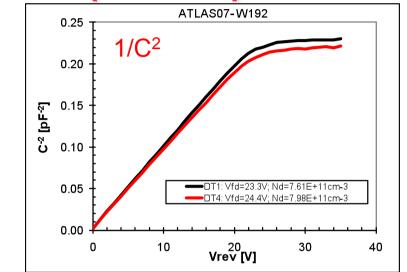

## 3D-DTC-4: preliminary results (1) Planar test diodes (4 mm<sup>2</sup>)

- $J_{lk} \sim 500 \text{ nA/cm}^2$  (higher than usual)

- V<sub>BD</sub>~ 40-50V (p-spray)

- Vdepl ~20 V  $\rightarrow \rho$  ~ 16 k $\Omega$ ·cm

- Surface parameters ok:

```

s_0=10-30 cm/s, N_{ox}=2-6x10^{11} cm<sup>-2</sup>

```

#### p-spray optimization studies

Test batches of planar structures processed in parallel to 3D batches and using the same thermal budget

• Optimized p-spray doping profile and layout being investigated

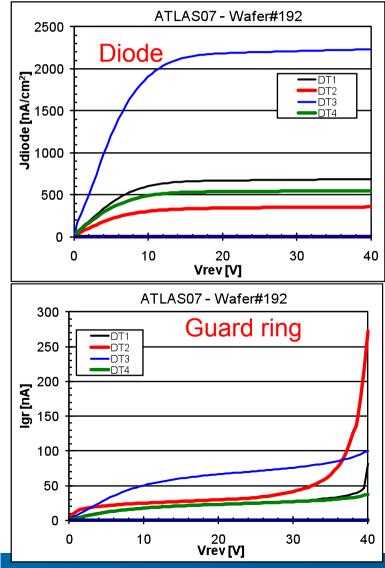

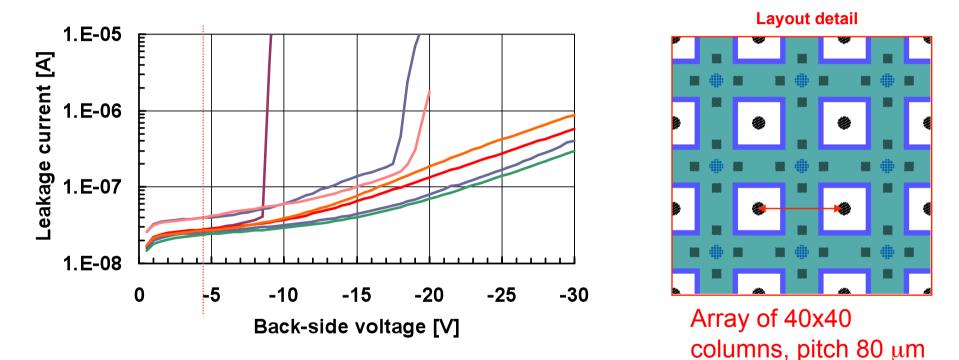

### 3D-DTC-4: preliminary results (2) 3D test diodes (~10mm<sup>2</sup>), I-V curves

- J<sub>lk</sub>~330 nA/cm<sup>2</sup> (~20 pA/col.) at V<sub>depl</sub> (comparable to planar diodes)

- Leakage not degraded from DRIE but likely from mechanical stress

- Intrinsic breakdown (p-spray) + early breakdown due to defects

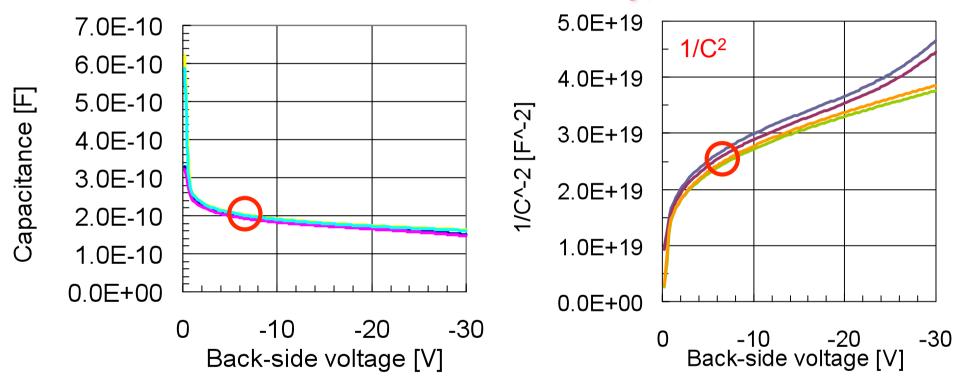

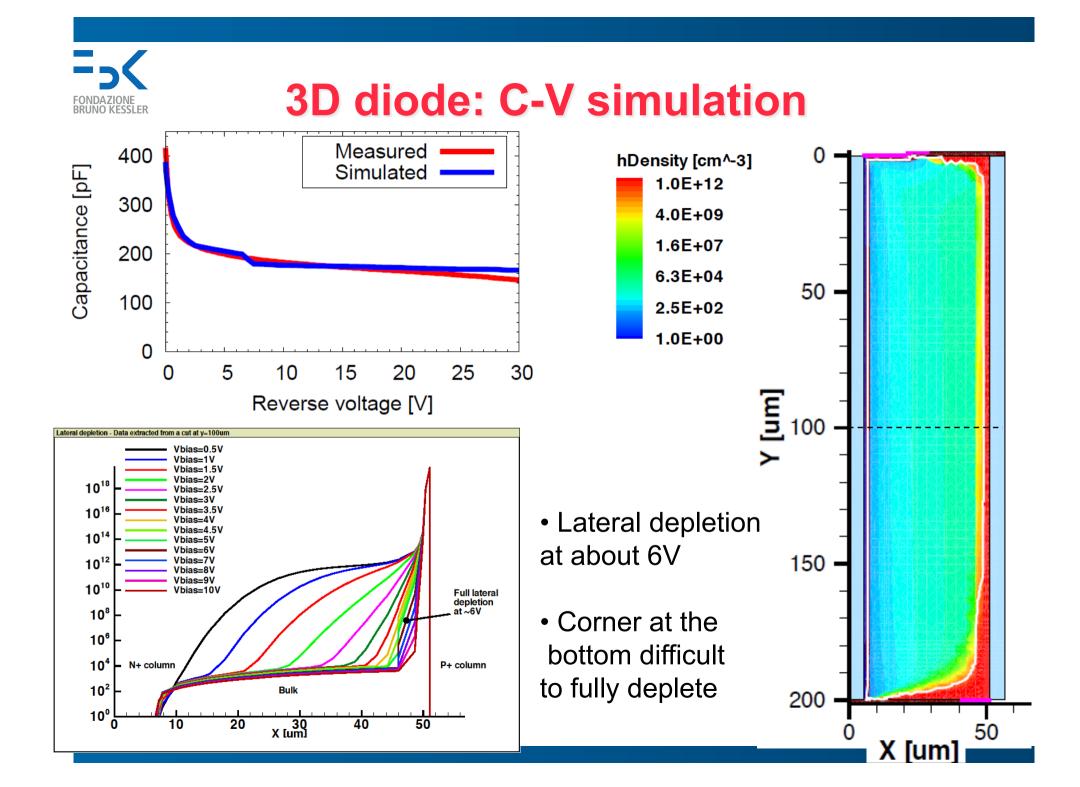

### 3D-DTC-4: preliminary results (3) 3D test diodes (~10 mm<sup>2</sup>), C-V curves

- Capacitance ~200pF (125 fF/col.) at V<sub>depl</sub>

- Non negligible contribution from surface (p-spray)

- Depletion at a few V (see next slide)

## Conclusions

- The development of 3D detector technologies at FBK-irst is proceeding with encouraging results

- •To further improve performance and process reproducibility, 3D-DDTC<sup>+</sup> detectors (with "passing through" columns) have been developed and preliminary results have been reported

- More wafers to come in a few weeks with an optimized fabrication process which improve electrical parameters

#### 6<sup>th</sup> "Trento" Workshop on Advanced Silicon Radiation Detectors (3D and P-type Technologies)

FBK – irst, Trento, Italy March 2-4, 2011

#### **TOPICS:**

Design and simulation

Fabrication Technologies

Radiation Hardness

Read-Out

Applications

Organizing Committee:

M. Boscardin, C. Piemonte | FBK-irst, Italy G.-F. Dalla Betta | Univ. Trento, Italy H.F.-W. Sadrozinski | SCIPP, UCSC, USA G. Casse | Univ. Liverpool, UK Y. Unno | KEK, Japan