# Edge-TCT evaluation of High Voltage-CMOS test structures with unprecedented breakdown voltage for high radiation tolerance

Benjamin Wade\*, Matthew Franks, Jan Hammerich, Nissar Karim, Samuel Powell, Eva Vilella Figueras, Chenfan Zhang

\* bwade@hep.ph.liv.ac.uk University of Liverpool, Department of Physics

UNIVERSITY OF LIVERPOOL UK Research and Innovation

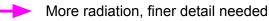

# Trackers

- Collision event generates charged particles

- Charged particles curve in magnetic field

- Tracker follows the path

- Curvature determines charge, mass of particle

Placed close to collision center

High rate of events MHz-GHz rate of bunch crossings

Minimal track disruption

Higher collision energies

Sensors receive high radiation dose

Thin sensors

#### Sensors need to be thin, fast, radiation tolerant, and within budget

DISCLAIMER: I do not work for ATLAS, this is just an example

Run Number: 265545, Event Number: 572035

Date: 2015-05-21 10:39:54 CEST

# **Pixel Sensors**

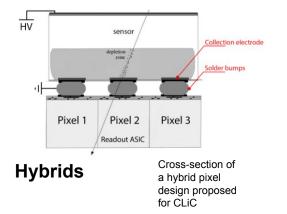

## **External Readout Circuitry:**

Fast readout X Specialised bump-bonding Increases thickness Limits granularity

## Integrated Readout Circuitry:

- Thin sensors

- Industrial standard

- Cost effective

### **HV-CMOS**

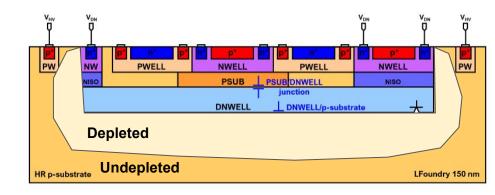

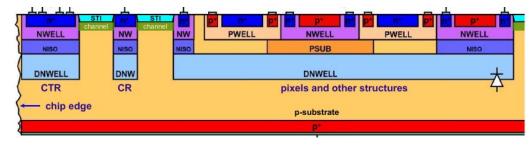

Cross-section of a typical HV-CMOS pixel

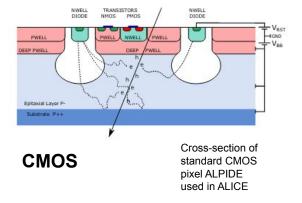

## Integrated Readout Circuitry:

- Thin sensors

- Industrial standard

- Cost effective

#### High Voltage Pixel:

- ✓ More radiation tolerant

- Fast charge collection (Drift)

## Low Voltage Pixel:

X Less radiation tolerant X Slow charge collection (Diffusion)

## High Voltage Pixel:

- More radiation tolerant

- Fast charge collection (Drift)

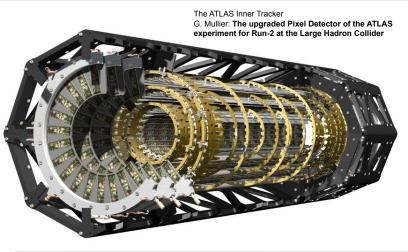

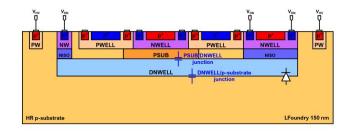

# **Future Requirements**

| Industrial Star<br>Manufacturing |                     | No specialis processes            | No specialised (expensive)<br>processes                                    |  |           | V <sub>SN</sub><br>D<br>NW<br>NISO | P DIVELL<br>PSUB PSUB DNWELL<br>DNWELL DNWELL<br>DNWELL UNCT |   |                                                              |

|----------------------------------|---------------------|-----------------------------------|----------------------------------------------------------------------------|--|-----------|------------------------------------|--------------------------------------------------------------|---|--------------------------------------------------------------|

| High Voltage                     |                     |                                   | Radiation tolerant,<br>Fast time resolution                                |  | HR p-subs | itrate                             | , jano                                                       | T | oundry 150 nm                                                |

| Monolithic                       |                     | - Thin                            |                                                                            |  |           |                                    |                                                              |   |                                                              |

|                                  | Pixel Size<br>(µm²) | System Time<br>Resolution<br>(ns) | Radiation Tolerand<br>(NIEL)<br>(1 MeV n <sub>eq</sub> cm <sup>-2</sup> Ye |  |           |                                    |                                                              |   |                                                              |

| HL-LHC                           | 50 x 50             | 0.03                              | 10 <sup>16</sup>                                                           |  |           | Geneva                             | Future                                                       |   |                                                              |

| FCC-hh                           | 25 x 50             | 0.1                               | 10 <sup>16</sup> to 10 <sup>17</sup>                                       |  |           | PS<br>CDE                          | Circular<br>Collider                                         |   |                                                              |

| Current<br>HV-CMOS               | 50 x 50             | 3.16                              | 10 <sup>15</sup>                                                           |  |           | LHC<br>27 km                       | 100 km                                                       |   | Gogli Errit<br>Hogo 2.241 Specificar<br>Bog to day Coginison |

Future tracking detector specifications, and current HV-CMOS capabilities

https://cds.cern.ch/record/2653532/files/FCC%20v2.jp g?subformat=icon-1440

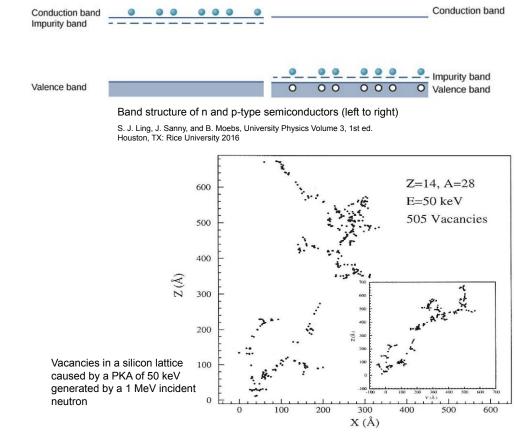

## Bulk Damage: Non Ionising Energy Loss (NIEL)

Incident radiation knocks an atom out of the lattice, Primary Knock-on Atom (PKA)

- Atom travels knocking more atoms out of the lattice, interstitial-vacancy pairs (Frenkel Pairs)

- Damage introduces acceptor removal, energy levels in the band structure, and charge traps

- Changes doping profile and resistivity

F. H onniger, "Radiation damage in silicon. defect analysis and detector properties", 2008.

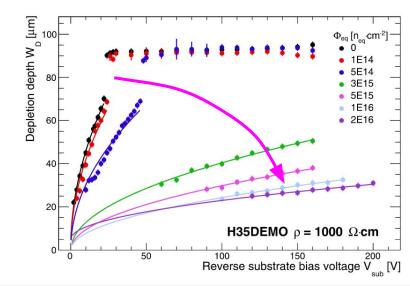

# **Sensing Region**

- Sensing diode increases depletion region with negative biases until diode breaks down

- NIEL reduces depletion region ability to grow

- Counteracted by increasing bias voltage

- more room for growth

- Increases charge collection speed

- Charge traps less effective

$$W = W_0 + \sqrt{\frac{2\epsilon_r\epsilon_0}{qN_A}V_{bias}}$$

- W = Depletion depth of semiconductor

- $W_0$  = Depletion depth at 0 V

- $\epsilon_r = \text{Relative permittivity of silicon}$

- $\epsilon_0$  = Permittivity of free space

- q = Charge of an electron

- $N_A$  = Doping concentration of acceptor atoms

- $V_{bias}$  = Reverse bias voltage

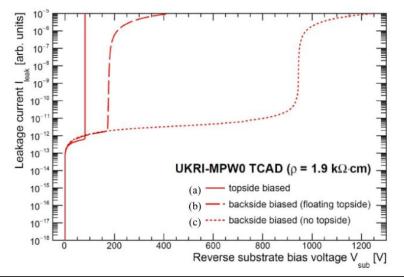

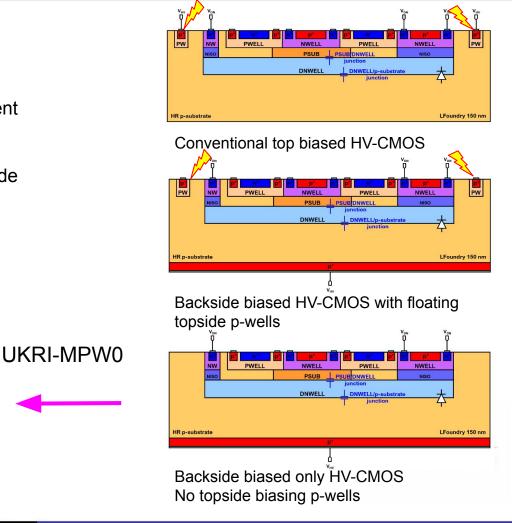

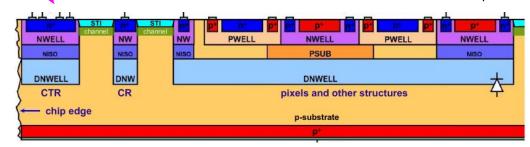

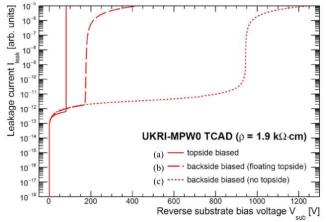

# **Biasing Scheme**

- Increase breakdown voltage

- Top side p-well identifies as low resistivity current path, reduces breakdown

- Simulation show no topside p-wells and backside biasing improves breakdown ~ 1000 V

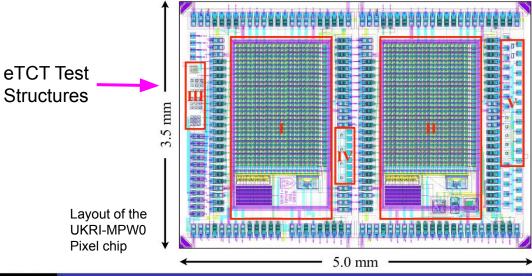

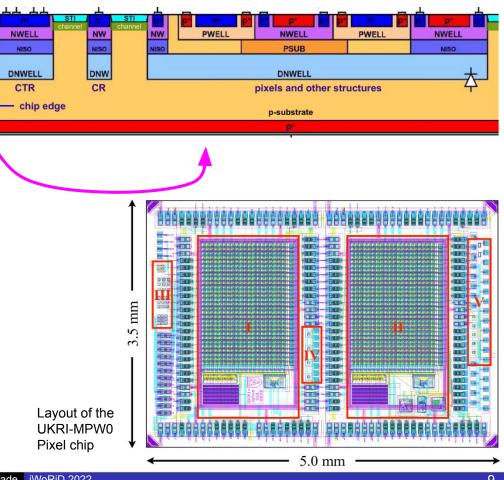

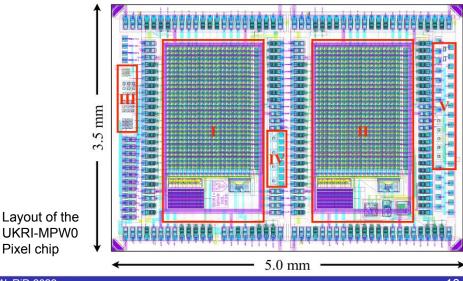

# **UKRI-MPW0**

Cross-section of UKRI-MPW0 pixel

- LFoundry 150 nm, HV-CMOS

- 1.9 kΩ cm Substrate Resistivity

- Thinned to 280 µm thickness before backside processing

- Fully backside biased only

- 2 Backside Processing Methods (IBS)

- Current Terminating Ring (dn-well)

- 2 Matrices of 20 x 29 Pixels

- 60 x 60 µm<sup>2</sup> Pixel Size

- 3 Sets of Test Matrices

(3 x 3 Passive pixels for eTCT)

# Backside Processing Method

- Backside processing provided by Ion Beam Service (IBS)

- 2 Processing methods offered

- Beamline Ion Implantation + Rapid Thermal Annealing

Experience with processing method Potential damage to readout electronics Doesn't fully anneal boron implantation damage

Plasma-Immersion Ion Implantation + UV Laser Annealing

More defined doping profile Targeted annealing has minimal damage to rest of the chip

Cross-section of

**UKRI-MPW0** pixel

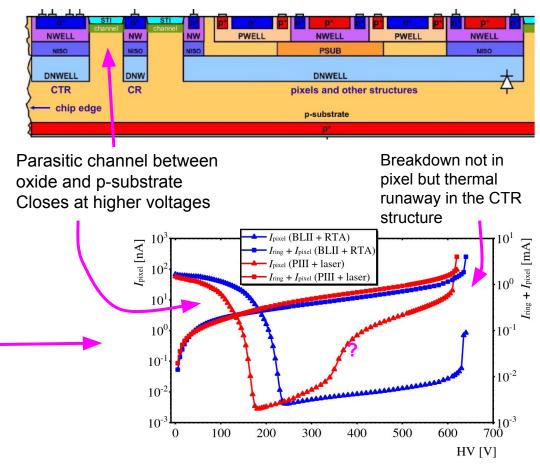

Current Terminating Ring (CTR)

- Deep n-well ring structure, unconventional (No topside p-well)

- Increase fill factor (avoid multiple rings)

- Shorted to guard-ring

- High leakage current from edge of chip (~ 4 mA)

- Breakdown voltage limited by current through CTR metal

- Low pixel leakage current

Cross-section of

**UKRI-MPW0** pixel

## "Breakdown"

# Cross-section of UKRI-MPW0 pixel

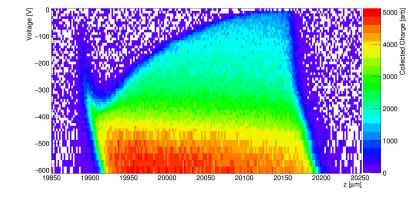

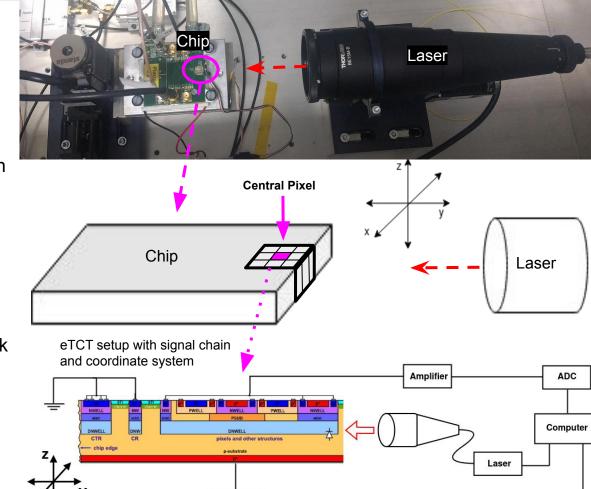

# eTCT

- IR laser penetrates silicon

- Induces signal at focal point

- Used to map charge collection region

- Records the collected charge with a laser at a specific point

- Cooled to -20 °C temperature

- IR laser, 1 kHz firing

- 200 ns waveforms

- 2 GHz oscilloscope sample rate

- 10 ns integration around current peak

HV

Benjamin Wade iWoRiD 2022

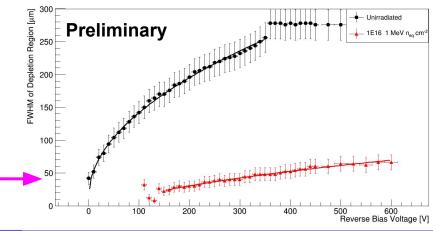

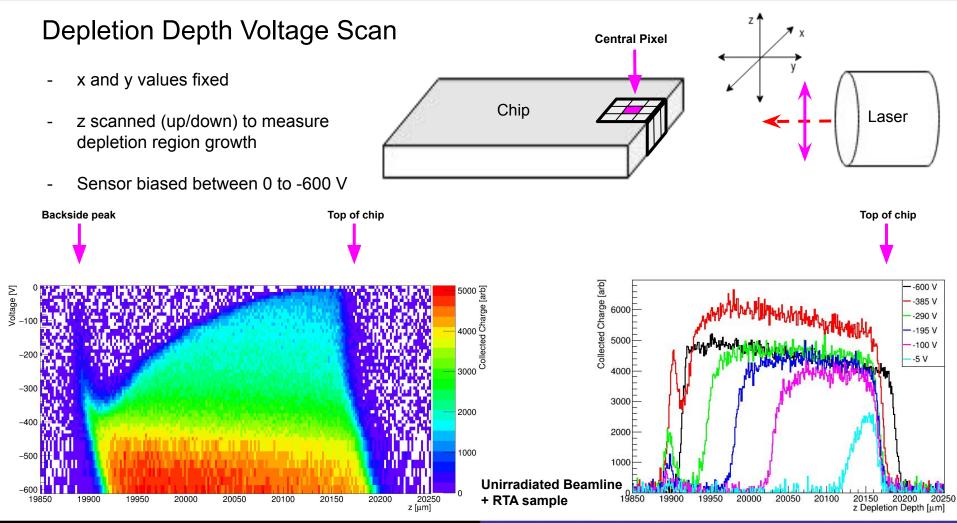

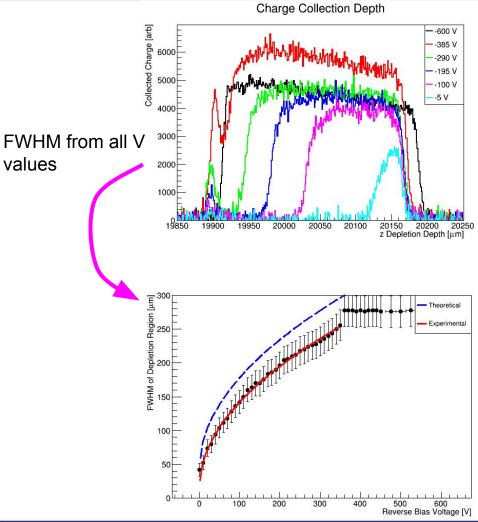

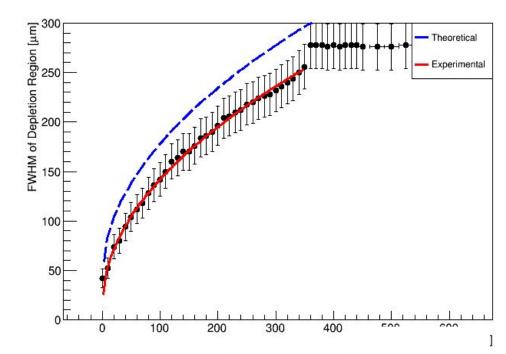

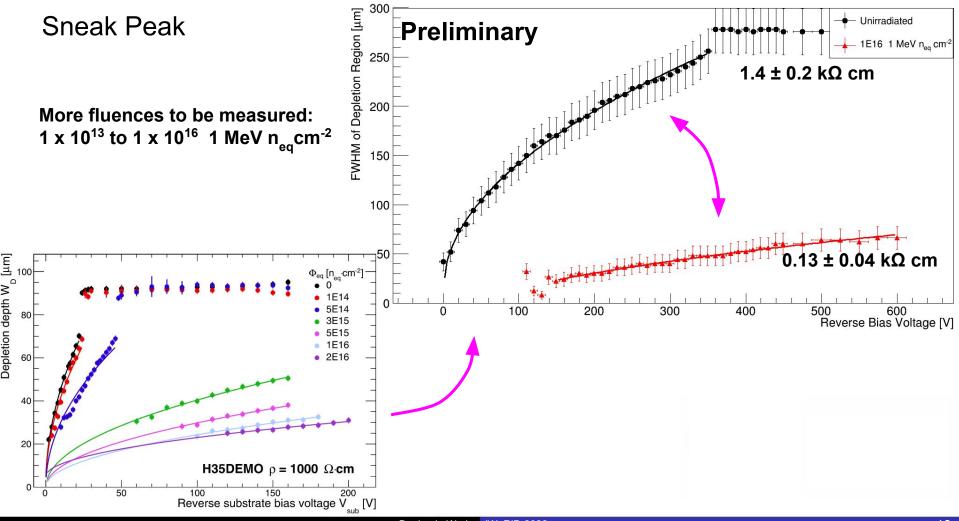

## **Depletion Depth**

- FWHM of collected charge found for the region at each Voltage

- Substrate resistivity and doping concentration calculated from fit

$$W = W_0 + \sqrt{\frac{2\epsilon_r \epsilon_0}{qN_A} V_{bias}}$$

- W = Depletion depth of semiconductor

- $W_0$  = Depletion depth at 0 V

- $\epsilon_r$  = Relative permittivity of silicon

- $\epsilon_0$  = Permittivity of free space

- q = Charge of an electron

- $N_A$  = Doping concentration of acceptor atoms

- $V_{bias}$  = Reverse bias voltage

## Substrate Resistivity

- Unirradiated Beamline Ion Implantation + Rapid Thermal annealing sample measured

- Fit shows resistivity less than nominal

- Inline with RD50-MPW1 with 1.9  $k\Omega$  cm

|                                                   | Resistivity<br>(kΩ cm) |

|---------------------------------------------------|------------------------|

| UKRI-MPW0 Nominal                                 | 1.9                    |

| UKRI-MPW0 Experimental                            | 1.4 ± 0.2              |

| RD50-MPW1 Experimental (same nominal resistivity) | 1.3                    |

## **Conclusion & Outlook**

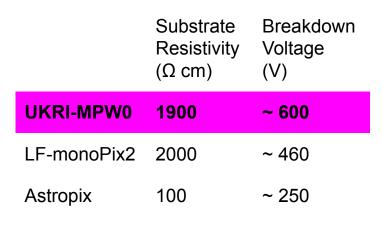

- 600 V unprecedented breakdown for HV-CMOS pixel

- eTCT measurements starting to arrive

- Start measuring irradiated samples up to 10<sup>16</sup> 1 MeV n<sub>eq</sub> cm<sup>-2</sup>

- Measure samples of other backside processing method

- Start TCAD simulations of UKRI-MPW1

- Improve leakage current

- Remove parasitic channel

- Increase bias voltages

- Improve depletion depth with fluence