Exploration of the TPSCo 65 nm CMOS imaging process for building waferscale, thin and flexible detection layers for the ALICE ITS3

Serhiy Senyukov (IPHC CNRS-IN2P3) for the ALICE ITS project

29 June 2022

### Outline

- ALICE detector LS3 upgrade: from ITS2 to ITS3

- Small bent sensors

- Technology choice for larger sensors

- First submission in TPSCo 65 nm CIS process

- Overview of test results

- Summary and next steps

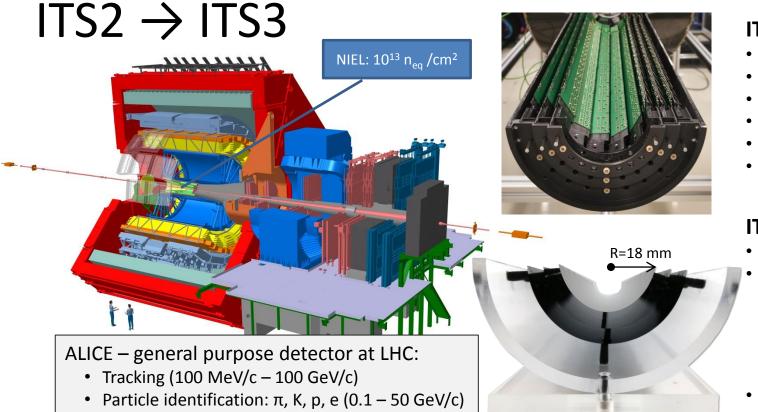

### ALICE detector LS3 upgrade:

#### ITS2: (S.Beolé's talk)

- 7 layers of MAPS

- TJ 180 nm CMOS

- 12.5 Giga pixels

- Pixel size:  $27 \times 29 \ \mu m^2$

- Water cooling

- 0.3 % X<sub>0</sub> / inner layer

#### ITS3:

- 4 outer layers of ITS2

- 3 new fully cylindrical inner layers

- Sensor size up to 27×9 cm

- Thickness 30-40 μm

- No FPCs

- Air cooling in active area

- \* 0.05 %  $X_0$  / inner layer

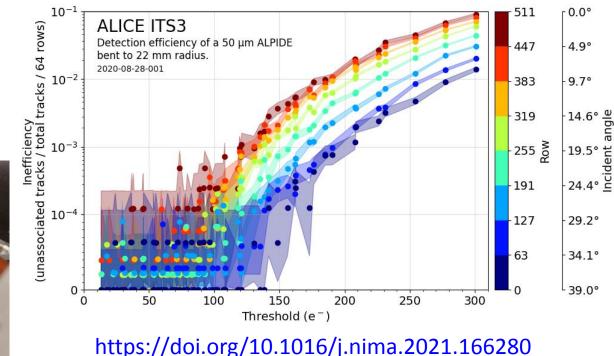

### Small bent sensors work well

50 μm thick ITS2 chip (ALPIDE) bent to 22 mm showed excellent efficiency in the beam test in 2020

### It's time to go bigger (in area): TPSCo 65 nm CMOS IS

- Continuation of the TowerJazz 180 nm (ITS2)

- Provides 2D stitching

- Available on 300 mm wafers  $\rightarrow$  27×9 cm<sup>2</sup> final sensor

- 65 nm  $\rightarrow$  lower power consumption

- 7 metal layers

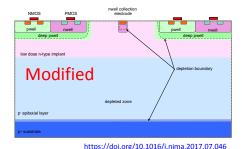

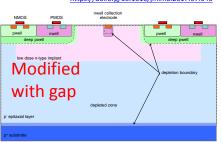

- Process modifications for full depletion:

- Standard (no modifications)

- Modified (low dose n-type implant)

- Modified with gap (low dose n-type implant with gaps)

- 4 process splits:

- 1. Default

- 2. First intermediate optimization

- 3. Second intermediate optimization

- 4. Fully optimized process

https://iopscience.iop.org/article/10.1088/1748-0221/14/05/C05013

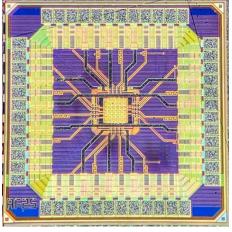

### First test submission: MLR1

- Submitted in December 2020

- Main goals:

- Learn technology features

- Characterize charge collection

- Validate radiation tolerance

- Each reticle (12×16 mm<sup>2</sup>):

- 10 transistor test structures (3×1.5 mm<sup>2</sup>)

- 60 chips (1.5×1.5 mm<sup>2</sup>)

- Analogue blocks

- Digital blocks

- Pixel prototype chips: APTS, CE65, DPTS

- Testing since September 2021

### **APTS: Analogue Pixel Test Structure**

- 6×6 pixel matrix

- Direct analogue readout of central 4×4 submatrix

- Two types of output drivers:

- Traditional source follower (APTS-SF)

- Very fast OpAmp (APTS-OA)

- AC/DC coupling

- 4 pitches: 10, 15, 20, 25 μm

- 3 process variations

- Presented results with <sup>55</sup>Fe source

1.5×1.5 mm<sup>2</sup>

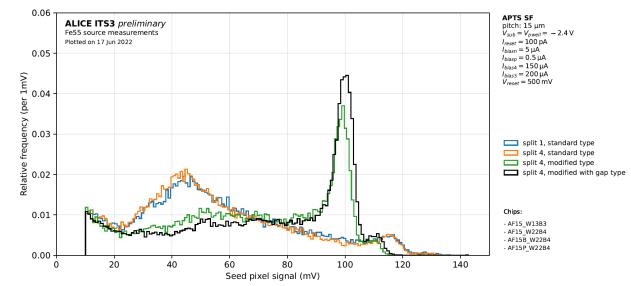

### APTS-SF:

## Process modification reduces charge sharing

- In standard process seed pixel takes ~50% of charge

- In modified process most of the charge is collected in one pixel

Effect on efficiency and spatial resolution to be verified at beam test

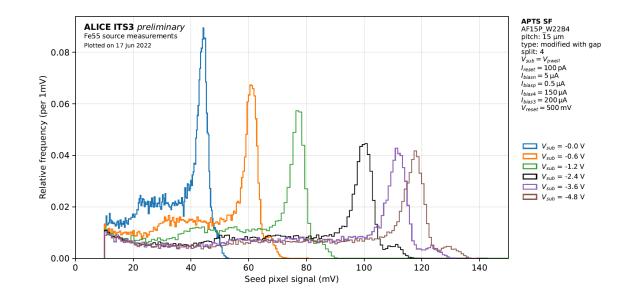

### APTS-SF: Substrate bias amplifies the signal

- Substrate bias lowers the node capacitance to as low as 2.2 fF

- Signal amplitude increases

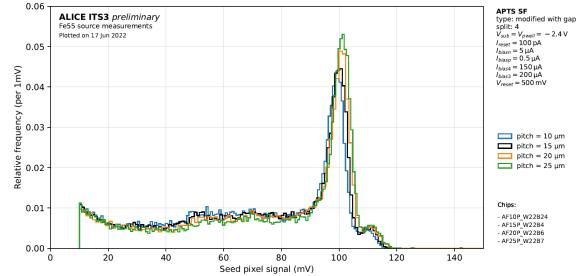

### APTS-SF: Charge collection vs. pixel pitch

- Charge collection efficiency doesn't seem to depend on pixel pitch

- Remarkable result to be confirmed by beam test

- If efficiency stays high at larger pitches -> way to decrease the power consumption

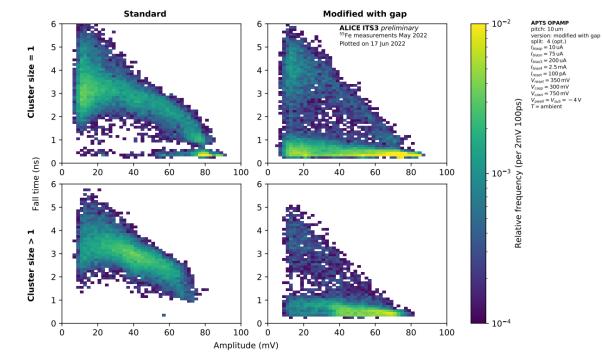

### **APTS-OA:**

## Process modification reduces charge

### collection time

- Fast readout allows to estimate the charge collection time via signal fall time

- In modified process the charge is collected faster

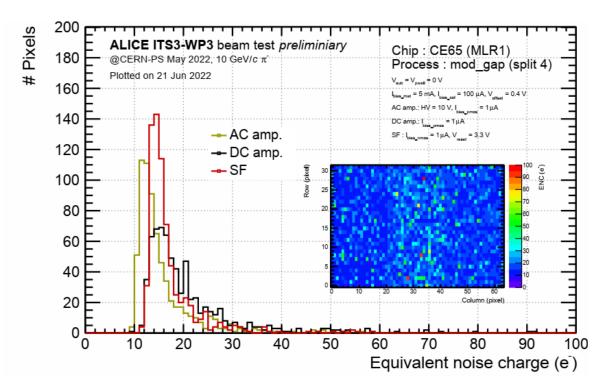

### CE65:

### Circuit Exploratoire 65 nm

- 2 matrix sizes

- $64 \times 32$  with 15  $\mu$ m pitch

- $48 \times 32$  matrix with 25  $\mu$ m pitch

- Rolling shutter readout (50 µs integration time)

- 3 in-pixel architectures:

- AC-coupled amplifier

- DC-coupled amplifier

- Source follower

- 4 chip variants:

- Standard process 15 μm pitch

- Modified process 15 μm pitch

- Modified process with gaps 15 μm pitch

- Standard process 25 μm pitch

- Presented results from CERN PS beam test

### 1.5×1.5 mm<sup>2</sup> <sup>12</sup>

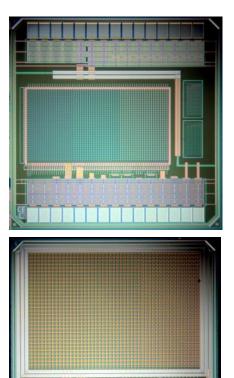

### CE65: Cluster charge doesn't depend on process modification and pixel architecture

- All submatrices in standard and modified processes collect the same total charge

- Charge distribution parameters roughly correspond to effective epitaxial layer of 11 μm (via H. Bichsel https://doi.org/10.1103/RevModPhys.60.663)

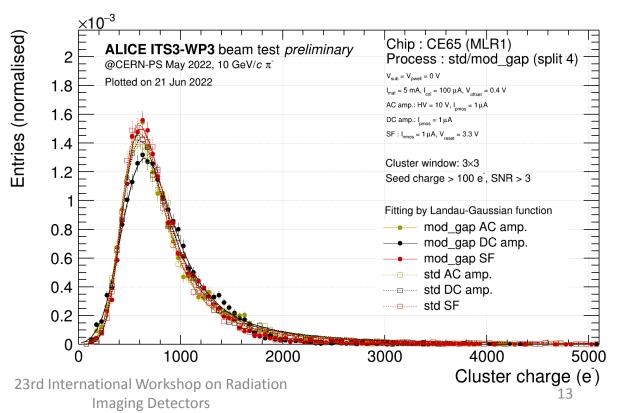

# CE65: Process modification reduces charge sharing

- Effect observed in APTS with <sup>55</sup>Fe sources confirmed at beam test

- In modified process all charge is mostly collected by single pixel

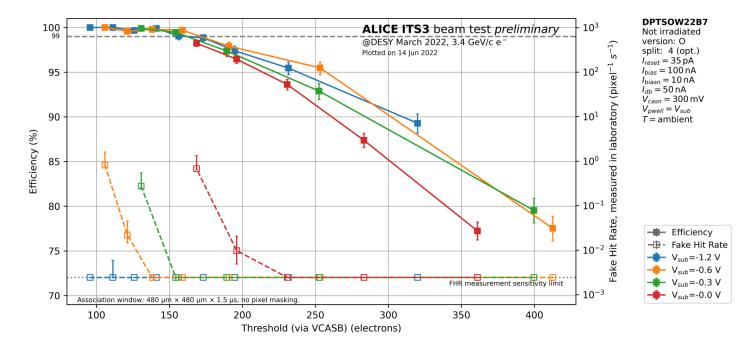

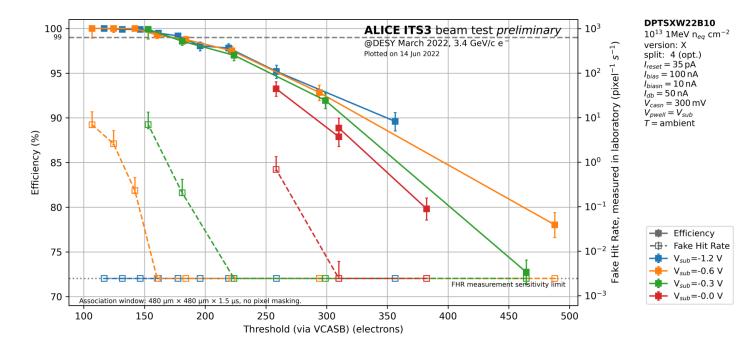

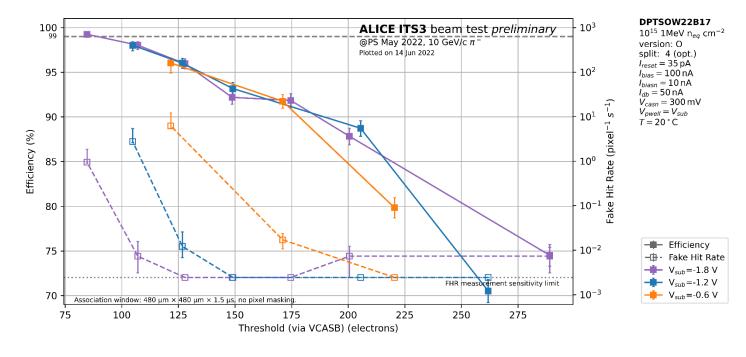

### DPTS: Digital Pixel Test Structure

- 32×32 pixel matrix

- Asynchronous digital readout

- Time-over-Threshold information

- Pitch:  $15 \times 15 \ \mu m^2$

- Only "modified with gap" process modification

- Tunable Power vs Time resolution via pixel frontend parameters

- Presented results from DESY and PS beam tests

1.5×1.5 mm<sup>2</sup>

### Non irradiated DPTS: Excellent efficiency and low fake hit rate

### Irradiated DPTS (10<sup>13</sup> n<sub>eq</sub>): Larger fake hit rate, but has margin

### Irradiated DPTS ( $10^{15} n_{eq}$ ): Efficient at 20 °C with limited fake hit rate

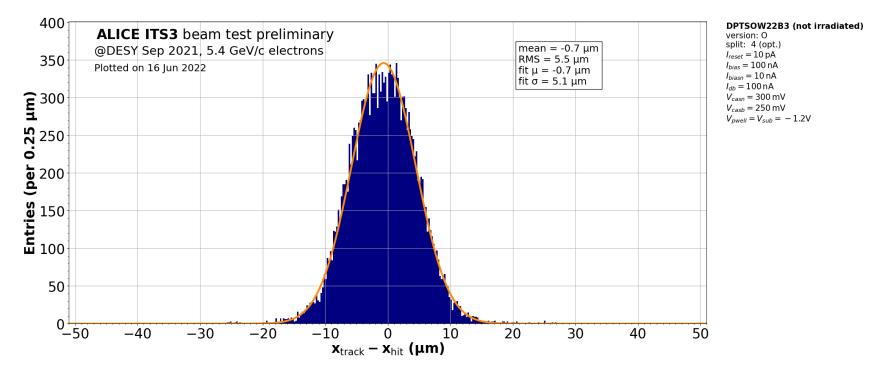

### DPTS: Spatial resolution ~5 µm

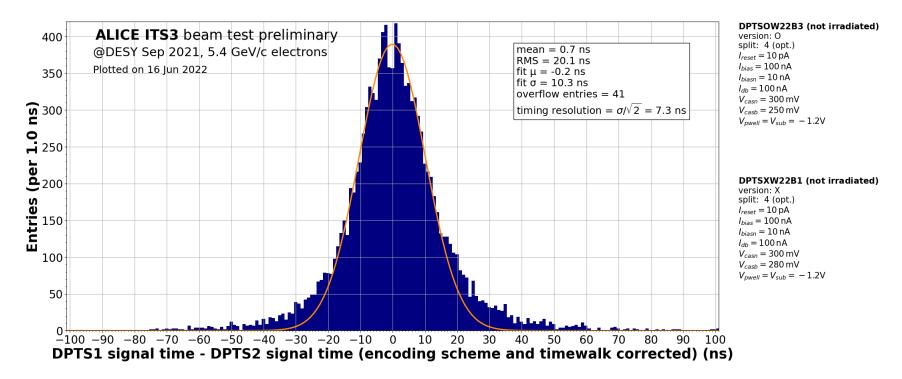

### DPTS: Temporal resolution ~7 ns

### Summary

- TPSCo 65 nm CMOS IS process is being evaluated for future ALICE ITS3

- Chips from MLR1 submission yield promising results on technology capabilities:

- Efficiency > 99% at FHR < 1 hit/second/1024 pixels</li>

- Spatial resolution ~5  $\mu m$

- Temporal resolution ~7 ns

- Withstands NIEL irradiation of up to  $10^{15} n_{eq}/cm^2$

- Efficiency ~99% at FHR 1 hit/second/pixel at 20 °C

d = 300 mm

### Next step: stitching

First run with 2 stitched sensors in preparation:

- MOSS

260×14 mm<sup>2</sup> 6.72 Mpixels <sup>-</sup>

- MOST

260×2.5 mm<sup>2</sup> 900 kPixels

More news at IWoRiD 2023?