# Development of CoRDIA: An Imaging Detector for next-generation Synchrotron Rings and Free Electron Lasers

Ulrich Trunk for the CoRDIA collaboration:

Sergei Fridman<sup>1</sup>, Heinz Graafsma<sup>1</sup>, Mohamed Lamine Hafiane<sup>2</sup>, Tomasz Hemperek<sup>2</sup>, Alexander Klyuev<sup>1</sup>, Hans Krüger<sup>2</sup>, Torsten Laurus<sup>1</sup>, Alesandro Marras<sup>1</sup>, David Pennicard<sup>1</sup>, Sergej Smoljanin<sup>1</sup>, Ulrich Trunk<sup>1</sup>, Cornelia Wunderer<sup>1</sup>

<sup>1</sup>DESY

<sup>2</sup>Bonn University

#### Outline

- ☐ Future sources and detector requirements

- ASIC design

- Signal chain

- Development roadmap

- Outlook

#### **Current Imagers**

#### Imager example for PETRA: LAMBDA

- Up to 10 megapixel (55 μm pixel size)

- 2 kHz frame rate (continuous)

- Photon counting up to250,000 photons/pixel/s

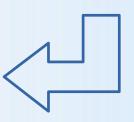

#### Imager example for Eu.XFEL: AGIPD

- 1 megapixel (200 μm pixels),4 megapixel in development

- 4.5 MHz burst imaging(internal storage: 352 images)

- Dynamic range single photon

to 10<sup>4</sup> photons /pixel/image

#### Future Source Upgrades

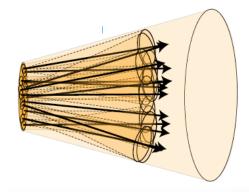

**PETRA-IV**: Upgrade to diffraction limited ring (2028)

PETRA-III electron bunch

PETRA-IV electron bunch

- 100-1000 fold improvement in brilliance and coherent flux

- ☐ Frame rate requirements in some experiments increase from kHz to >100 kHz (continuous)

readout

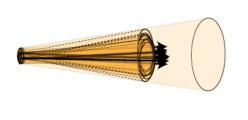

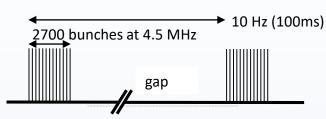

**European XFEL:** CW mode operation (20??)

Current Eu.XFEL burst mode

Future CW operation

- many more [O(1)] bunches per second

- no gap for burst-readout of internal storage

Common need for:

- continuous readout

- > 100kHz frame rate

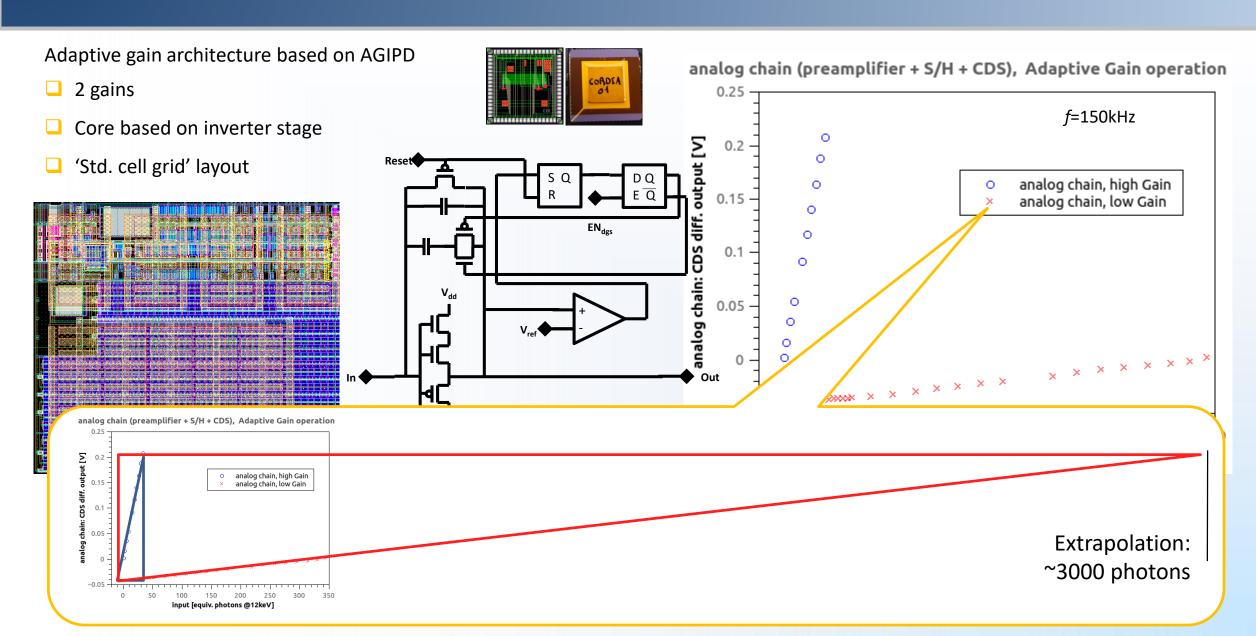

## CoRDIA – Continuous Readout Digitising Imager Array

#### **CoRDIA** – Design Goals

- ☐ Pixel size 100μm × 100μm

- Continuous Frame Rate f<sub>FR</sub> ≈ 150kHz

(≥100kHz)

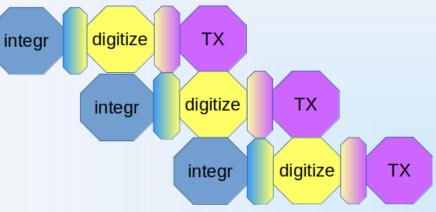

- Dead-time free pipelined operation

- Single-photon sensitive (@ ≤12keV)

- ≥ 10k photon Dynamic Range

- Little or no dead area

#### **CoRDIA** – Implementation

- Hybrid pixel detector

- Charge integrating

- Dynamic gain switching (à la AGIPD)

- Electron-collecting to be compatible with various sensors:

- Si for hard (12keV X-Rays)

- High-Z materials for E > 15keV

- Active (LGAD) sensors for low E

- On-chip digitisation @ ≥ 10 bit

- Multi-Gbit data transmission (based on Timepix4 implementation)

- TSMC 65 nm technology

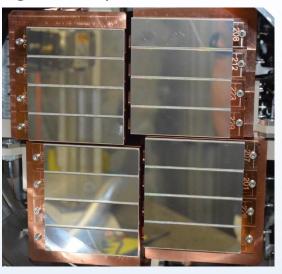

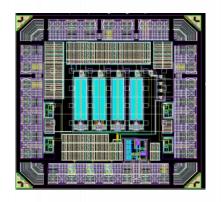

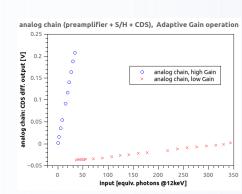

CoRDIA 0.1 (analogue) &

HSI\_ADC01 (SAR ADC) test chips

Collaboration of Bonn University & DESY

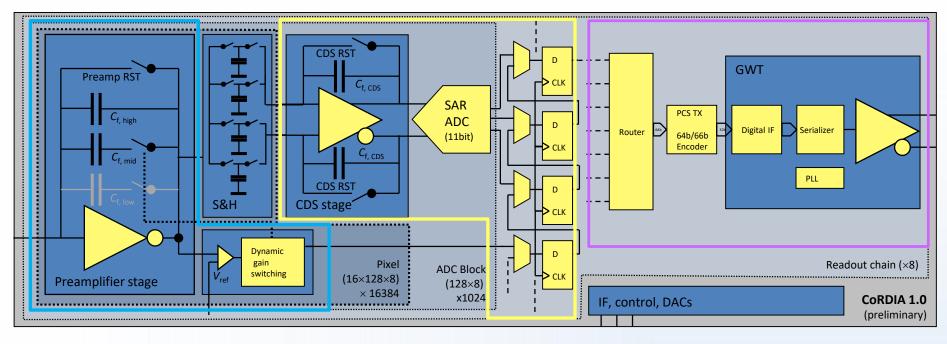

#### CoRDIA – Architecture & Signal Path

#### **CoRDIA Architecture**

- ☐ CW (continuous wave) operation

- Pipelined

- Small dead time due to reset of integrating preamp

- ☐ Size of individual ASIC chip still under discussion:

128 x 128, 128 x 192, 256 x 192, 256 x 256

#### Preamp

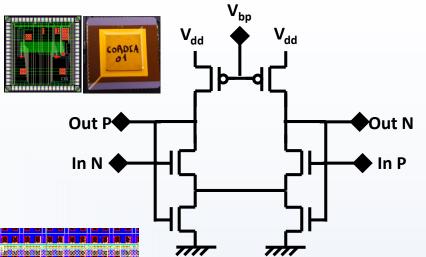

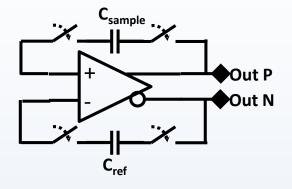

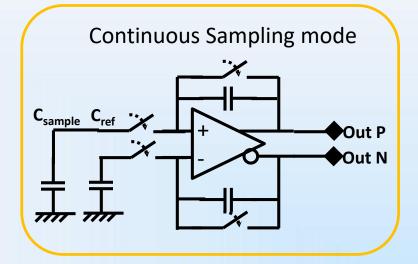

## CDS – Correlated Double Sampling Stage

Based on a fully differential amplifier

- Differential pair with simple CM feedback

- SC or continuous sampling (CS) mode

- 2 gains (in CS mode)

- 'Std. cell grid' layout

Switched Capacitor mode

#### SAR ADC

#### HSI\_ADC01 contains 4 successive approximation register (SAR) ADCs

- □ 11 bit

- ≥2.5 MSamples/s

- Serial data output

- ~10 ENOBs (best one)

Nonlinearity (INL & DNL) ≤1 LSB => ~10 ENOBs

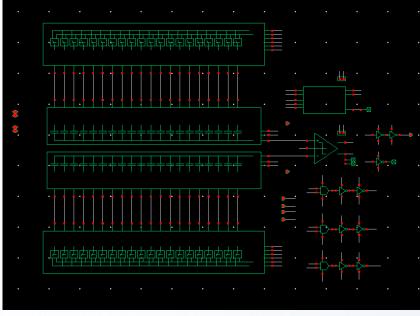

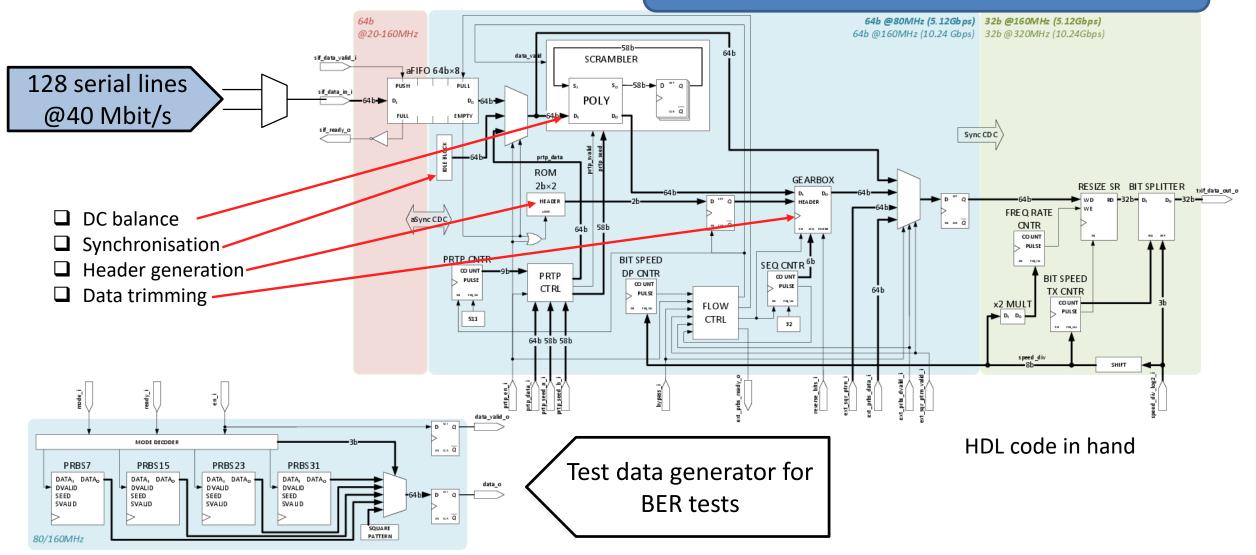

#### PCS TX: BLOCK DIAGRAM

#### Physical Coding Sublayer

3

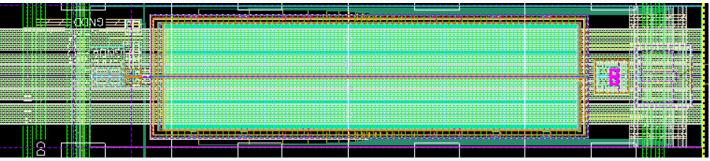

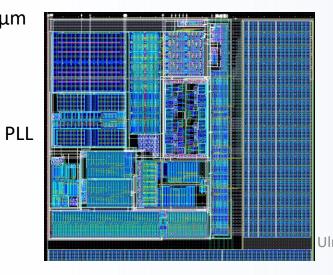

## GWT – Gigabit Wire Transmitter

Developed by

Vladimir Gromov (NIKHEF)

Consists of a PLL & a 32 to 1 serializer/mux

- PLL

- 320MHz or 640MHz

- 86 μm x 120 μm

- Serializer/mux

- 5.12 Gbit/s or 10.24 Gbit/s

- Individual DLLs for either speed

- Differential (100  $\Omega$ ) off-chip driver

- 86 μm x 67 μm

Config. Delay Line A DLL @ 320MHz clock out rst\_ventr\_vdd\_PLL Digital Core blocks (synthesized rst\_ventr\_vdd\_DLL Analog Core blocks (custom) Serializer

dataIn: 32bit VDD\_ana MUX 16bit converter **Dual Port FIFO** (asynchronous) Double |Out + clock write @ Data Rate 160MHz / sel <1> 320MHz Rm=32Ω clock ref 320MHz clock read (320MHz/640MHz) Clock Cleaner (PLL-CC) PLL output clocks sel\_A<15:0> sel\_B<15:0> (320MHz / 640MHz) clock in Edge Combiner\_A 320MHz DLL Lock monitor 16 phases\_A @ 195ps 16 phases B@ 97ps PLL Lock monitor Charge Pump VDDGWT Rd=100 clock\_out Filter Capacitor Delay Line B GNDGWT EN\_B DLL @ 640MHz VDD\_dig Schematics by Vladimir Gromov (NIKHEF)

Timepix4 GWT @5 Gbit/s

X. Llopart, On behalf of the Medipix4 Collaboration 11 th February 2022 **CERN** seminar

Ulrich Trunk for the CoRDIA

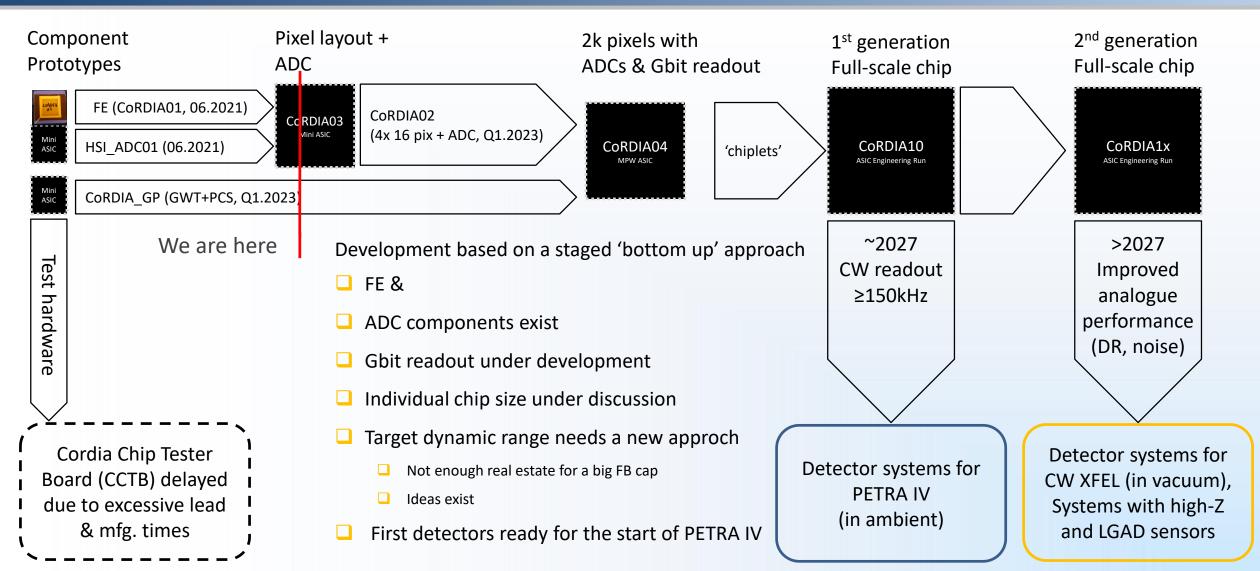

## CoRDIA Development Roadmap

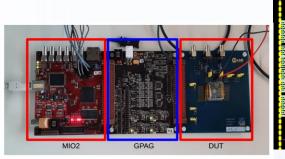

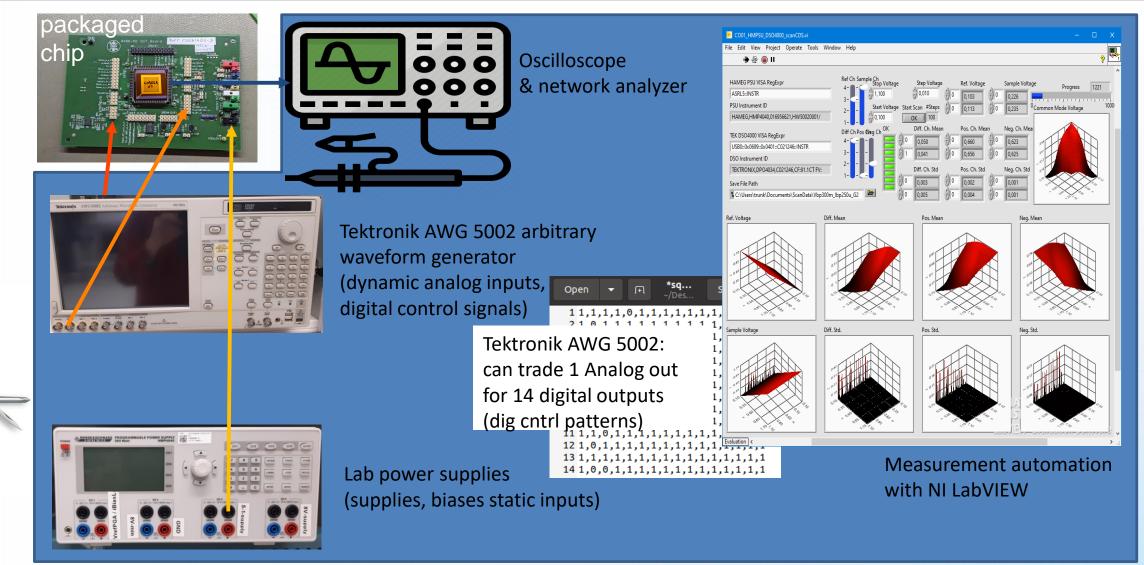

## Chip Test Environment

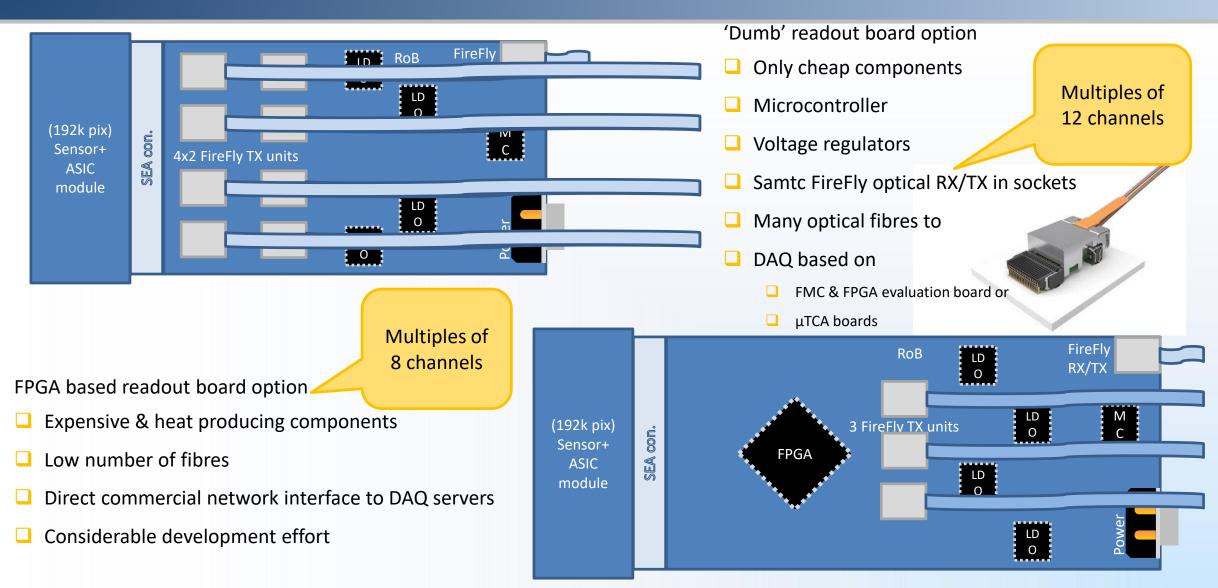

## Partitioning, Chiplets & Readout Electronics

## Partitioning, Chiplets & Readout Electronics

Final chip size is still under discussion...

- $\square$  Multiple of (16 x 128) pixel = 2048 pixels

- Choice of ROB architecture

- Yield

- Available sensor sizes

TimePix 4 sized chips

| Chip size<br>(pixl) | # of 5<br>Gbit links | Smallest<br>reasonable<br>FEM | FEM size<br>(pixel) | # of FireFly<br>TX (12 ch) | 256 x 768<br>pix module<br>size (chips) |

|---------------------|----------------------|-------------------------------|---------------------|----------------------------|-----------------------------------------|

| 128 x 128           | 8                    | 2 x 3                         | 256 x 384           | 6                          | 2 x 6                                   |

| 128 x 192           | 12                   | 2 x 1                         | 256 x 192           | 2                          | 2 x 4                                   |

| 256 x 192           | 24                   | 1 x 1                         | 256 x 192           | 2                          | 1 x 4                                   |

| 256 x 256           | 32                   | 1 x 3                         | 256 x 768           | 8                          | 1 x 3                                   |

AGIPD sized chips

#### Summary

CoRDIA – Continuous Readout Digitizing Imager Array - is...

- ☐ Targeted to DL Synchrotron sources (like PETRA IV)

- CW FELs (future CW Mode of European XFEL)

- Hybrid Pixel Detector

- Charge Integrating & dynamic gain switching

- Pixel size 100μm x 100μm

- □ Continuous Frame Rate  $f_{FR} \approx 150$ kHz ( $\geq 100$ kHz)

- On-chip digitisation @ ≥ 10 bit

- MGbit data transmission

- ☐ All fundamental components exist

- ☐ FE & ADC on test chips

- MGBT readout on TimePix 4

- (Component) test chips show good performance

- Implementation of pixel blocks is ongoing

- Implementation of MGBT readout started

- Full-size chips for detectors at PETRA IV ~2027

- CW-FEL version with higher analogue performance ready for future CW operation of Eu.XFEL