# Development of the Slow Controller of the RPC System Link for LS2 Update of the CMS/HL-LHC Experiment

Workshop RENAFAE 2022 - CBPF-Rio Collaboration Ph.D. Candidate Eng. Fabio Marujo da Silva, MSc. (CEFET/RJ) Team Leader: Gilvan Augusto Alves, D.Sc. (CBPF) Electronic Coordinator: Behzad Boghrati, D.Sc. (IPM)

April 27<sup>th</sup>, 2022 - fmarujod@cern.ch

- Muon System

- RPC Muon

- Link Board/Control Board

- New Link Board/Control Board

- Slow Controller

- uTCA CRATE

- AMC13/MCH

- uHTR

- Kintex-7 EVB

- Preliminary and Expected Results

- Overview

# **RPC Muon - CMS HL-LHC Upgrade (Phase-2):**

## System Muon: Upgrade nas FE/BE readout e RPC Link Board

Technical proposal CERN-LHCC-2015-010 https://cds.cern.ch/record/2020886 Scope Document CERN-LHCC-2015-019 https://cds.cern.ch/record/2055167/files/LHCC-G-165.pdf

#### L1-Trigger/HLT/DAQ

https://cds.cern.ch/record/2283192 https://cds.cern.ch/record/2283193

- Tracks in L1-Trigger at 40 MHz

- PFlow-like selection 750 kHz output

- HLT output 7.5 kHz

#### Calorimeter Endcap https://cds.cern.ch/record/2293646

- 3D showers and precise timing

- Si, Scint+SiPM in Pb/W-SS

#### Tracker https://cds.cern.ch/record/2272264

- · Si-Strip and Pixels increased granularity

- Design for tracking in L1-Trigger

- Extended coverage to η ≈ 3.8

#### **Barrel Calorimeters**

**MIP Timing Detector**

Precision timing with:

https://cds.cern.ch/record/2296612

Barrel layer: Crystals + SiPMs

#### https://cds.cern.ch/record/2283187

- + ECAL crystal granularity readout at 40 MHz with precise timing for  $e/\gamma$  at 30 GeV

- ECAL and HCAL new Back-End boards

#### Muon systems https://cds.cern.ch/record/2283189

RPC link -board

DT & CSC new FE/BE readout

New GEM/RPC 1.6 < n < 2.4</li>

# **New Hardware**

- Control Board

- Link Board

- Extended coverage to n ≈ 3

Beam Radiation Instr. and

- Luminosity, and Common Systems and Infrastructure https://cds.cern.ch/record/ 2020886

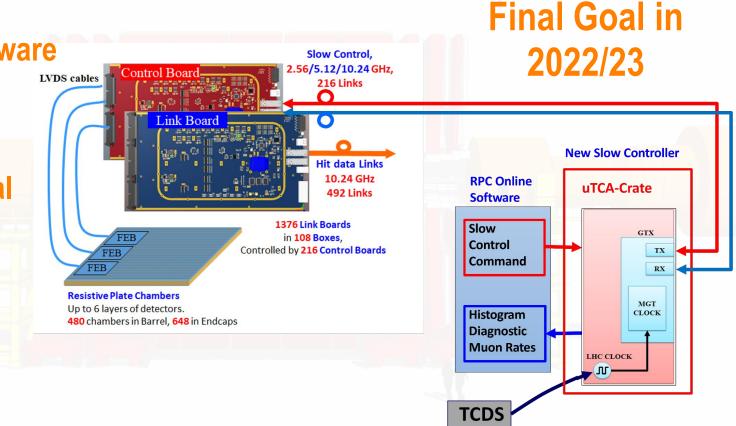

#### **New Slow Controller**

- Control Board

Link Board

- Online RPC

- Real Time

- Dashboard

Innovative and extremely challenging new capabilities

**F. Marujo - Slow Controller - CBPF-Rio Collaboration** – Workshop RENAFAE april 27<sup>th</sup>, 2022

Endcap layer: Low Gain Avalanche Diodes

## Link Board/Control Board

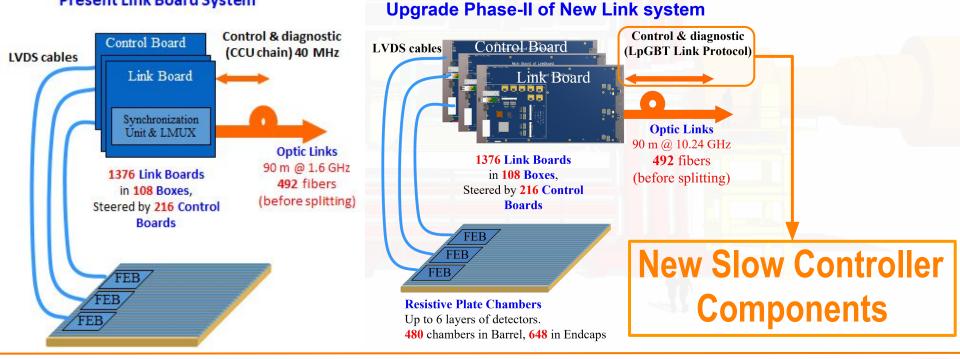

# Link Board system Overview

**Update motivation**

#### **Present Link Board System**

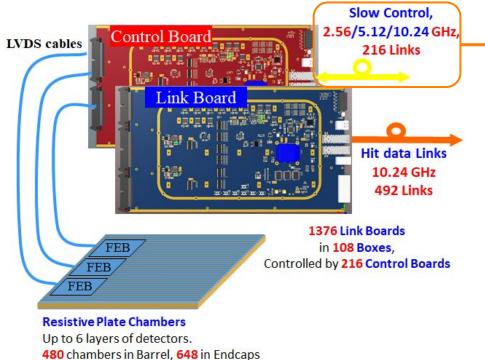

# Wew Link Board/Control Board

# New Link Board system Overview

# Based on Xilinx's Kintex-7 FPGA

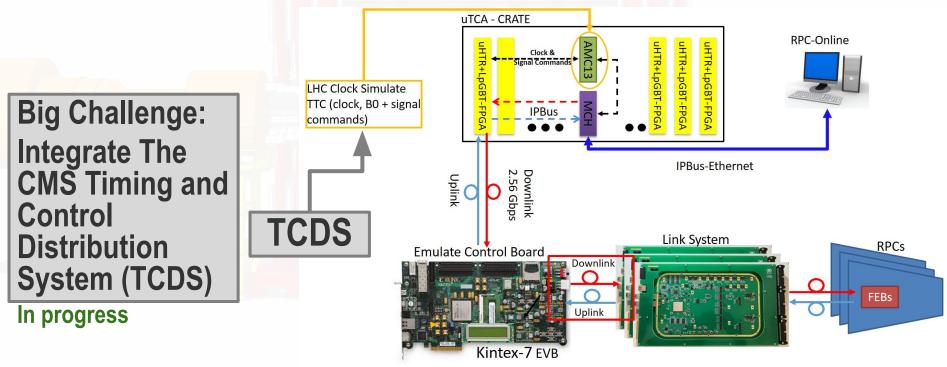

**New Slow Controller** FPGA XC7K160T - Version Industrial **Redundant optical link Remote programming High-speed data transmission** at **FIXED LATENCE Point-to-point fiber optic** connection between the control boards and the Slow Controller

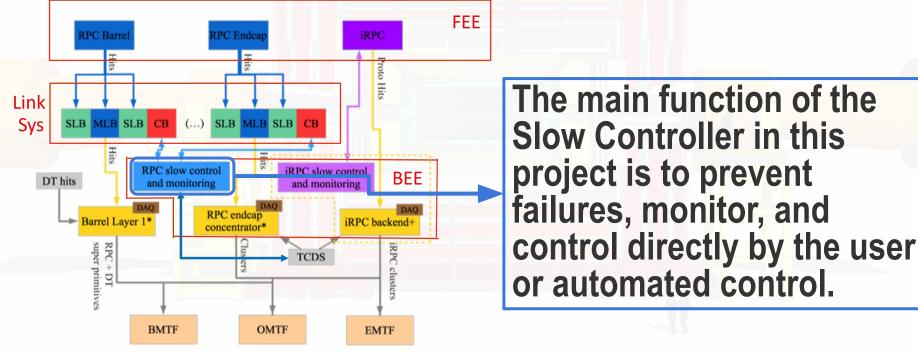

# What is Slow Controller?

Slow Controller is Subsystem to monitor/control one or more systems

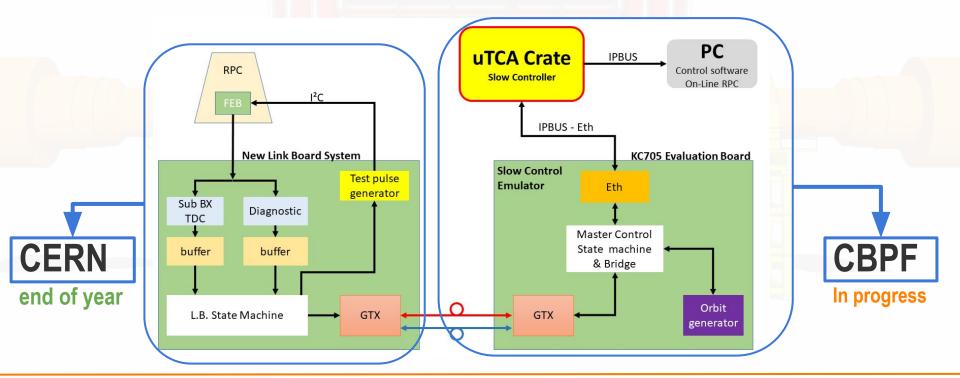

# **Slow Controller development**

## Implementation: FPGA-Kintex7, Rack uTCA and AMC13

# **Slow Controller development**

## Hardware Implementation for Slow Controller

# uTCA CRATE

#### Main Hardware modules

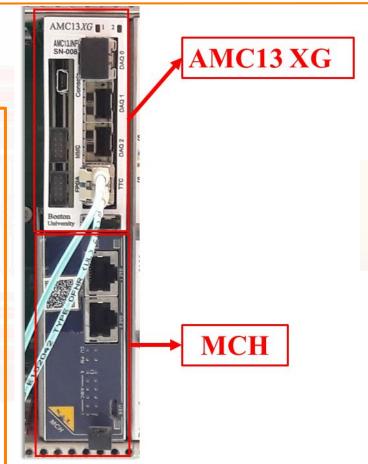

# AMC13/MCH

# Main Hardware modules

- The AMC13XG: a new generation clock/timing/DAQ module for CMS µTCA

- Supports 10 gigabit optical fiber and backplane interfaces

- Implementation using Xilinx Kintex-7TM FPGAs

- **μTCA MCH Ethernet switch**

- External applications can perform READ, WRITE, and RMW transactions on this bus by way of Internet Protocol (IP) packets

# uHTR

## **Main Hardware modules**

µTCA Trigger and Readout Module (uHTR)

Front-end data links (1.6 Gbps and 4.8/5.0 Gbps)

Data links which carry DAQ data from front FPGA to back FPGA (4 Gbps)

DAQ data output format to AMC13/DTC

"QIE Reset" broadcast TTC/TCDS command

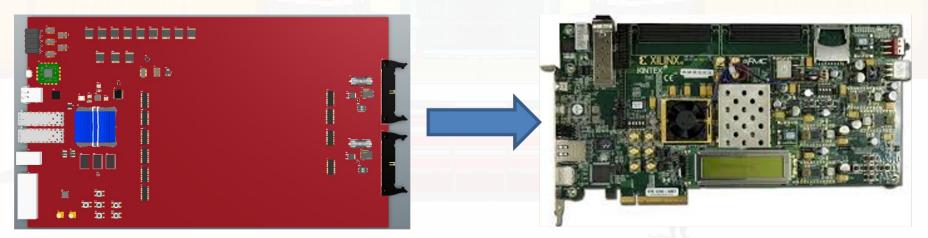

# Kintex-7 EVB

#### Main Hardware modules

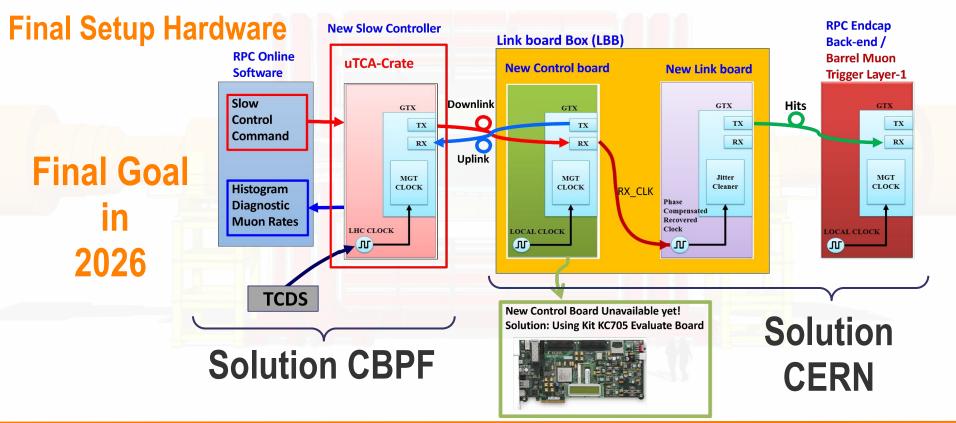

# New Control Board Unavailable yet! Solution: Using Kit KC705 Evaluation Board

#### In process: New Control Board

#### Kit KC705 Emulate Control Board

# Overview

## **Now Setup Hardware**

# **Solution CBPF**

Test individual modules

Connectivity

Hardware Integration

# **Overview**

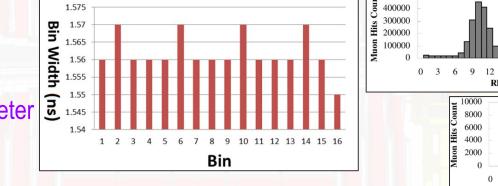

# Preliminary and Expected Results

# Overview

## **Expected Results in 2026**

Slow Controller Operation-Online RPC (Back-End) software uses Slow Controller

# By Online RPC FEB Threshold Setting TTC clock precision adjustment (LHC) windows configuration open/closed FPGA configuration file (remote programming)

# Preliminary and Expected Results

# Overview

## **Expected Results in 2026**

The ONLINE Software: Request/control services through Slow controller

**CMS Online RPC**

Slow Controller Calibration mode Link Board Parameter

Setting

- Control Board

- Parameter setting

- Physics RUN

- Standby

- HistogramDiagnostic

FEB Test

العالية وخطيته

15 18 21 24 27 30

**RPC Strip**

10000000

2018-03-26

10:26:25

HBB2 / 1/F (worked)

10000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

10000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

10000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

10000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

10000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

10000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

1000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

1000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

1000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

1000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

1000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

1000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

1000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

1000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)

1000000

- 2 PR30 / 1/5 (worked)

- 2 PR30 / 1/5 (worked)