- ➔ Hardwired signals:

- ST\_CIRCUIT\_OK (issued per circuit by QPS) → ST\_ABORT\_PIC (received by PIC)

- Provokes a fast power abort of the concerned power converter

- Transmitted via current loops integrating QPS, PIC and PC

- ➔ Software signals:

- ST\_PWR\_PERMIT signal to be verified prior to powering of a circuit

- Signal issued per circuit thus avoiding masking of signals during hardware commissioning

- Signal is TRUE in case the related QPS systems and their supervision are available and ready for powering

- Integrity of a superconducting circuit (e.g. after a quench) not covered by the signal

- To be checked with the help of post mortem analysis

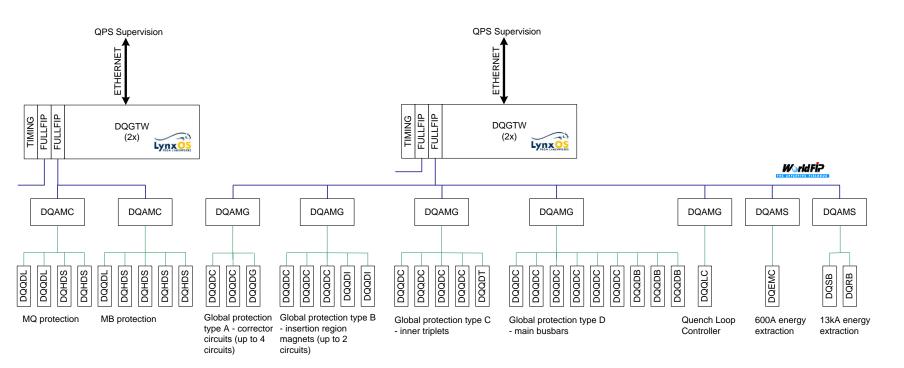

## **QPS** controls layout

## ➔ Equipment per sector:

- 4 x gateways controlling 6 fieldbus segments with up to 60 clients

- 201/205 DQAMC type controllers

- ~29 DQAMS type controllers

- ~30 DQAMG type controllers

- Each QPS controller calculates a local ST\_PWR\_PERMIT signal based on the information collected from the associated equipment (quench detectors, quench heater power supplies ...)

- Signal is transmitted permanently and time stamped

- Signal is by definition FALSE if controller not in LOGGING state

- The ST\_PWR\_PERMIT of a circuit is calculated on the supervision level based on predefined tables and exchanged between QPS PVSS & PIC PVSS

- ST\_PWR\_PERMIT<sub>Circuit</sub> =  $\Sigma$ ST\_PWR\_PERMIT<sub>Controller</sub>

- In case of the main circuits the involved controller signals are routed through several gateways (up to 4)

- Signal is not interlocking a change of its state from TRUE to FALSE creates an alarm

- The signal has to be verified in case of repetitive powering cycles

- Implementation (software interlock?) to be discussed

- Signal generation and exchange to be checked within LHC hardware commissioning