European Research Counci Established by the European Commission

MONOLITH

# Monolithic pixel sensor design for picosecond-level time resolution

Antonio Picardi on behalf of the MONOLITH group antonio.picardi@cern.ch

# **The MONOLITH ERC Project**

Funded by the H2020 ERC Advanced grant 884447<sup>[1]</sup>, July 2020 - June 2025

Monolithic silicon sensor able to:

precisely measure 3D spatial position of charged particles

provide picosecond time resolution

- > Technology choice:

- Fast and low-noise SiGe BiCMOS electronics

- > Novel sensor concept: the Picosecond Avalanche Detector (PicoAD)

<sup>[1]</sup> MONOLITH H2020 ERC Advanced Project Web Page - https://www.unige.ch/dpnc/en/groups/giuseppe-iacobucci/research/monolith-erc-advanced-project/

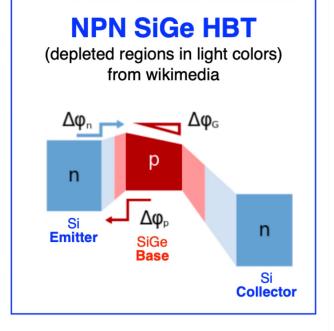

Leading-edge technology IHP SG13G2, 130 nm IHP process featuring SiGe HBT

### SiGe HBT = BJT with Germanium as base material:

- ➤ higher doping in base possible

- ➤ thinner base

- $\succ$  reduced base resistance  $R_b$

### Grading of Ge doping in base:

charge transport in base via drift

reduced charge transit time in base

high current gain β

$$ENC_{series\ noise} \propto \sqrt{k_1 \frac{C_{tot}^2}{\beta} + k_2 R_b C_{tot}^2}$$

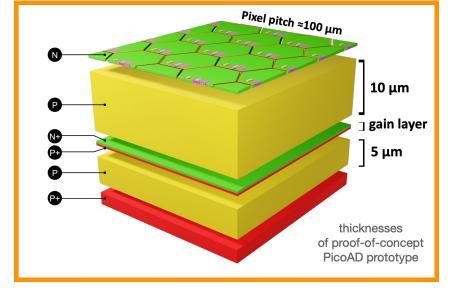

# **PicoAD | Sensor Concept**

### Multi-Junction Picosecond-Avalanche Detector<sup>[1]</sup>

➤Continuous and deep gain layer

De-correlation from implant size/geometry

high granularity and full fill factor (high spatial resolution)

>Only small fraction of charge gets amplified

reduced charge-collection (Landau) noise (enhance timing resolution)

<sup>[1]</sup>G. Iacobucci, L. Paolozzi and P. Valerio. Multi-junction pico-avalanche detector; European Patent EP3654376A1, US Patent US2021280734A1, Nov 2018

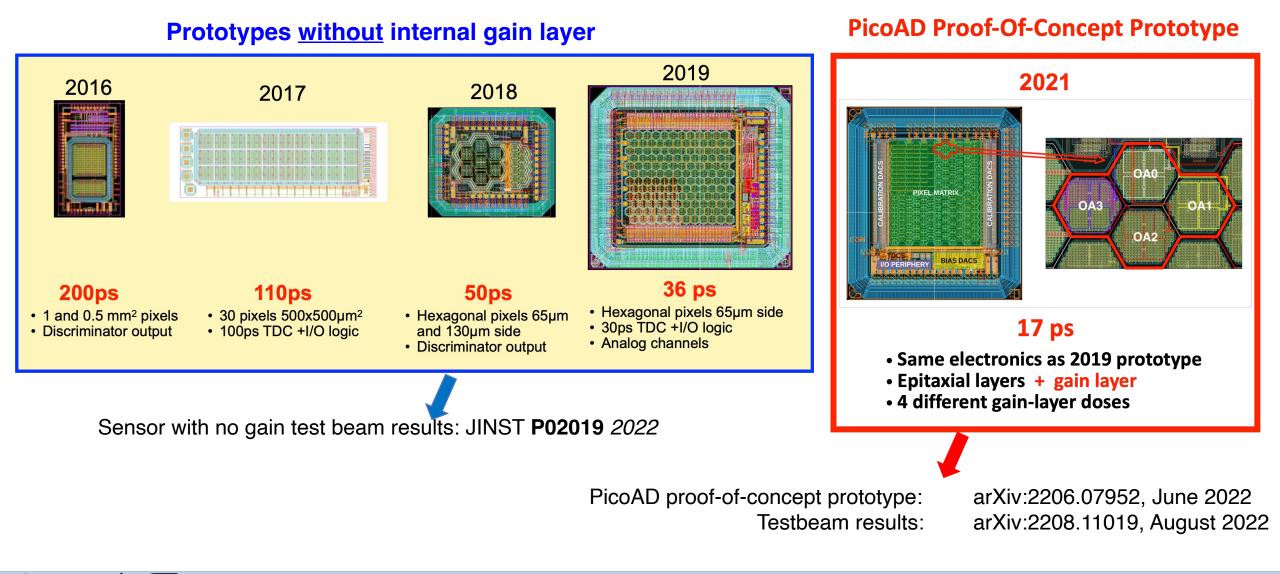

# SiGe BiCMOS prototypes at UniGe

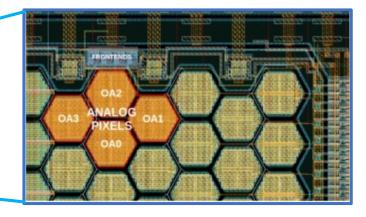

# Analog pixels proof-of-concept prototype

100  $\mu$ m pitch hexagonal pixels 25  $\mu$ m depletion

Front-end electronics:

➢ HBT preamp (off-pixel)

➢ Two HBT BJT-based emitter follower (off-pixel) to drive 50 Ω

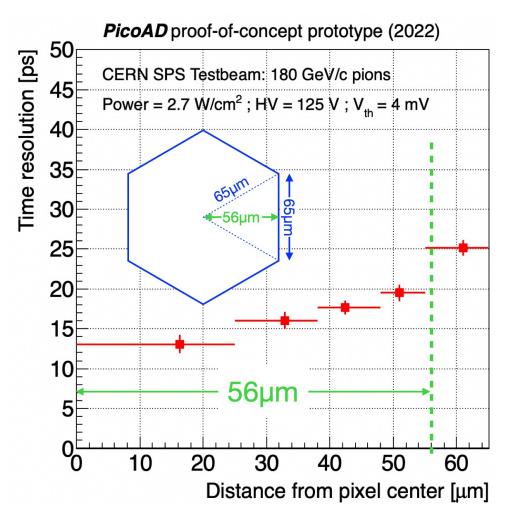

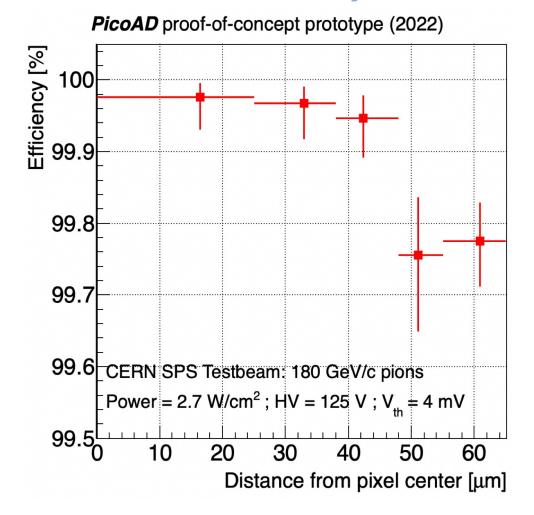

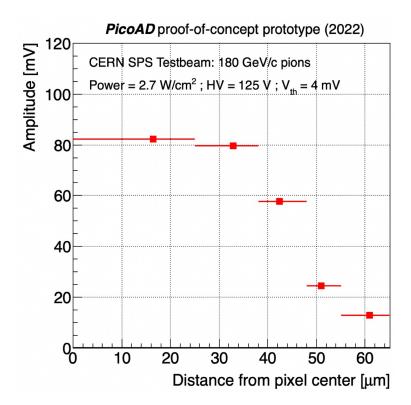

### **Testbeam results**

### **Time resolution**

UNIVERSITE

DE GENÈVE

### Efficiency

European Research Council Established by the European Commission

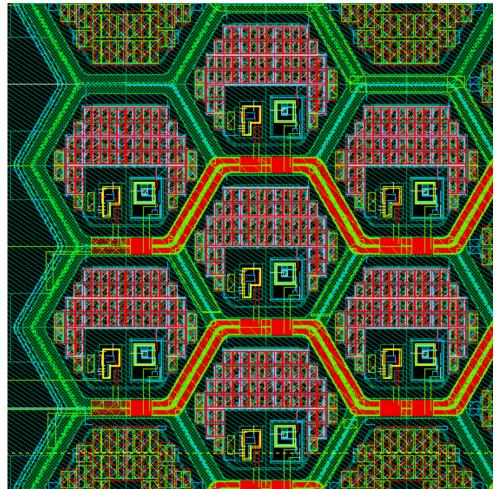

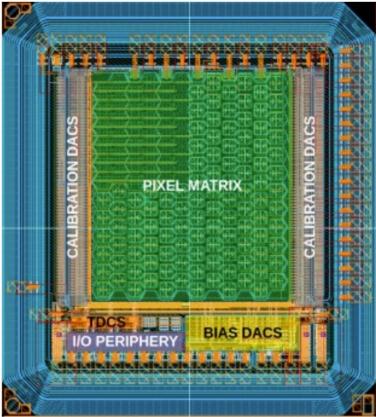

# **Next MONOLITH TESTCHIP**

New prototype (submitted on September 16<sup>th</sup>)

➢ Proof of concept PicoAD prototype ⇒ time resolution ≈ 17 ps

>Next MONOLITH testchip  $\Rightarrow$  target time resolution  $\leq$  10 ps

- ➢PicoAD sensor

- ➤Improved electronics

- >Smaller capacitance: pixel pitch (112  $\mu$ m  $\rightarrow$  50  $\mu$ m)

- >Reduction of wells interpixel isolation gap  $(10 \ \mu m \rightarrow 6 \ \mu m)$

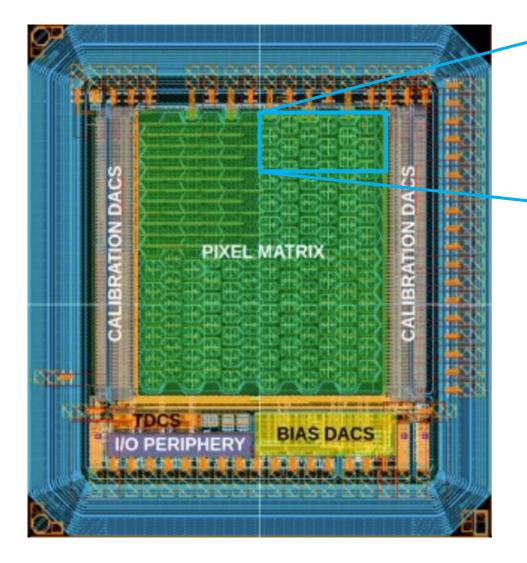

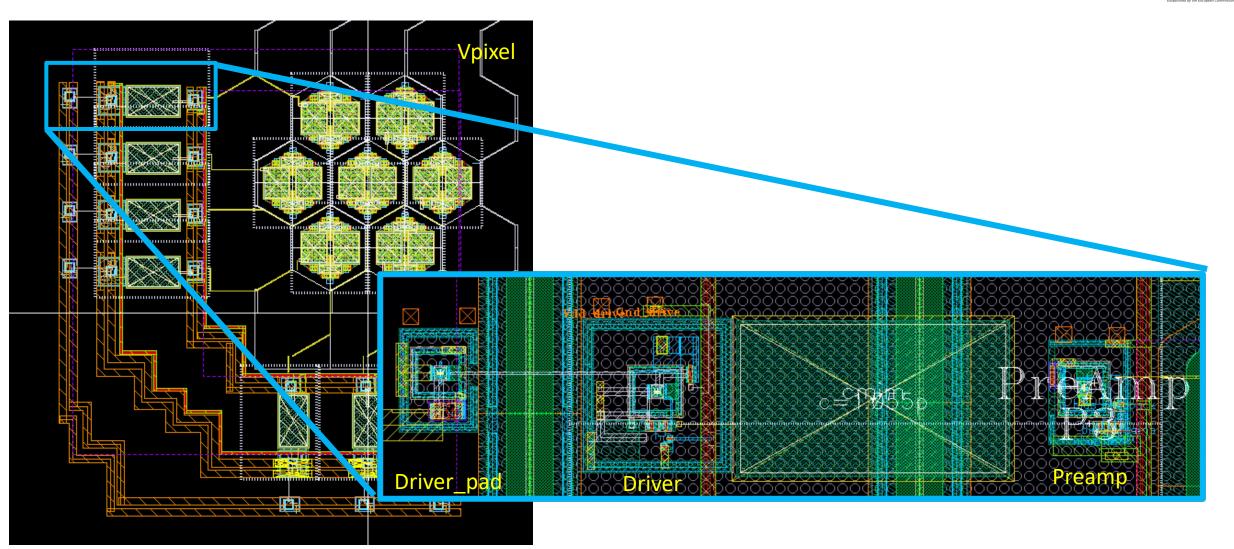

# **MONOLITH prototype | Flavors**

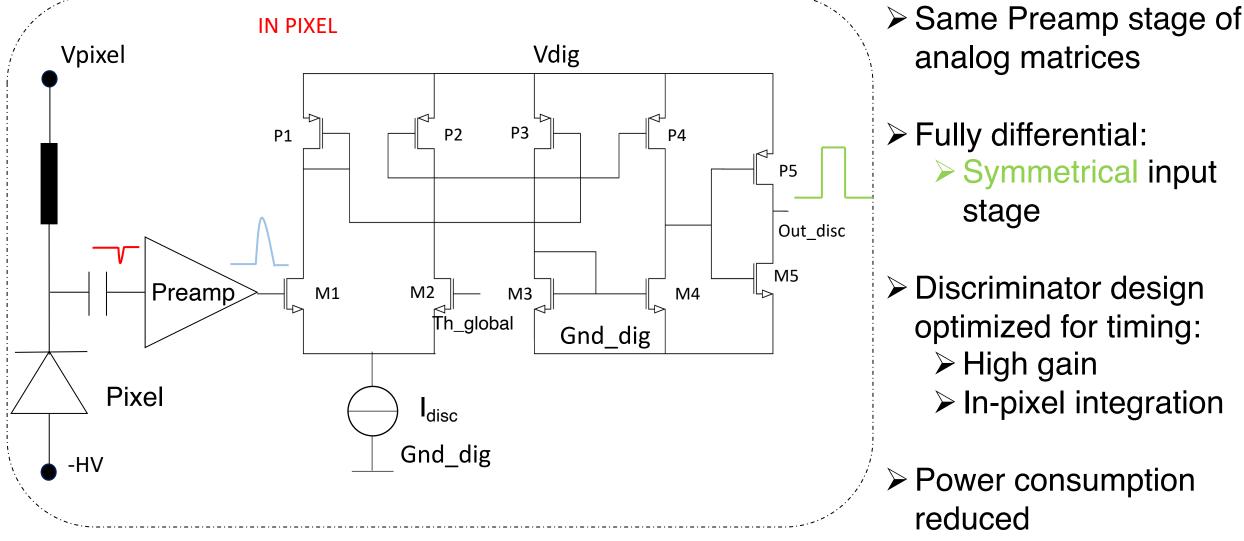

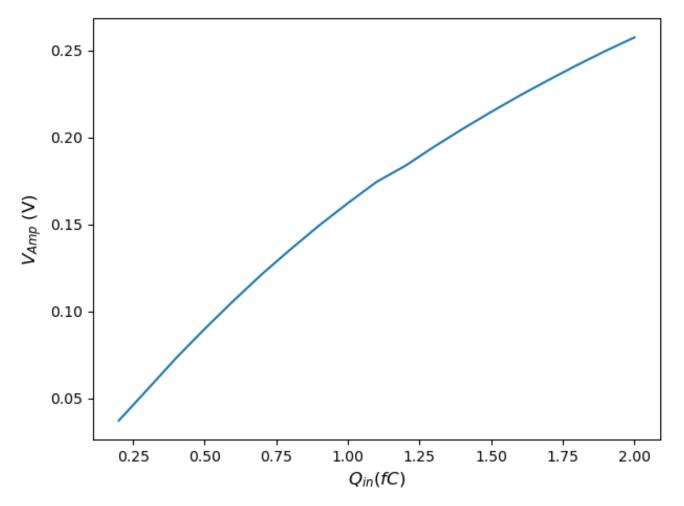

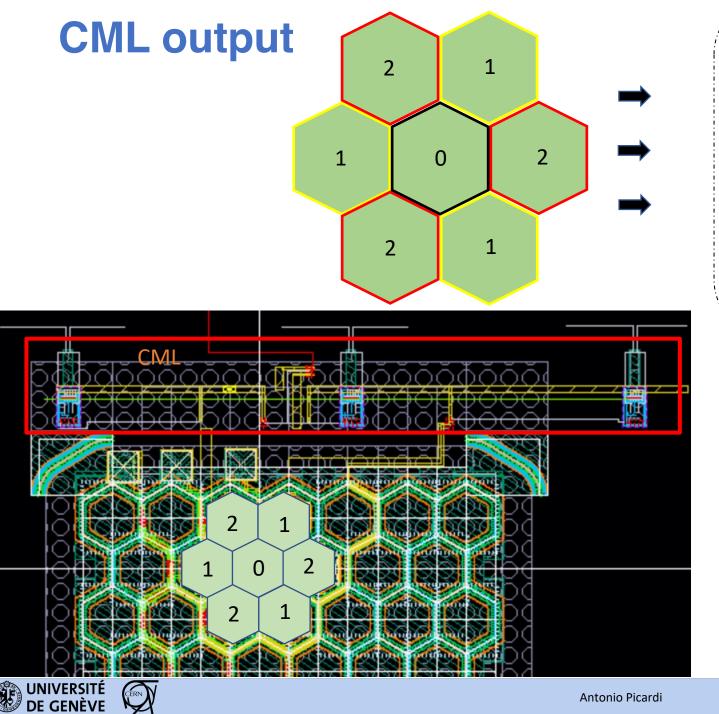

3 sub-matrices for probing performance of each stage of the FE architecture

# Each sub-matrix with 7 analog pixels: >AM0:

Preamp (in-pixel)

Driver stage (off-pixel)

### ≻AM1:

Preamp (off-pixel)Driver stage (off-pixel)

### ≻DMO:

Preamp and Discriminator (in-pixel)

CML output

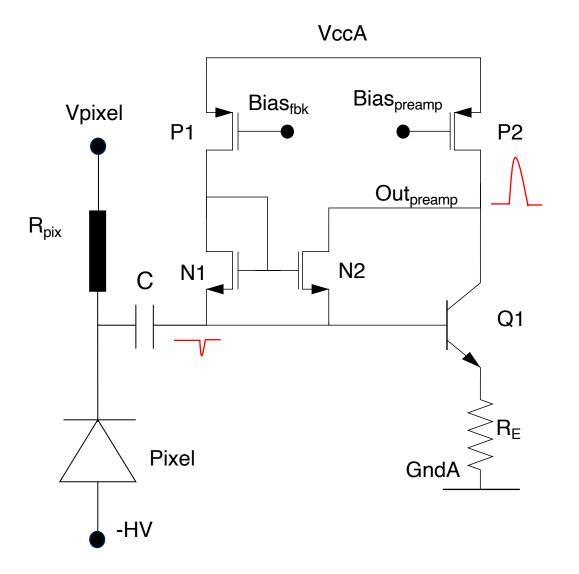

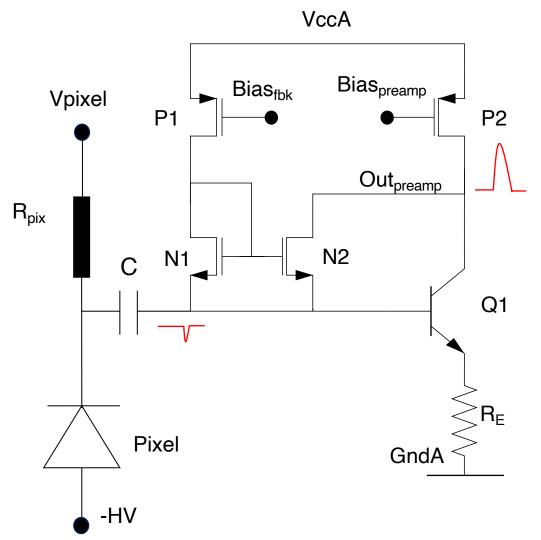

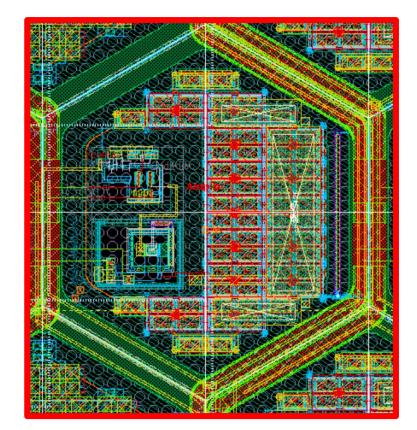

# Preamp stage: how we improved it

### Charge sensitive amplifier:

- Single-ended BJT-based stage with active load (PMOS)

- Gain and BW controlled by Bias<sub>fbk</sub> (tunable feedback resistance)

- Preamp current set by Bias<sub>preamp</sub>

### **Power consumption reduction:**

$\succ$  I<sub>preamp</sub>: 150  $\mu$ A  $\rightarrow$  50  $\mu$ A

$$\succ$$

V<sub>ccA</sub>: 1.8 V  $\rightarrow$  1.2 V

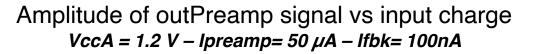

Cadence Spectre simulation with:

# **Preamp contribution to jitter**

|                        | $I_{fbk} = 10 nA$<br>$I_{preamp} = 200 \mu A$<br>$V_{ccA} = 1.2 V$ | $I_{fbk}$ = 100 nA<br>$I_{preamp}$ = 50 $\mu$ A<br>$V_{ccA}$ = 1.2 V |

|------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------|

| Component              | Jitter <sub>outPreamp</sub><br>[ps]                                | Jitter <sub>outPreamp</sub><br>[ps]                                  |

| BJT_hbt (Q1)           | 6.9                                                                | 3.4                                                                  |

| RE                     | 2.3                                                                | 1.8                                                                  |

| Pmos_load (P2)         | 4.8                                                                | 3.1                                                                  |

| Nmos_fbk (N1) and (N2) | 2.0                                                                | 2.6                                                                  |

| Pmos_fbk_slave (P1)    | 1.3                                                                | 2.3                                                                  |

| All_components         | 8.7                                                                | 4.4                                                                  |

|                        |                                                                    |                                                                      |

OLD DESIGN NEW DESIGN

P2 and Q1 give the dominant contribute to the noise

# **Discriminated Front-End (DM0)**

$\blacktriangleright$  I<sub>disc</sub>= 20  $\mu$ A  $\rightarrow$  5  $\mu$ A

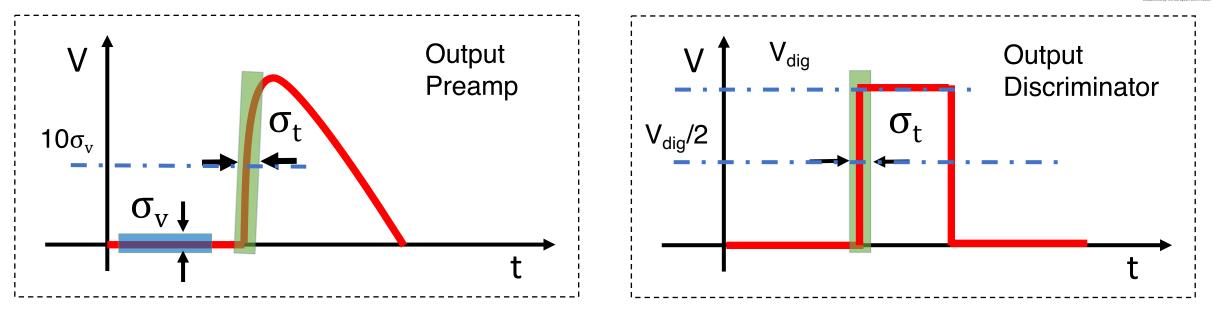

# **Timing performance (simulated)**

Cadence Spectre simulation for: Input charge=1 fC  $V_{ccA}=1.2 \text{ V } I_{fbk}=100 \text{ nA } I_{preamp}=50 \mu \text{ A } I_{disc}=5 \mu \text{ A}$

| σ <sub>preamp</sub> | σ <sub>discriminator</sub> |

|---------------------|----------------------------|

| ≅5 ps               | ≅7 ps                      |

Antonio Picardi

erc

MONOLITH

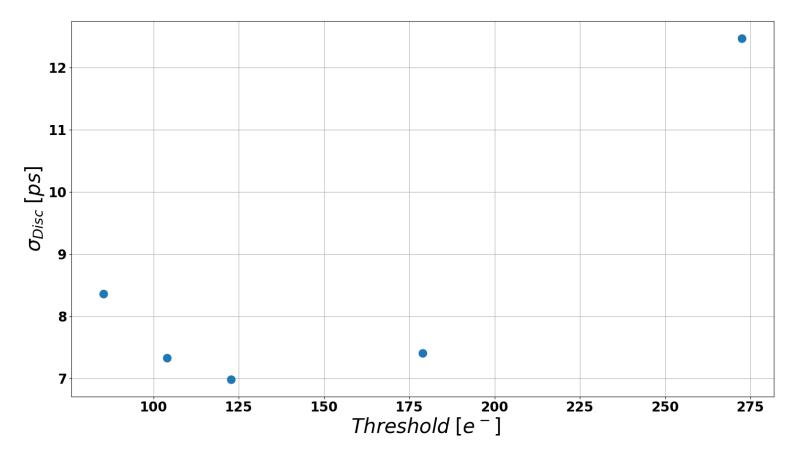

### **DM0 timing performance with threshold scan**

Cadence Spectre simulation Input charge= 1 fC Ipreamp= 50 μA Ifbk= 100 nA VccA= 1.2 V Vdisc= 1.4 V Idisc= 5 μA

> At threshold around 125 e<sup>-</sup>,  $\sigma_{\text{Disc}}$  below than 10 ps is obtained

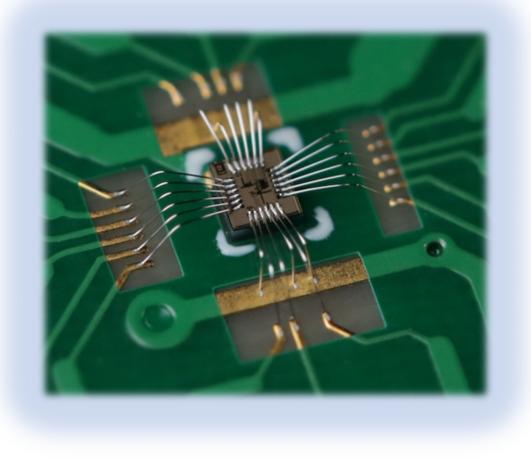

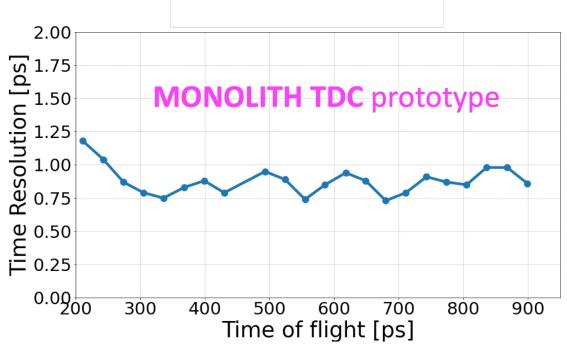

# **Sub-picosecond TDC**

We are developing a sub-picosecond TDC based on a novel design (our patent<sup>[5]</sup> & more):

#### Standalone prototype still under test at UNIGE. Integrated in MONOLITH 2022 monolithic ASIC.

<sup>[5]</sup> R. Cardarelli, L. Paolozzi, P. Valerio and G. Iacobucci, European Patent Application / Filing - UGKP-P-001-EP, Europe Patent EP 18181123.3. 2 July 2018.

# **Summary**

The PicoAD Monolithic proof-of-concept prototype (100  $\mu$ m pixel pitch, sensor not yet optimized for timing):

- Full sensor-bias voltage:

- ➤ Efficiency= 99.9%

> Average Time resolution  $\sigma_t = (17.3 \pm 0.4)$  ps

New ASIC monolithic prototype (just submitted) :

- > 50  $\mu$ m pitch and reduced interpixel distance

- Improved frontend

- New in-pixel discriminator

Full-reticle chip with 50  $\mu$ m pitch and 10ps timing in Summer 2025

European Research Council Established by the European Commission

# **BACKUP SLIDES**

# **MONOLITH TEAM**

#### **Giuseppe lacobucci**

- project P.I.

- System design

#### Thanushan Kugathasan

· Lead chip design Digital electronics

#### **Roberto Cardella** Sensor design

Laboratory test

#### Mateus Vicente

- System integration

- Laboratory test

#### Matteo Milanesio

· Laboratory test Data analysis

#### Antonio Picardi

- Chip design Firmware

#### Jihad Saidi Laboratory test

Data analysis

UNIVERSITÉ

DE GENÈVE

**Carlo Alberto Fenoglio** Chip design

#### Lorenzo Paolozzi

Analog electronics

#### Magdalena Munker

· Laboratory test

- Stefano Zambito · Laboratory test Data analysis

#### Théo Moretti Laboratory test

- Chiara Magliocca · Laboratory test

- · Data analysis

Sensor design

#### **Didier Ferrere**

- System integration

- Laboratory test

#### Board design

RO system

#### Sergio Gonzalez-Sevilla

- System integration

- · Laboratory test

#### Stéphane Débieux

- · Board design

- RO system

#### Main research partners:

Marzio Nessi

Roberto Cardarelli **INFN Rome2 & UNIGE**

Holger Rücker IHP Mikroelektronik

### Swiss National

Sinergia

ATTRACT

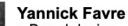

### **Gain measurements**

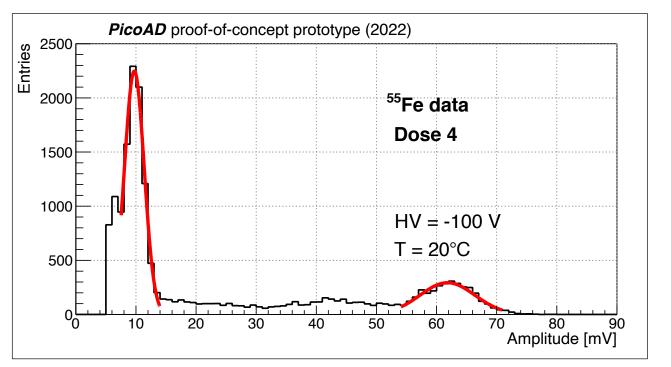

#### X-rays from <sup>55</sup>Fe radioactive source:

- ➤ mainly ~5.9 keV photons

- ➤ point-like charge deposition

#### Characteristic double-peak spectrum

- > photon absorbed in drift region

- > holes through gain layer & multiplied

- first peak in the spectrum

- > photon absorbed in absorption region

- > electrons though gain layer & multiplied

- second peak in the spectrum

MONOLITH

erc

European Research Counci

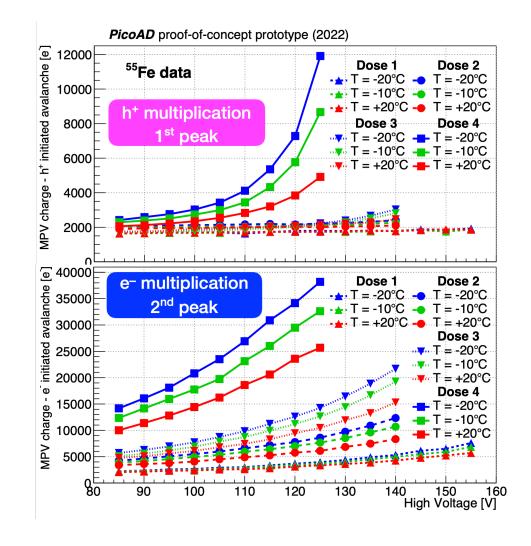

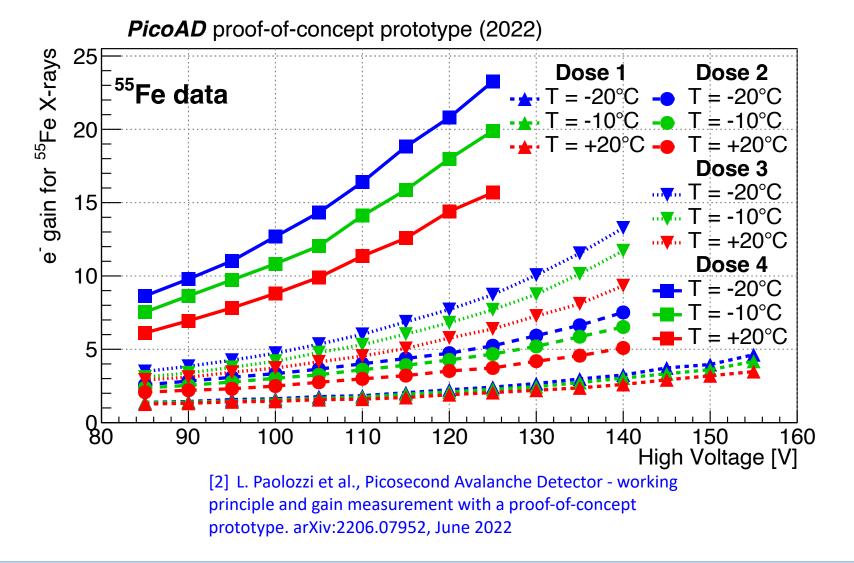

### **Gain measurements**

# Average amplitudes of h+ and e- gains extracted via gaussian fit around local maxima

Assumption of no gain multiplication when:

- photon absorbed in drift region

- Iowest voltage (85 V)

- Iowest dose (dose 1)

# **Detection effieciency**

CERN SPS Testbeam: 180 GeV/c pions PicoAD proof-of-concept prototype (2022)  $V_{th} = 4 \text{ mV}$ ; HV = 125 V; Power = 2.7 W/cm<sup>2</sup> Track position y [mm] Efficiency Track position y [mm] 0.9 3.1 3.1 0.8 0.99 3.05 0.7 3.05 0.6 0.98 3 3 0.5 0.4 0.97 2.95 2.95 0.3 0.2 0.96 2.9 2.9 0.1 2.85 0 2.85 0.95 -3.95 -3.9 -3.85 -3.8 -3.75 -3.7 -3.65 -3.8 -3.85 -3.75 -3.7 -3.65 -3.95 -3.9 Track position x [mm] Track position x [mm]

Apparent degradation at the external edges of the four pixels is due to the telescope pointing resolution of  $\approx 10 \ \mu m$

OA3

#### Selection of two triangles:

- representative of a whole pixel

- unbiased by telescope resolution

Efficiency

### **Gain measurements | Results**

A gain of  $\approx 20$  for <sup>55</sup>Fe X-rays is reached at HV = 120 V and T = -20 °C<sup>[2]</sup>

### **Testbeam results:**

Signal amplitude

# 2019 prototype

100µm pitch hexagonal pixels - 25µm depletion

MPW submission in 2019 funded by H2020

### **Four Matrices**

### 1. Active pixel

- Front end in pixel

- HBT preamp + driver (in pixel) + CMOS discriminator (outside pixel)

- 2. Active pixel v2

- HBT preamp + CMOS discriminator

- 3. Limiting amplifier:

- HBT preamp + HBT limiting amplifier

- 4. Double threshold:

- HBT preamp + two CMOS discriminators

### **Electronic Front-End DM0 | Layout Design**

# Preamp off-pixel AM1 | Layout Design

### **OutPreamp amplitude vs. Input Charge**

CERN

Group of 3 pixels as input of OR (red

and yellow)

The output are taken differential

ended from CML stage

Pixel0 to study frontend performance

29