### Rad-hard RISC-V SoC and ASIP Ecosystems Studies for High-Energy Physics Applications

Marco Andorno, on behalf of A. Caratelli, D. Ceresa, J. Dhaliwal, K. Kloukinas, R. Pejasinovic

2022/09/21

#### **Outline**

#### 1. Introduction

- Motivations and benefits

- R&D context and timeline

#### 2. System-on-Chip platform

- Open-source cores comparison

- SoC architecture

- Radiation hardening techniques

#### 3. ASIP (Application Specific Instruction set Processor) cores

- Introduction to ASIP Designer

- Optimization

# Introduction

### **Few definitions**

#### System-on-Chip

Full system on a single IC

Platinum Members

Vicrosemi

Rambus SAMSUNG A SiFive Western Digital

bluespec Ortus

Processor core + Memories + Peripherals + .

Microsoft

**RISC-V**

Open-standard instruction set  $\rightarrow$  No license fees

Few simple base instructions + Extensions (floating point, vector, ...)

**ASIP (Application-Specific Instruction set Processor)**

Custom instruction set tailored to the application

$\mathbf{R}$

### **Motivations and benefits**

The increase in design complexity calls for the need of a more abstract design methodology

#### Programmability

Allows retargeting an ASIC for a different application

algorithm within the same application

#### **Standard interconnect bus**

Promotes collaborativework

#### **IP blocks library**

Enables modularity with self-contained building blocks

Helps design reusability

An SoC platform provides all this, leading to

- Shift from design for an application to **design for resources**

- **Faster turnaround time**, both for design and verification

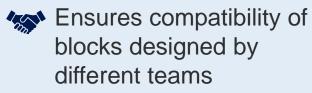

### **EP R&D context and timeline**

Activities within the framework of the EP R&D WP5 IC Technologies (5-year initial plan)

### **Rad-tol SoC ecosystems for HEP applications**

Fully radiation tolerant

# **System-on-Chip Platform**

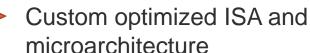

### Initial RISC-V cores and SoC platforms survey

### **Open-source cores comparison**

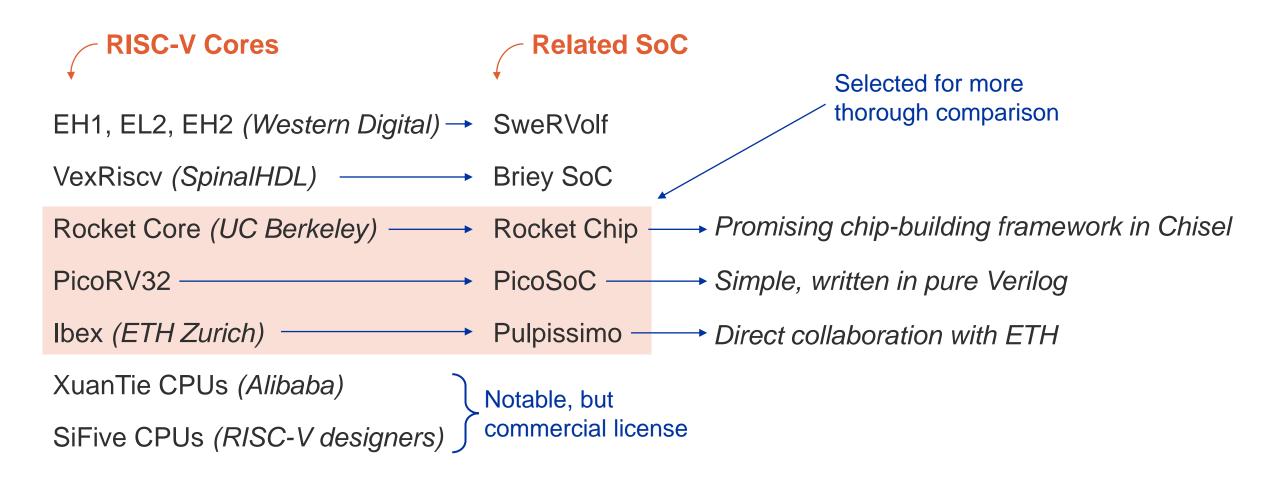

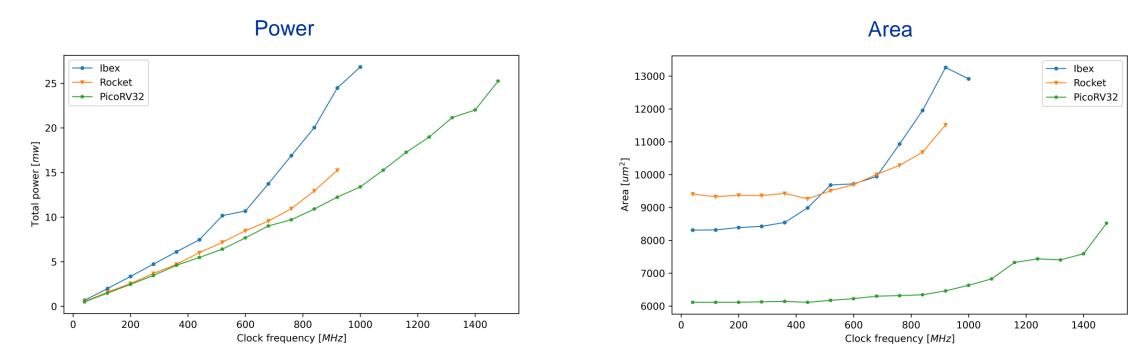

Three RISC-V open-source cores were evaluated initially:

|                  | lbex                                      | Rocket Core                                  | PicoRV32                                    |

|------------------|-------------------------------------------|----------------------------------------------|---------------------------------------------|

| Developers       | lowRISC (prev. ETH Zurich)                | <u>CHIPS Alliance</u> (prev. UC<br>Berkeley) | <u>Independent</u>                          |

| HDL              | SystemVerilog                             | Chisel (generates Verilog)                   | Verilog                                     |

| License          | Apache License 2.0                        | BSD 3-clause                                 | ISC                                         |

| ISA              | RV32I[E,M,C,B]                            | RV[32,64]I[M,A,F,D]                          | RV32I[E,M,C]                                |

| Pipeline         | 2-stage in order                          | 5-stage in order                             | None                                        |

| Memory interface | req/gnt<br>(separate for instr. and data) | TileLink<br>(adapts to AXI/APB)              | valid/ready<br>(shared for instr. and data) |

| CPI              | ≥ 1                                       | ≥ 1                                          | ~ 4                                         |

| Power*           | 6.11 mW                                   | 4.71 mW                                      | 3.97 mW                                     |

| Area*            | 8543.3 μm²                                | 9427.6 μm²                                   | 6141.9 μm²                                  |

\*Post synthesis results on TSMC 28 nm technology @ 320 MHz, using low, standard and ultra-high Vt transistors.

#### **Open-source cores comparison**

For control and monitoring applications speed is not a requirement  $\rightarrow$  selection based on **power consumption** and **area**

Post-synthesis results show a clear winner: **PicoRV32** was selected as the SoC core

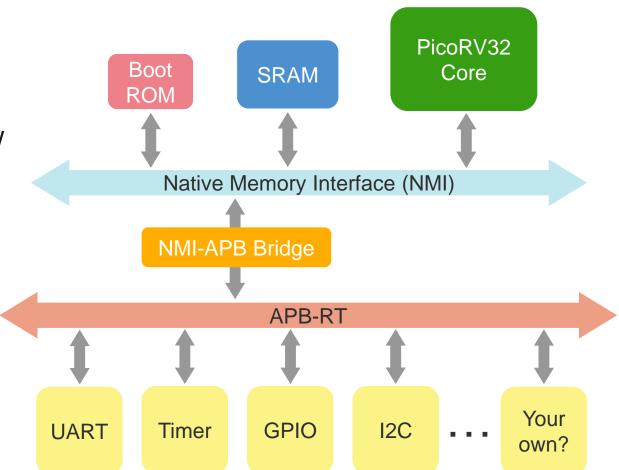

### **SoC** architecture

#### **Specifications:**

- Microcontroller-style (small, low power, low performance)

- RV32I instruction set (no multiplier/FPU)

- Radiation-tolerant

- APB-RT bus (from ARM AMBA) with a set of peripherals

- Simple programming interface

### **Radiation hardening techniques**

Triple Module Redundancy (TMR) where possible  $\bullet$

- Full TMR on the APB interconnect would be too much overhead, so we use **Hamming Encoding** for error correction/detection  $\rightarrow$  APB-RT

- Control signals are still fully triplicated (pwrite, psel, pstrb, pready, pslverr) •

- 32-bit data and address buses are encoded by byte with Hamming(13,8), to permit byte access operations

- 4 parity bits for single error correction 1 extra parity bit for additional double error detection

- Placement constraints on buffers to avoid multi-bit upsets

### SoC platform recap

#### Some possible applications:

- Slow control and monitoring on detector chips

- Standalone radiation-tolerant microcontroller

- Embedded microcontroller on a pixel chip to run routines like pixel-matrix calibration

What we're building now is a **demonstrator chip** to showcase this design paradigm

The goal for the future is to provide this as a **flexible**, **standardized and open platform** for designers in the community to **build and implement their own SoC**, with their own peripherals and custom hardware blocks.

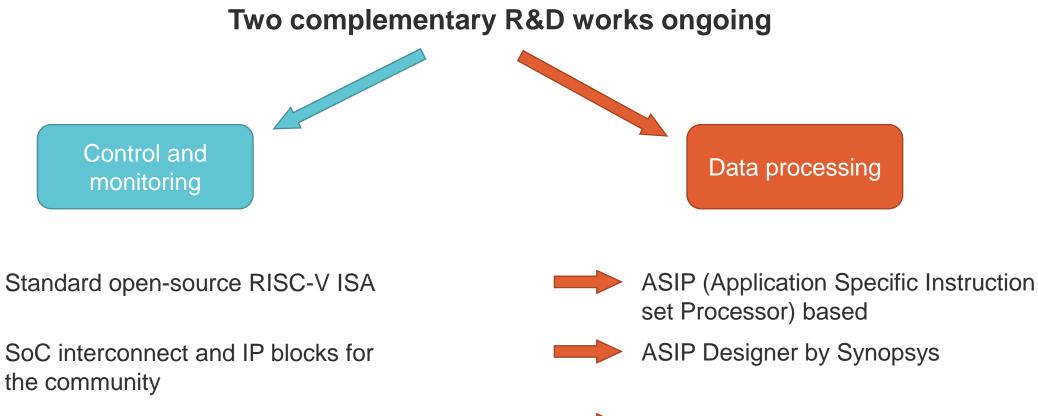

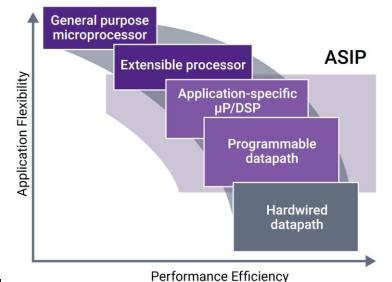

# **ASIP Cores**

(Application Specific Instruction set Processor)

### **Data processing requirements**

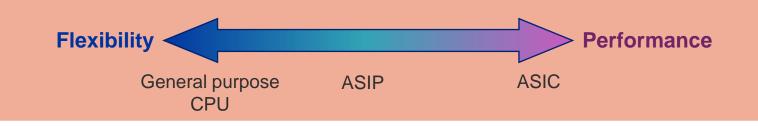

#### **Beyond a general-purpose microprocessor:**

- Maximize Performance/Power ratio

- Application specific solution

- Specialized hardware accelerators help offload the CPU.

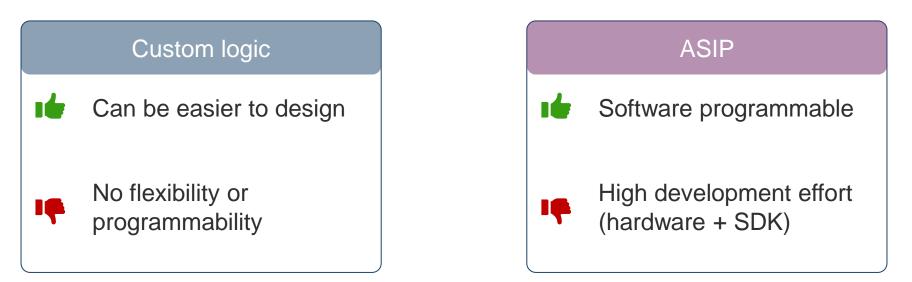

#### Two possibilities for them:

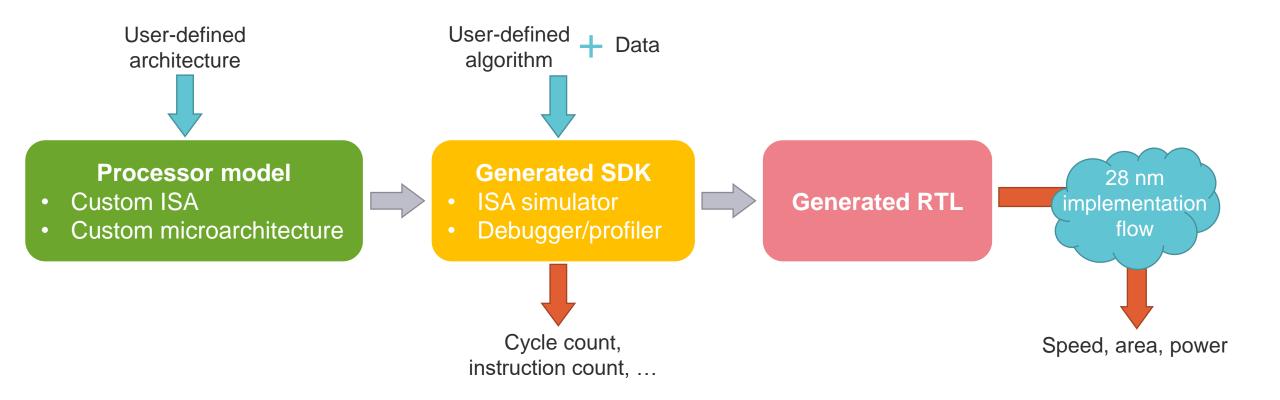

### **Introduction to ASIP Designer**

Tools like **Synopsys ASIP Designer** help with the hardware/software codesign of ASIPs:

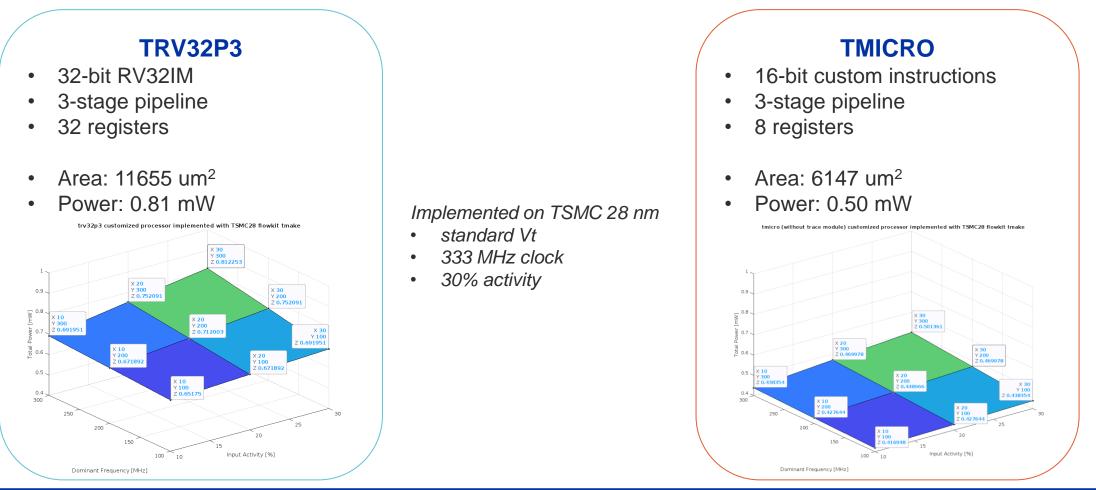

### **Core comparison - Implementation**

To showcase the workflow of ASIP Designer, two processor cores were compared using a clustering and filtering algorithm for pixel hit events:

### **Core comparison - Profiling**

#### **ASIP** Designer offers a number of profiling metrics:

| <ul> <li>Instructions</li> </ul>                                                                                                                  | 1Total cycle count:25602Report cycle count:25603Total instruction count:2144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>Functional units</li> </ul>                                                                                                              | 4       Report instruction count :       2144         5       Report instruction coverage :       71.64%         6       Total size in program memory:       2948                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| <ul> <li>Model coverage</li> <li><sup>8</sup> Function summary:</li> <li>Ocycles % of total Instruction % of total % Coverage Function</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Hazards                                                                                                                                           | 1       1188       46.41%       952       44.40%       55.86% sorting_by_clusters         3       617       24.10%       559       26.07%       100.00% fetching_by_ToA         4       322       12.58%       240       11.19%       100.00% output_to_IM         5       318       12.42%       288       13.43%       100.00% main                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                   | $\begin{smallmatrix} 5 \\ 6 \\ 104 \\ 104 \\ 106\% \\ 106\% \\ 106\% \\ 288 \\ 13.43\% \\ 100.00\% \\ 100.00\% \\ computing_CoG_Etot \\ comput$ |  |

Wemory accesses

### **Core comparison - Optimization**

#### From profiling data, several algorithm-specific optimizations were implemented:

#### Area and power reduction

- Resource optimization: removed

unused divider block

- Instruction pruning: profiling shows around 30% instructions are never used, so can be removed in the ISA

#### **Performance enhancement**

- Custom instructions: memory accesses are always of 2 or 3 words at a time, so defining new instructions to read multiple words at once improves latency

- Dedicated accelerators: a MAC unit was introduced to speed up repetitive operations

- ASIPs offer a good tradeoff between the flexibility of a general purpose processor and the performance of custom logic.

- Tools can help deal with the complexity of designing the hardware and software together and optimizing the architecture.

- ASIPs allow to add on-chip data processing capabilities to pixel chips, detector electronics and SoCs in general.

# Conclusions

### **Summary and conclusions**

We have demonstrated a workflow for both control and data processing applications:

General-purpose RISC-V processor

Standard SoC interconnect bus

Radiation tolerance techniques

Application-specific ASIP

Application-optimized ISA and architecture

Example of on-chip data processing solution

#### Main takeaway

Designing for resources and programmability are keys to **cost-effective**, **collaborative** and **fast** silicon design.

# Thank you!

home.cern