Fast prototyping of Front End ASICS and validation of associated DAQ with a Cadence Protium platform.

# **<u>G.BERTOLONE</u>**, M.SPECHT, C.COLLEDANI, K.JAASKELAINEN, G.CLAUS, H. SCHOTT, H.PHAM, Y.ZHAO

TWEPP 2022 BERGEN 19-23/09

Institut Pluridisciplinaire Hubert Curien, 23 rue du Loess, 67037 Strasbourg, France

Contact: gregory.bertolone@iphc.cnrs.fr

ASICs designed for HEP embed always more digital components and require complex and critical verifications. Prototyping enables implementations of digital part of ASIC in programmable Abstract components such as FPGA. Interactions with external devices such as DAQ, micro-controller or other FPGA are then possible. Debugging of internal firmware or complex stimuli becomes easier and faster than time-consuming simulations.

Cadence PROTIUM is an FPGA based solution that allows ASIC designers to easily and automatically prototype the RTL code of their ASIC. At IPHC, it was used to do the functional validation of several ASICs and DAQ system.

# **ASICs Prototyping**

## Principle

Map ASIC RTL code into FPGAs

### What is Cadence PROTIUM platform?

**PROTIUM** = FPGAs board + dedicated Software (Cadence + Xilinx Vivado)

PC with

## Why IN2P3 chose PROTIUM?

PROTIUM keep the original ASIC RTL code  $\bullet$ => **no need to modify** the ASIC code to fit FPGAs

#### Benefits of FPGA prototyping:

- **Pre-silicon verification**

- Firmware/Software verification

- Connect hardware

- Cheaper than multiple ASIC respin

+ extension boards for hardware connections (RAM, I/O, FMC,...)

| software | PF | FPGAs<br>with ASIC RTL<br>code | e<br>• • • • | 2 | tension<br>oards | NATIONAL<br>INSTRUMENTS | External<br>hardware |

|----------|----|--------------------------------|--------------|---|------------------|-------------------------|----------------------|

| software |    |                                |              |   |                  | T                       |                      |

PROTIUM FPGAs = Xilinx Ultrascale VU440 (equivalent to 2 Virtex 7)

architecture

#### Easy to use => no need of special FPGA skills

- Accelerates the DAQ and slow control development

- **Black Box** flow:

- ASICs and IPs (custom or Xilinx) connected inside the same FPGAs

- **Allow system integration** (see F.Morel's poster)

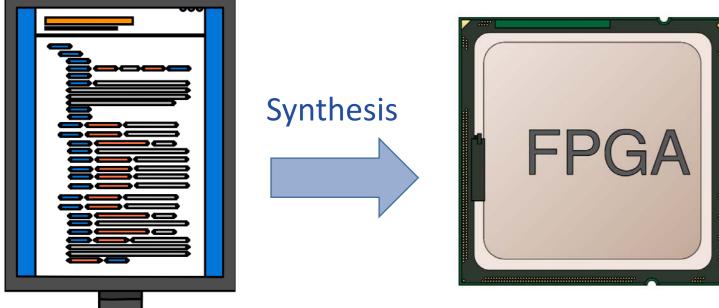

# Verification with PROTIUM of digital parts of MIMOSIS 1 & 2

|   | + registers                |   | Data flow        |  |  |  |  |  |  |

|---|----------------------------|---|------------------|--|--|--|--|--|--|

|   |                            |   | management       |  |  |  |  |  |  |

| ł | Sequencer                  | J | SRAMs (~1M bits) |  |  |  |  |  |  |

|   | Clocks                     |   | serializer       |  |  |  |  |  |  |

|   | generator                  |   | Serializer       |  |  |  |  |  |  |

| ' |                            |   |                  |  |  |  |  |  |  |

|   | Pad Ring                   |   |                  |  |  |  |  |  |  |

|   | 1 to 8 LVDS links @320 MHz |   |                  |  |  |  |  |  |  |

### **MIMOSIS 1 & 2**

• Designed for the **CBM-MVD** in a **180 nm CIS** technology • Reticle size ASIC (17x31 mm<sup>2</sup>), 0,5 million of pixels (digital logic in each pixel)

• MIMOSIS1 produced in 2020

• MIMOSIS2 Taped Out in Sept 2022 with Clocks, reset and FSM fully tripled with CERN TMRG tool

**I2C update and debug for MIMOSIS2**

Bug detected in the I2C watchdog during the test of

Same PROTIUM scripts and slow control

**steering** for MIMOSIS1 and MIMOSIS2

in PROTIUM for MIMOSIS2

♦ correction and validation of the **new RTL** code

PROTIUM S1 @IPHC

A common platform for designers & test engineers

MIMOSIS1

Slow Control

Steering

**PROTIUM FPGA**

PROTIUM

#### **PROTIUM Memory board:**

- Store stimuli and results

- Emulates the matrix

(1 FPGA instead of 6 needed)

Data readout test :

• **Standard mode** (in development)

Seplace pixel matrix with PROTIUM

memory board

• Test mode (ASIC feature)

Sinjection of stimuli into the bottom

periphery via dedicated I2C registers.

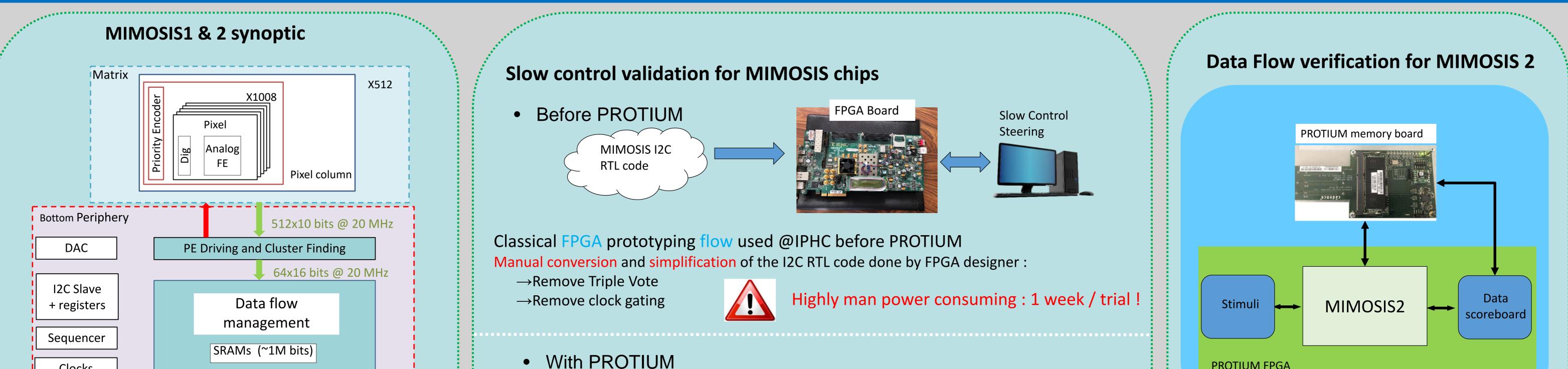

# Validation of PICMIC0 system before Tape Out

MIMOSIS RTL modules

(without the matrix)

$\rightarrow$ Keep the original ASIC RTL

$\rightarrow$ Automated TCL scripts

Simulation vs Prototyping

run time test

**UVM** Testbench

63 min

**PROTIUM** prototyping flow

code

~2 hours / trial

1300 I2C

R/W access

(all MIMOSIS1

registers)

Runtime needed

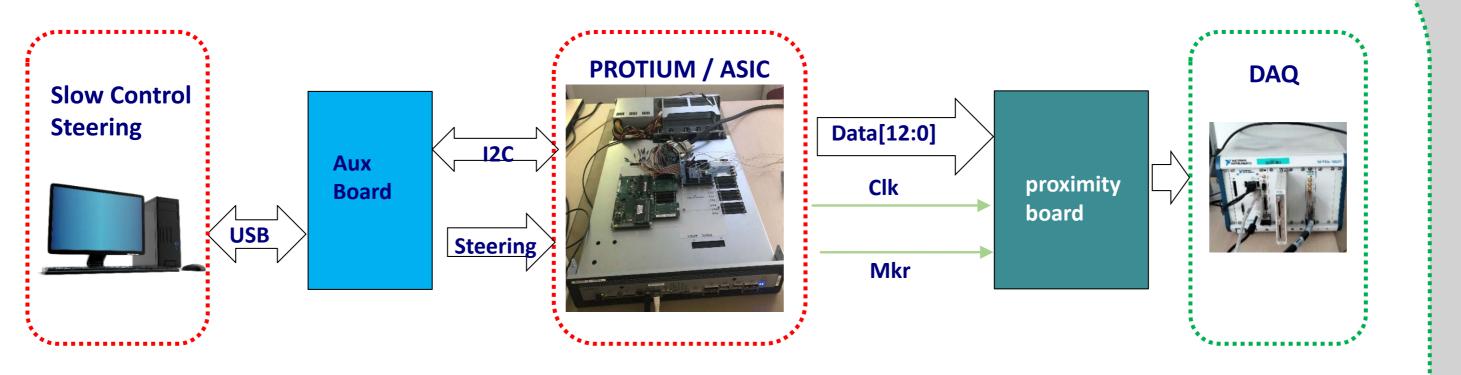

DAQ system chain for PICMICO

PROTIUM

hardware I2C

**DAQ** software

1,8s

**Benefits from PROTIUM usage** on IPHC projects

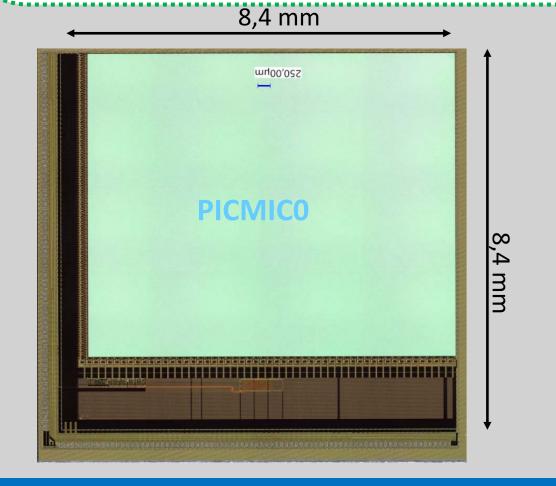

### **PICMICO ASIC**

#### • IN2P3 collaboration (IPHC & IP2I)

• Encodes hits positions from an Micro Plates Chamber Detector (MCD)

• Each pixel embedded an I2C register for hit emulation

• Produced in **Q2 2022** (180 nm CIS)

**Benefits of PROTIUM flow** for this project :

- Early development of DAQ and slow control

- ASIC functional verification with external hardware system

- I2C chain driven by an external **Arduino** (DAQ software and hardware extensive checks

with 1 million R/W cycles in less than 3 hours )

- Data readout tested with DAQ and data analysis software  $\bullet$

- Same software and hardware for ASIC validation and PROTIUM flow

• **ASIC Verification** improved before Tape Out

Early development of DAQ and slow control

systems

**Common platform** between ASIC designers

and test engineers

$\square$  man power cost,  $\neg$  project closure

- High capacity FPGAs available

- Reticle size MAPS with full pixel matrix.

- Embedded software such as RISCV dev.

- IA development such as smart trigger

We acknowledge S. Imbert Principal AE at Cadence for his strong support