# Electronics for the far-forward CMS muon detector upgrade, ME0

# Joseph Carlson on behalf of the CMS Muon Group

**TWEPP 2022**

Contact: jcarlson@physics.ucla.edu

## Introduction

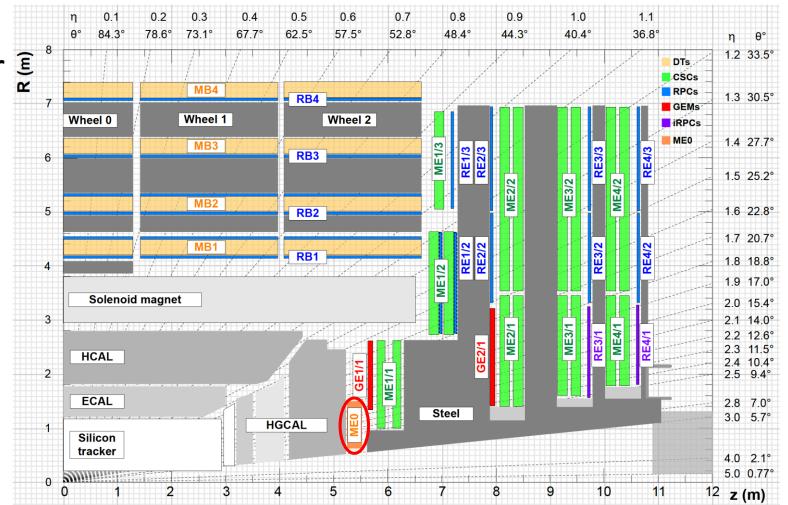

#### **ME0** Detector:

- In each endcap, arranged in a wide planar 🗐 ring with inner radius  $\approx 0.6$  m and outer radius  $\approx 1.5$  m, centered on beamline

- 6-layer triple Gas Electron Multiplier (GEM) stacks

- Each chamber covering  $\Delta \varphi = 20^o$  and  $\Delta \eta = 0.8$  (divided into 8 partitions in  $\eta$ )

- 384 radial strips in each  $\eta$  partition

- ME0 electronics designed to deal with high data rates and be radiation hard

#### **Motivation:**

- Improve muon reconstruction at high luminosity (HL-LHC) by supplementing other muon subsystems untill  $|\eta| = 2.4$

- Extend muon acceptance to  $|\eta| = 2.8$

Figure 1: Quadrant of CMS experiment highlighting ME0 (2.0  $< |\eta| < 2.8$ )

CMS Collaboration, The Phase-2 Upgrade of the CMS Muon Detectors, Technical Report CERN-LHCC-2017-012, CMS-TDR-016 (2017)

## **Electronics Testing**

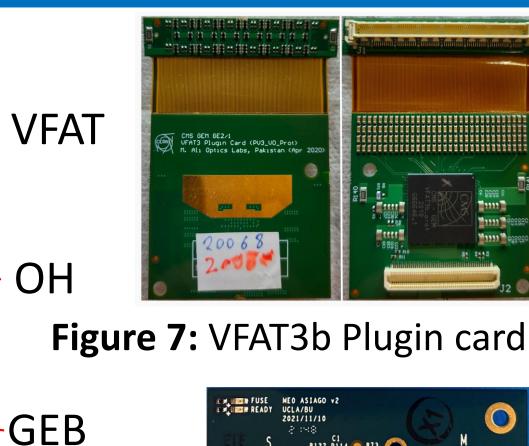

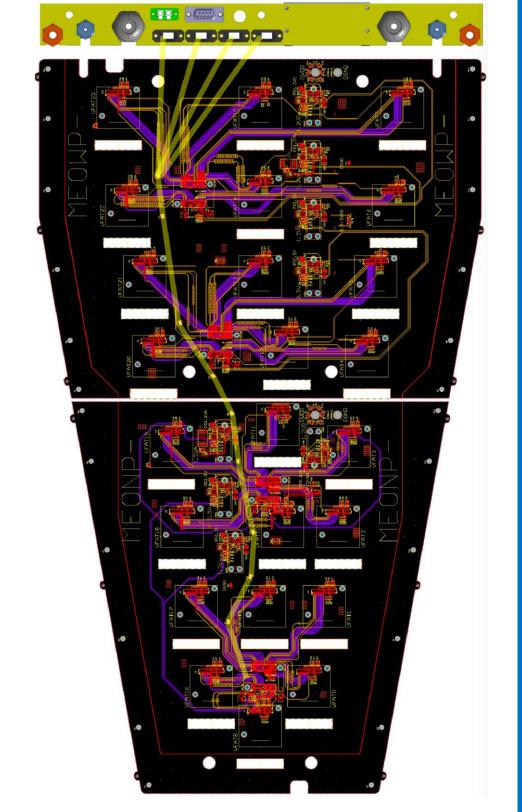

Chamber Readout Board

Figure 6: Picture of

ME0 front-end

electronics

halogen-free PCB, optimized fiber routing and powering configuration **VFAT3b:** all wafers for ME0

**GEB:** Future iteration with

**Current Status and Plans:**

produced and tested for all MEO

Pre-production/prototypes

electronics

produced, packaging expected in 2022. Slight re-routing.

OH: tested reliable optical and electrical links with bit error ratio  $< 10^{-12}$ )

Backend: tested with ME0 front-end electronics. More boards for teststands coming

Figure 8: Pre-production ME0 OH

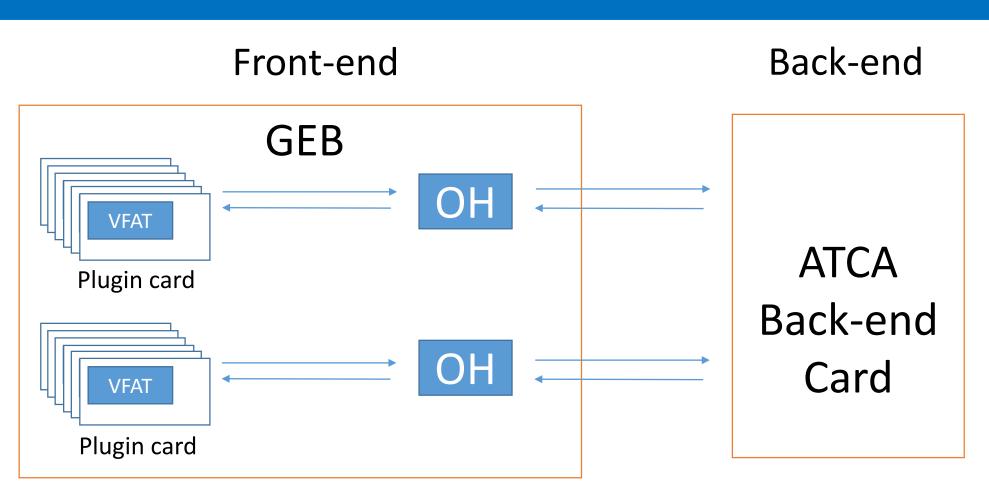

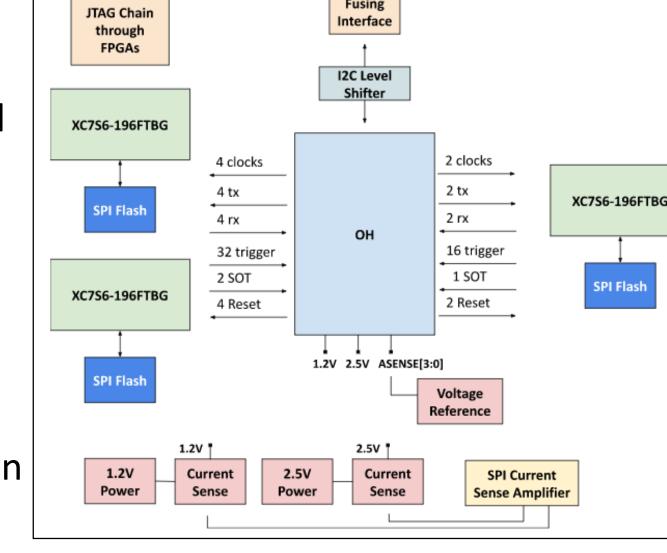

## ME0 Electronics Overview

Figure 2: Block diagram for ME0 front-end and back-end electronics

- 128 strips per VFAT plugin card

- 6 Plugin cards per OH

- 2 OHs per GEB

- 2 GEBs per layer

6 layers per stack 18 stacks per endcap

2 endcaps in CMS

**GEB: GEM Electronic Board** OH: Optohybrid

Figure 3: Design of the GEB

### ATCA based back-end system will be used for MEO (also for GE2/1 and CSC):

- Has FPGA for online computation and transceivers to interface with VTRx+

- 2 MEO stacks per card, 18 cards in total

- Supports high DAQ data rate of 700 Gb/s (all raw trigger hits from OH)

### GEB (by PKU) is fixed to the chamber readout board to which the VFATs are connected:

- Responsible for routing the signals from the VFATs to the OH

- Distributes power to the VFATs and OHs from 3 DC-DC converters per GEB

- 1 wide and 1 narrow GEB per layer

#### bPOL12V DC-DC converters (by CERN) will be used on the GEB for powering:

- Provide 1.2V and 2.5V to VFATs and OH

- Carrier board for bPOL12V being designed for MEO (by ULB)

### VFAT3b (by INFN Bari, CERN) is the frontend chip to read out the strips on MEO (also used in GE1/1, GE2/1):

- 128 channel chip, reads charges from the sensor, providing tracking and trigger data

- Radiation resistant

- Packaged in a plugin card with protection circuit

for trigger and control

# VFAT3 SRAM1 Control Logic + Data Formatter Slow Control (Registers & logic)

Figure 4: VFAT3b block diagram

#### Optohybrid (by UCLA) is the readout Connector 1 to GEB interface for 6 VFATs on the ME0 GEB: 2 lpGBT chips and 1 VTRx+ transceiver on each OH board No FPGA to ensure radiation hardness, tx (10.24 Gbps) tx (10.24 Gbps) data sent to back-end without IpGBT S **IpGBT M** compression 40 MHz refclk Electrical links to VFATs at 320 Mb/s High speed optical links at 10.24 Gb/s for data transmission and at 2.56 Gb/s

Figure 5: Block diagram for ME0 OH

**Connector 2 to GEB**

#### QUESO (by UCLA) tester board for the MEO OH.

- QUESO: QUalification of Electrical Signals and Optics

- FPGAs on QUESO loopback a pseudo random bit sequence (prbs) signal to the OH

- prbs goes through unique bitmask on each electrical link

- Data is then serialized by the OH and sent to the backend over the optical link for validation

- Testing to be done for all 1000 OH produced for ME0

Figure 9: QUESO Block Diagram

## Latest Status and Results from ME0 Integration

Multi-layer ME0 stack test stand being integrated at CERN:

- Using all the latest ME0 electronics available

- First test of simultaneously operating multiple ME0 layers

- Will be important for firmware testing including stub finding

Figure 10: Picture of the MEO stack at CERN

#### **Current Status and Test Results:**

- Currently has 2 layers (more layers to be added soon)

- Half of each layer assembled due to constraints in availability of electronics

- Successfully tested the operation of all VFATs and OH on 2 layers, mainly:

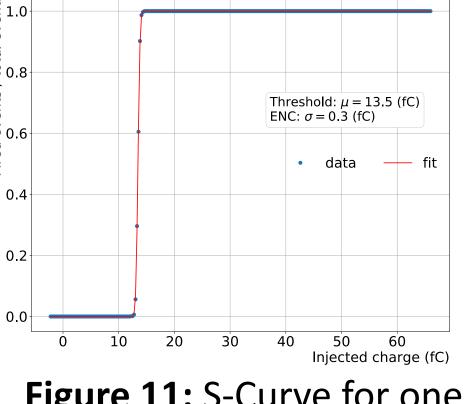

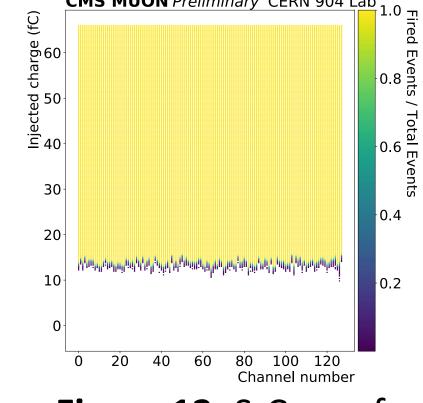

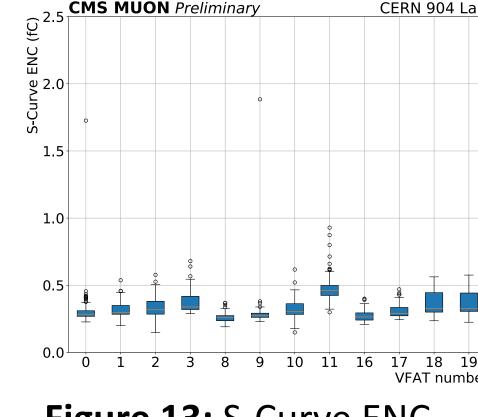

- Equivalent noise charge (ENC) measurements for the data links using S-Curves with injected calibration signals – results look good

Figure 11: S-Curve for one channel with data and fit results on one VFAT plugin card on a MEO detector

Figure 12: S-Curve for all 128 channels on one VFAT plugin card on a MEO detector

Figure 13: S-Curve ENC distributions for all 128 channels for 12 VFATs on a ME0 detector

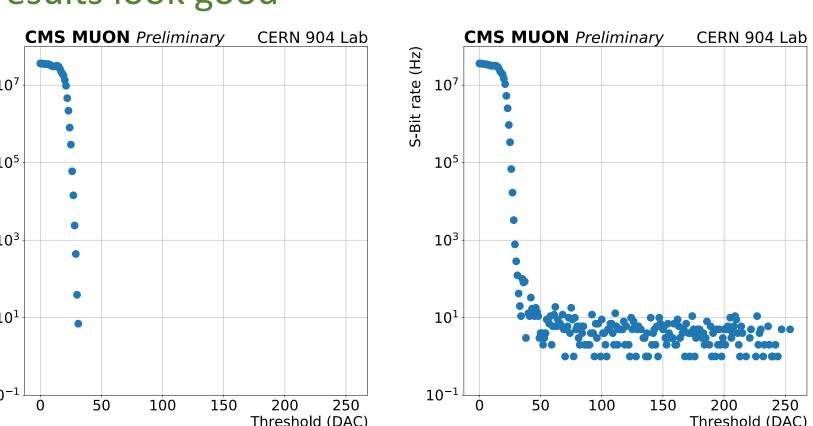

The noise rate measurement of the trigger links (S-bits) by scanning against the threshold setting in the VFAT – results look good

Figure 14: S-bit noise rate vs threshold from all 128 channels on one VFAT on a ME0 detector without (left) and with (right) application of high voltage across the GEM foils

#### **Planning for ME0 Electronics:**

Complete the testing of all MEO electronics after integrating with chamber