# **RD50-MPW3: Design and initial laboratory** evaluation

Chenfan Zhang\* on behalf of the RD50 CMOS group \* Department of Physics, University of Liverpool <u>chenfan@hep.ph.liv.ac.uk</u>

RD50 41st workshop Seville, 29 Nov. - 2 Dec. 2022

### Introduction

- CERN-RD50 CMOS Working Group make efforts in:

- ► ASIC design;

- ► TCAD simulations;

- DAQ development;

- ► Chip performance evaluation.

- Currently involves 17 institutes.

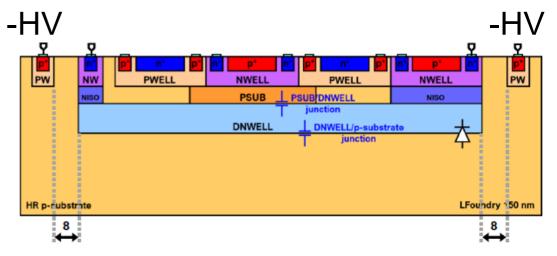

- A series of HV-CMOS prototypes have been developed using LFoundry 150 nm HV-CMOS process.

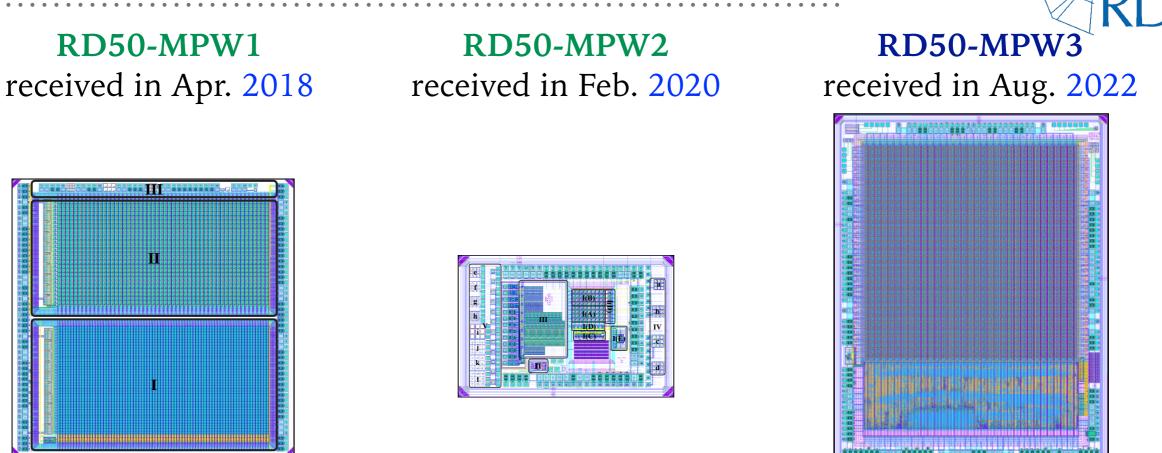

## **RD50 HV-CM0S Prototypes**

- **RD50-MPW1**: test the LF150 process, low  $V_{BD}$  (55 V) and high  $I_{Leak}$  (~  $\mu$ A).

- RD50-MPW2: high V<sub>BD</sub> (130 V), low I<sub>Leak</sub> (~ nA) and fast analog front-end. Small pixel matrix (8×8), no in-pixel digital readout, no digital readout periphery.

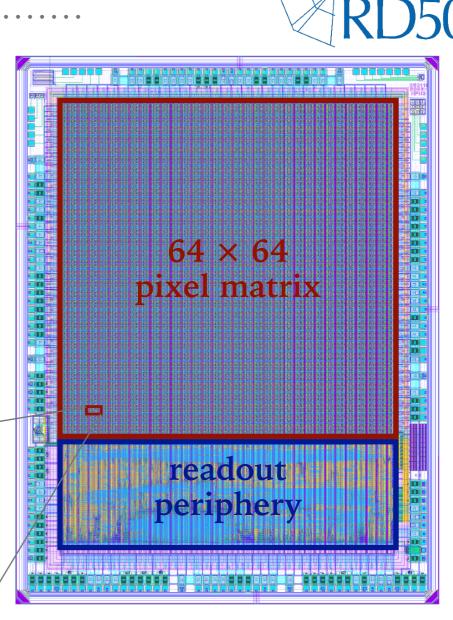

- RD50-MPW3: larger pixel matrix (64×64) with in-pixel digital readout and advanced peripheral readout.

- This talk gives an overview description of RD50-MPW3 and presents its initial laboratory evaluation results.

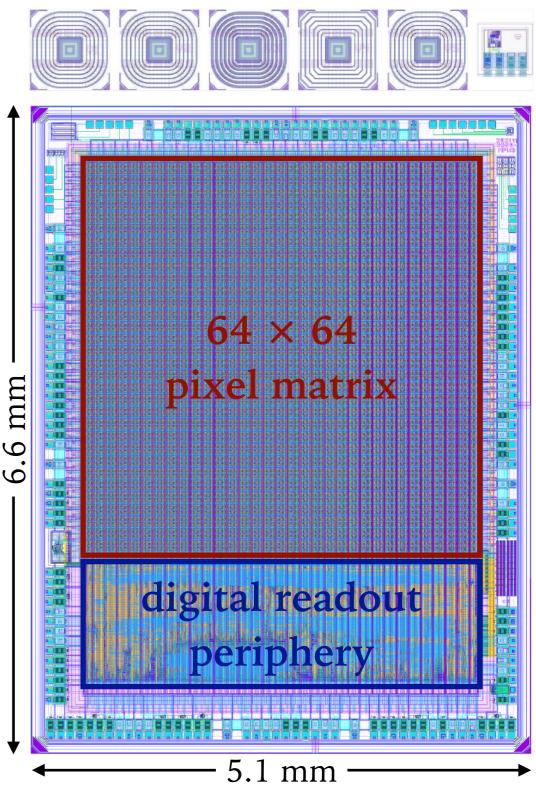

### **General details of RD50-MPW3**

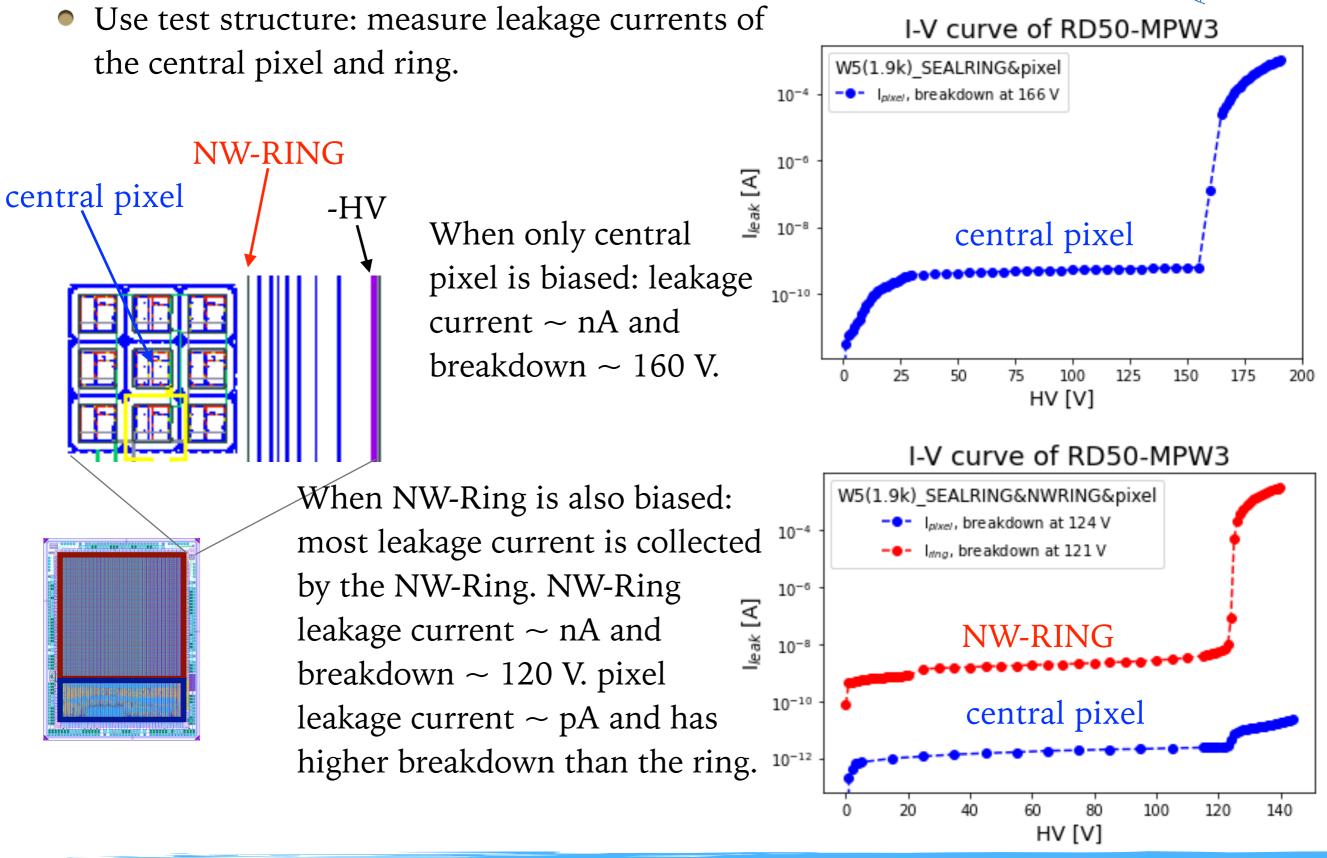

- **RD50-MPW3** is designed based on lessons learnt from the previous two chips:

- ► same chip ring for high V<sub>BD</sub>; low I<sub>Leak</sub>;

- ► fast analog front-end.

- Mainly composed of a pixel matrix, a digital readout periphery and test structures.

- Wafers with different resistivity (3 × 1.9 kΩ·cm, 1 × 3 kΩ·cm and 1 × 10 Ω·cm).

- New features in RD50-MPW3:

- double-column architecture;

- ► FE-I3 style digital readout circuits;

- optimised digital periphery for effective chip configuration and fast data transmission.

- **RD50-MPW3** was submitted for fabrication in Dec. 2021, and was received in Aug. 2022.

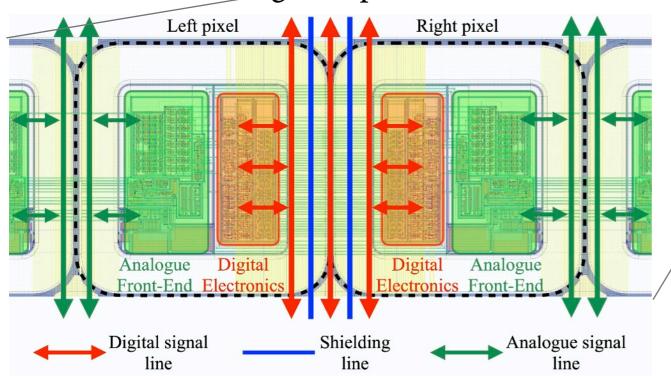

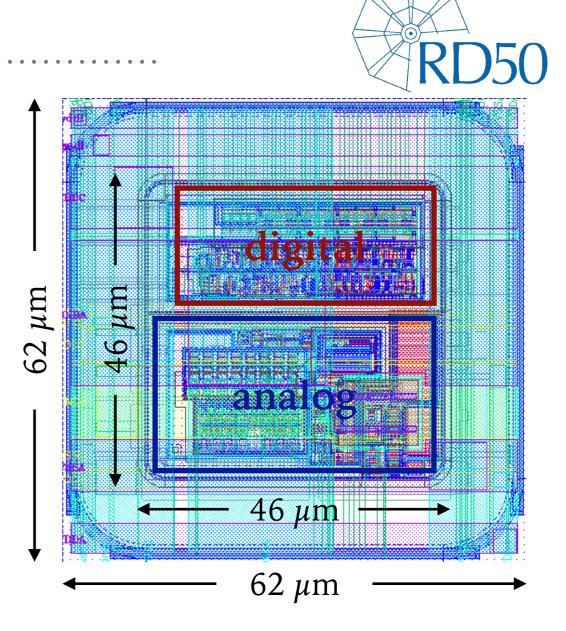

## **Pixel Matrix**

- 64 columns are organised into 32 double columns.

- To save area and avoid crosstalk between digital and analog signals:

- Digital signal lines are placed in the middle of each double column;

- Analog lines are placed between double columns;

- Shielding lines (grounded) are inserted between digital signal lines to minimise coupling.

- A power grid using Metal 5 and Metal 6 is used to minimise IR voltage drop.

- Time stamps of the rising and trailing edges are recorded for

Time of Arrival (ToA) and

Time over Threshold (ToT).

- More details in <u>Chenfan's talk</u> <u>in 40th RD50 workshop</u>.

- Both analog and digital electronics are included inside each pixel.

- Analog and digital circuits are placed into separate deep p-wells and have different power lines to minimise crosstalk noise.

- Substrate is biased to high voltage from the front side.

# **Readout Periphery**

8 bits per reais

Conf rea Pix0

Conf reg Pix1

Conf reg Pix2

Conf\_reg\_Pix3 Conf\_reg\_Pix4

Conf reg Pix5

Conf reg Pix6

Conf\_reg\_Pix7 Conf\_reg\_Pix8

onf reg Pix15

Conf\_reg\_EOC

**Clock & Reset**

**I2C to Wishbone**

1 DCOL of Matrix

Output Pad

**Pixel Matrix**

I/O Pads, Power, Monitoring, ...

FOC

5

MUX

128 to 1

LE, TE, Pixel Address

(8 bit each)

Token Handle

s toke

EOC

CU

**TX Unit**

ext token

FIFO (24 bit \* 32)

EOC addres

EOC

TS

DATA OUT REG (32 bit)

- One End-Of-Column (EOC) per DCOL

- Configuration of pixels

- Pixel data readout + 32 words deep buffer\_

- Transmission Unit (TX Unit) for data transmission

- 128 words deep buffer (FIFO)

- Framing

- Encoding (Aurora 8bit-10bit)

- Serialization (Serial stream at 640MHz)

- Control Unit (CU) for reading out EOC buffers

- Controls data propagation from EOCs to TX Unit

- Global Timestamp (TS) Generator

- 8bit, running at 40MHz

- Gray-encoded to minimize activity on bus

- Clock and Reset Generator

- Dividing a fast (640MHz) clock into a 40MHz clock

- Clock multiplexer for optional external 40MHz

- Synchronizing the 2 external reset signals with both clock domains

- I2C to wishbone module

- Converts external I2C signals to internal wishbone control signals

(by Patrick Sieberer, more details in Patrick's talk in 40th RD50 workshop)

Chenfan Zhang (UoL) - RD50 41st workshop (Seville) 2022/12/02

TS

**Initial IV**

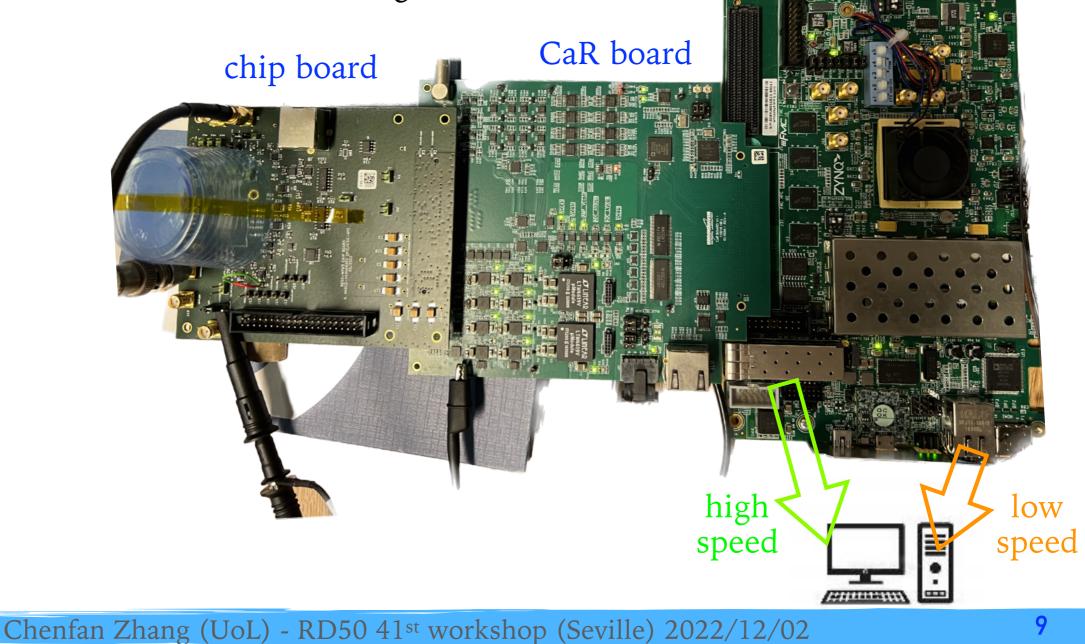

## **DAQ System**

- Based on Caribou DAQ system.

- Dedicated chip board.

- 2 data paths:

- ► high speed via UDP for data taking;

- ► low speed via network for monitoring.

Zync-7000

RD50

Based on a customised firmware.

• Software is based on Peary from Caribou.

- ► DAQ configuration.

- ► Chip configuration.

- ► Execute commands to run the chip.

#### Power Tab

| Power   | Misc     | Matrix |           |  |

|---------|----------|--------|-----------|--|

| P       | ower     | U [V]  | I_max [A] |  |

| 1 bl    |          | 0.9    | 3         |  |

| 2 p1v3  | vssa     | 1.3    | 3         |  |

| 3 p1v8  | _nw_ring | 1.8    | 3         |  |

| 4 p1v8  | _vdd!    | 1.8    | 3         |  |

| 5 p1v8  | vdda     | 1.8    | 3         |  |

| 6 p1v8  | vddc     | 1.8    | 3         |  |

| 7 p1v8  | vsensbus | 1.8    | 3         |  |

| B p2v50 | Ь        | 2.5    | 3         |  |

| 9 th    |          | 1.2    | 3         |  |

- ► Set bias and supply voltages.

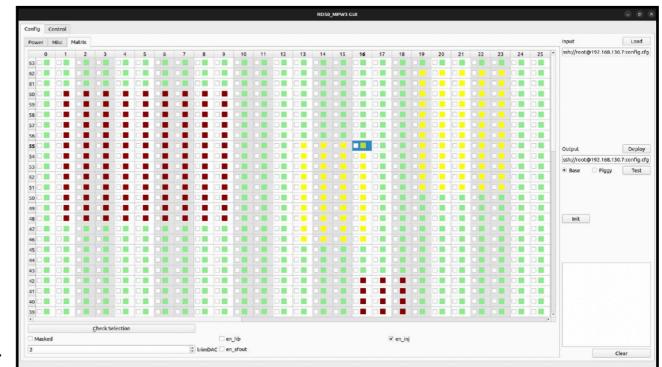

- ► Select pixels for configuration.

|                                                                                                                   |         | RD50_MPW3 GUI           |           |         |

|-------------------------------------------------------------------------------------------------------------------|---------|-------------------------|-----------|---------|

| anfig Control Monitor                                                                                             |         |                         |           | 1       |

|                                                                                                                   |         | root@192.168.130.7      |           | Connect |

|                                                                                                                   | <b></b> | config.cfg              | 3         | INFO    |

|                                                                                                                   |         | Get Cmds 4              | Configure | Power   |

| endinjections (args: 3)                                                                                           |         | 1 1.8 17                |           | Test    |

|                                                                                                                   |         | sendinjections 1 1.8 17 | *         | Reset   |

| 4:28:57.984 (INFO) [RD50_MPW3] Powering up                                                                        |         |                         |           | 1       |

|                                                                                                                   |         |                         |           |         |

| infigure 0                                                                                                        |         |                         |           |         |

| 4:29:01.069[ (BRROR) [RDS0_MPW3] opening calibration file 'calib_base.txt' failed<br>one configuring with dcol 31 |         |                         |           |         |

| 4:29:01.419 [INFO) [RD50_MPW3] finished configuring full matrix                                                   |         |                         |           |         |

| tCommands 0                                                                                                       |         |                         |           |         |

| st of commands available for device ID 0 - RD50_MPW3:                                                             |         |                         |           |         |

| test2 (args: 0)<br>readbackPixRegs (args: 1)                                                                      |         |                         |           |         |

| scurve (args: 2)                                                                                                  |         |                         |           |         |

| daqStop (args: 0)<br>testAbuffOut (args: 1)                                                                       |         |                         |           |         |

| readEEPROM (args: 1)                                                                                              |         |                         |           |         |

| resetChip (args: 0)                                                                                               |         |                         |           |         |

| sendinjections (args: 3)<br>calibrate (args: 2)                                                                   |         |                         |           |         |

| calibrate (args: 2)<br>configDcolDbg (args: 2)                                                                    |         |                         |           |         |

| writeEEPROM (args: 2)                                                                                             |         |                         |           |         |

| saveConfigTrace (args: 1)                                                                                         |         |                         |           |         |

| triggerUDPPack (args: 0)                                                                                          |         |                         |           |         |

| readbackEoc (args: 1)                                                                                             |         |                         |           |         |

| powerStatusLog (args: 0)                                                                                          |         |                         |           |         |

| monitorAlertStatus (args: 0)<br>configEocDbg (args: 2)                                                            |         |                         |           |         |

| configureClocks (args: 0)                                                                                         |         |                         |           |         |

| openShutter (args: 2)                                                                                             |         |                         |           |         |

| findPhase (args: 0)                                                                                               |         |                         |           |         |

| verifyConfig (args: 0)<br>testStuff (args: 2)                                                                     |         |                         |           |         |

| setReg (args: 2)                                                                                                  |         |                         |           |         |

| setChipType (args: 1)                                                                                             |         |                         |           |         |

| dagStart (args: 0)                                                                                                |         |                         |           |         |

| getReg (args: 1)                                                                                                  |         |                         |           |         |

| rifyConfig 0                                                                                                      |         |                         |           |         |

| one with double column 31 with Id 7                                                                               |         |                         |           |         |

| 4:29:25.806 (INFO) [RD50_MPW3] Great success :D                                                                   |         |                         |           |         |

| erifyCanfig 0                                                                                                     |         |                         |           |         |

| one with double column 31 with Id 7<br>4:29:44.520 (INFO) [RD50_MPW3] Great success :D                            |         |                         |           |         |

|                                                                                                                   |         |                         |           |         |

| endinjections 1 1.8 17 0<br>ent injection 00                                                                      |         |                         |           |         |

|                                                                                                                   |         |                         |           | Clear   |

|                                                                                                                   |         |                         | •         | 0.000   |

#### Matrix Config. Tab

#### Control Tab

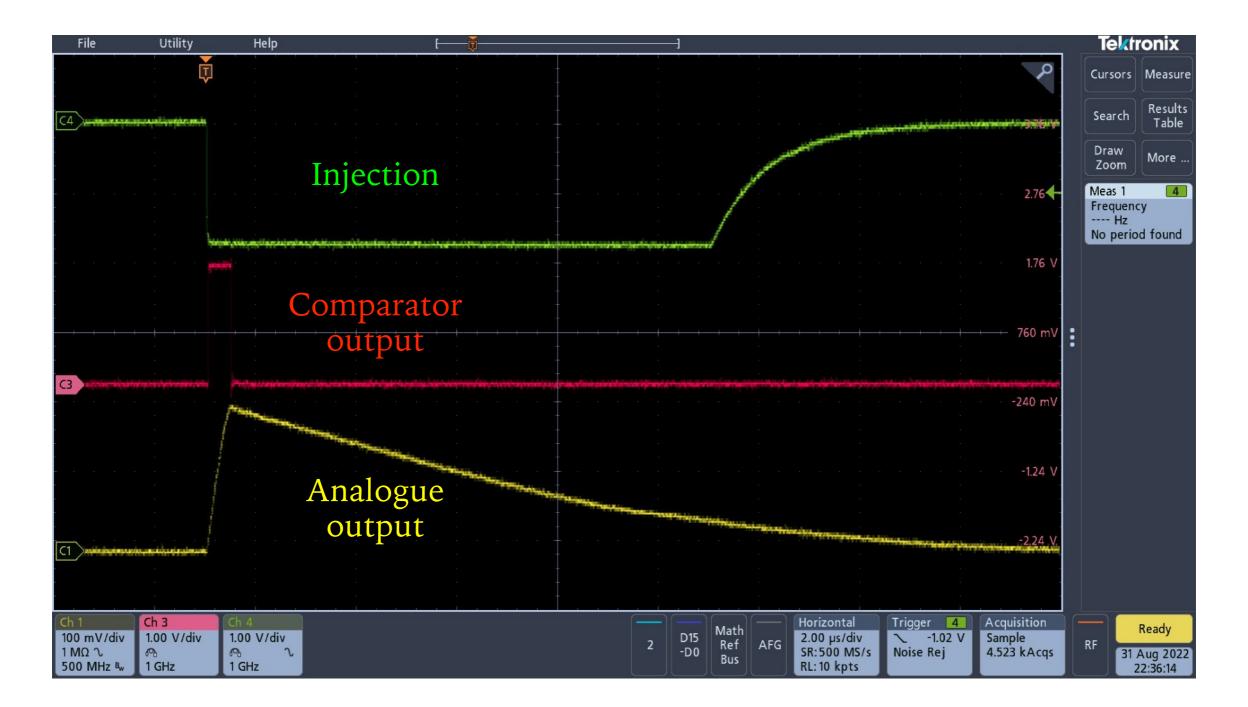

### **First Response**

RD50

- Send injection signal into pixel.

- Chip, DAQ and GUI are functioning.

# **High Noise**

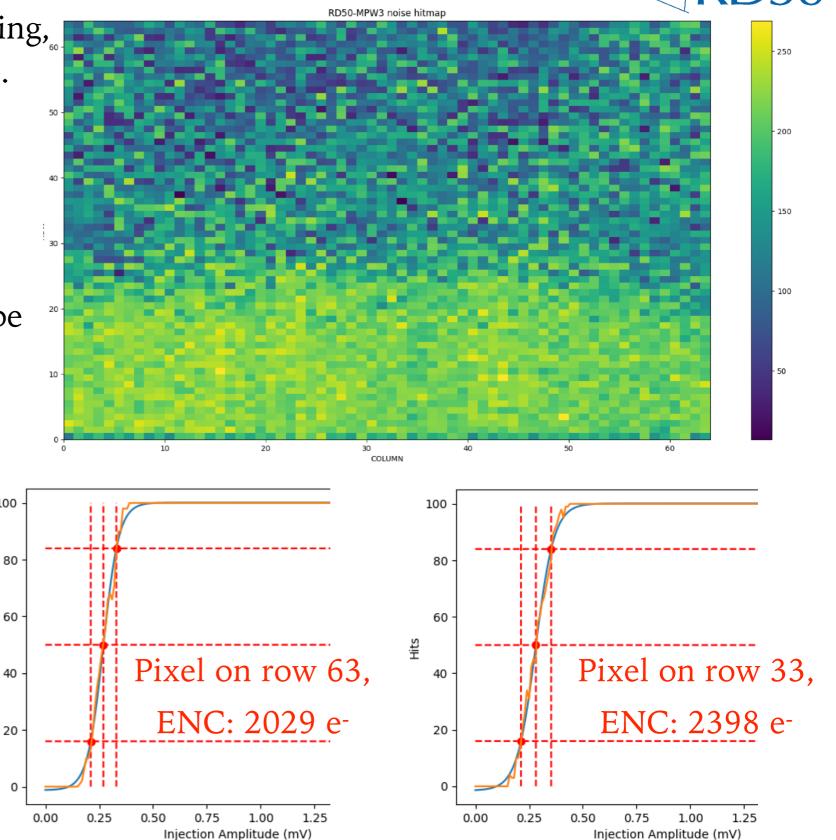

- When set the chip open-running, hits are recorded due to noise.

- Threshold = 300 mV above baseline voltage.

- Shutter window = 2 s.

- Bottom part of the matrix is more noisy. -> (noise might be from the digital periphery)

- S-curve shows pixel on the top (row 63) has noise of  $ENC = 2029 e^{-}$ , pixel in the middle (row 33) has  $ENC = 2398 e^{-1}$ .

- Investigating the high noise...

Chenfan Zhang (UoL) - RD50 41st workshop (Seville) 2022/12/02

100

Hits

40

## **Current Status and Future Plan**

- Need to slow down the clock to allow pull-down to work properly.

- Need to understand the high noise issue.

- More sophisticated lab measurements are on-going...

- Beam test has been taken at CERN SPS in October 2022, details will be presented in the following talk by Patrick.

- In the future potential submission:

- ► Fix the issues found in RD50-MPW3;

- ► Try thinning and backside processing.