# UKRI-MPWO: A proof-of-concept, backside biased only High Voltage CMOS pixel chip

E. Vilella, M. Franks<sup>1</sup>, J. Hammerich, N. Karim<sup>2</sup>, S. Powell, B. Wade, C. Zhang University of Liverpool <sup>1</sup>Now with ETH Zürich <sup>2</sup>Now with Leonardo UK Ltd *vilella@hep.ph.liv.ac.uk*

# **Motivation**

- To improve radiation tolerance of HV-CMOS sensors

- Increasing V\_BD

- With HV backside biasing

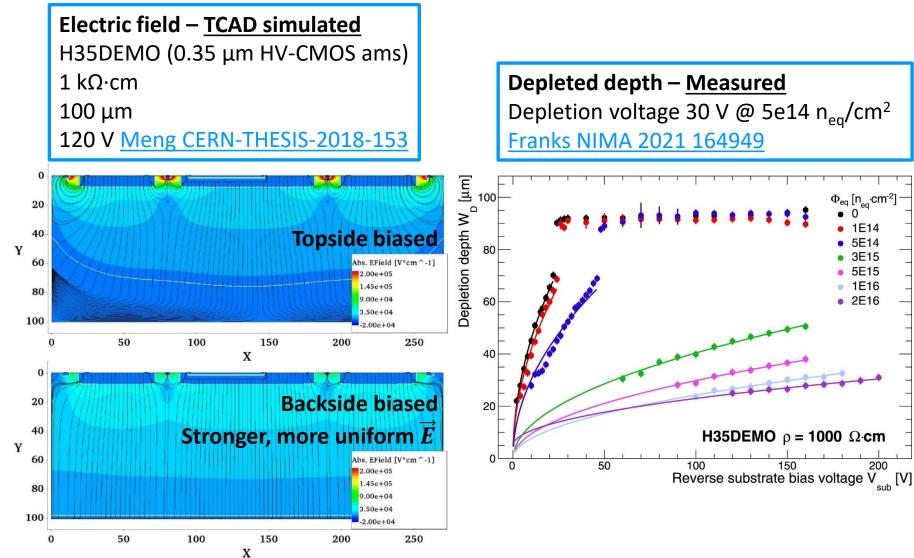

# State-of-the-art

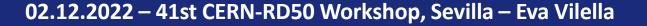

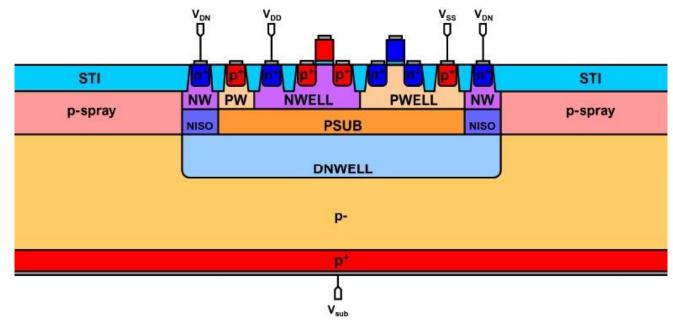

- 150 nm HV-CMOS LFoundry Traditional cross-section

- P-substrate/DNWELL sensing junction

- Topside p-type contacts to bias the p-substrate to HV

- Pixel readout electronics embedded inside DNWELL

e.g. RD50-MPWx pixel chips, hyperlinks: Vilella PoS(Vertex2019)019 Marco JPS Conf. Proc. 010008 (2021) Vilella NIMA 2022 166826

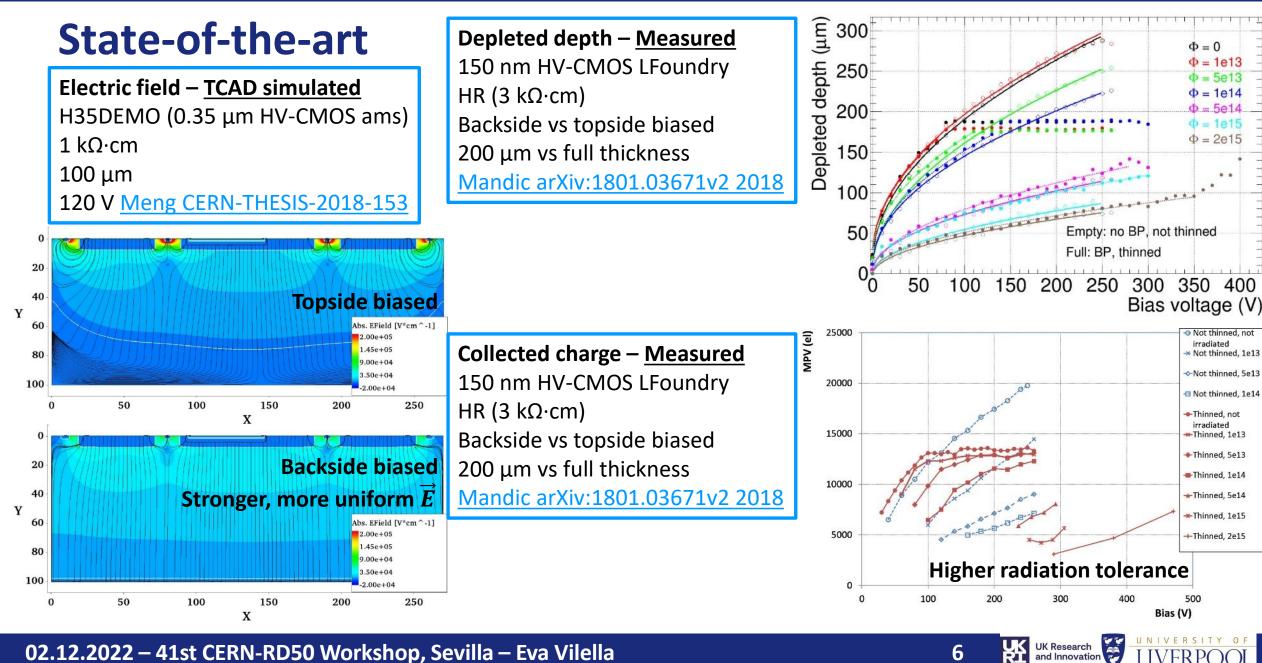

# State-of-the-art

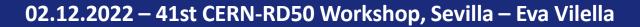

- 150 nm HV-CMOS LFoundry Optimised cross-section

- P-substrate/DNWELL sensing junction

- Backside p-type contacts to bias the p-substrate to HV, keeping topside p-type contacts

- Pixel readout electronics embedded inside DNWELL

e.g. H35DEMO, LF-CPIX, hyperlinks: <u>Franks NIMA 2021 164949</u> <u>Mandic arXiv:1801.03671v2 2018</u> <u>Meng CERN-THESIS-2018-153</u>

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

Δ

# State-of-the-art

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

ÄŘ 5

5E15

1E16

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

**UK Research** 6 and Innovation

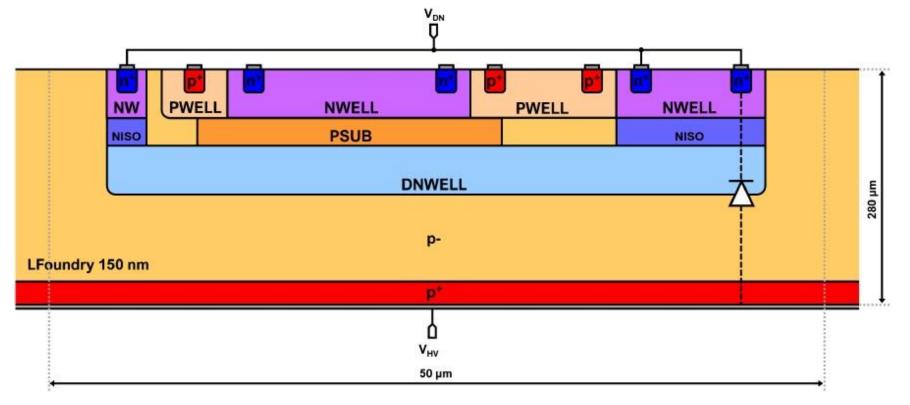

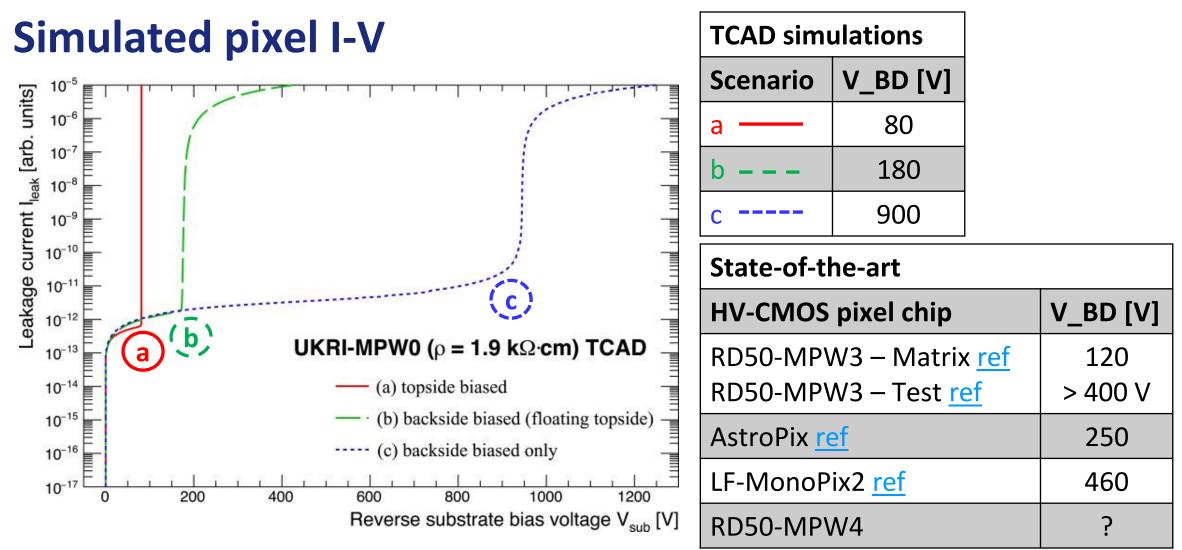

# Idea

## 150 nm HV-CMOS LFoundry – New cross-section

- P-substrate/DNWELL sensing junction

- Backside p-type contacts only to bias the p-substrate to HV

- Pixel readout electronics embedded inside DNWELL

- By removing the topside p-type contacts entirely  $\rightarrow$  V\_BD can be increased significantly

- These simulations form the basis for the UKRI-MPWO design (see <u>CERN-THESIS-2022-144</u>)

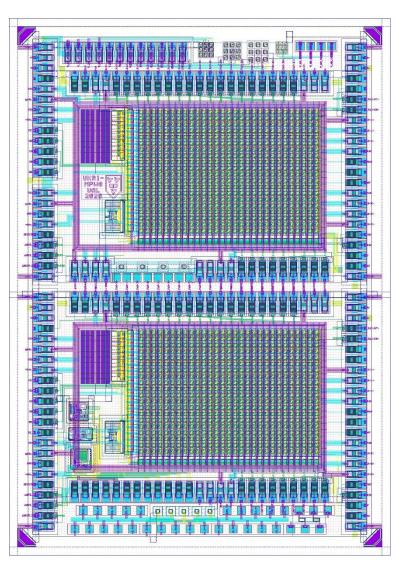

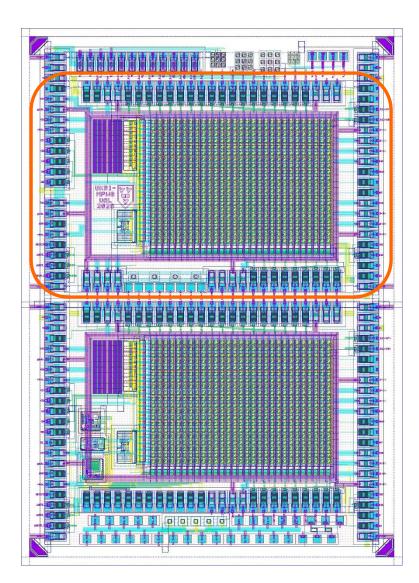

# **UKRI-MPW0 – Chip overview**

| Technology process    | 150 nm HV-CMOS LFoundry     |

|-----------------------|-----------------------------|

| Substrate resistivity | 1.9 kΩ·cm                   |

| Chip size             | 3.5 mm x 5 mm               |

| Fabrication type      | MultiProject Wafer (MPW)    |

| Submission date       | November 2020               |

| Chip thickness        | 280 μm (TAIKO grinding*)    |

| HV biasing            | From the chip backside only |

### \*TAIKO grinding (more info <u>here</u>)

- Leaves ring of silicon around the outer edge of the wafer

- Inner area can be made very thin (100  $\mu$ m)

- Ring is removed prior to dicing and assembly

- 4000 mesh

- Compatibility with backside processing

- Backside plasma etching for a less rough surface less and to etch the potential defects

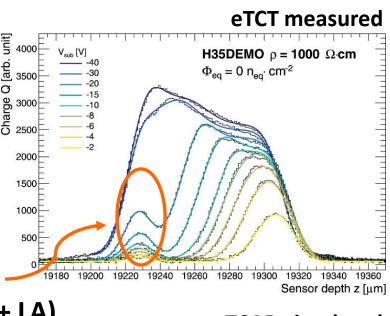

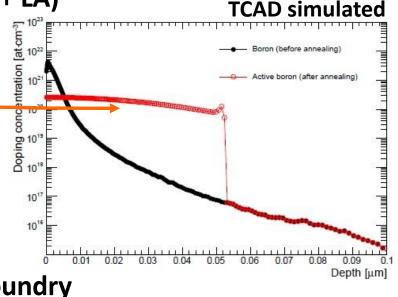

# **UKRI-MPW0 – Backside processing**

- Two alternative methods investigated

- 1) Beamline Implantation + Rapid Thermal Annealing (BI + RTA)

- Annealed at 450°C

- Too low to properly activate all the implanted boron

- High enough to potentially damage the MOS transistors

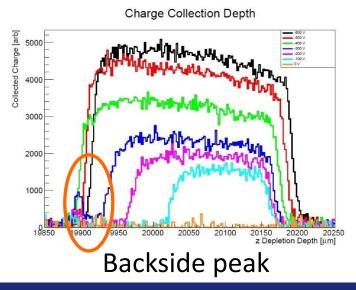

- Backside peak observed in eTCT measurements (H35DEMO)

- 2) Plasma Ion Immersion Implantation + UV Laser Annealing (PIII + LA)

- Localised annealing

- Annealing T can be higher

- All the implanted boron can be properly activated

- No damage to the MOS transistors

- Shallow implant profile

- Keeps all dopants and defects into annealed region

- Advantageous over BI + RTA

- Done by Ion Beam Services (IBS) on full wafers loaned by the foundry

**UK Research**

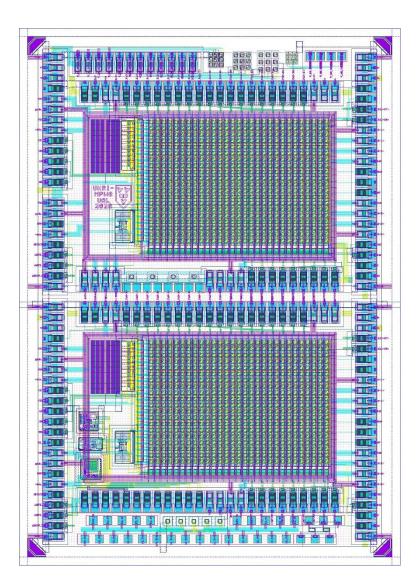

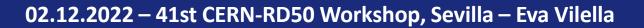

# **UKRI-MPW0 – Chip overview**

| 2 active pixel<br>matrices | <ul> <li>With linear transistors only</li> <li>With linear and ELT transistors</li> <li>With 20 x 29 pixels per matrix</li> </ul> |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

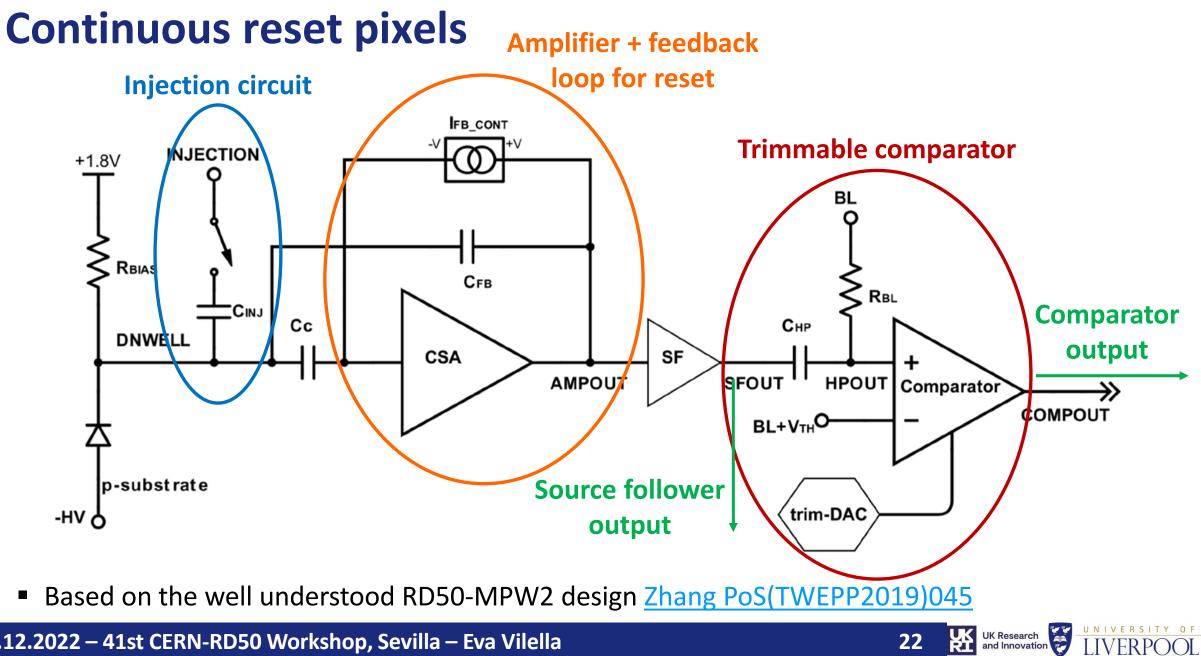

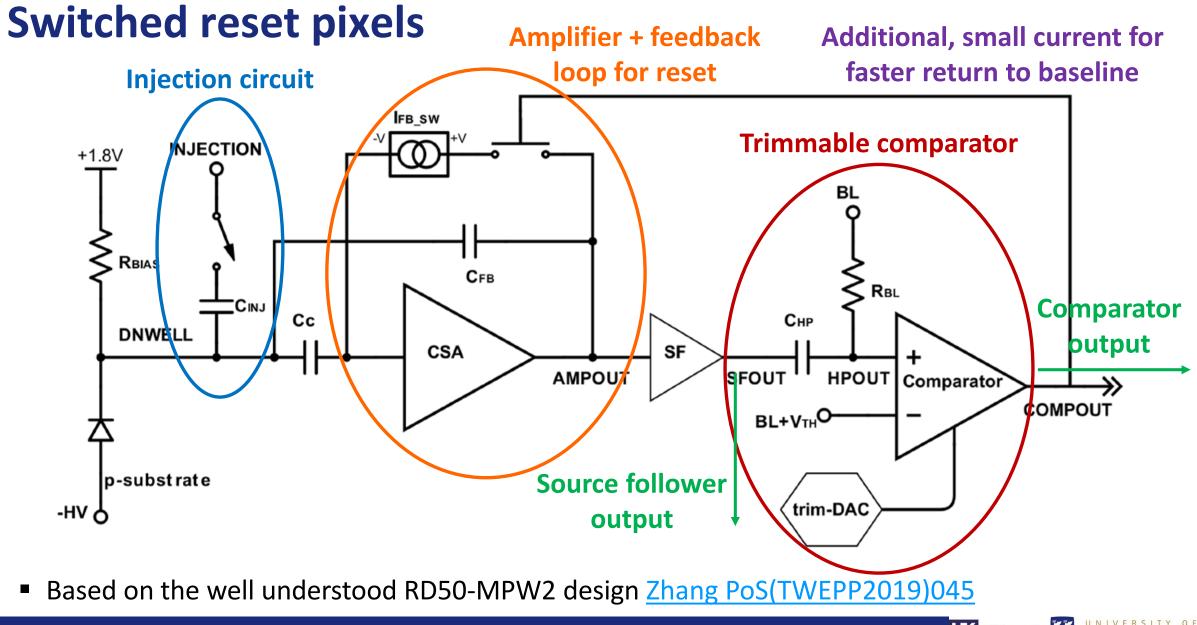

| 3 pixel flavours           | <ul> <li>Continuous reset</li> <li>Switched reset</li> <li>Modulated feedback</li> </ul>                                          |

| Test structures            | <ul> <li>With passive pixels for eTCT<br/>(RD50-MPWx style)</li> <li>With linear and ELT transistors</li> </ul>                   |

| Pixel size                 | 60 μm x 60 μm                                                                                                                     |

UK Research and Innovation

11

LIVERSITY OF

# **UKRI-MPW0 – Chip overview**

| 2 active pixel<br>matrices | <ul> <li>With linear transistors only</li> <li>With linear and ELT transistors</li> <li>With 20 x 29 pixels per matrix</li> </ul> |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 3 pixel flavours           | <ul><li>Continuous reset</li><li>Switched reset</li><li>Modulated feedback</li></ul>                                              |

| Test structures            | <ul> <li>With passive pixels for eTCT<br/>(RD50-MPWx style)</li> <li>With linear and ELT transistors</li> </ul>                   |

| Pixel size                 | 60 μm x 60 μm                                                                                                                     |

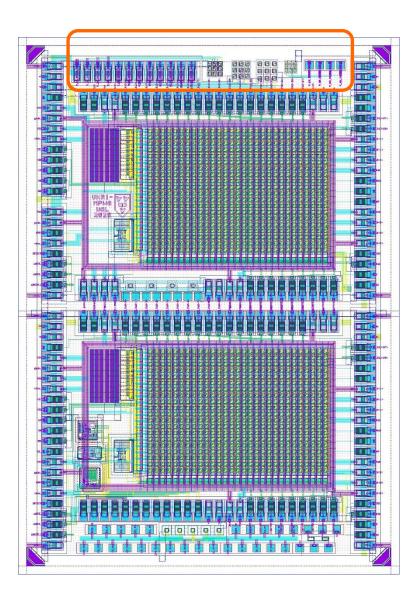

# Measured pixel I-V – PIII + LA, before irradiation

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

13 UK Research and Innovation

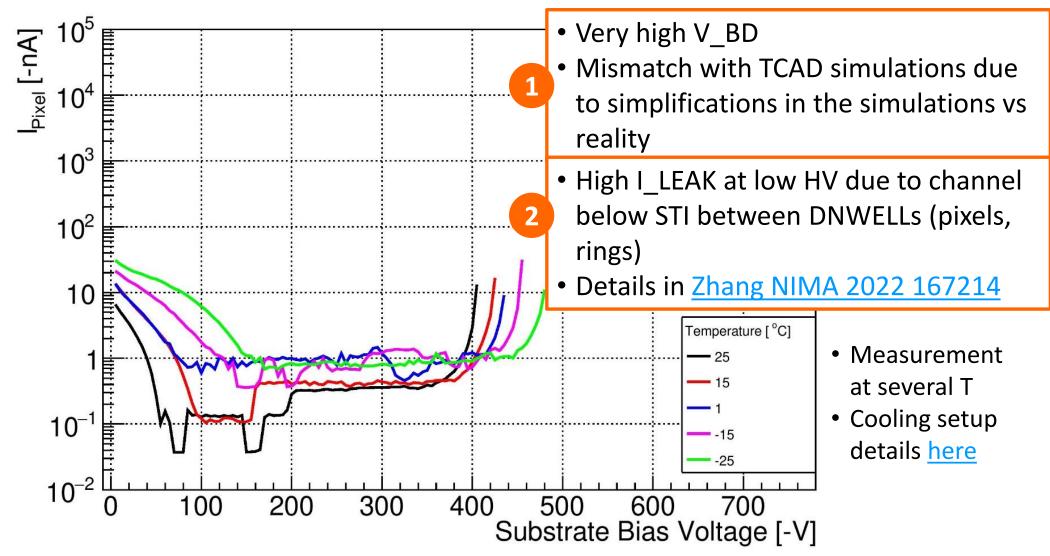

# Measured <u>pixel</u> I-V – PIII + LA, neutron 3e13 $n_{eq}$ /cm<sup>2</sup>

14 WK Research and Innovation

200 A

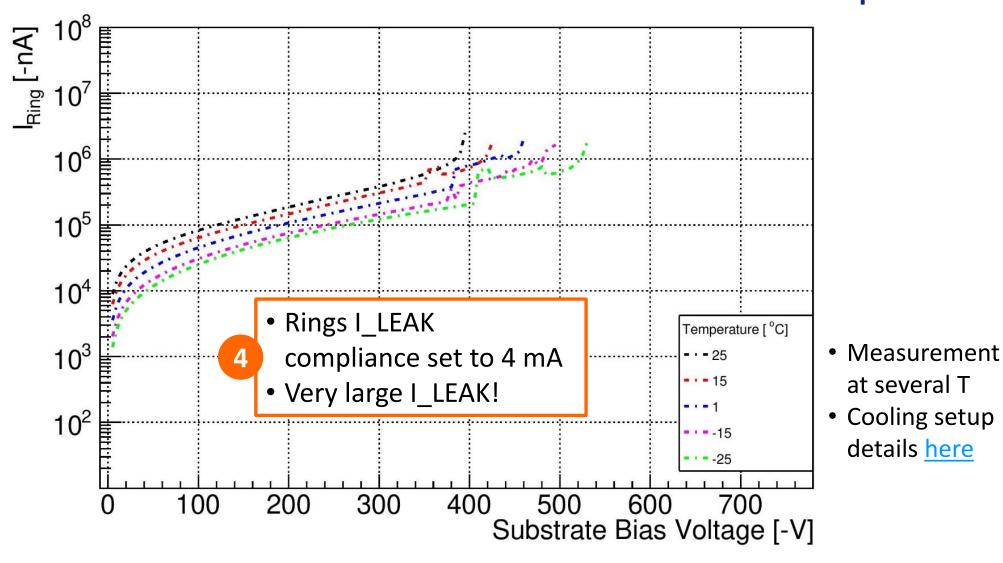

# Measured <u>chip rings</u> I-V – PIII + LA, neutron 3e13 $n_{eq}/cm^2$

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

15 WK Research and Innovation

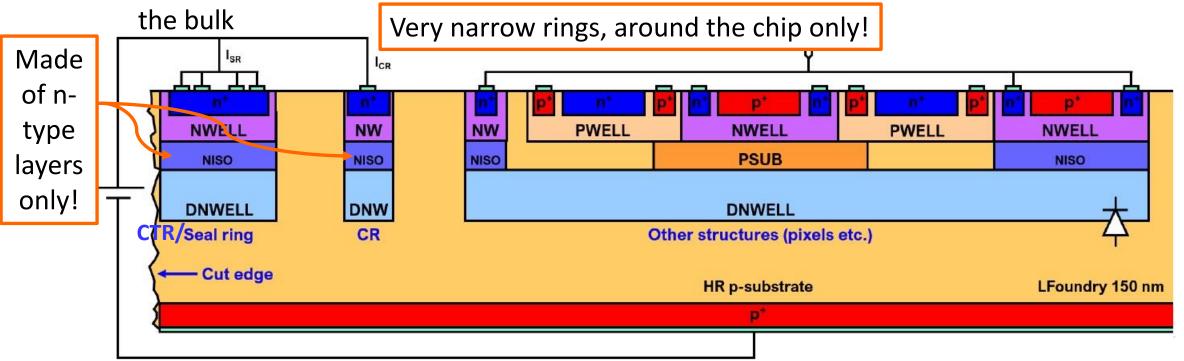

# **UKRI-MPW0 – Chip rings**

- Current Terminating Ring (CTR) that surrounds the whole chip

- Collects the current generated at the cut edge surface

- Used also as the chip seal ring to protect the design during the dicing process

- A Clean-up Ring (CR) between the CTR and the sensor

- Cleans up the remaining current that cannot be collected by the CTR due to diffusion into

#### **UKRI-MPW0 – Chip rings** Current Terr E sub - Collects $\overline{4}$ CTR – Used als 🗋 10⁻ **7**⊟S A Clean-up I<sub>2</sub> pixel – Cleans u 🖁 diffusion into the bulk <sup>궁 10</sup> Made eaka of n-10-11 type NWE NWELL layers NISO NISO only! 10-12 DNWE Seal r UKRI-MPW0 (ρ = 1900 Ω·cm) TCAD - Cut LFoundry 150 nm 10<sup>-13</sup> 500 1000 1500 2000 Reverse substrate bias voltage V<sub>sub</sub> [V]

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

17 W UK Research and Innovation

**IVERPO**

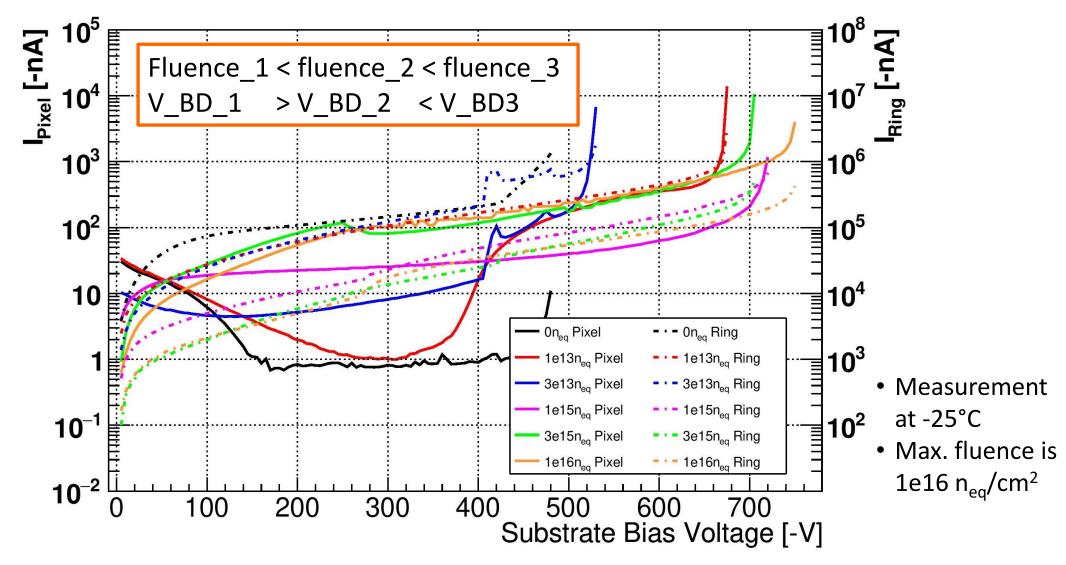

## Measured <u>pixel + chip rings</u> I-Vs – PIII + LA, all fluence

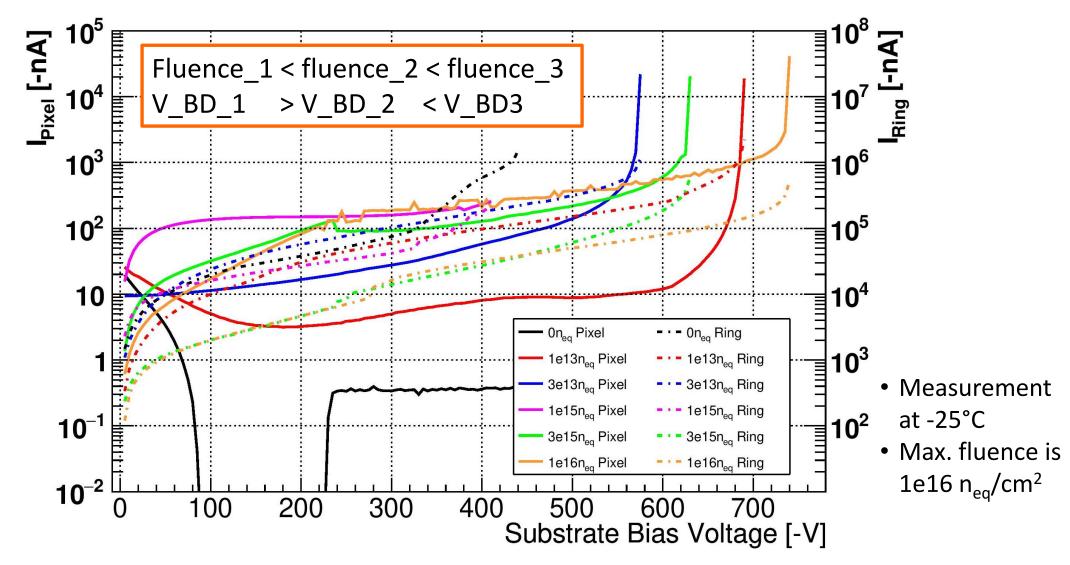

## Measured pixel + chip rings I-Vs – BI + RTA, all fluence

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

19 K UK Research and Innovation

IVERPOO

# Custom-made 300 - - 1 · 10<sup>13</sup>

**Measured eTCT – BI + RTA**

# PCB 8. chip

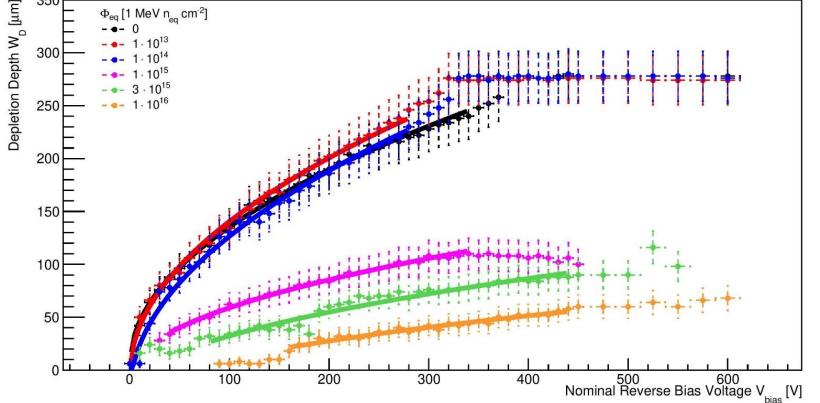

$\underbrace{\underbrace{\mathbf{f}}_{\mathbf{g}}}_{\mathbf{g}} \overset{350}{\mathbf{f}} = \underbrace{\Phi_{eq} \left[1 \text{ MeV } n_{eq} \text{ cm}^2\right]}_{\mathbf{g}}$

- Depletion voltage 300 V @ 1e14  $n_{eq}/cm^2$  (280  $\mu$ m)

- > 50µm depleted depth @ 1e16 n<sub>eq</sub>/cm<sup>2</sup>

- Irradiated PIII + LA samples currently being evaluated

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

UK Research and Innovation

# **UKRI-MPW0 – Chip overview**

| 2 active pixel <<br>matrices | <ul> <li>With linear transistors only</li> <li>With linear and ELT transistors</li> <li>With 20 x 29 pixels per matrix</li> </ul> |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 3 pixel flavours             | <ul> <li>Continuous reset</li> <li>Switched reset</li> <li>Modulated feedback</li> </ul>                                          |

| Test structures              | <ul> <li>With passive pixels for eTCT<br/>(RD50-MPWx style)</li> <li>With linear and ELT transistors</li> </ul>                   |

| Pixel size                   | 60 μm x 60 μm                                                                                                                     |

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

LIVERPOC

# UKRI-MPW0 – DAQ

- Based on Caribou

- UKRI-MPW0 chip carrier board

- UKRI-MPW0 mother board

- Analogue pixels have SFOUT & COMPOUT readout only

- This boards incorporates digital readout

- Measurements of pixel address and time-stamp are possible

- CaR board

- SoC (ZC706)

UK Research and Innovation

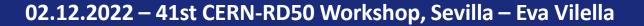

# Active matrix – BI + RTA, before irradiation

- The three different pixel flavours are visible (please ignore three dead columns in the FPGA)

- Measured (using test pulses) and simulated values agree

- Gain expected from design  $\rightarrow$  65  $\mu$ V/e<sup>-</sup> (continuous), 80  $\mu$ V/e<sup>-</sup> (switched)

- Noise expected from design  $\rightarrow$  150 e<sup>-</sup> (continuous), 100 e<sup>-</sup> (switched)

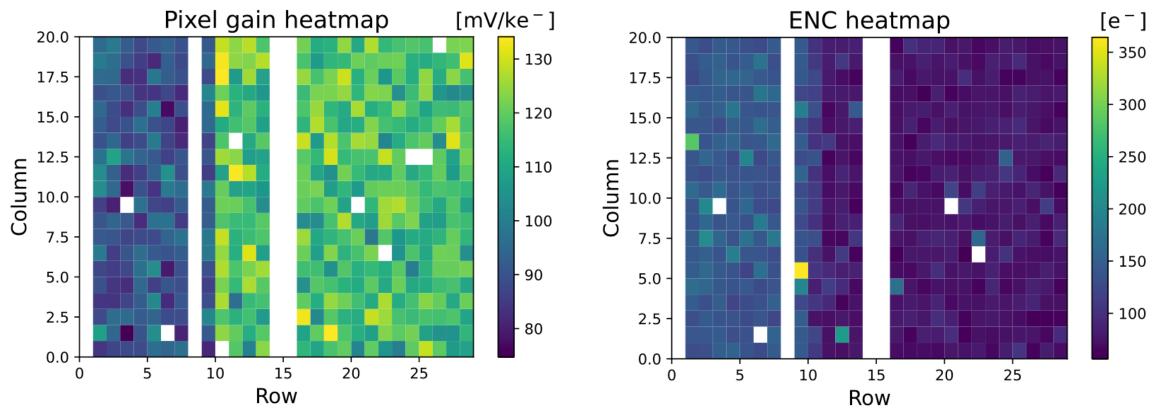

# Active matrix – BI + RTA, before irradiation

- HV = 500 V, V\_TH = 1050 mV

- Sr90 source (old and weak)

- Shutter window = 20 s

- Switched reset pixels have better sensitivity (as in RD50-MPW2)

# **Current plans to improve sensor design**

- To improve pixel I\_LEAK, while keeping a high V\_BD

- Prevent channel below STI & achieve isolation between n-type layers

- Adding a low or moderate-doped and shallow p-type layer beneath the STI

- Running TCAD simulations to understand dose, depth, and spacing

- In conversations with the foundry

- To improve rings I\_LEAK

02.12.2022 – 41st CERN-RD50 Workshop, Sevilla – Eva Vilella

# **Conclusion and outlook**

- UKRI-MPWO is a proof-of-concept, backside biased only HV-CMOS pixel chip

- After 1e16 n<sub>eq</sub>/cm<sup>2</sup> neutron irradiation

- V\_BD > 700 V

- Depletion depth > 50  $\mu$ m

- We are doing studies to improve the sensor leakage current

- Unfortunately we don't have conclusive results yet on the what type of backside processing works better

- We have evaluated the matrix of active pixels before irradiation, and we'll measure irradiated samples next