ATLAS calorimeter and topological trigger upgrades for Phase 1

Samuel Silverstein, Stockholm University For ATLAS TDAQ/L1Calo

+ Overview

- + Upgrade to PreProcessor MCM

- + Topological trigger

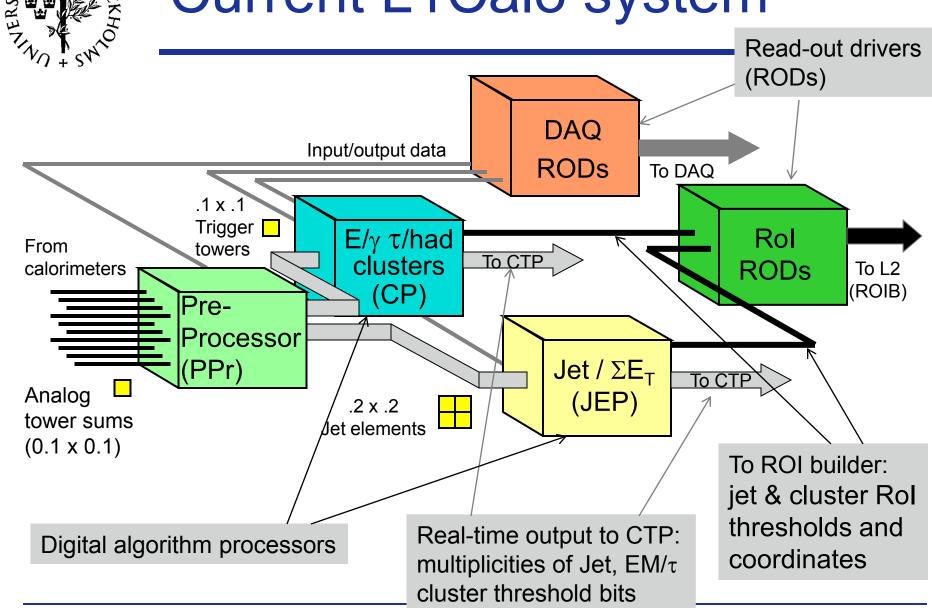

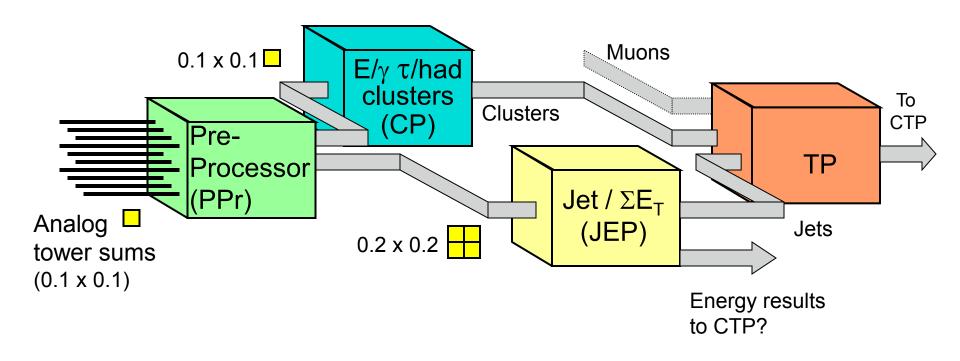

## Current L1Calo system

# Phase I upgrades to L1Calo

- PreProcessor:

- New mixed-signal MCM with FPGA

- Topological processing

- Add Rol coordinates and additional information to the real-time data path

- Topology-based algorithm processor for L1Calo (plus Muon) Rols

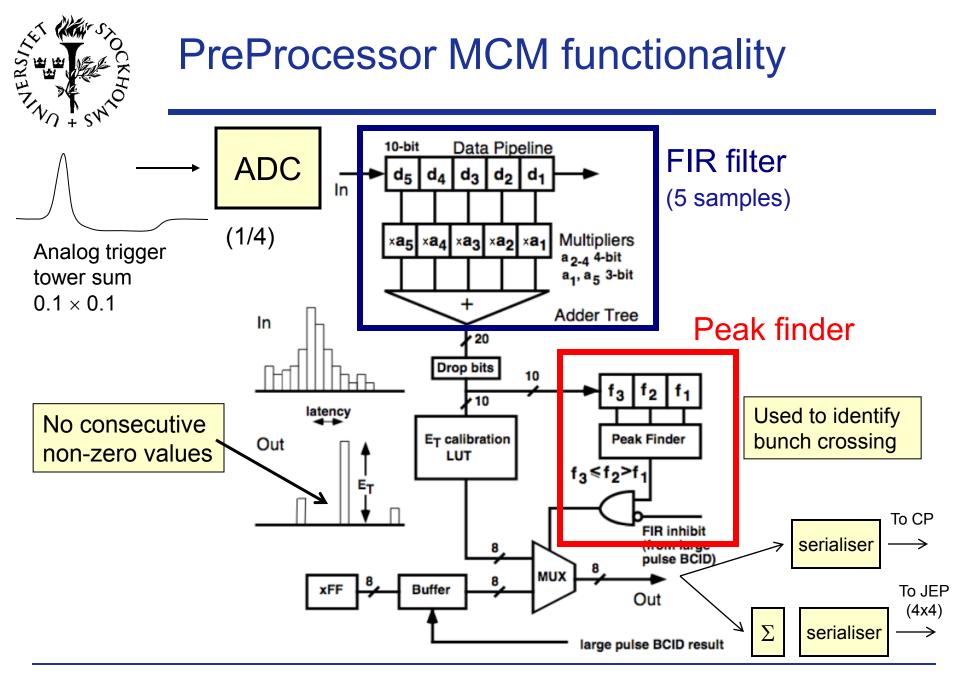

## New PreProcessor MCM

- FPGA-based replacement for existing mixed-signal MCM

- Motivations

- Drop-in replacement if failure rate higher than expected

- Possible to upgrade digital processing algorithms, e.g.

- Improve BCID algorithms

- Compensate for baseline shifting at high luminosity

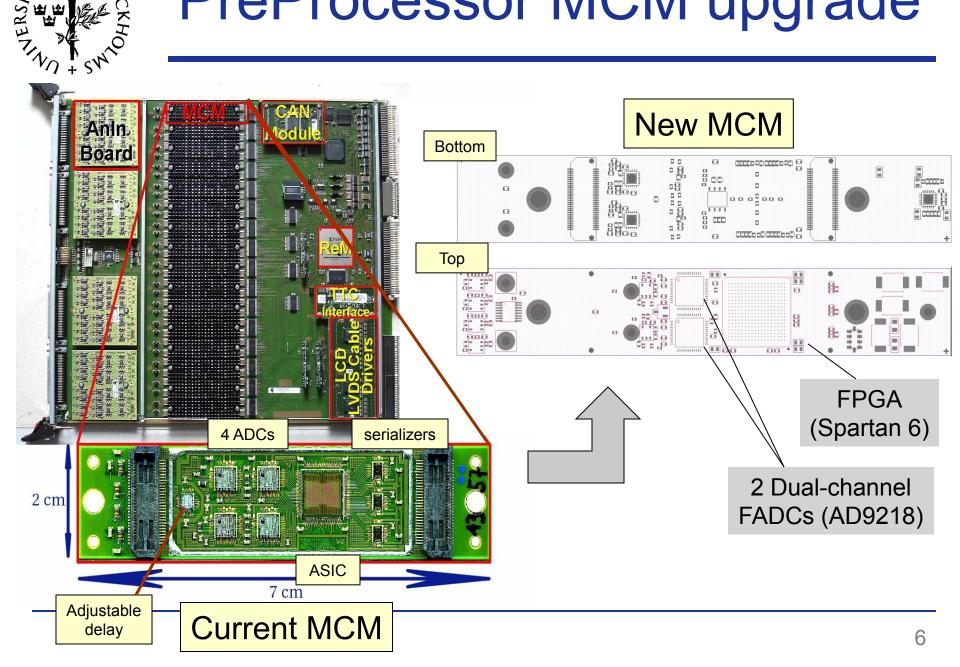

- Features

- Two dual-channel FADCs (AD9218)

- Lower power consumption/channel

- Run at 80 MHz clock rate (latency reduction)

- Replace several digital chips with single FPGA (Spartan 6):

- Adjustable fine delay for ADC clocks

- PreProcessor ASIC

- 480 Mbit/s LVDS serialisers to CP and JEP

## **PreProcessor MCM upgrade**

## **Topological processing**

- Motivations

- Reduce rates while saving physics efficiency

- Current triggers are multiplicity based

- Higher thresholds lose physics, less effective with pileup

- Minimum changes to L1Calo system, rest of experiment

- Adding topology to L1Calo:

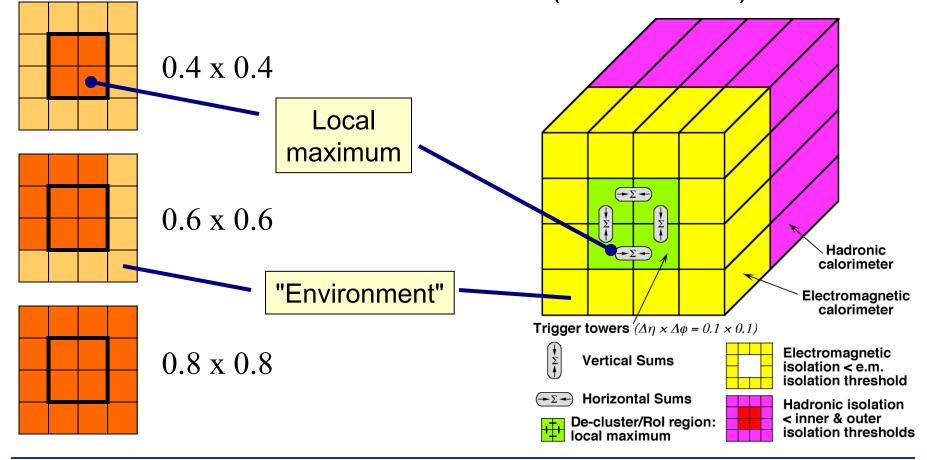

- Keep present data granularity, Jet and EM/ $\tau$  cluster algorithms

- Add Rol coordinates and information to real time data path

- New firmware in existing processor modules

- Higher backplane speed to increase RTDP bandwidth

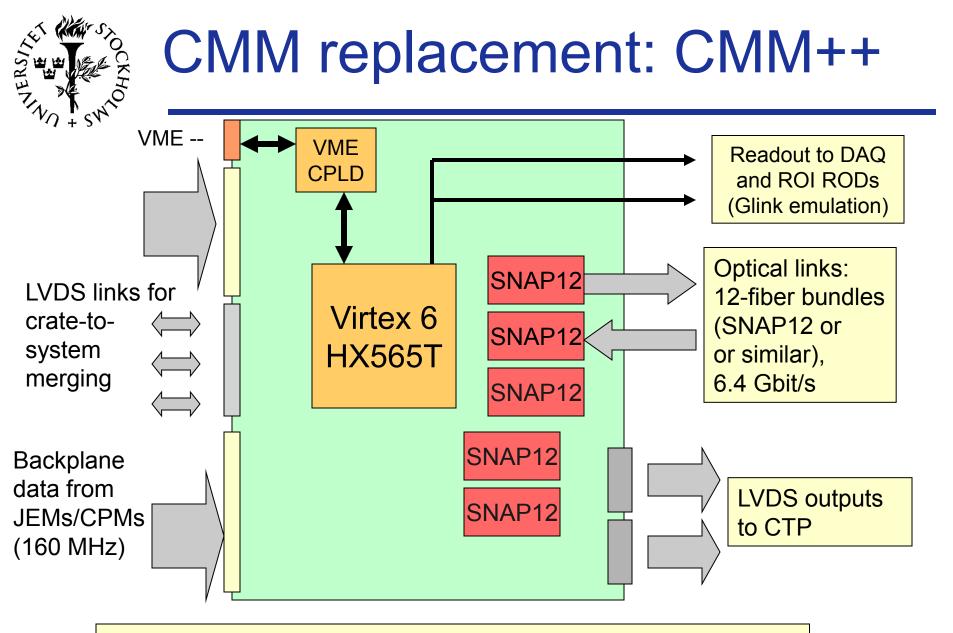

- Replace data merging modules in crates with new boards

- Receive and process high-speed backplane data

- Send Rols to topological processor (TP) over high-speed links

- Topological processor (TP)

- New subsystem (preferred solution)

- Pipelined, fixed-latency processing of all Rols (L1Calo + Muon)

## Jet and cluster algorithms

Jet algorithm:

EM cluster algorithm (τ/had similar):

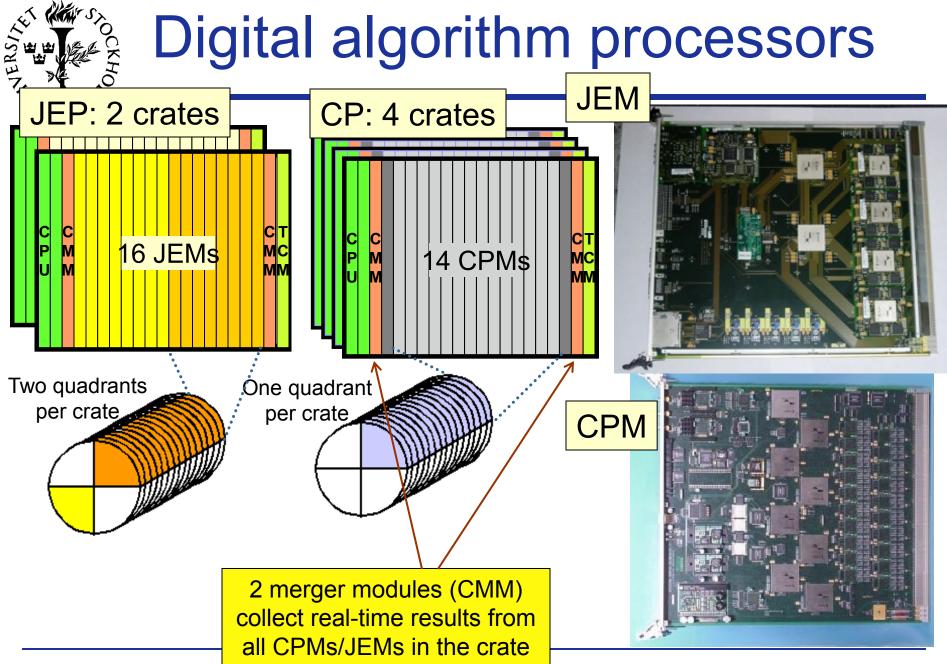

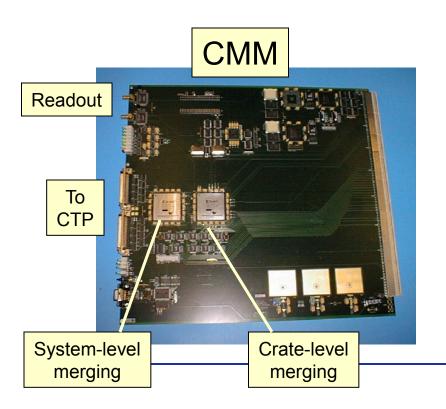

# Data merger module: CMM

- 25 point-to-point backplane links from each JEM/CPM to each CMM

- Current speed 40 MHz (25 bits/BC)

- e.g.  $8 \times 3$ -bit multiplicities + 1 Parity bit

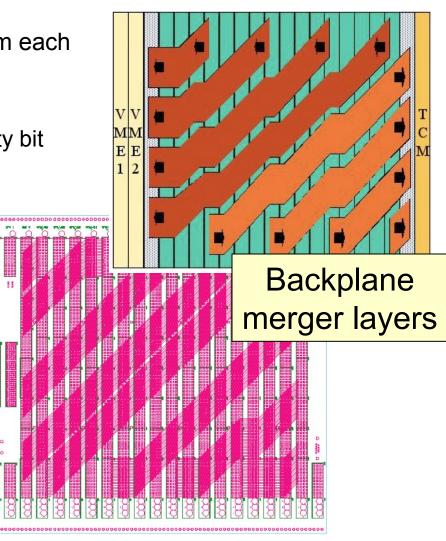

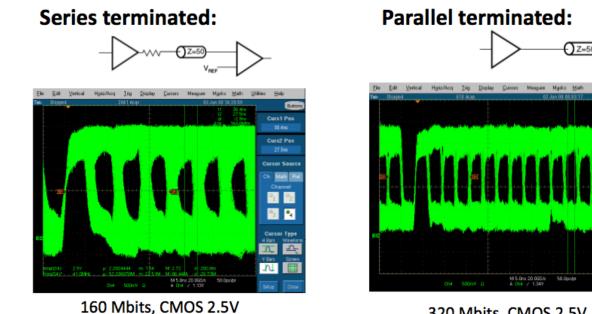

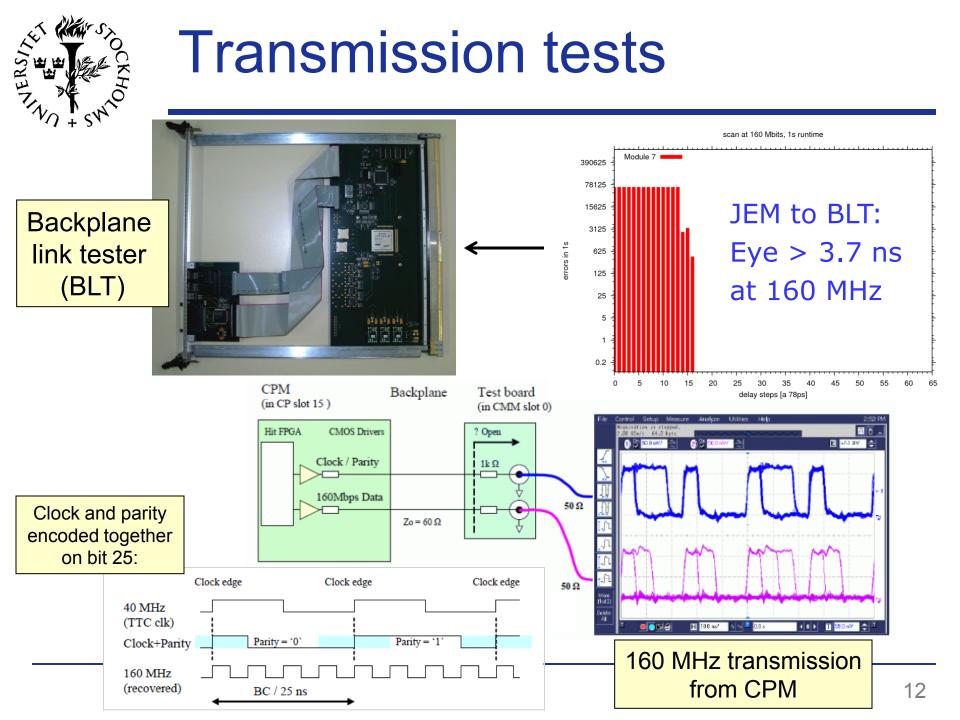

## Higher backplane bandwidth

- Backplane can run at >320 Mbit/s ( $8 \times current$ )

- (given fast transmitter, optimum termination)

- Actual limit: FPGA outputs on CPM and JEM

- Both work well at 160 Mbit/s ( $4 \times current$ ) \_\_\_\_

320 Mbits, CMOS 2.5V

Curst Po

Curs2 Po

#### Adding Rols to backplane data

- Example: proposed 96-bit jet output

- $4 \times 24$  bits at 160 MHz (25<sup>th</sup> bit used for clock + parity)

- 8 "presence bits" (Which of the 8 subregions had an Rol?)

- Report up to 4 Rols (expect < 2 per JEM)</li>

- 2 fine position bits (localize jet to  $0.2 \times 0.2$  coordinates)

- 8 threshold bits

- Up to 12 additional bits per Rol

- For example, jet E<sub>T</sub>

| P1 | P2                             | P3 | P4                | P5 | P6                | P7 | P8          | Threshold bi              | ts Rol 1 (8b)                  | Threshold bits Rol 2 (8b) |

|----|--------------------------------|----|-------------------|----|-------------------|----|-------------|---------------------------|--------------------------------|---------------------------|

| -  | Fine Pos<br>Rol 1              |    | Fine Pos<br>Rol 2 |    | Fine pos<br>Rol 3 |    | Pos<br>ol 4 | Threshold bits Rol 3 (8b) |                                | Threshold bits Rol 4 (8b) |

|    | Jet Rol 1 E <sub>T</sub> (12b) |    |                   |    |                   |    |             |                           | Jet Rol 2 E <sub>T</sub> (12b) |                           |

|    | Jet Rol 3 E <sub>T</sub> (12b) |    |                   |    |                   |    |             |                           | Jet Rol 4 E <sub>T</sub> (12b) |                           |

Must be backward-compatible with existing CMM

# Topological processor (TP)

- Two options being considered:

- <u>Preferred</u>: New topological processor (TP) subsystem

- Modern technology / form factor (Virtex 6/ATCA)

- Receive and process all L1Calo Rols

- Able to include Muon Rols

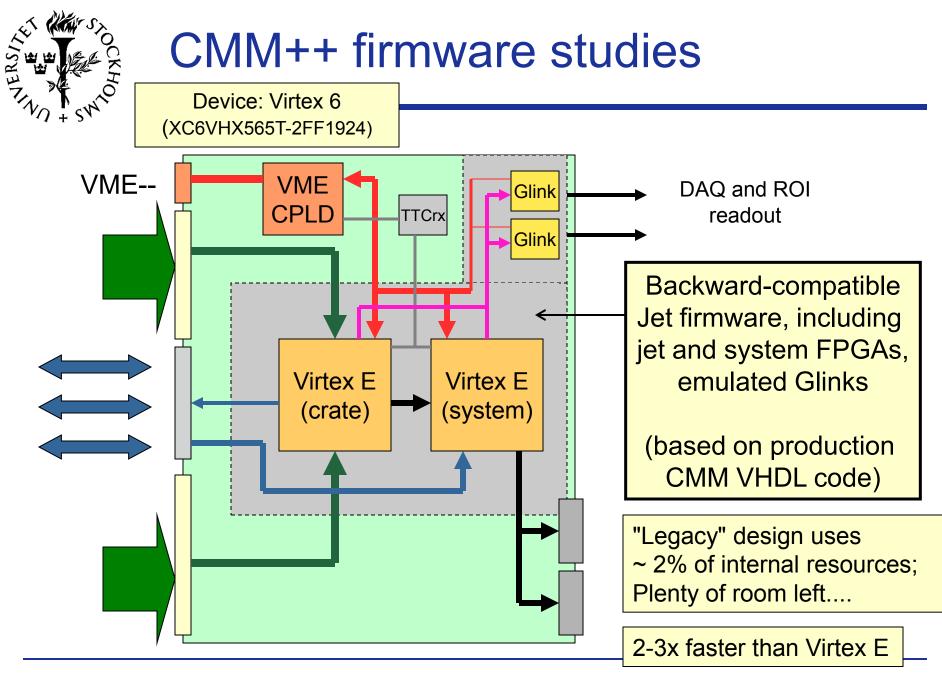

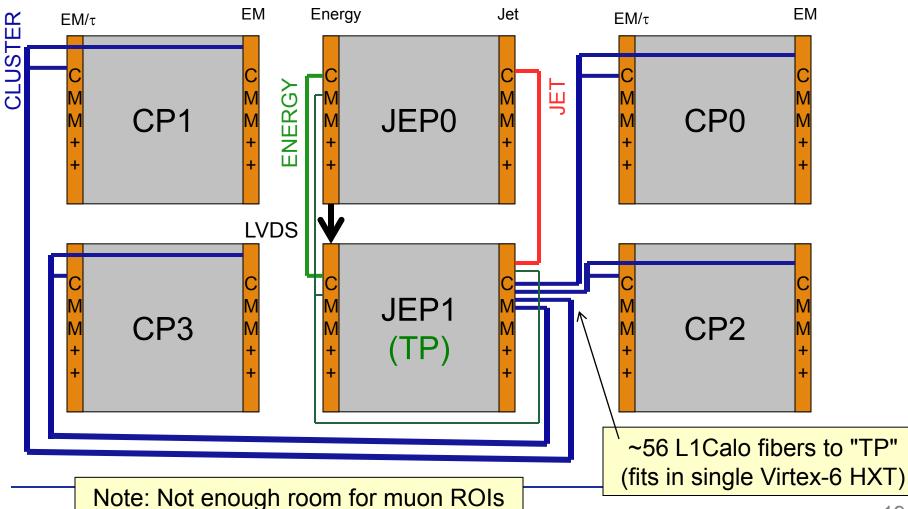

- <u>Backup</u>: Topological algorithms in CMM++

- Connect fiber links in a star configuration, with one CMM++ as the TP

- Process all jet, CP Rols

- No room for muon Rols

- More limited algorithm processing (less scalable)

## TP subsystem (preferred)

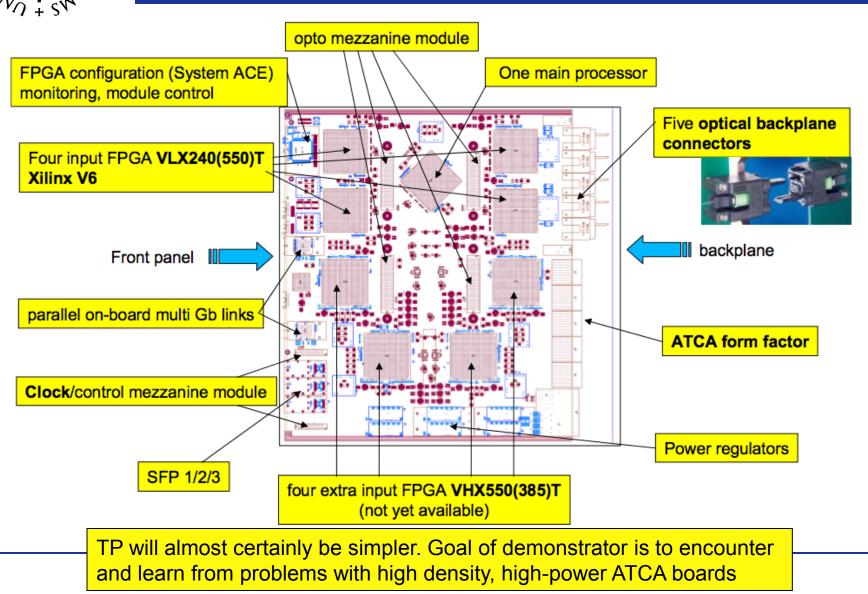

# TP technology demonstrator

**JER**

#### Backup: TP in designated CMM++

## Summary and status

- PreProcessor MCM replacement

- ASIC code ported to Spartan 6 FPGA, plus serialiser and clock manager functionality

- PCB layout complete and sent out, expect boards back soon

- CP/JEP crates

- Backplane transmission tests at 160 MHz look good

- Studies indicate upgraded firmware in CPMs and JEMs will easily fit and run at full speed

- CMM++ specifications in early stage, studies of prototype firmware look promising

- Topological Processor (TP)

- Two options (CMM++ or new TP crate)

- Technology demonstrator layout nearly complete, soon available for testing