œ

micro and nanoelectronics

mage chain

MINATEC\*

2011

# **Advanced Packaging in LETI**

David HENRY CEA-LETI-Minatec ACES 2011 – CERN – 10-03-2011

leti

microsystems ambient intelligence

œ

# **General outline**

## **1. Introduction**

- 2. Wafer Level Packaging

- Key processes & technologies

- **Applications** examples

- 3. 3D Integration

- Key processes & technologies

- **Applications** examples

- 4. Conclusion and perspectives

# Leti at a Glance

Founded in 1967 as part of CEA Leti is ISO2001 standard certified

## 1,600 researchers

190 PhD students + 34 post PhD

## **CEO Dr. Laurent Malier**

# 227 M€ budget

> 75% from contract~ 30M€ CapEx

## **Over 1,700 patents**

284 in 2009 40% under license

## 37 start-ups & 23 common labs

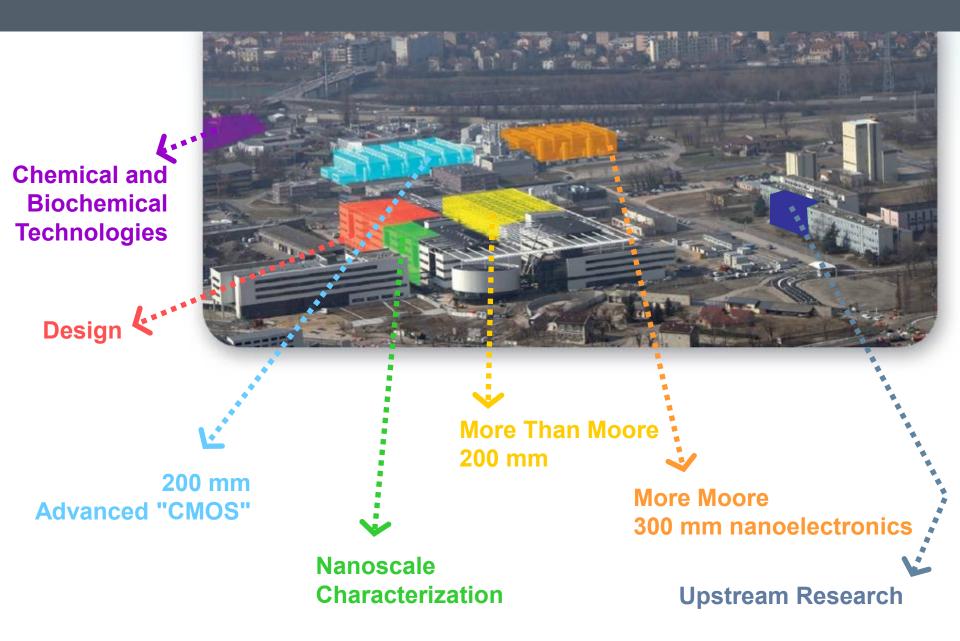

# Leti's Research Infrastructures

# Advanced packaging in LETI : two research axes

## → Packaging & integration team in LETI : ~ 60 people involved in :

## Wafer Level Packaging

Manage functions at wafer level :

- Mechanical protection

- Hermeticity

- Controlled atmosphere / Vacuum

- Cost decrease

# Package Silicon 3 Silicon 2 Silicon 1

## → 3D Integration

To assembly more than one dies in one package :

- Electrical links between strata

- Electrical links with external world

- Thermal management

- Form factor reduction

- Cost decrease

#### Electronic component

# **General outline**

## 1. Introduction

- 2. Wafer Level Packaging

- Key processes & technologies

- **Applications** examples

- 3. 3D Integration

- Key processes & technologies

- **Applications** examples

- 4. Conclusion and perspectives

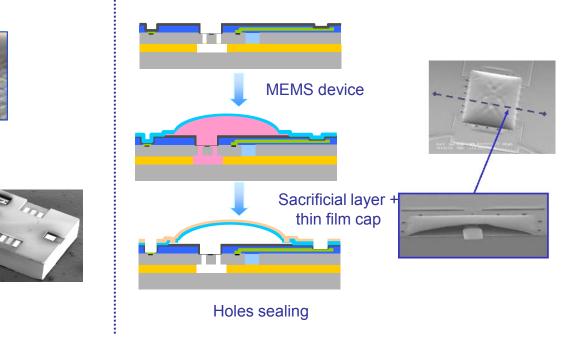

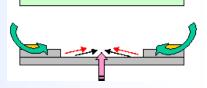

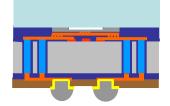

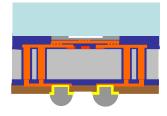

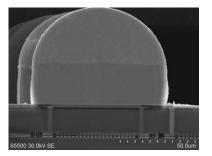

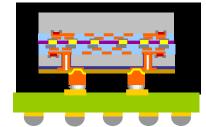

# Wafer level packaging approaches

Bonding cap

MEMS device

Bonding of the cap

Contact

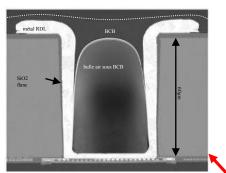

Thin film packaging

An ultra compact solution, compatible with IC fabs

.

# Wafer level packaging approaches

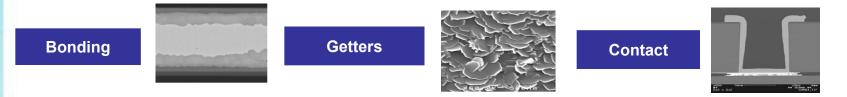

## Requires to develop Generic technologies :

## **Bonding** :

- Polymer solution for prototyping and low cost applications

- Eutectic bonding : An hermetic solution, compatible with high vacuum, and flip chip

Accelerometers

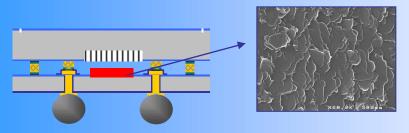

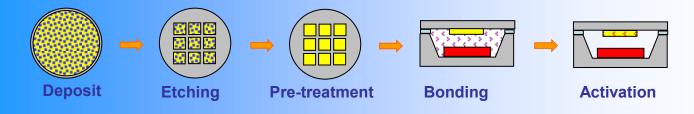

# **Generic technologies : getters**

## Why do we need getters in cavities :

- Controlled and Low pressure (< 10-2 mbar) required in micro-cavities</p>

- Outgassing sources : sealing / MEMS / µleaks / permeation

- Outgassing sources could become critical for the pressure

Getter material is able to pump residual gases

Deposited and patterned as a standard layer (no outsourcing)

- Tunable activation temperature (to fit with sealing process)

- Compatible with both wafer bonding and thin film packaging

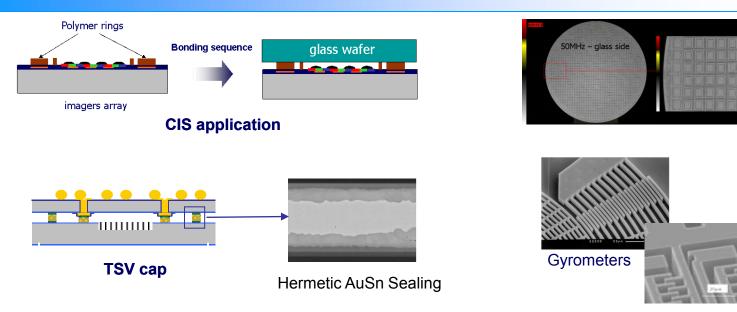

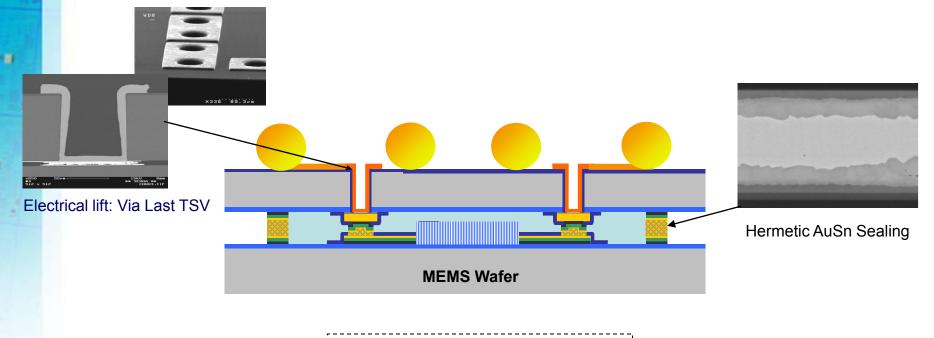

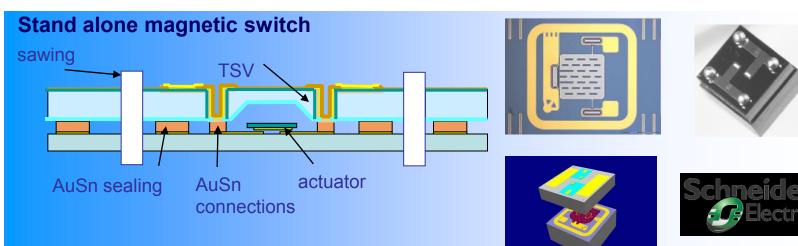

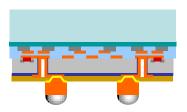

# **Generic technologies : contact by TSV**

#### Electrical contact to outside world :

- Hermetic metallic sealing (AuSn Wafer to wafer bonding)

- → TSV (Through Silicon Vias) in the cap wafer

- Direct available for flip-chip

## Available on 200 mm wafers

# **General outline**

## I. Introduction

## 2. Wafer Level Packaging

Key processes & technologies

**Applications** examples

3. 3D Integration

Key processes & technologies

**Applications** examples

4. Conclusion and perspectives

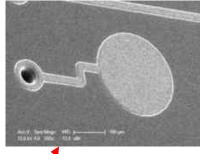

# **Applications for Bonding cap**

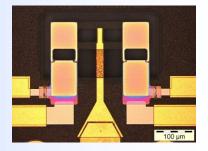

## **RF Switch with electrode on the cap wafer**

**Functional demonstrators available :**  *Presented at MEMS 2010: A fully packaged piezolectric switch with low voltage electrostatic hold, M. Cueff et al.*

#### **Published at Transducers 09**

A New Magnetically Actuated Switch for Precise Position Detection, Coutier & al.

- 0

-

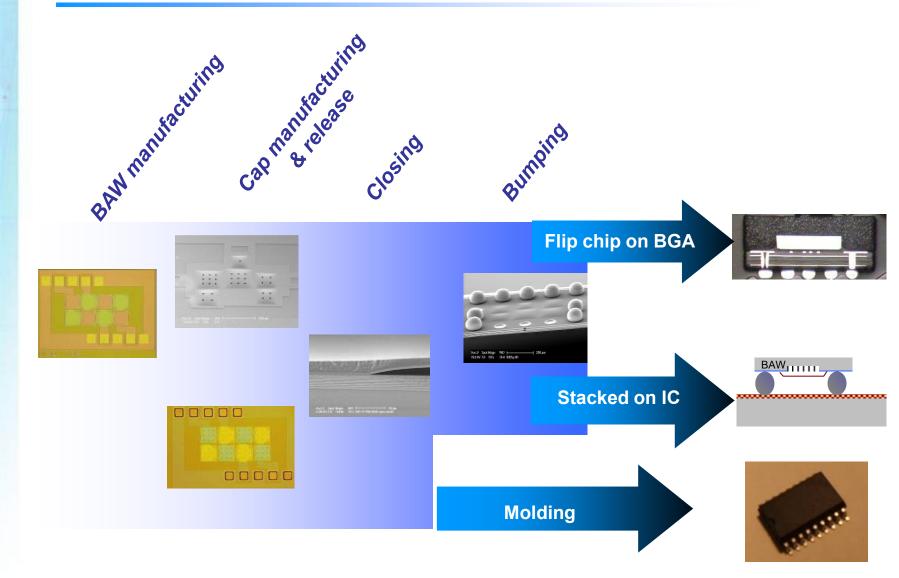

# **Application for bonding cap: BAW protection**

# **General outline**

- I. Introduction

- 2. Wafer Level Packaging

- Key processes & technologies

- **Applications** examples

- 3. 3D Integration

- Key processes & technologies

- **Applications** examples

- 4. Conclusion and perspectives

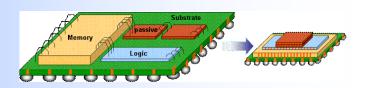

# What is 3D Integration ?

It's the way to achieve an electronic system or a component by using the third dimension (Z) instead of only the two first dimensions (X & Y)

→ 3D Integration key drivers :

- Form factor decrease

- Miniaturization of final device (X,Y,Z)

Performances improvement

- → Decrease R, C, signal delay

- → Increase device bandwidth

- Decrease power consumption

- Cost decrease

- → Si surface decrease

- Reuse of existing Packaging, BEOL & FEOL lines

One Chip SetTopBox (STM)

- -

1

# **LETI approach for 3D Integration**

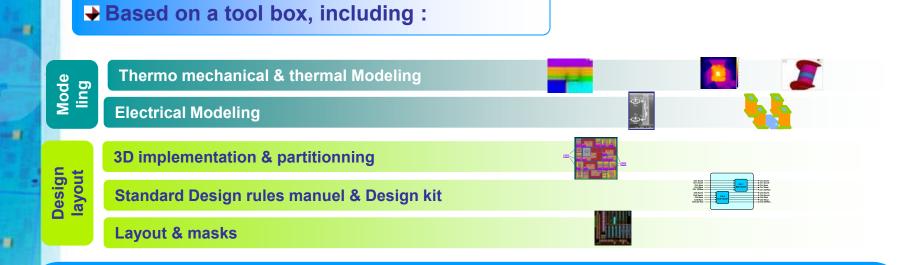

## Based on a tool box, including :

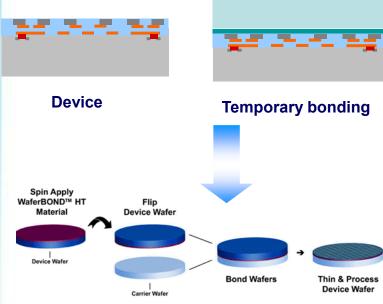

# **Temporary bonding / Thinning/handling Toolbox**

## Temporary bonding / thinning / handling

3D techno

Debonding / handling / Stacking

Source : A. Jouve / Brewer Science / 3D IC 2009

EVG 520 bonder

Wafer bonded with temp. glue

Debonder EVG 805

Mount to Film Frame

Debonded wafer (70 µm)

ACES Workshop, CERN, 2011 March 10th

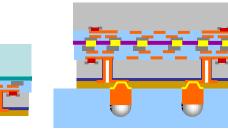

# Interconnections toolbox

## → Face to face connections

C2C pillars SLID / TLP

## Classic Flip chip (Ball or stud bump)

чве

## Solder-free µinserts

C2S pillars

**Cu-Cu Direct bonding**

-

-

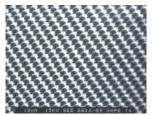

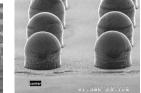

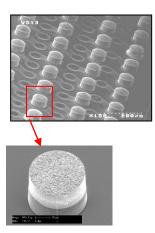

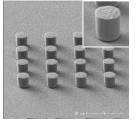

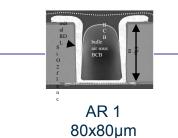

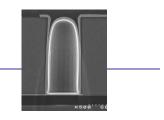

# **TSV** Toolbox

## Through Silicon Via (TSV)

#### Via First TSV (Polysilicon filled)

Via Middle TSV (Copper or W filled)

AR 7 , 2 x 15  $\mu m$   $\,$  AR 10, 10x100  $\mu m$

W filled

#### Via Last TSV (Copper liner)

AR 2, 60x120µm

AR 3, 40x120µm

ACES Workshop, CERN, 2011 March 10th

.....

# **TSV** Toolbox

## Components placement

- → Wafer to wafer (W2W)

- → Chips to wafer (C2W)

- High speed

- High accuracy

Datacon

Source : ASM

EVG 560

# **General outline**

## I. Introduction

- 2. Wafer Level Packaging

- Key processes & technologies

- **Applications** examples

- 3. 3D Integration

- Key processes & technologies

- **Applications** examples

- 4. Conclusion and perspectives

-----

-

1

# Assembling the bricks as a LEGO...

œ

#### letī (MINATEC

.

.

# Assembling the bricks...

|               | 1 active layer | 3 level stack            | 9                           |                       |                             |

|---------------|----------------|--------------------------|-----------------------------|-----------------------|-----------------------------|

| Die/die       | Die/substrate  | TSV                      | Handling                    | Die placemer          | nt & die molding            |

| Solder balls  | Wire Bonding   | TSV First                | Temp. Bonding<br>+slide off | High throuput<br>P&P  | Thick Polymer<br>molding    |

| opper Pillars | Solder balls   | TSV Middle<br>& BS AR10  | Temp Bonding<br>+ zonebond  | High precision<br>P&P | Thin Polymer<br>molding     |

| µinserts      | Copper pillar  | TSV Last<br>AR1          | Permanent bonding           | Self Assembly         | Thin Oxyde<br>planarisation |

| µtubes        |                | TSV Last<br>AR2          |                             | Wafer<br>To Wafer     | WLUF                        |

| Cu-Cu         |                | TSV Last<br>AR3          |                             |                       | Classic<br>Underfill        |

| DTW Cu-Cu     |                | TSV Last<br>High density |                             |                       |                             |

| Die/die        | Die/substrate | TSV                      | Handling                    | Die placement & die moldir |                             |

|----------------|---------------|--------------------------|-----------------------------|----------------------------|-----------------------------|

| Solder balls   | Wire Bonding  | TSV First                | Temp. Bonding<br>+slide off | High throuput<br>P&P       | Thick Polyme<br>molding     |

| Copper Pillars | Solder balls  | TSV Middle<br>& BS AR10  | Temp Bonding<br>+ zonebond  | High precision<br>P&P      | Thin Polymer<br>molding     |

| µinserts       | Copper pillar | TSV Last<br>AR1          | Permanent bonding           | Self Assembly              | Thin Oxyde<br>planarisation |

| µtubes         |               | TSV Last<br>AR2          |                             | Wafer<br>To Wafer          | WLUF                        |

| Cu-Cu          |               | TSV Last<br>AR3          |                             |                            | Classic<br>Underfill        |

| DTW Cu-Cu      |               | TSV Last<br>High density |                             |                            |                             |

#### 1 active laver Face to Face Face to back 3 level stack Die/die Die/substrate TSV Handling Die placement & die molding emp. Bondi igh throuput Solder balls Wire Bonding TSV First +slide off P&P molding TSV Middle & BS AR10 Femp Bonding Thin Polymer High precision P&P Copper Pillars Solder balls + zonebond molding TSV Last Self Assembly uinserts AR1 TSV Last AR2 utubes WLUF TSV Last AR3 Classic Underfill DTW Cu-Cu

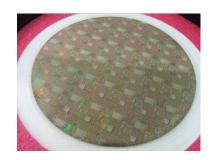

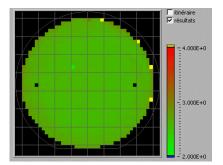

#### **TSV for CMOS image Sensors**

Transferred to industry

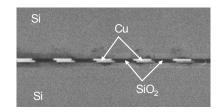

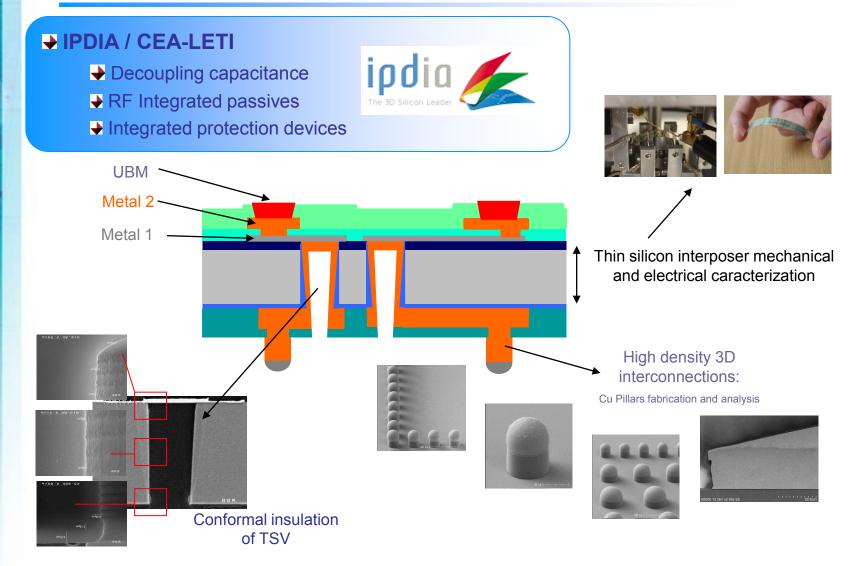

# **Examples of Applications with partners**

## ST Micro / CEA-LETI

- CIS application for mobile phone

- → TSV AR 1 : 1

Production mode since 2009

300 mm production line @ STM Crolles (FR)

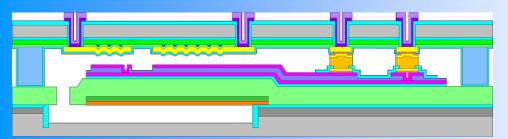

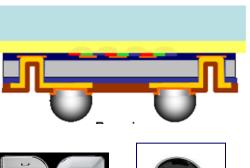

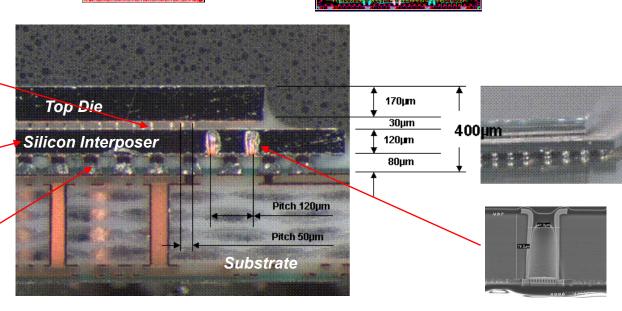

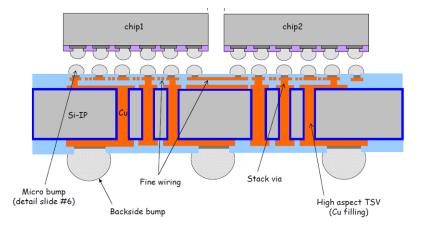

# **Examples of Applications with partners**

#### → ST Micro / CEA-LETI

- Partitioning for Set Top Box application

- → 45nm technology stacked on 130nm interposer (Mature + advanced)

Advanced CMOS (45nm)

Top Chip

130 nm chip

Interposer

C2C Cu Pillars

Thinned wafer <sup>-</sup> (120 μm)

Chip to substrate copper pillars

**TSV** AR 2, 60x120μm

# **Examples of Applications with partners**

œ

# **Examples of Applications with partners**

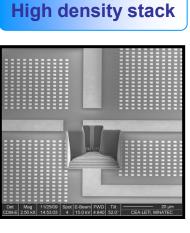

## Shinko / CEA-LETI

- → High end applications → Logic stack

- → 300 mm wafers

## Common lab started January 2011 Nagano Engineers assigned to Leti

27

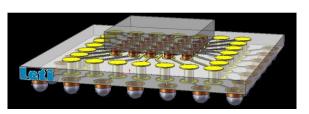

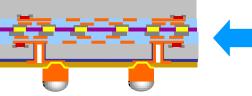

# The next step of the toolbox : Open 3D initiative

## Open 3D Initiative objectives

- Need of 3D technologies for a lot of applications / products: medical, bio, imaging, space, energy, …

- A complete 3D development is long and costly (techno development, specific design,...).

- OPEN 3D initiative : to offer a 3D integration solutions for demonstrators & prototyping based on existing technologies

#### Open 3D philosophy :

Bottom component coming from IC Foundry or customer

Top component coming from IC Foundry or customer

Open 3D offer 3D technologies service

Final assy possible with packaging partners

ACES Workshop, CERN, 2011 March 10th

# The next step of the toolbox : Open 3D initiative → Open 3D technological offer :

## DRM / Layout & masques

## Six elementary bricks

- → TSV Last (AR 1:1 & 2:1)

- Interconnections C2C : Cu pillars

- Interconnections C2C Cu post

- Interconnections C2S : Cu pillars

- Temporary bonding / Thinning / Debonding

- Stacking & underfilling

œ

# **General outline**

## Introduction

- 2. Wafer Level Packaging

- Key processes & technologies

- **Applications** examples

- 3. 3D Integration

- Key processes & technologies

- **Applications** examples

- **4.** Conclusion and perspectives

30

## **General outline**

## Conclusions

Wafer level packaging and 3D Integration are the best candidates of packaging & integration approaches for the next generations of devices.

LETI has developed a technological toolbox for Wafer level packaging and 3D Integration

→ A part of this toolbox is now mature and ready for using at prototype level

## Perspectives / Collaboration models

To develop new technologies to fill the toolbox and to meet our customers requirements.

Collaboration models :

Classical R&D projects for new technologies developments / EU, local or bilateral funding.

→ Prototyping Via open 3D initiative

micro et nancélectronique intelligence ambiante biologie et santé chaîne de l'image

# Thank you for your attention Questions ?

Loyauté Envie d'entreprendre Envie d'entreprendre Travail en équipe Innovation

œ