#### CMS HGCAL and gitlab pipelines

SoC Interest Group Meeting

Arnaud Steen, on behalf of the HGCAL

May 3, 2022

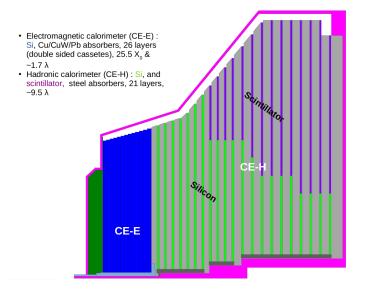

#### CMS Endcap calorimeter for phase 2

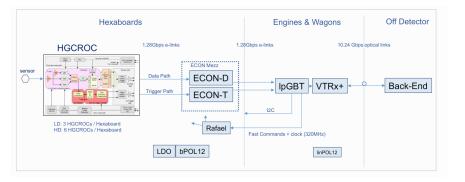

#### Electronic system overview in HGCAL

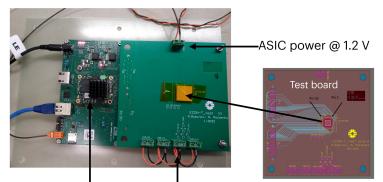

# Use of SOC in HGCAL : single module/ROC test system

• Hexa-controller test system with silicon module

- Custom board hosting a Trenz TE0820 module with a ZYNQ UltraScale+

- "Trophy" board carrying power and signals from/to HGCROCs

- Silicon module with embedded ROCs

• Same test system for single ROC testboard

• Very similar test system for tile-module

### Use of SOC in HGCAL : ECON-T testing

- Concentrator ASICs in HGCAL

- ► ECON-T : collect and filter trigger primitives from HGCROC and transmit them to lpGBTs

- ECON-D : collect DAQ data from HGCROC and transmit them to IpGBTs

FPGA Individual power domains

### Use of SOC in HGCAL : v2/3 system tests

- V2 system test:

- ZCU102 as back-end (fast command, link capture, lpGBT control)

- Hexacontroller (with Trenz) as ECON emulators

- V3 system test:

- ZCU102 as back-end

- Hexacontroller (not in the picture) will be used as ECON-D emulators as it is not yet available

# Next uses of SOC in HGCAL : robot for testing HGCROC

- pprox 120k HGCROC to test during production

- 2 robots will have each 5 single ROC testers

Arnaud Steen, NTU

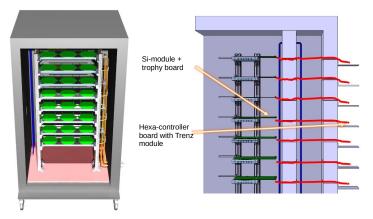

## Next uses of SOC in HGCAL : multi-module test system

• Si-modules will be tested inside a cold box ( $\approx$  -30 $^{\circ}C$  ) after assembly

- 6 Si module assembly centers will be equipped with such system

- Hexaboards (30k) will be also tested with such system in 1 or 2 labs

Arnaud Steen, NTU

### Use of SOC in HGCAL

- Similar use of TE0820 module and ZCU102:

- root and boot partitions placed in SD card

- using centos 7

- ▶ firmware loaded "manually" by the user with a python script (≈ re-writting of the fpgautil.c : a simple command line tool to load FPGA)

- Xilinx IPs:

- Direct I2C for ROC configuration + ADC (ROC power consumption, DC levels) readout on the "trophy" board and single ROC socket board

- ★ Direct GPIO to control signals like resets for the ROCs, enable/power good for LDOs

- $\blacktriangleright$  Custom IPs  $\rightarrow$  AXI lite and AXI full. Using uio driver: "uio-pdrv-genirq" and uhal library (ipbus-software):

- ★ Control of the registers of fast command block, link capture block ...

- ★ Readout of FIFOs

- ★ Control of IpGBT registers

- SOMs registered on network and use DHCP

- Running test in practice:

- ssh connection in the ZYNQ

- load the PL for the system at hand

- start the SW

#### Firmware and software in HGCAL test systems

- Common firmware blocks for several test systems:

- Same fast command block for single module/ROC test system and V2/3 system test

- Same link capture block for

- ★ single module/ROC test system capturing ROC data (trigger primitive or DAQ data)

- ★ V2/3 system capturing ECON data

- "uio-pdrv-genirq" to have interface with AXI registers and software

- Common software using a custom ipbus-software version to memory map the AXI registers and read the FIFOs. Was inspired by Dan Gastler's presentation (ApolloUpdate slides), from which we added:

- Interrupt signal handler

- "Non-incremental" block read (to read FIFOs)

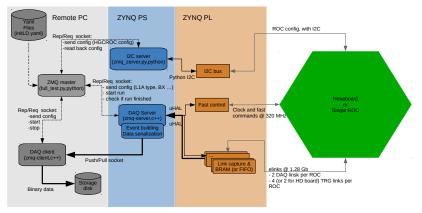

#### Example : single module/ROC test system

• DAQ flow overview

- Synchronization of the software by using zmq library: https://zeromq.org/

- Configuration using yaml format: https://yaml.org/

#### Gitlab chain for HGCAL firmware

#### • Last year (link):

- vivado running in dedicated docker runner launched with gitlab pipeline

- artifacts with .bit and .dtsi files, to be downloaded as zipped file

| Pipeline Needs Jobs 6 Tests 0 |                    |

|-------------------------------|--------------------|

| Check_prerequisite            | Run_vivado         |

| ⊘ list_projects               | ⊘ hexaboard-hd-t   |

|                               | ⊘ singleroc-tester |

|                               | ⊘ tileboard-tester |

|                               |                    |

device tree compiler used locally to create the .dtbo file before loading the FPGA

#### Gitlab chain for HGCAL firmware

- Update since last year:

- Device tree compiler run in the gitlab pipeline to create the .dtbo and add it to the artifacts

- Configurable (depending on the design) .xml files for ipbus-software added to the artifacts

- Artifacts packaged inside RPM

- RPMs upload to a yum repository (hosted on a eos website).

| Check_prerequisite | Run_vivado | Prep_outputs                      | Make_rpm        | Deploy  |

|--------------------|------------|-----------------------------------|-----------------|---------|

| ⊘ list C           | build 5    | 📀 build: [hexaboard-hd-tester-v1p | ol-trophy-v1] 🙄 | eploy C |

|                    |            | 📀 build: [hexaboard-hd-tester-v1p | o1-trophy-v2] 🔅 |         |

|                    |            | ⊘ build: [singleroc-tester-v1p1-1 | p2V] ③          |         |

|                    |            | ⊘ build: [singleroc-tester-v1p1]  |                 |         |

|                    |            | 📀 build: [tileboard-tester-v2p0]  |                 |         |

|                    |            |                                   |                 |         |

► To install/update the FW:

yum install -y hexaboard-hd-tester-v1p1-trophy-v2

# Gitlab chain for HGCAL software for single module/ROC tester

- Before having gitlab CI/CD for the SW

- DAQ server and DAQ client (c++) needed to be compile (using cmake tool) from source code

- DAQ server and client depend on several pre-requisites : ipbus-software (only server), zmq, yaml-cpp, boost ...

- Gitlab CI/CD for HGCAL software

- pipeline to build the software for aarch64 (server) and x86\_64 (client)

- split the pipeline into several steps and save container image after installing pre-requisite:

- 1 Build container image with centos7 and with installing pre-requisites

- 2 Build container image : compile cppzmq latest versions

- Build container image (only done for aarch64): compile HGCAL ipbus-software version + create and save RPM on the yum repository

- **4** Use 3rd image (resp. 2nd image) image to compile the DAQ server (resp. client) + create and save RPMs on the yum repository. Submodules (python SW) are also packaged inside the RPMs.

## Gitlab chain for HGCAL software: docker build template

• Docker build template being re-used in steps 1,2 and 3

| 1  | .build_template:                                                      |  |

|----|-----------------------------------------------------------------------|--|

|    | stage: build                                                          |  |

|    | image: docker                                                         |  |

|    | tags:                                                                 |  |

|    | - docker-privileged                                                   |  |

|    | services:                                                             |  |

|    | - docker:dind                                                         |  |

|    | before_script:                                                        |  |

|    | - docker runrmprivileged aptman/qusstaticp \${TGT_ARCH} # only        |  |

|    |                                                                       |  |

|    | - docker login -u \${CI_REGISTRY_USER} -p \${CI_REGISTRY_PASSWORD} \$ |  |

|    | {CI_REGISTRY}                                                         |  |

| 11 | 1 script:                                                             |  |

| 12 | - docker build                                                        |  |

| 13 | <pre>\${CI_PROJECT_DIR}</pre>                                         |  |

|    | file \${CI_PROJECT_DIR}/\${CONTEXT_DIR}/Dockerfile                    |  |

|    | tag \${REG_SLUG}:latest                                               |  |

|    | tag \${REG_SLUG}:\${CI_COMMIT_REF_NAME}                               |  |

|    | build-arg CI_COMMIT_REF_NAME=\${CI_COMMIT_REF_NAME}                   |  |

|    | - docker pushall-tags \${REG_SLUG}                                    |  |

| 19 |                                                                       |  |

|    |                                                                       |  |

#### Gitlab chain for HGCAL software: dockerfiles

• Step 1: starting from centos 7 image + install pre-requisite

• Step 2: compile and install cppzmq (from a fork of cppzmq in which we added the CI pipeline)

FROM gitlab-registry.cern.ch/hgcal-daq-sw/docker-images/centos7/ centos7-aarch64:latest ADD / //home/centos7-with-cppzmq ENV (CPP2M0 pATH="/home/centos7-with-cppzmq" ENV BUILD DIR="/home/centos7-with-cppzmq"build" NUM mkdir -p s(BUILD DIR) && cd s(BUILD DIR) && cmake3 ../ && make .j`nproc` && make install && cpack3 && is S(BUILD DIR) && cmake3 ../ && make .j`nproc` &&

• Step 3: compile HGCAL version (to have AXI over UIO over uhal) ipbus-software

| FROM gitlab-registry.cern.ch/hgcal-daq-sw/docker-images/centos7-with-cppzmq/centos7-aarch64:latest |

|----------------------------------------------------------------------------------------------------|

| # This is where the COPY/ADD would go to get the git repo                                          |

| ADD ./ /home/ipbus-software                                                                        |

| # This is where the building process would go                                                      |

| ENV ORIGINAL PATH="/home/ipbus-software"                                                           |

| ENV LONG ENOUGH PATH="/home/ipbus-software "                                                       |

| RUN lscpu \                                                                                        |

| 66 mv \${ORIGINAL PATH} \${LONG ENOUGH PATH} \                                                     |

| 66 mkdir -p \${ORIGINAL_PATH} \                                                                    |

| 66 cd s{LONG_ENOUGH PATH} \                                                                        |

| <pre>&amp;&amp; export CPLUS INCLUDE PATH="\$CPLUS_INCLUDE_PATH:/usr/include/python3.6n/" \</pre>  |

| && make -k -j`nproc' Set=uhal \                                                                    |

| && make install -j`nproc` Set=uhal \                                                               |

| ‱ export PACKAGE_RELEASE_SUFFIX=hgcal_v0_0_0 ∖                                                     |

| 55 make -k Set=uhal PACKAGE_RELEASE_SUFFIX=s(PACKAGE_RELEASE_SUFFIX) rpm \                         |

| && cp `findiname "*.rpm"` \${ORIGINAL_PATH} \                                                      |

| 66 ls s{ORIGINAL_PATH}                                                                             |

|                                                                                                    |

• Need  $\approx$  30 mins on shared runner  $\rightarrow$  important to have this step separated

#### Gitlab chain for HGCAL software: last step

• Build DAQ server for aarch64:

#### • Build DAQ client for x86\_64

#### • CI/CD pipeline

#### Summary and next plans

- Using gitlab pipelines and RPMs for software and firmware building and deployment. Helpful for:

- FW/SW developers as it gives quick confirmation if a commit is OK

- FW/SW developers as it garanties that the users are using right version of FW/SW and all their submodules

- Users: "yum install ..." without having to compile from source is easier and more convenient. It avoid issues with different pre-requisite versions ...

- Issue in getting Trenz modules with infinite delivery dates (9.9.9999)

- Considering using Kria modules instead of Trenz

- Move from Vivado 2019.2 to 2021.2

- Will then have Trenz, Kria and ZCU102 systems

- Plan to automatize PetaLinux build