# Laser-Scribing and Al<sub>2</sub>O<sub>3</sub> Sidewall Passivation of P-Type Sensors

Marc Christophersen<sup>1</sup>, Bernard F. Phlips<sup>1</sup>, Vitaliy Fadeyev<sup>2</sup>, and Hartmut F.-W. Sadrozinski<sup>2</sup>

Code 7654, U.S. Naval Research Laboratory;

Santa Cruz Institute for Particle Physics, University of California Santa Cruz

Contact: marc.christophersen@nrl.navy.mil +1-202-404-2448

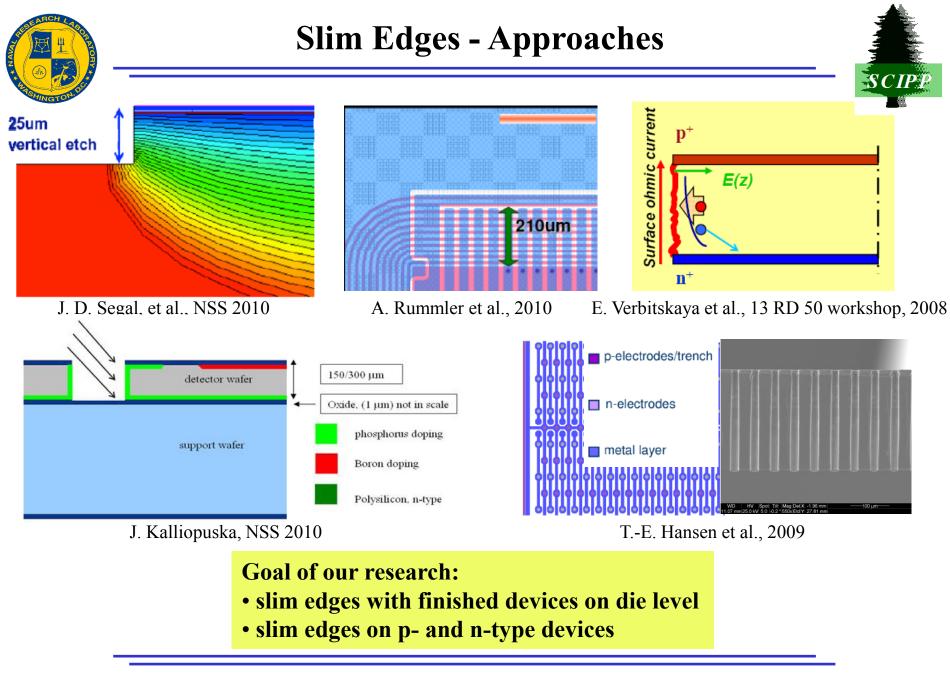

- Slim Edges Motivation and Approaches

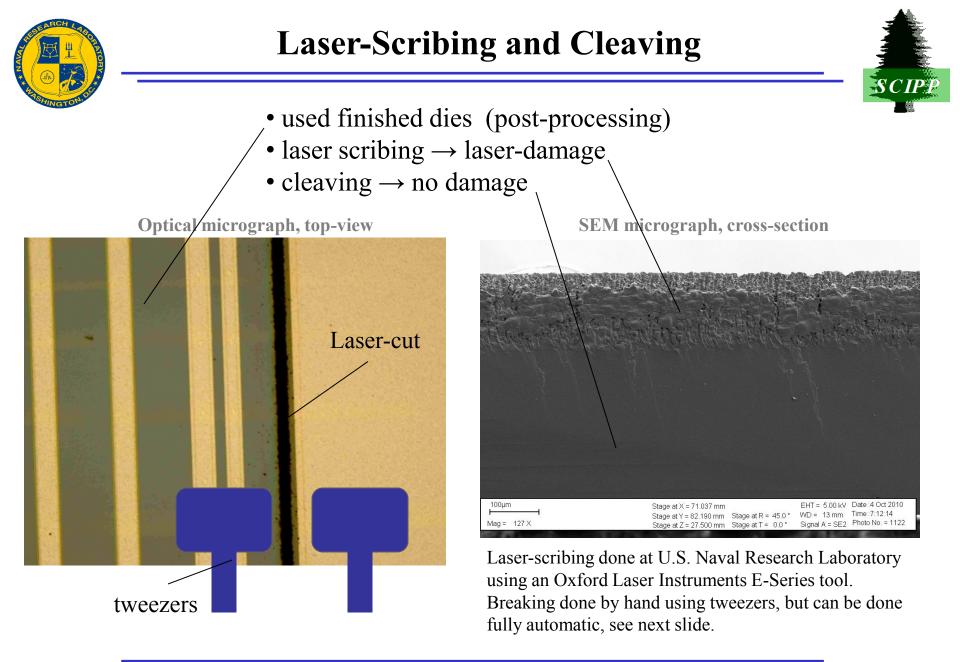

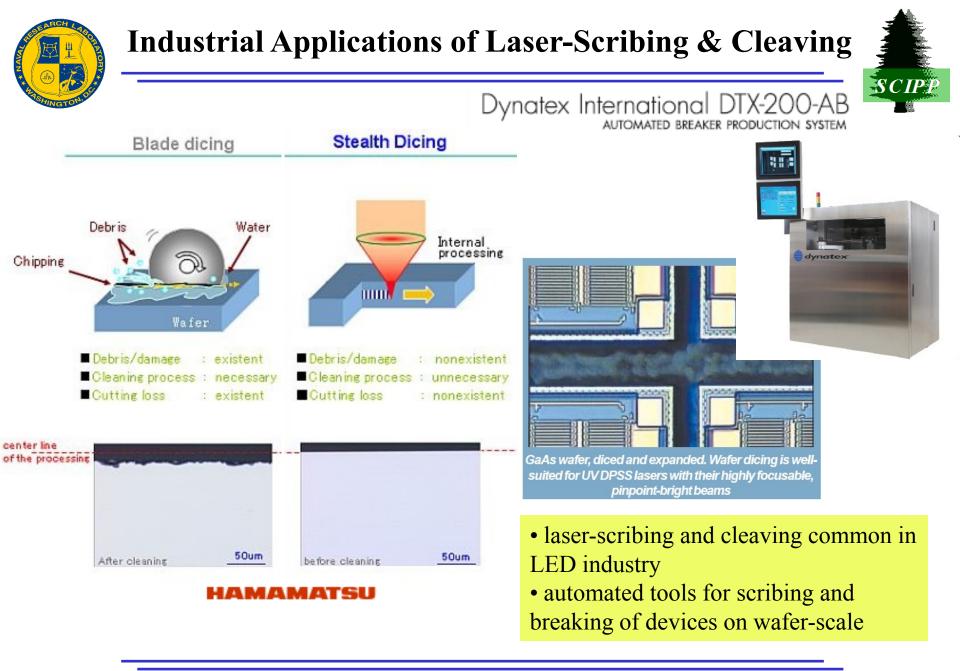

- Laser-Scribing and Cleaving

- Results for N-Type Sensors

- Laser Parameters

- IV Curves for N-Type Sensors

- Results for P-Type Sensors

- Alumina for P-Type Silicon Passivation

- Introduction into Atomic Layer Deposition (ALD)

- Silvaco Simulations for P-Type sensors

- IV Curves for P-Type Diodes with Alumina Passivation

- Conclusions and Outlook

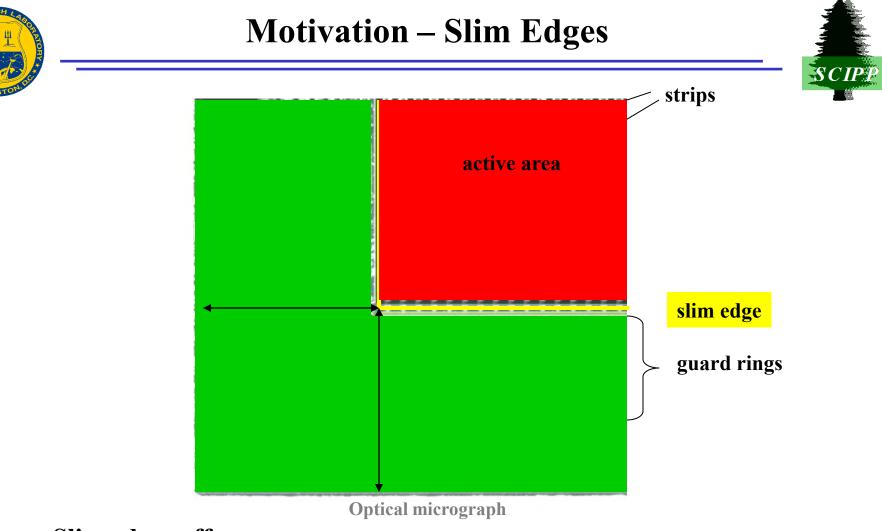

#### Slim edges offer:

- better tiling of sensors (especially for imaging applications)

- reduced inactive area

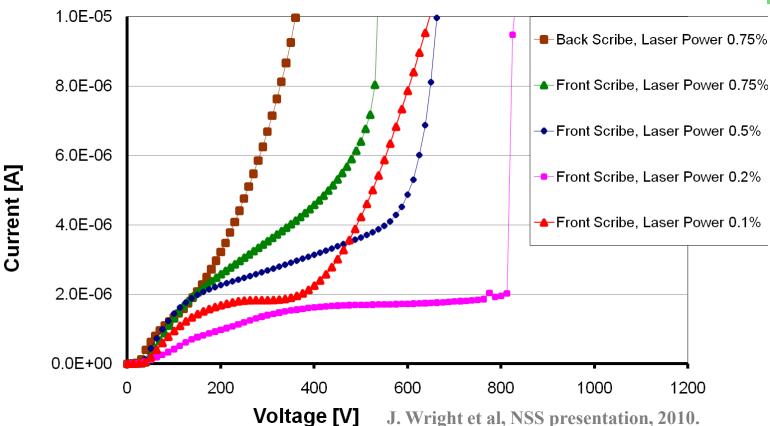

## N-Type Sensor Results – NSS 2010

7

- scribe at 100 um from the guard ring.

- front-side scribe seems to be preferential to back-side one.

- lower laser power is preferential.

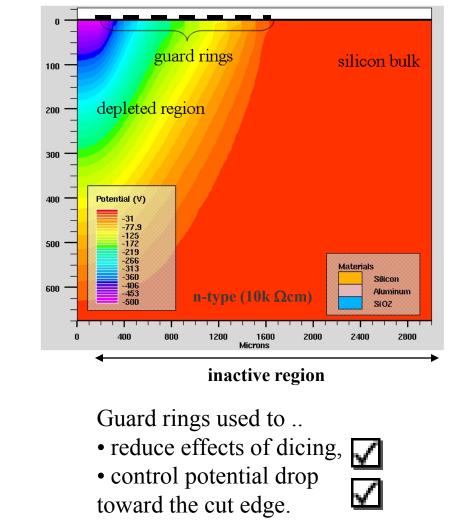

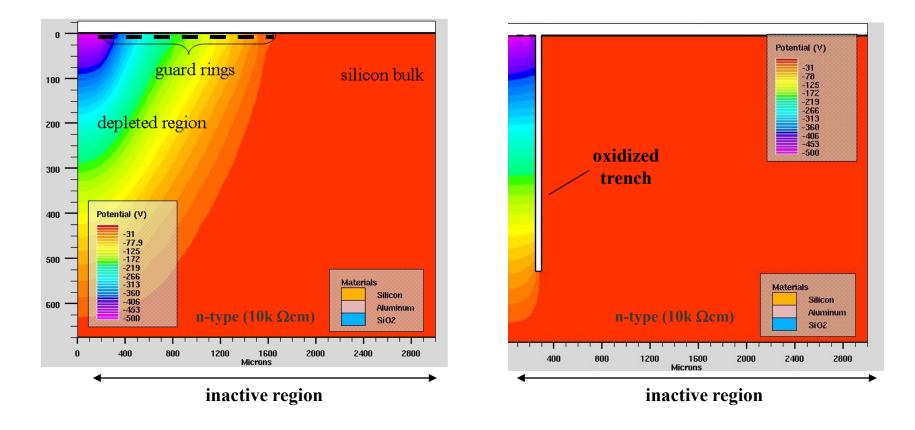

# How Do We Establish Controlled Potential Drop?

Silvaco simulations

#### How Do We Establish Controlled Potential Drop? N-Typ Si

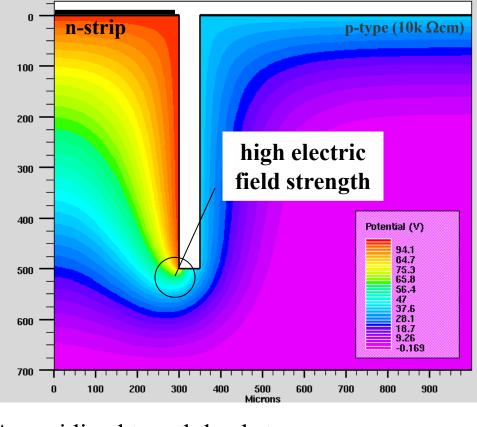

A passivated trench with a thermally grown oxide (**positive** charge density 10<sup>11</sup> cm<sup>-2</sup>) trench will lead to:

- control potential drop toward the cut edge,

- protection from saw cut edge.

#### How Do We Establish Controlled Potential Drop? N-Typ Si

"6th Trento Workshop", March 2-4, 2011

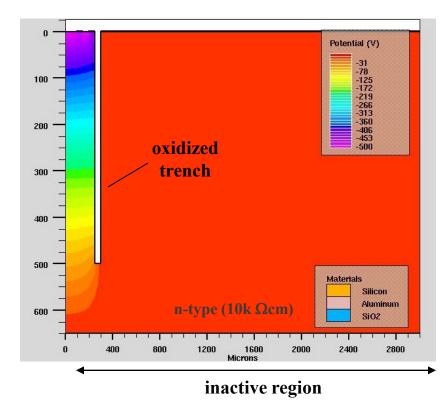

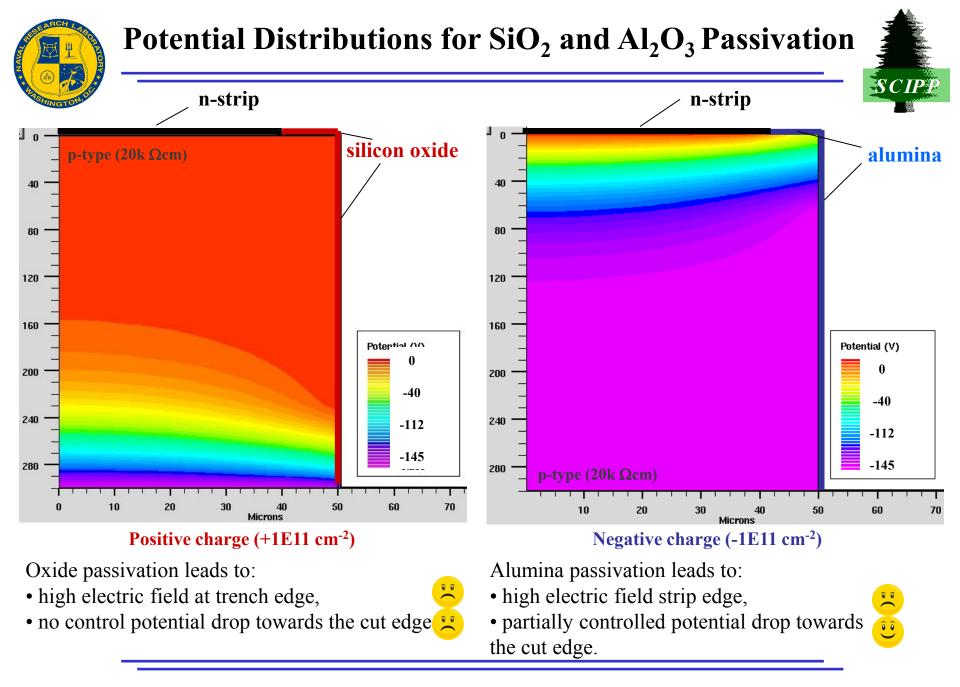

# **Oxidized Trench for P-Type Si**

An oxidized trench leads to:

- high electric field at trench edge,

- no control potential drop toward the cut edge,

- no protection from saw cut edge.

"6th Trento Workshop", March 2-4, 2011

ชิ ชิ

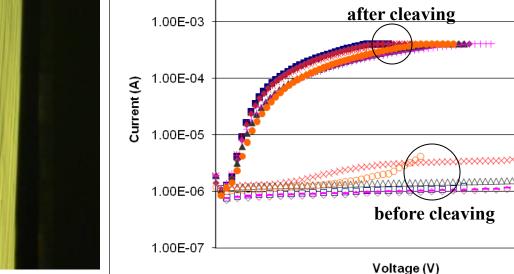

## **P-Type Sensor – NSS 2010 Presentation**

□W16 #3

◇W16 #4 ♦W16 cut #4 ×W18 #3

W16 cut #3

XW18 cut #3 △W18 #4

▲W18 cut #4 --W23 #3 +W23 cut #3

OW23 #4

W23 cut #4

50

100

**Optical micrograph, cross-section**

- Some of the sensors showed a relatively early breakdown voltages of 200/300 V before the procedure.

- Processed sensors show a uniform early breakdown at  $\sim 20$  V.

1.00E-02

• We also tested Micron and HPK p-type sensors.

J. Wright et al., NSS presentation 2010

200

250

300

350

150

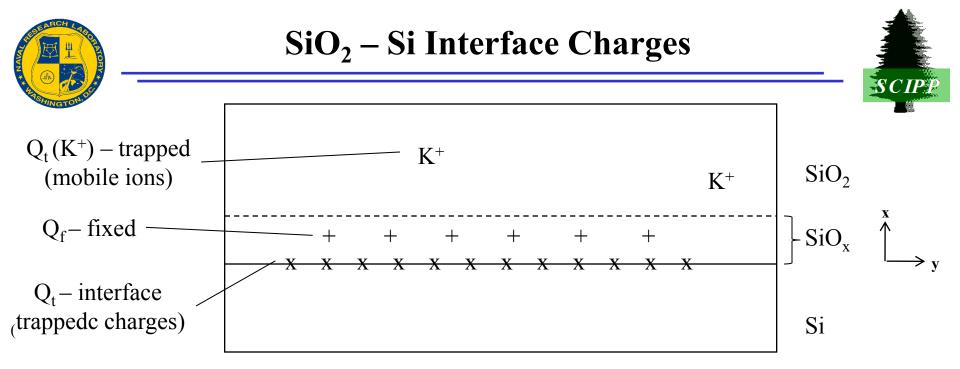

"Origin" of excellent passivation for **n-type Si**:

-Thermally grown oxides typically have from ~  $10^{10}$  to  $1-2x10^{11}$ **positive** charges per cm<sup>2</sup>, localized within about 35 Å of the Si/SiO<sub>2</sub> interface [Silicon Processing for the VLSI Era (Vol I), S. Wolf and R. Tauber, Lattice Press 1986, p. 223].

- surface recombination rate: FZ n-type Si (10  $\Omega$ cm): ~ 60 cm/s

<sup>&</sup>quot;6th Trento Workshop", March 2-4, 2011

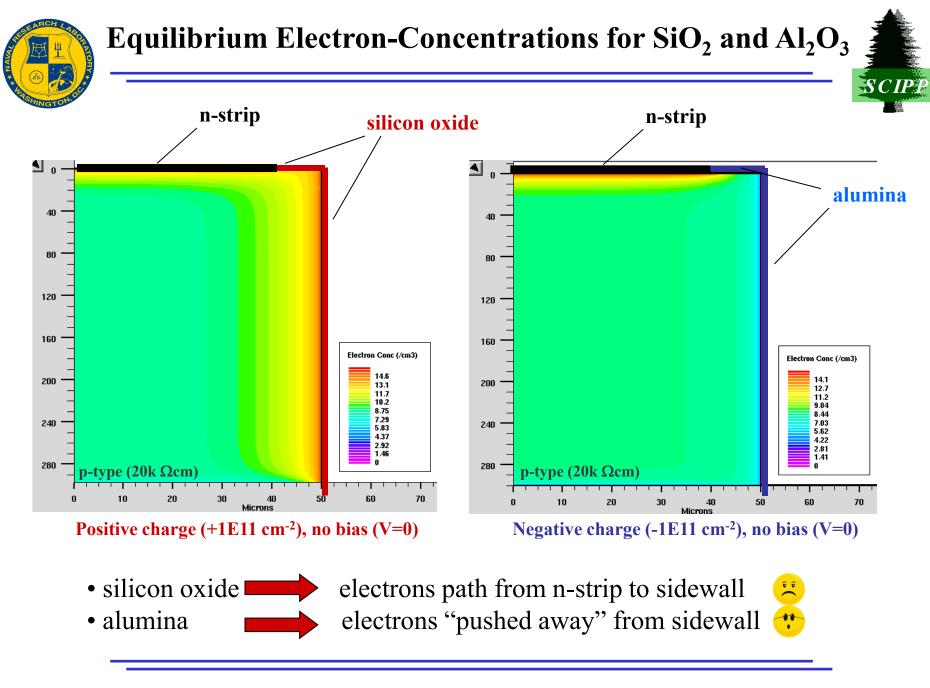

# **Negative Surface Charge for P-Type Passivation**

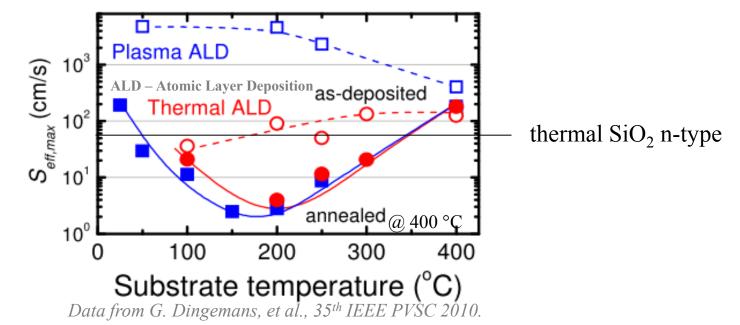

Surface recombination rate for FZ p-type Si (2  $\Omega$ cm), Al<sub>2</sub>O<sub>3</sub> passivation

- low recombination rate after  $Al_2O_3$ passivation  $\rightarrow$  high carrier life time

- detector material  $k\Omega cm \rightarrow$  higher life times

- fixed *negative* interface charge

- low temperature process (< 400 °C)

- standard process in solar cell industry

# Negative interface charge enables effective surface passivation for p-type Si.

Values for surface recombination rate and charge density for  $Al_2O_3$ /p-type Si are comparable to SiO<sub>2</sub>/n-type Si.

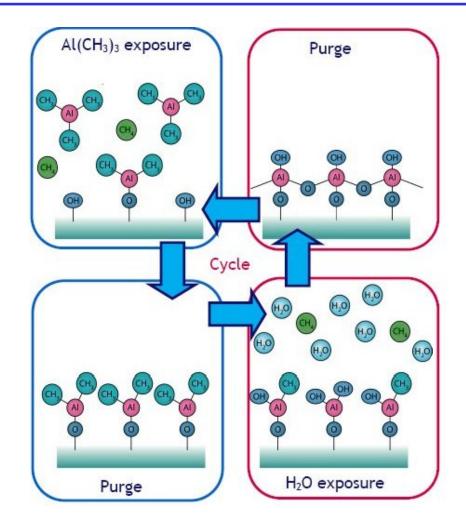

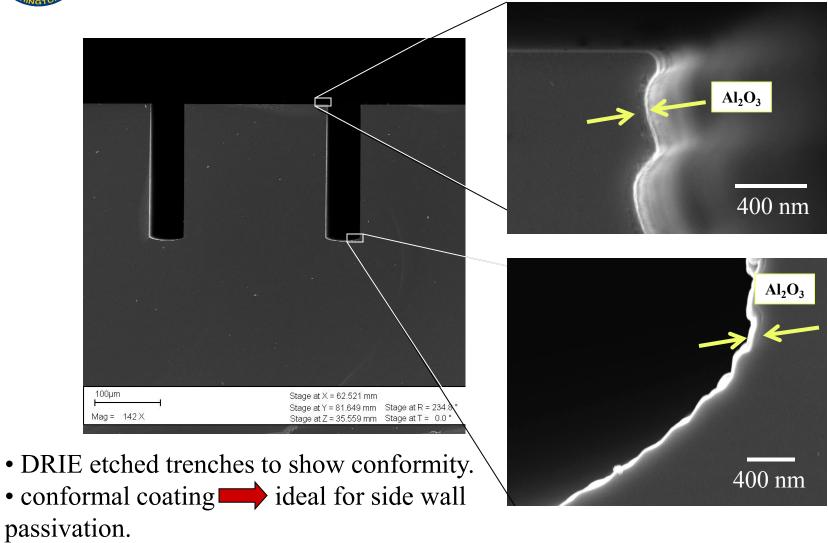

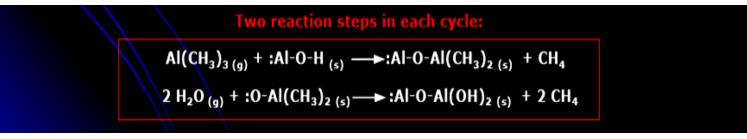

- Similar in chemistry to CVD (chemical vapor deposition), except that the ALD (**atomic layer deposition**) reaction breaks the CVD reaction into two half-reactions, keeping the precursor materials separate during the reaction.

- ALD film growth is **self-limited and based on surface reactions**, which makes achieving atomic scale deposition control possible.

- Perfect 3-D conformality, 100% step coverage: uniform coatings on flat, inside porous and around particle samples.

- Origin of negative interface charge: Functional surface groups on the silicon wafer are not optimal for an adsorption of the TMA (trimethylaluminium) precursor molecules, which leads to an incomplete reaction of the TMA and, consequently, an increased relative oxygen concentration at the interface (F. Werner et al., 25<sup>th</sup> European Photovoltaic Solar Energy Conference, Valencia, Spain, 6-10 September 2010).

## **U.S. Naval Research Laboratory's FlexAL®**

- FlexAL® from Oxford Instruments.

- plasma & thermal ALD in one flexible tool.

- stage temperature: 100 400 °C.

- installed at NRL's Nanoscience Institute.

# **Alumina ALD Deposition Cycle**

ALD Growth of  $Al_2O_3$  from  $Al(CH_3)_3$  and  $H_2O$

"6th Trento Workshop", March 2-4, 2011

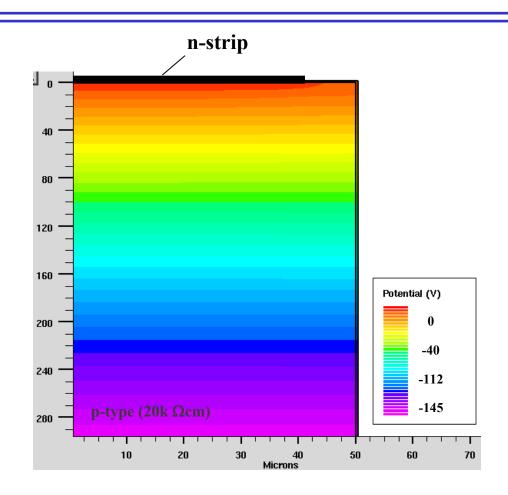

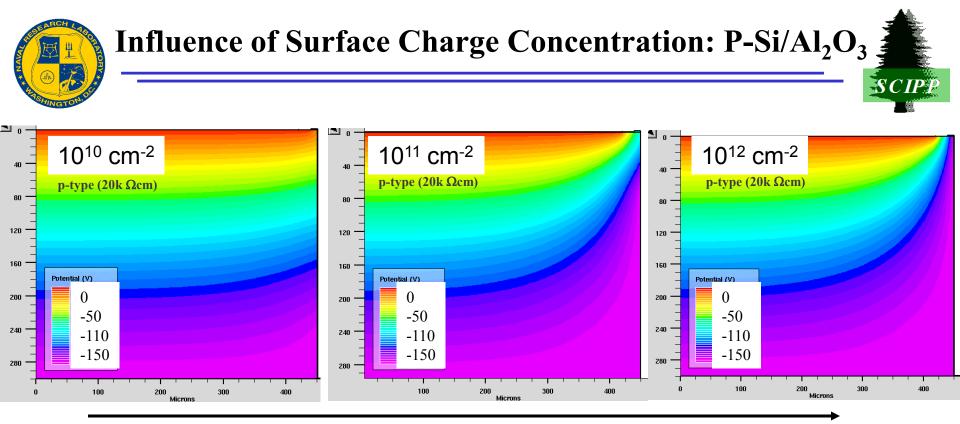

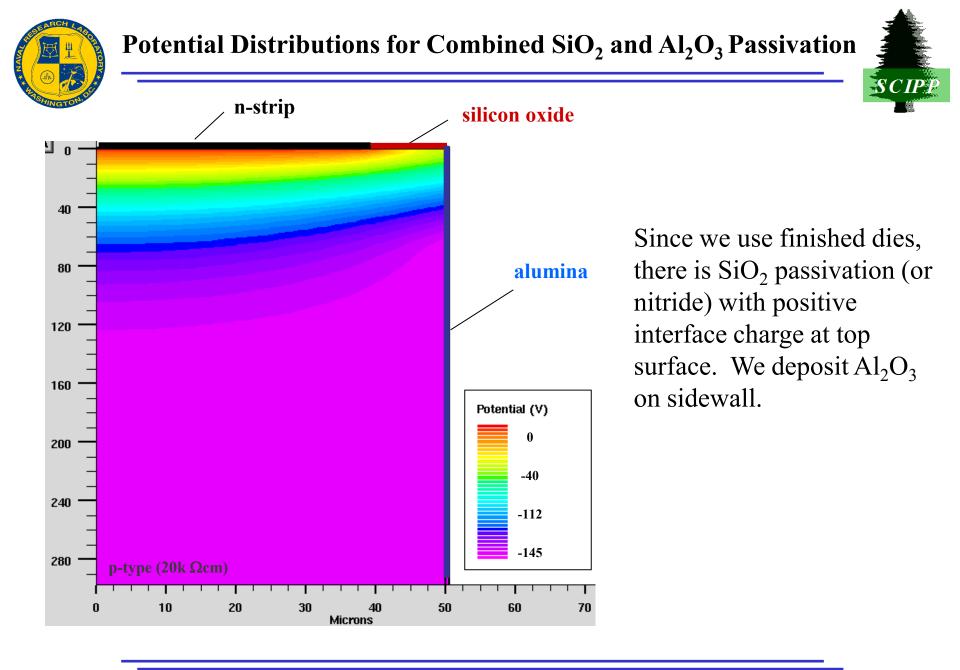

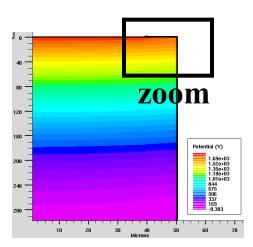

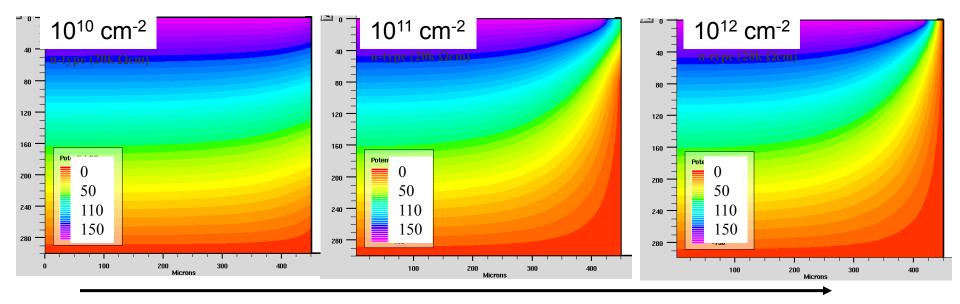

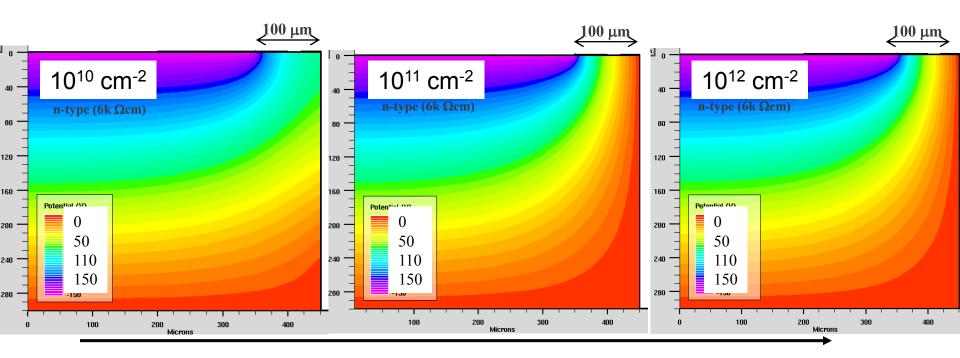

#### **Potential Distribution Without Surface Charge**

Not considering surface charges leads to *wrong* potential distribution at sidewall.

increasing negative surface charge

Typical literature values for alumina are ~  $10^{11} - 10^{13}$  cm<sup>-2</sup> depending on deposition conditions. BUT most research is focused on increasing (*not decreasing*) surface charge.

The potential drop at edge depends strongly on surface charge density.

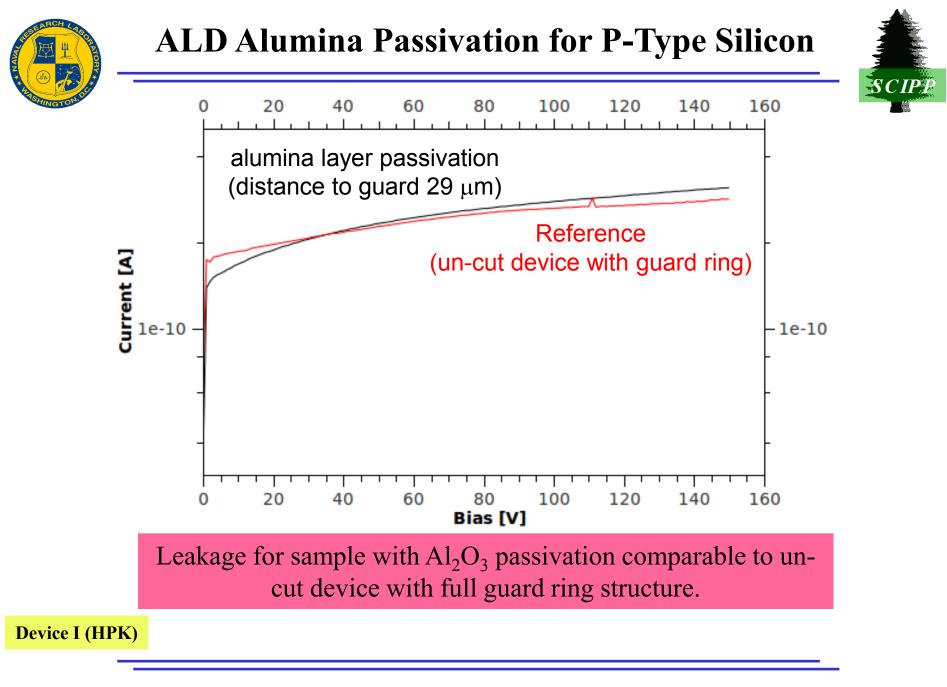

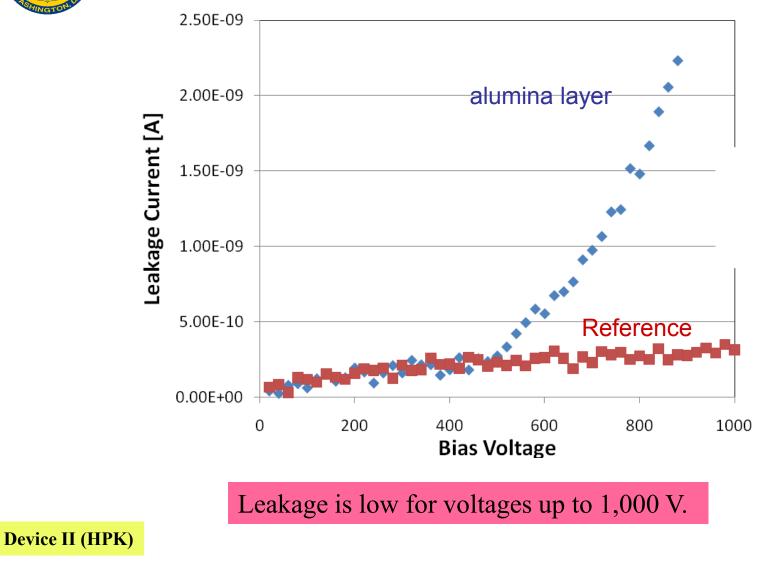

#### Low Leakage Currents up to 1,000 V

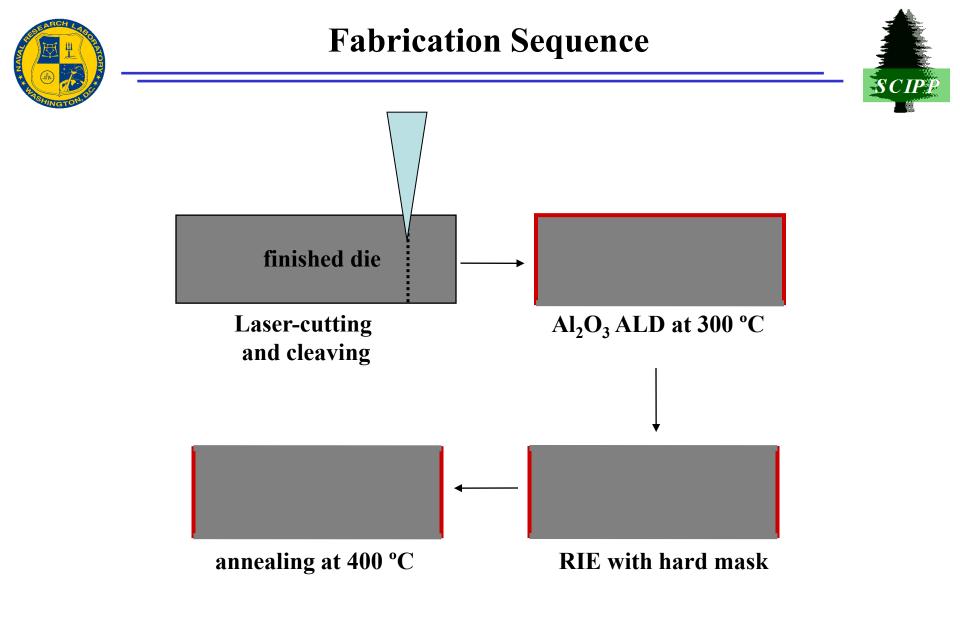

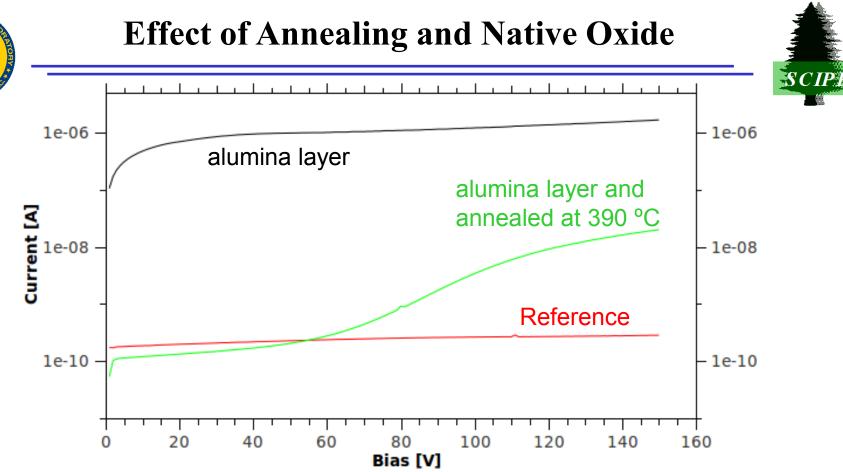

- annealing of alumina layer reduces leakage current (same effect as seen for solar cells, see slide #14 ).

- formation of native oxide (wrong surface charge)  $\uparrow$  leakage current.

- native oxide forms rapidly (within seconds/minutes) in air.

- native oxide:  $\sim 2$  nm thick, high charge trap density.

**Device III (HPK)**

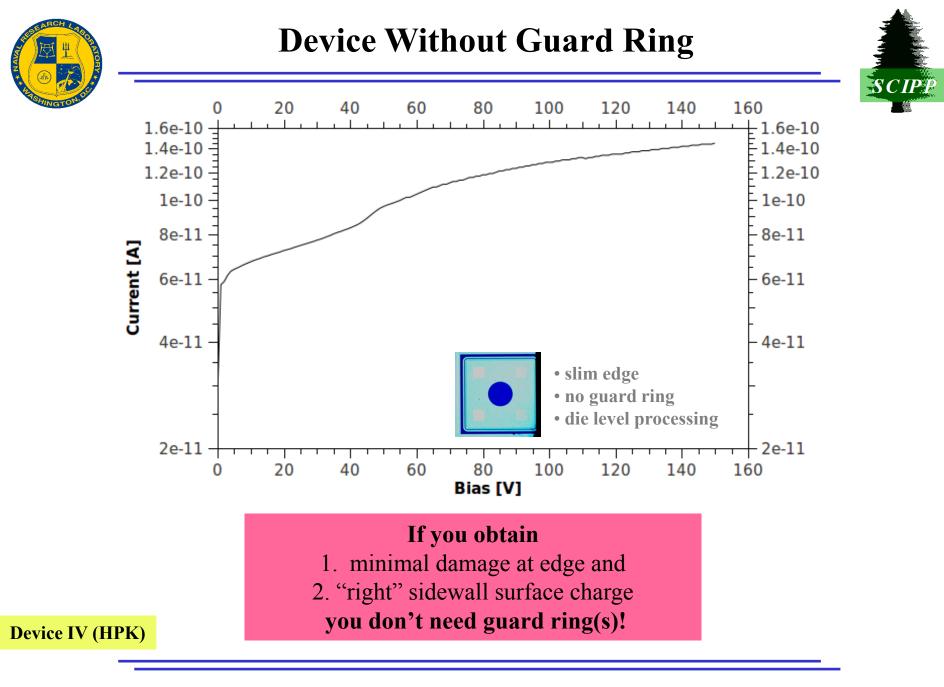

# **Device Without Guard Ring**

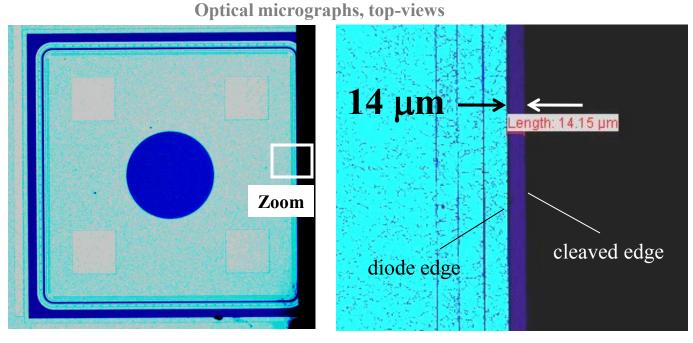

- No guard ring left.

- Slim edge (14  $\mu$ m distance to active area).

- Leakage current 0.1 nA (see next slide).

- Pure cleaving of sample (no laser damage).

- Alumina sidewall passivation (thermal Al<sub>2</sub>O<sub>3</sub> ALD at 300 °C).

- Done on finished die.

**Device IV (HPK)**

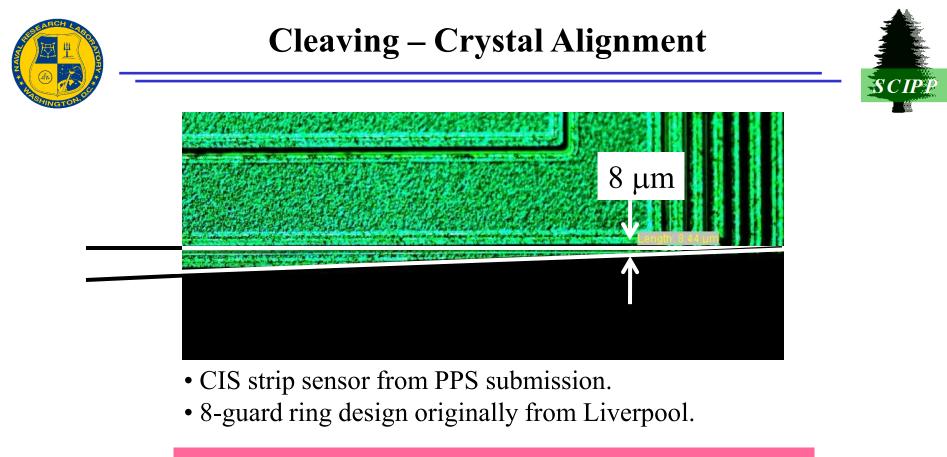

#### Cleaving is easier if

- device aligned with <100> direction,

- no mechanical stress from thin films.

SEMI standard for flat/crystal alignment: +/- 0.9 degrees typical values for FZ material: +/- 0.1 degrees

**Device V CIS**

• controlled potential drop towards edge.

"6th Trento Workshop", March 2-4, 2011

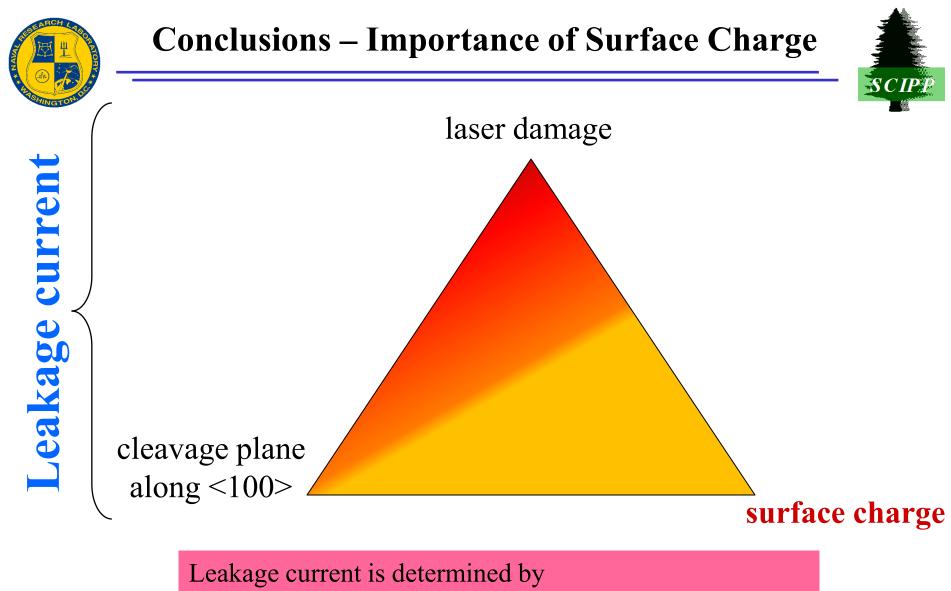

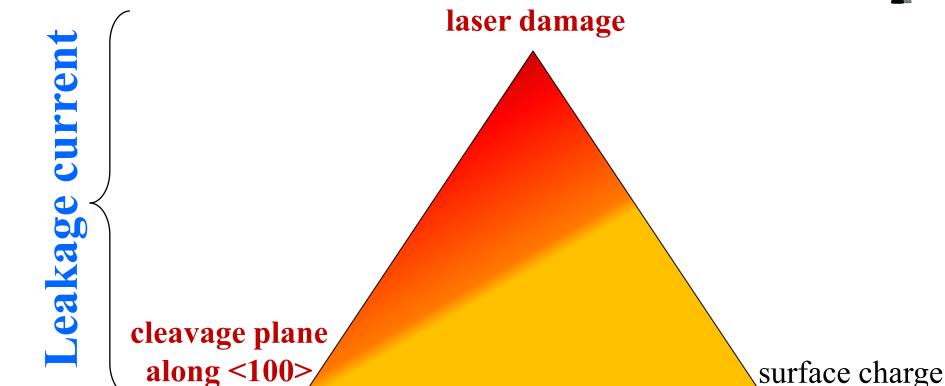

# **Conclusions – Importance of Sidewall Damage**

#### Leakage current is determined by

- controlled potential drop towards edge.

- "quality" of silicon edge (cleaving leads to *no* silicon damage).

- Laser damage  $\leftrightarrow$  distance to active area.

- Laser damage can be minimized by laser power and defocusing.

- Cleavage plane depends on alignment and breaking process.

- Cleaved sidewall has no silicon damage.

- N-type silicon requires **positive** side wall passivation.

- > **P-type** silicon requires **negative** side wall passivation.

- Alumina/silicon interface has negative charge.

- Alumina ALD passivation conformal, low-temperature process, low leakage currents, and can be used on finished die.

- We made a slim-edge p-type diode without guard ring and extremely low leakage currents (comparable to an active edge).

- If you obtain (i) minimal damage at edge and (ii) "right" sidewall surface charge you don't need guard ring(s)!

- We currently perform charge collection measurements.

- Adjustable surface charge by ALD deposition.

- Determine exact alumina/silicon interface charge (CV plots).

- Alumina surface charge region sensitive to radiation/dose?

# **Back-Up Slides**

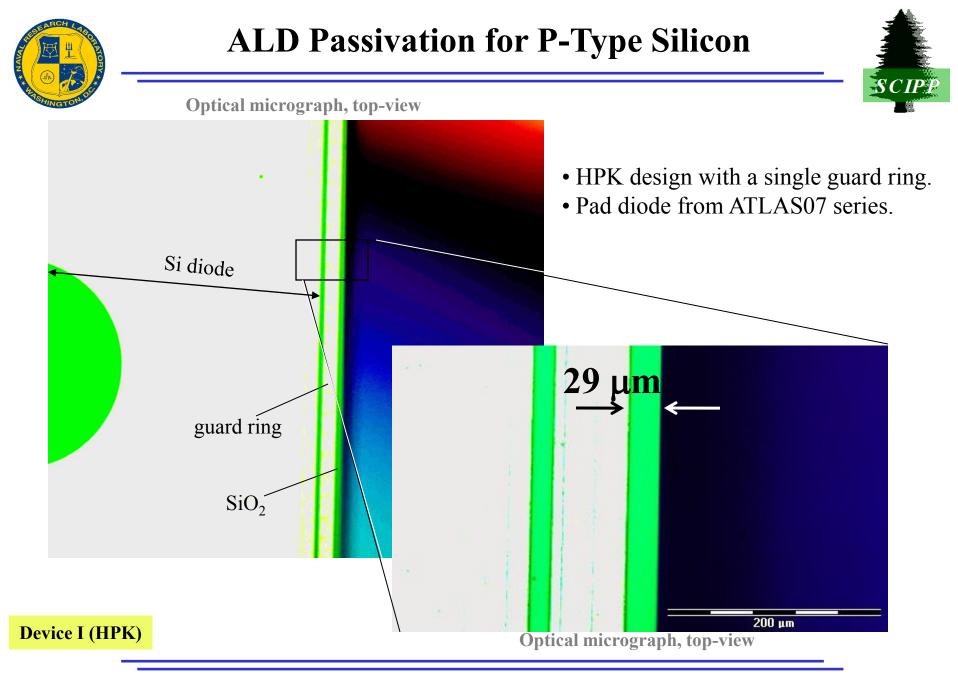

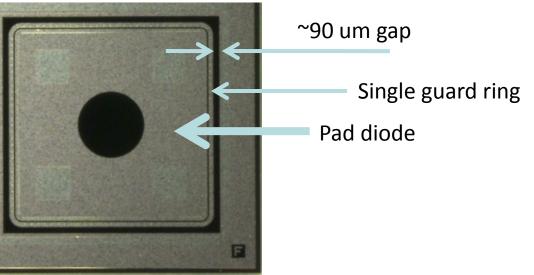

# **Devices I-IV: HPK Samples**

- Using a pad diode from HPK test structure meant to provide control over key sensor parameters for ATLAS07 sensors (\*).

- It features a classic HPK singleguard ring design.

- Simple DC-coupled n-on-p pad.

Vdepl ~ 180 V. Thickness 320 um.

(\*) ATLAS07 strip sensors have been developed for ATLAS tracker upgrade for higher luminosity. They served as test vehicle for inter-strip isolation, punch-through protection, and other studies.

#### **References:**

Y. Unno et al., "Development of n-on-p silicon sensors for very high radiation environments", NIM A, doi:10.1016/j.nima.2010.04.080.

S. Lindgren et al., "Testing of surface properties pre-rad and post-rad of n-in-p silicon sensors for very high radiation environment", NIM A, doi:10.1016/j.nima.2010.04.094 .

J. Bohm et al., "Evaluation of the bulk and strip characteristics of large area *n*-in-*p* silicon sensors intended for a very high radiation environment ", NIM A, doi:10.1016/j.nima.2010.04.093 .

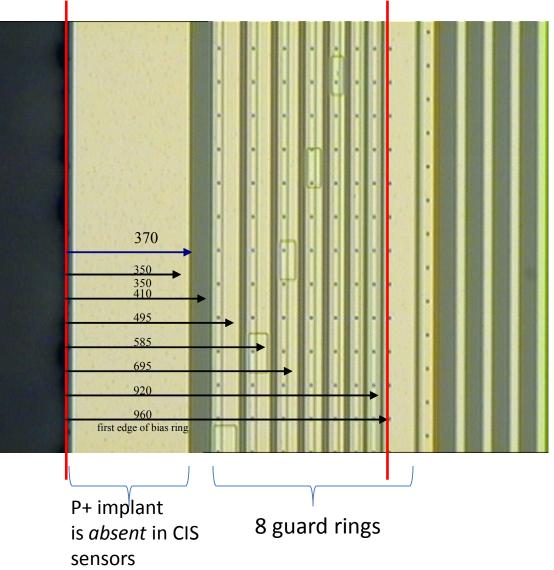

# Device IV: CIS Sensor

- These strip test structures were part of ATLAS Planar Pixel submission to CIS foundry.

- The basic design is the same that Liverpool group used in Micron submissions (\*).

- 8 guard ring structures. N-on-p sensor type. Vdepl ~50 V.

- The usual p+ implant structure at the periphery was specifically removed to facilitate the edge studies.

(\*) G. Casse, P.P. Allport, A. Greenall, "Response to minimum ionising particles of p-type substrate silicon microstrip detectors irradiated with neutrons to LHC upgrade doses", NIM A 581 (2007) p. 318.

## ALD – Step Coverage

• Releases sequential precursor gas pulses to deposit a film one layer at a time.

Two fundamental mechanisms:

- Chemisorption saturation process

- Sequential surface chemical reaction process

- Since each pair of gas pulses (one cycle) produces exactly one monolayer of film, the thickness of the resulting film may be precisely controlled by the number of deposition cycles.

- One TMA (trimethylaluminium) and  $H_2O$  vapor pulse per cycle, ~ 1 Å per cycle, pumping ~ 3 sec per cycle.

Laser-Scribing &  $Al_2O_3$  Sidewall Passivation of P-Type Sensors 39

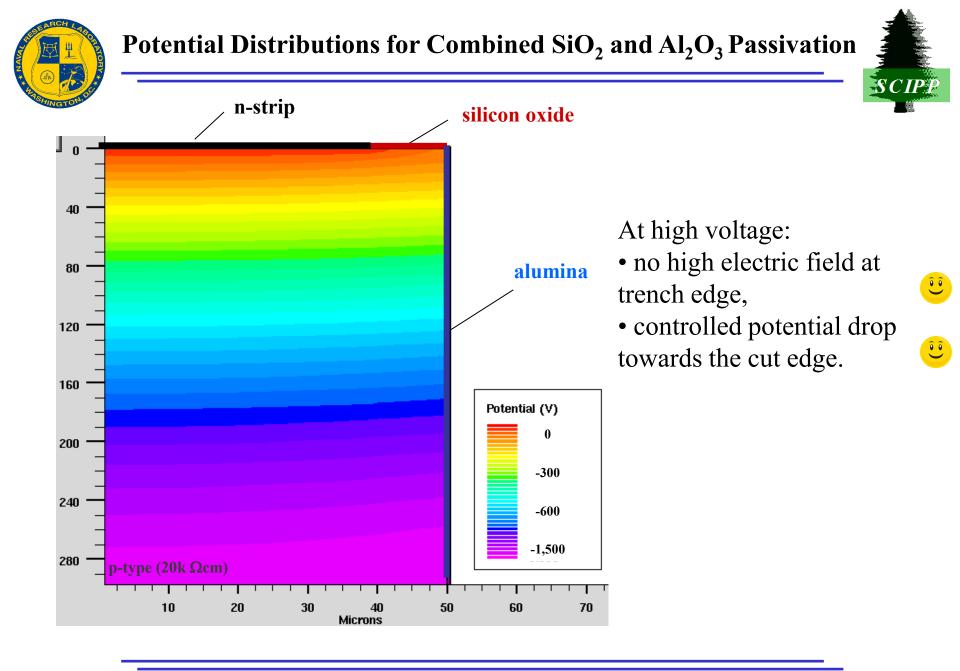

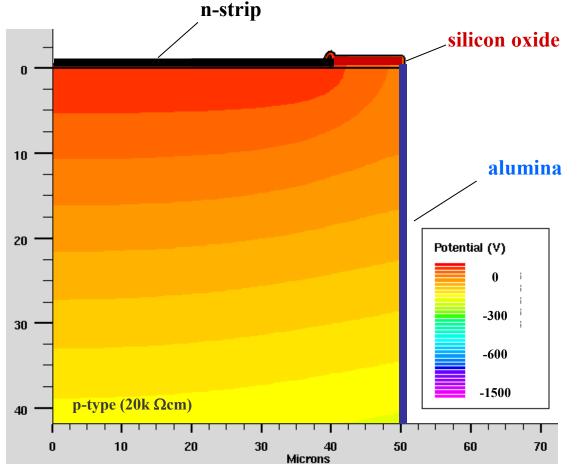

#### Potential Distributions for Combined SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> Passivation

0

<u>ê</u> ê

Ũ

At high voltage:

- no high electric field at trench edge,

- controlled potential drop towards the cut edge,

- no potential at surface.

### Influence of Surface Charge Concentration: N-Si/SiO<sub>2</sub>

increasing positive surface charge

"6th Trento Workshop", March 2-4, 2011

## Influence of Surface Charge Concentration: N-Si/SiO<sub>2</sub>

increasing positive surface charge

The simulation is done for p-on-n strips on top surface.