### LHCb Upgrade Electronics

#### Mailing list:

Go to simba.cern.ch, search for lhcb-upgrade-electronics

#### Link to upgrade electronics meetings:

http://lhcb-elec.web.cern.ch/lhcb-elec/html/upgrade.htm

#### Meetings in 2011:

10th February (TFC for discussion)

14<sup>th</sup> April

9<sup>th</sup> June

11<sup>th</sup> August

13<sup>th</sup> October

8th December

#### News

#### Reminder:

Working group on FPGAs in radiation environment: See mail from Jorgen If you are interested to join, please contact me

#### **ACTEL FPGA irradiations:**

1<sup>st</sup> tests by Syracuse 2<sup>nd</sup> run in planning for early 2011 Parallel irradiation (at CERN?) to be investigated OT + Calo interested so far (maybe also CMS HCAL): anyone else?

#### Front-end simulations (Tomasz Skwarnicki):

Data available (contact Tomasz)

Sub-detectors starting: Velo well advanced & already producing output for TELL40 simulations — next meeting in January

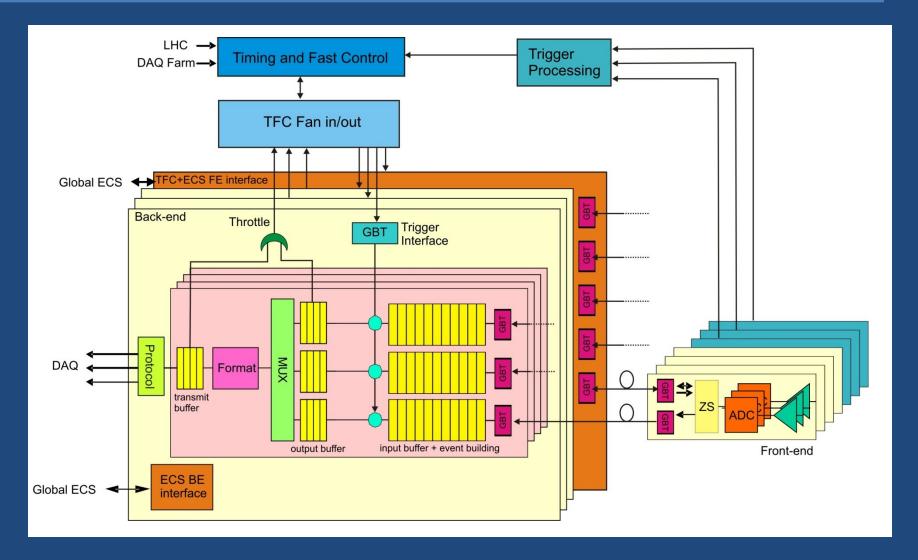

# Architecture: Agree on separation of DAQ from TFC/ECS

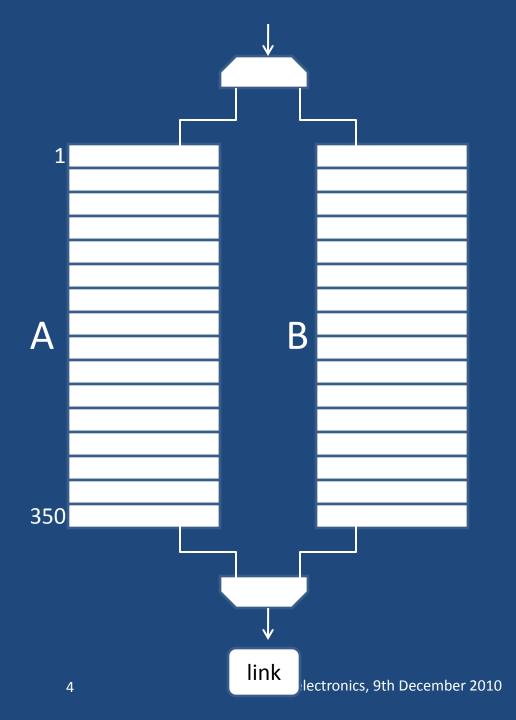

## Front-end buffer implementation

Traditional FIFO or RAM (a la Calo)

Introduces some synchronicity within and between subdetectors (later BXs in the 350 will be the truncated ones)

Dependent on bunch time structure ACTEL users can re-configure 'easily', but others....? Large RAM not so easy to implement in FE ASICs Adds latency to data (350 cycles on average)...... if trigger latency is still 160 cycles, we'll need to buffer triggers