# Update of Development of ECS unit for Counting Room Electronics

## André Massafferri Pablo Diniz Herman Lima Fernando Sousa **Leonardo Lessa** Irina Nasteva

Centro Brasileiro de Pesquisas Físicas (CBPF), Rio de Janeiro, Brasil

## Electronics Meeting, 9<sup>th</sup> december 2010

# Topics

- 2 The Design

- 3 The Development

- The Hardware

- CCPC Software

- PCIe core  $\leftrightarrow I^2C$

- NIOS & JTAG

- 4 The prototype

- 5 Conclusion and Remarks

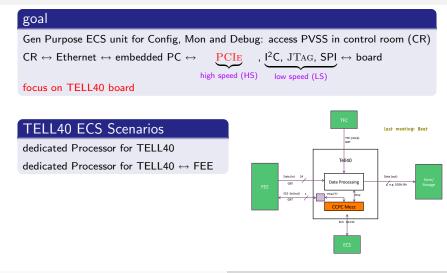

# The concept of the project

# The concept of the project

#### Schedule expectation

Prototype  $\rightarrow$  Final HW & SW  $\rightarrow$  Validation 2011-12

Mass Production  $\rightarrow$  Installation (?)/16

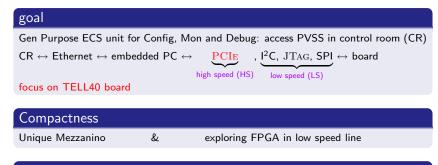

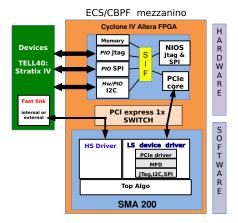

## The Design

- CCPC with 2 PCIe lanes:

- 1Gbs LAN + Switch

- Switch drives:

- $\rightarrow$  10 PCIe lines to TELL40

- HS block transfer

- $\rightarrow$  1 PCIe lane to FPGA

- translation to LS protocols

- 10 outputs I<sup>2</sup>C

- 10 outputs JTAG <u>no chain</u>

- 2 outputs SPI

## The Design: main components

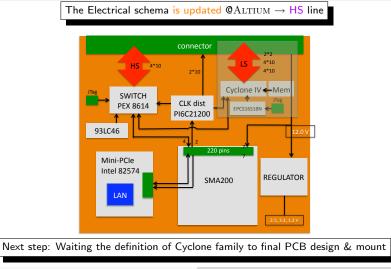

# The embedded PC: SMA 200 digital logic SmartCore Atom Z530, 1GB, DDR2 RAM 1.1 GHz, connector and heatspreader PCle 1.0: 2 lanes x1 (2.5Gbs) The FPGA → LS line: Cyclone /V GX EP4CGX22: 22k LEs, 150 I/Os, 4 transceivers or (to be studied) EP4CGX15: 14.4k LEs, 72 I/Os, 2 transceivers The PCle Switch → low latency, 1+10 ports: PEX 8614

The Ethernet: Mini-PCle Form Factor (Intel 82574L) (at least for 1<sup>0</sup> prototype)

# The ReDesign: HW & SW diagram

The Hardware CCPC Software PCIe core  $\leftrightarrow l^2C$  NIOS & JTAG

## The Hardware

- CBPF Setup → SMA200 & Arria II kits

- CERN Setup → SMA200 (thanks Beat & Niko) & Cyclone IV (thanks Guido) kits

- next year ECS-CBPF proto < − ▷ Validation board (test protocol + guideline for Collaboration concerning implementation of PCIe physical lines)

The Hardware CCPC Software PCIe core  $\leftrightarrow 1^2$ C NIOS & JTAG

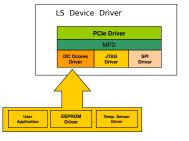

# The CCPC Software: driver

#### The previous driver release:

- Probe and identify the device on PCI Bus

- 2 Allocate resources on PCI device for use in other drivers

- Provide access for UserApp directly to PCIe device

The Hardware CCPC Software PCIe core  $\leftrightarrow 1^2$ C NIOS & JTAG

# The CCPC Software: driver

#### The new driver (phylosofy useful to SOPC builder)

- The UserApp cannot access the PCI regs directly

- Each controller have your own driver and the UserApp access from it

The Hardware CCPC Software PCIe core  $\leftrightarrow 1^2$ C NIOS & JTAG

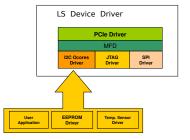

# The CCPC Software: driver

#### The new driver (phylosofy useful to SOPC builder)

- The UserApp cannot access the PCI regs directly

- Each controller have your own driver and the UserApp access from it

- Output Section 2 PCIe Device Driver: inherited from first release and included an interrupt handler → working on it

- Multi-Function Device Driver: Kernel Driver for devices with > 1 function; responsible for distribute the resources

- 5 <u>I2C Ocores Driver</u>: Abstract the control of the i2c controller → need to integrate with interrupt handler

- JTAG and SPI Driver: soon

The Hardware CCPC Software PCIe core  $\leftrightarrow I^2C$  NIOS & JTAG

# $\mathsf{PCIe}\ \mathsf{core}\ \leftrightarrow\ \mathsf{I}^2\mathsf{C}$

## PCIe core: SOPC builder

(1) fully featured PCI Express block component  $\rightarrow$  only native endpoint

PCI Express Avalon-MM Bridge: translate messages across the busses, a built-in PCI Express Protocol Stack (Completer/Requester) and Interrupt controller

The Hardware CCPC Software PCIe core  $\leftrightarrow I^2C$  NIOS & JTAG

# $\mathsf{PCIe}\ \mathsf{core}\ \leftrightarrow\ \mathsf{I}^2\mathsf{C}$

## PCIe core: SOPC builder

(1) fully featured PCI Express block component  $\rightarrow$  only native endpoint

PCI Express Avalon-MM Bridge: translate messages across the busses, a built-in PCI Express Protocol Stack (Completer/Requester) and Interrupt controller

## I<sup>2</sup>C OpenCore Controller

- Compatible with Philips I<sup>2</sup>C Standard

- 2 SW programmable clock frequency

- One of the second se

- Supports 7 and 10 bits addr mode

- 6 Adapted to use with Avalon-MM as slave

- More than one controller can be used on system

The Hardware CCPC Software PCIe core  $\leftrightarrow l^2C$  NIOS & JTAG

# $\mathsf{PCIe}\ \mathsf{core}\ \leftrightarrow\ \mathsf{I}^2\mathsf{C}$

## PCIe core: SOPC builder

$\textcircled{0} \ \ \mbox{fully featured PCI Express block component} \rightarrow \mbox{only native endpoint}$

PCI Express Avalon-MM Bridge: translate messages across the busses, a built-in PCI Express Protocol Stack (Completer/Requester) and Interrupt controller

## I<sup>2</sup>C OpenCore Controller

- Compatible with Philips I<sup>2</sup>C Standard

- 2 SW programmable clock frequency

- 3 Normal / Fast and High Speed Operation mode

- Supports 7 and 10 bits addr mode

- 6 Adapted to use with Avalon-MM as slave

- More than one controller can be used on system

As soon as the interruption issue at driver level is finalized  $({\rm few \ weeks})$  the  $I^2C$  CHAIN will be ready for validation

The Hardware **CCPC** Software PCIe core  $\leftrightarrow l^2 C$ NIOS & JTAG

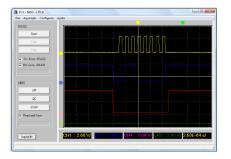

# NIOS & JTAG

- NIOS will be used to hold LS protocols but I<sup>2</sup>C

- We have finished an interface to Test NIOS performance

- SPI of ECS is done

- I<sup>2</sup>C is done, for test purpose

$\bullet \ JTAG \ {\rm SOLUTIONS} \left\{ \begin{array}{l} {\sf C} \ code \ {\sf Player} \ {\sf NIOS}: \ {\sf Compiled} \rightarrow {\sf ready} \ {\sf for} \ {\sf testing} \\ {\sf comercial} \ {\sf IC} \ {\sf on} \ {\sf NIOS} \ {\sf output}: \ {\sf just} \ {\sf start} \\ {\sf JTAG} \ {\sf code} \ {\sf running} \ {\sf in} \ {\sf SMA200}: \ {\sf under} \ {\sf investigation} \end{array} \right.$

## The Geometry

• Geometry: The Collaboration has defined the utilization of 2 slots for TELL40 space limitation & air flux is not a concern for our mezzanino (remind the

additional cards: SMA200 with heatspreader, Ethernet)

## The Schematic

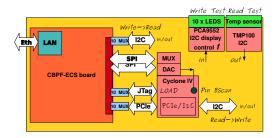

## The Validation board

• Validation Board: First approach  $\rightarrow$  Test all 10 lines of JTAG (Load and Boundary Scan Test), I<sup>2</sup>C and PCIe as well as the High Speed connectivity. Read (Temperature sensor) and Write (LED frequencies) Phases, to be applied to I<sup>2</sup>C and PCIe $\leftrightarrow$ I<sup>2</sup>C lines ... (thousand ideas: Read-Write on Memory, .... need to think on MUX/switch to drive the lines

# $$\label{eq:constraint} \begin{split} \text{We have redefined} & \left\{ \begin{array}{l} \text{HS} \rightarrow \text{10 PCle lines} \\ \text{LS} \rightarrow \text{1 PCle} \rightarrow \text{10 * [ } I^2\text{C} + \text{JTAG]} + 2 \text{ * SPI ]} \\ \end{array} \right. \end{split}$$

new CERN Setup ready

start design the Validation board

# We have redefined $\left\{ \begin{array}{l} \text{HS} \rightarrow 10 \text{ PCle lines} \\ \text{LS} \rightarrow 1 \text{ PCle} \rightarrow 10 \text{ * } [ \text{ I}^2\text{C} + \text{JTAG} ] + 2 \text{ * SPI } ] \\ \end{array} \right.$

new CERN Setup ready

start design the Validation board

## • THE PCIE FPGA CORE & LOW LEVEL DRIVER:

- First Version of the PCIe using Memory Mapped in SOPC is ready

- Second Version of the SCL driver using Memory Mapped under

construction

new phylosofy need to be validated and require some tricky treatment of interruptions

We have redefined  $\left\{ \begin{array}{l} {\sf HS} \rightarrow 10 \mbox{ PCle lines} \\ {\sf LS} \rightarrow 1 \mbox{ PCle} \rightarrow 10 \mbox{ * [ } {\sf I}^2{\sf C} + \mbox{ JTAG]} + 2 \mbox{ * SPl ]} \end{array} \right.$

### • The Output Communication:

SPI is ready in NIOS

I<sup>2</sup>C is ready outside (main solution) and inside (for test purpose) NIOS

JTAG: three solutions are under investigation  $\rightarrow$  C code player running NIOS

(under test), running in SMA200 and the usage of a commercial device

We have redefined  $\left\{ \begin{array}{l} {\sf HS} \rightarrow 10 \mbox{ PCle lines} \\ {\sf LS} \rightarrow 1 \mbox{ PCle} \rightarrow 10 \mbox{ * [ } {\sf I}^2{\sf C} + \mbox{ JTAG]} + 2 \mbox{ * SPl ]} \end{array} \right.$

## • The Output Communication:

SPI is ready in NIOS

$I^2C$  is ready outside (main solution) and inside (for test purpose) NIOS

JTAG: three solutions are under investigation  $\rightarrow$  C code player running NIOS

(under test), running in SMA200 and the usage of a commercial device

## • The proto PCB:

The schematic of HS Line was updated

As soon as we define the final archi  $\rightarrow$  the FPGA family decision  $\rightarrow$

schematic of LS Line

We have redefined

$$\left\{ \begin{array}{l} \mathsf{HS} \to 10 \ \mathsf{PCle} \ \mathsf{lines} \\ \mathsf{LS} \to 1 \ \mathsf{PCle} \to 10 \ * \ [ \ \mathsf{I}^2\mathsf{C} + \ \mathrm{JTag}] + 2 \ * \ \mathsf{SPI} \ ] \end{array} \right.$$

#### • The Schedule:

We are working parallely ... investigating different solutions The prototype will be ready first half of 2011