# Characterization and Calibration of the RD53B CMS Chip

<u>Marijus Ambrozas</u><sup>1</sup>, Stefano Mersi<sup>2</sup>

<sup>1</sup> Faculty of Physics, Vilnius University

<sup>2</sup> CERN

marijus.ambrozas@cern.ch

Fizikos fakultetas

2022-10-12

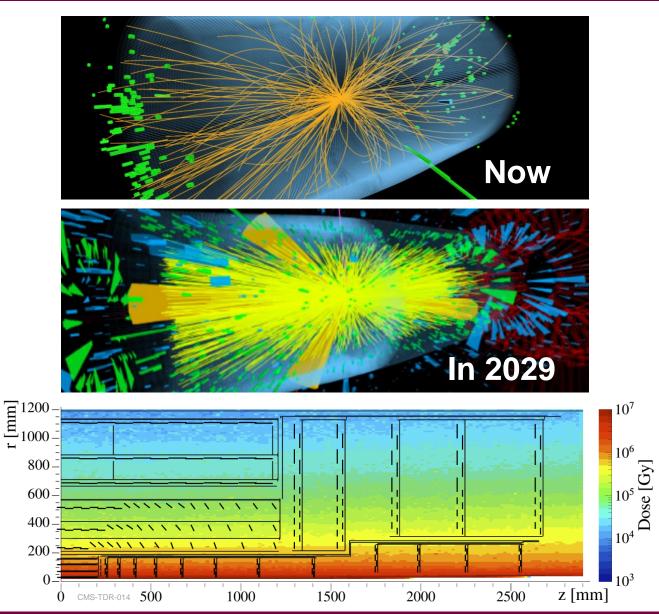

## HL-LHC upgrade schedule

- The High Luminosity LHC upgrade will take place during LS3

- This will result in:

- pp collisions up to 14 TeV

- Peak instantaneous luminosity: from LHC nominal  $1 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>  $\rightarrow$  to  $5 7.5 \times 10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>

- Integrated luminosity: from nominal  $\sim$ 300 fb<sup>-1</sup>  $\rightarrow$ to  $\sim$ 3000-4000 fb<sup>-1</sup>

- Average pile-up: from nominal  $20-30 \rightarrow$  to 140-200

- ~5 times larger track multiplicity in the events than LHC nominal

#### Detector requirements for Hi-Lumi

- 5x more collisions will greatly improve physics discovery potential, but there are also challenges:

- More tracks → higher data rates, harder to separate tracks

- More tracks → bigger radiation doses

- Therefore, the CMS tracker should satisfy the following requirements:

- High granularity to efficiently separate tracks

- High radiation tolerance to sustain efficiency up to 3000 fb<sup>-1</sup>

- Contribution to level-1 trigger to ensure more efficient event selection at high luminosity

- Extended acceptance range to improve the physics potential

- Reduced material budget

- This makes the current CMS tracker not viable for operation after the HL-LHC upgrade

M. Ambrozas

CBC 2022

3

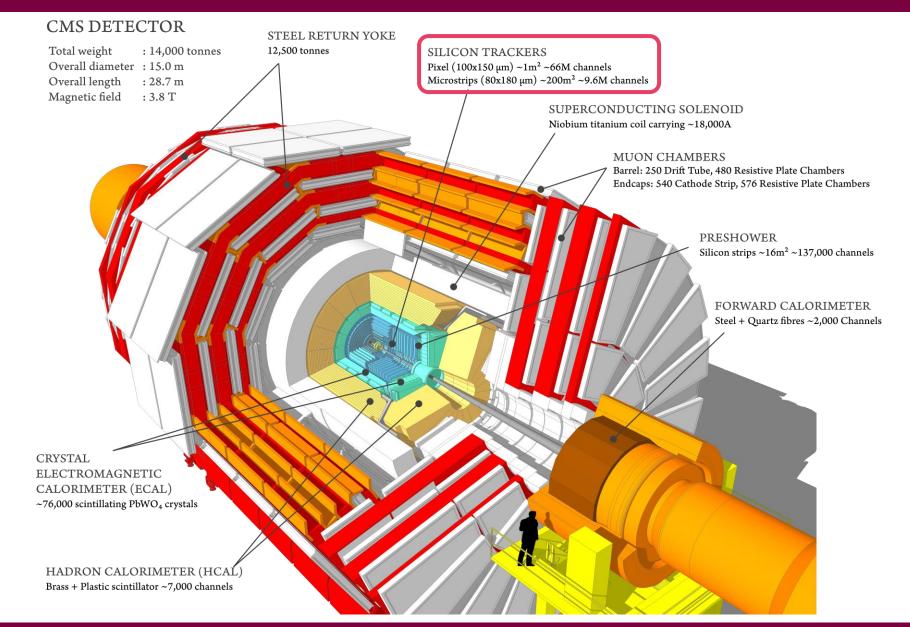

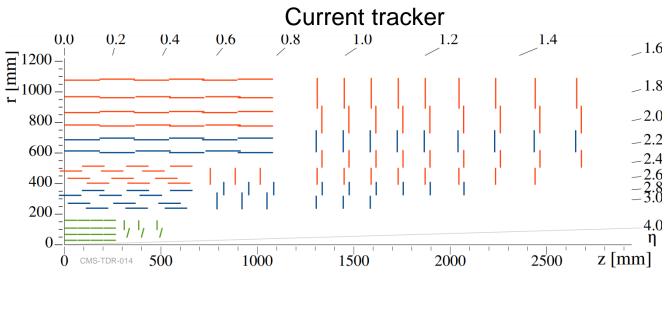

#### (Current) CMS tracker

#### M. Ambrozas

#### Phase-2 CMS tracker upgrade

NIVERSI HE AS SIGN

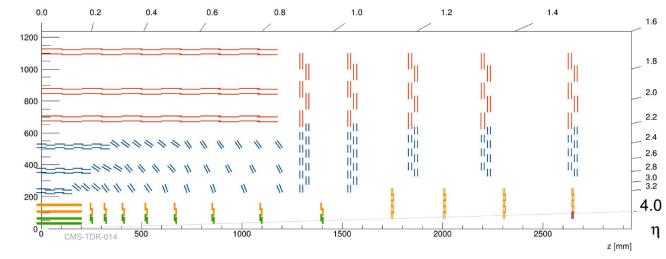

- Both CMS Inner and Outer Tracker systems will be completely replaced

- The Outer Tracker will have 6 barrel layers and 5 endcap disks per side and will feature micro-strip and macro-pixel silicon sensors

- Outer Tracker will also contribute to the L1 trigger

- The inner tracker will have 4 barrel layers and 12 disks (instead of the current 3 disks)

- This will greatly increase the tracking acceptance: up to  $|\eta| < 4.0$  instead of the current  $|\eta| < 3.0$

New tracker

M. Ambrozas

2022-10-12

5

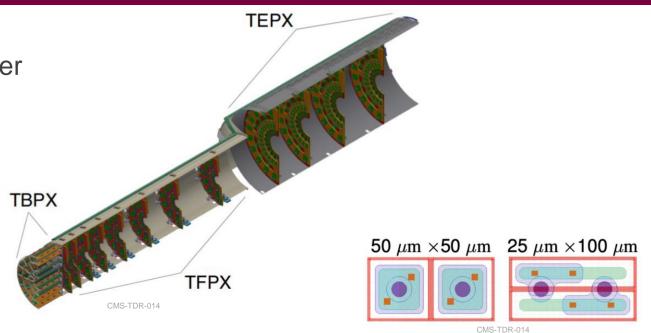

#### The new Inner Tracker

- The new Inner Tracker will feature ~6x smaller silicon pixels than the current one

- 25×100 μm<sup>2</sup> or 50×50 μm<sup>2</sup>

- 150 µm thickness

- Total active surface around 4.9 m<sup>2</sup>

- Total pixel count around 2 billion

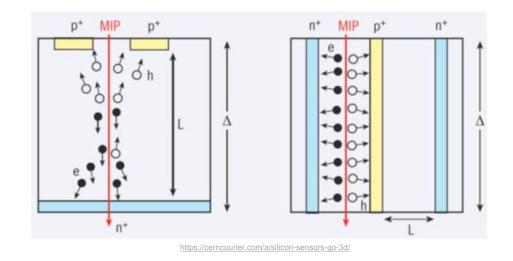

- Two different pixel technologies will be used

- 3D pixel sensors on barrel layer 1

- n-in-p planar sensors everywhere else

- A readout chip based on 64 nm CMOS technology is developed by RD53 collaboration

- RD53 is developing chips for both CMS and ATLAS with different features

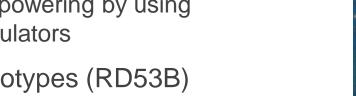

#### The CMS ReadOut Chip

- Features of the chip under development:

- Able to withstand the radiation up to 1 Grad

- Low power consumption of < 1 W/cm<sup>2</sup>

- Compatible with serial powering by using on-chip shunt-LDO regulators

- Second generation prototypes (RD53B) are undergoing tests

- The RD53B version for CMS is called CMS ReadOut Chip – CROC

- 432×336 channels

- Bump-bonded to the sensor

- Wire-bonded to the readout

- 4-bit digital readout for signal strength (ToT)

CBC 2022

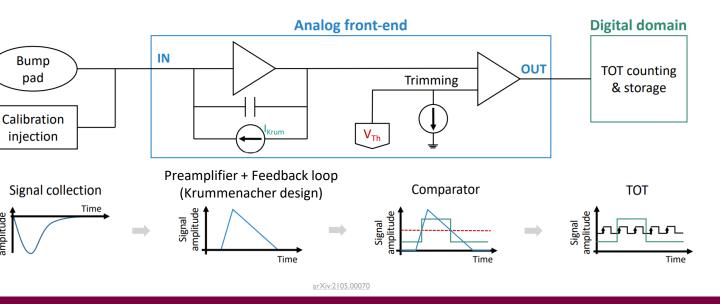

#### Test setups

HUS 15779 SILFINS SIGN

Our test setup for CROC chips consists of:

- Custom-made equipment:

- A CROC chip mounted on a Single Chip Card (SCC)

- Electrical readout FMC board connected to SCC via DP connection

- FC7 board with FPGA and 2 FMC connectors

- Standard equipment:

- DIO5 FMC board (provides external trigger, clock, etc.)

- Low and high voltage supply

- Computer connected to the FC7 via IPbus

- IPbus is a protocol used to communicate between software and firmware via ethernet (<u>https://ipbus.web.cern.ch/</u>)

- Computer runs the Ph2-ACF software which is designed to perform both Inner and Outer Tracker hardware tests

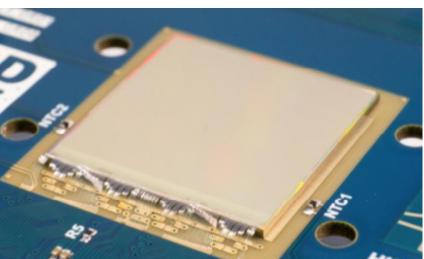

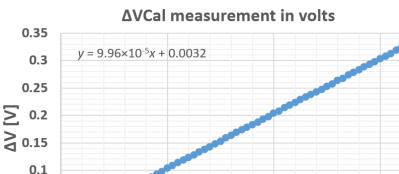

#### Chip threshold unit calibration

- Thresholds are measured by injecting calibration pulses of known amplitude

- The chip uses DAC units (ΔVCal) to determine the calibration pulse and, therefore, the threshold

- We have used the internal voltage multiplexer of the CROC to measure the actual value for the threshold

- The nominal value given by chip designers is 5.5 electrons of signal per ΔVCal unit

- Our measured ΔVCal values on 2 different chips were closer 5.0 electrons of signal

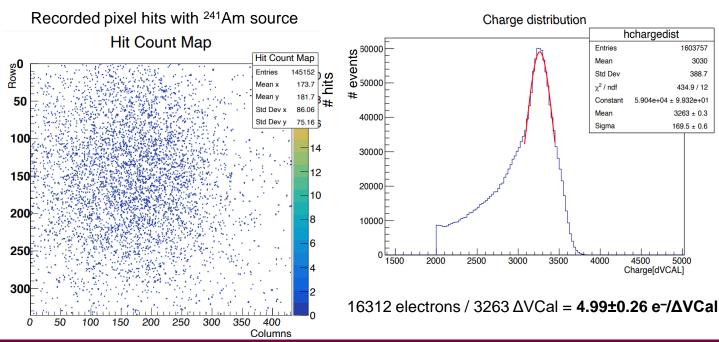

- The threshold unit value of ~5.0 electrons was also confirmed by using <sup>241</sup>Am x-ray source (measurement done by Oceane Poncet)

- X-rays are monochromatic (59.54 keV) and always release the same amount of signal in the sensor (16312 electrons)

1000

#### 1 ΔVCal = 9.96×10<sup>-5</sup> V $C_{cal} = 7.94 \times 10^{-19}$ F 1 ΔVCal → 7.91×10<sup>-19</sup> C 1 ΔVCal → 4.93 e<sup>-</sup> of charge

2000

**∆VCal** [DAQ]

3000

M. Ambrozas

CBC 2022

0.05

9

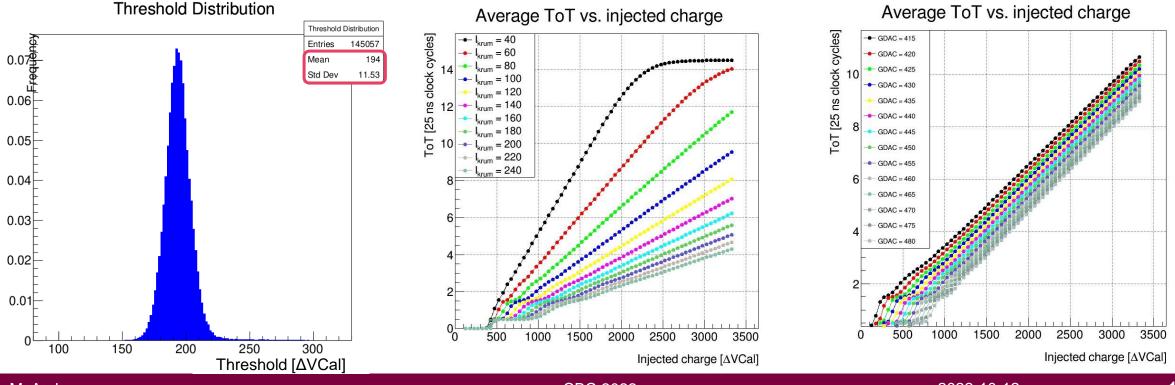

### Chip threshold and ToT gain tuning

- The threshold CROC chip can be successfully tuned at 1000 e<sup>-</sup> of signal (and possibly lower) with a threshold spread of only ~50 e<sup>-</sup> between the pixels

- This is made possible by the trimming DAC, having 4 bits to trim the threshold for each pixel individually

- Preamplifier feedback ("Krummenacher") current can be tuned to obtain different ToT gain curves

- Charge resolution can go below 1000 e<sup>-</sup> per ToT (with very low dynamic range) or as high as 3500 electrons per ToT and more (with very high dynamic range)

- ToT gain slope does not depend on the threshold itself, as expected with the linear analog front-end

CBC 2022

- The HL-LHC upgrade will highly increase the physics potential but also will pose new challenges for the detector makers

- The detectors will need higher resolution, higher data output rates, and higher radiation tolerance

- A completely new tracker is being prepared for CMS

- Pixel detector chips for the Inner Tracker are developed by the RD53 collaboration

- 2<sup>nd</sup> generation chips, called CROC, are undergoing tests and showing good performance

## Thank you!

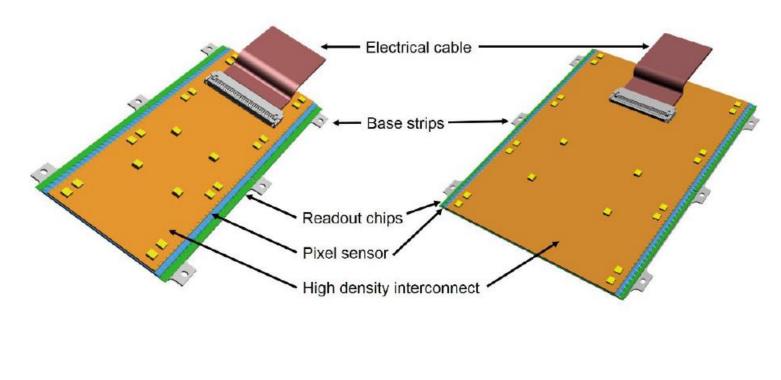

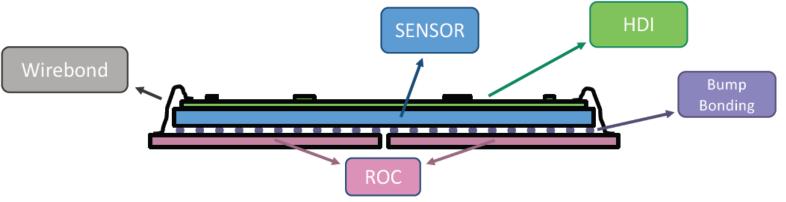

#### **Pixel modules**

- Two types of Pixel Modules

- 1x2 and 2x2 readout chip

- 3892 module plus spares (1156 1x2, 2736 2x2)

- 2 Billon pixels (124 million in current detector)

- Read Out Chip (ROC) only active element on module