### Tracking @ FCC-hh : R&D DICE project status

R&D Future colliders IRFU 20/04/2022

Marlon Barbero CPPM, Aix-Marseille Université, CNRS / IN2P3, France

- 1. Introduction

- 2. WP1 Hybrid Pixels (28 nm)

- 3. WP2 Depleted MAPS :

- a) TJ65

- b) LF150

- c) TJ180

- 4. Conclusions

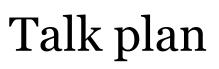

## DICE project

- DICE: A framework to **organize specific R&Ds towards tracking**.

- A project involving CPPM and IPHC, carried by M. Barbero / CPPM (+ involvement <u>IPHC</u> -J. Baudot et al-). Start: beginning 2021.

- General theme :

- Tracking / vertexing with pixel detector in relevant technologies for futures projects with main emphasis on:

- High counting rates/ high hit rates.

- Radiation hardness middle to high.

- 2 Work Packages:

- Hybrid Pixels: Exploring advanced process nodes technologies -e.g. 28 nm-(RS: Barbero / RT: Menouni)

- Monolithic Pixels: Focus on Depleted MAPS technologies Depleted MAPS in two main directions → exploitation of mature R&D and potential of new technologies (RS: Baudot / RT: Pangaud)

R&D Future Colliders, Saclay, 20/04/22: M. Barbero, DICE status

### WP1: Hybrid Pixels for future trackers

- Next generation pixel readout circuits for inner detectors:

- Severe radiation levels

- Unprecedented hit rates

- Complex trigger management technics

- High data transfer several tens Gbit/s -

- Small pixel size integrating complex digital functions (high integration density)

- Higher temporal resolution → 4D tracking

- Low power and small material budget

- 28 nm CMOS process standard:

- Excellent compromise in terms of integration density vs. TID tolerance

- Potential candidate to succeed to 65 nm CMOS node used for hybrid pixel development in framework of HL-LHC

- Higher instantaneous luminosity:

- Higher pile-up

- e.g. HL-LHC: ~ 200 pile-up events / bunch-crossing

- Small pixel size a must / time information would help separating tracks

## WP1: Short term plans

- **Investigation of 28 nm** process node:

- Process advocated by CERN

- "Standard" planar process  $\rightarrow$  TID effect resistant

- Study: <u>Compatibility with analog parts conception</u> (as necessary for pixel circuits):

- Base circuits simulations

- Process qualification in terms of performances for analog design, low power and low noise

- <u>TID-resistance process qualification</u>:

- Compatibility with high TID necessary for futures projects

- TID effects modelling:

- Analog and digital simulation taking TID effects

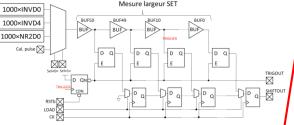

- <u>SEE studies</u>:

- Prototype circuits to study SEU/SET effects

- Very small node capacitance:

- Will it need new architectures for higher tolerance?

R&D Future Colliders, Saclay, 20/04/22: M. Barbero, DICE status

# WP1: Middle/Long term plans

- Conception of a small 64×64 pixel matrix with 25µm×µm pixels :

- "Digital on top" approach

- Mastering digital conception tools a must

- Prototype analog blocks with high constraints (low noise ampli, precision ADC, PLL, high speed serializer...)

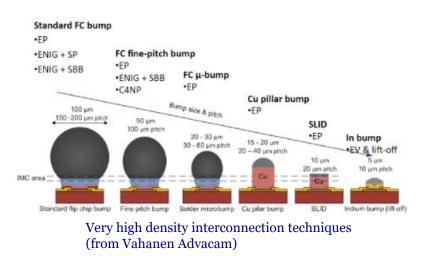

- Prospection work planned on advanced hybridization techniques:

- Advacam proposes hybridization techniques at 10-20µm level

- IZM?

- 3D techniques?

- Ambitious project in terms of manpower and budget:

- Conception cycles in these process types are longer and need more verifications

- Needs to be done in **collaborations**

- Potential interest in other IN2P3 laboratories through DICE

- First discussions in framework of RDR53

## WP1: Perspectives

- In CPPM:

- Small 3-person team of designers → approx. 1FTE equiv

- $\rightarrow$  Collaboration needed

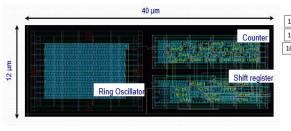

- Q3 2022: Chip prototype submission

- Single transistors (TID studies)

- Ring Oscillators (TID testing of digital libraries)

- SET test architectures

- Analog block (fast amplifier) in small pixel matrix

- Q3/Q4-2022: Test preparation

- Q4-2022/Q1-2023: Functional testing

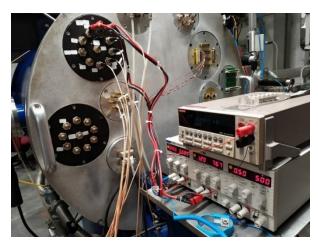

- Q1/2-2023: Irradiation tests (TID / SEE)

TID testing at AMU - Saint Jerome

Heavy ion testing at UCL - Louvain la Neuve

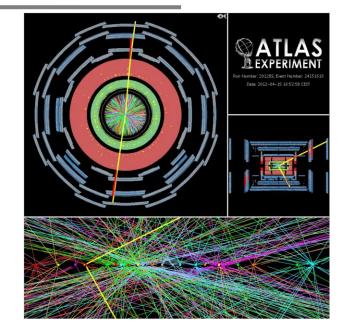

### WP2: Pixels depMAPS

- **<u>New R&D</u>**: Exploring <u>new technology TJ-65 nm</u>

- Short term

- Verification of basic performances

- Check adequacy with DICE objectives

- Middle term

- Prototype(s) dedicated to

- High hit rates (>> 100 MHz/cm<sup>2</sup>)

- Temporal resolution of order 100 ps

- Coping with NIEL >>10<sup>15</sup>  $n_{eq}/cm^2$

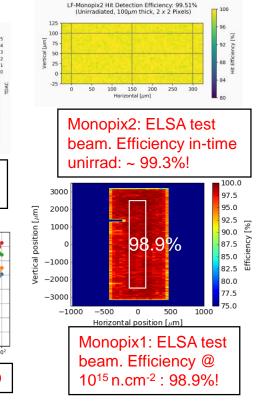

#### Exploiting mature R&D:

- Short term

- Validation of large size prototypes LF-/TJ- Monopix2, work in LF150 and TJ180 technologies

- Middle term

- Adapt TJ-Monopix2 the Belle II context: OBELIX-v1 demonstrator

## WP2: TJ65 / MLR1

• MLR1 submitted in Dec 2020  $\rightarrow$  back summer 2021

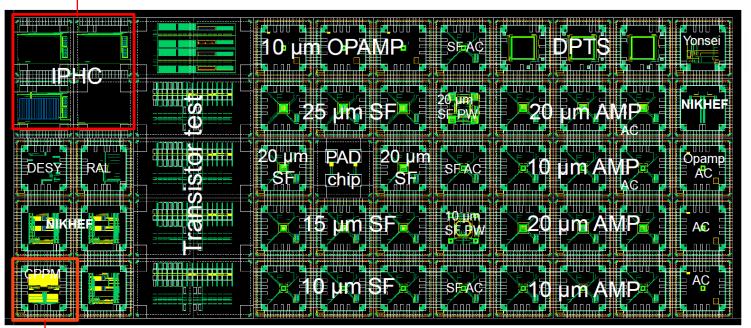

IPHC has contributed with analog Front-Ends CE65, conceived to study charge collection in this technology .

CPPM has contributed with a series of Ring Oscillators, conceived to characterize how the standard cells of the digital library cope with ionizing radiations in this technology .

WP2: TJ65 - IPHC / CE65

#### <u>CE65 targets</u>:

- Understand charge collection properties in TJ65

- SNR, charge sharing, signal speed

- Unirradiated and irradiated sensors

- Common activity with MP R&D CMOS

#### Different CE65 sensors:

- Small matrices with analog output: 64/48×32

- 12 versions each:

- Front-end: DC ampli, DC follower...

- Doping profiles: std & 3 modifications (steered by CERN)

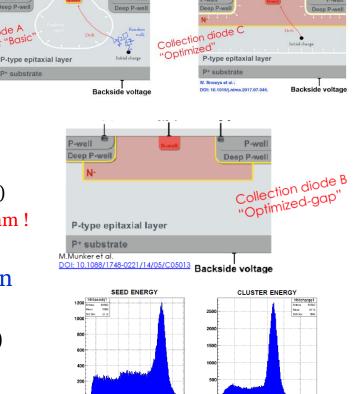

- Replicate implement of idea used successfully in TJ180 nm ! (optimized gap for boosted charge collection)

- Next step: Conception started in 2021 for submission ER1 in Q1/Q2-2022:

- Big sensors to study yield / stitching (ALICE-inspired)

- In this framework:

- MOSS & MOST IC (CERN steered ), H2M, SEU...

- Pixel optimizaation with new CE65++ matrices!

Optimized diode (B4)

Seed signal [ADU]

Charge collection 55Fe

Cluster signal [ADU]

MP DICE & MP CMOS interests!

'standard

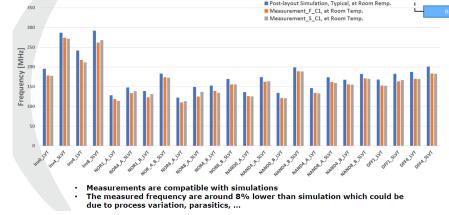

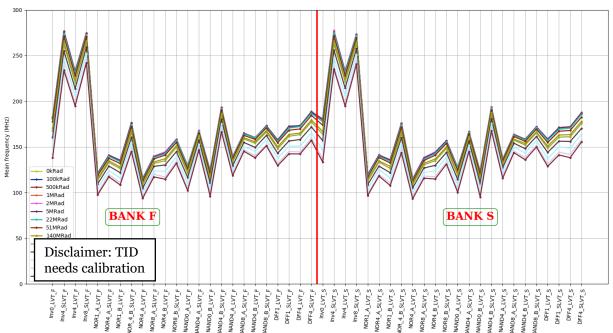

### WP2: TJ65 - CPPM / Ring-Oscillator

- In short: A prototype test IC containing  $24 \times 2$  ring oscillators, with various cell types (Inv, Nand, Nor, DFF), various sizes and two different V<sub>T</sub> (low, super-low).

- Oscillation frequency depends on:

- Temperature

- Polarization

- TID and Dose rates

- But other factors observed (in TSMC 65m) that can be tested here too:

- Dynamic vs. Static cells.

- Asymmetric cell entries

| Low V <sub>T</sub> |             | Super Low V <sub>T</sub> |              |

|--------------------|-------------|--------------------------|--------------|

| Size Min           | Size+       | Size Min                 | Size+        |

| INV0_LVT           | INV4_LVT    | INV4_SLVT                | INV8_SLVT    |

| NOR1_LVT_A         | NOR4_LVT_A  | NOR4_SLVT_A              | NOR8_SLVT_A  |

| NOR1_LVT_B         | NOR4_LVT_B  | NOR4_SLVT_B              | NOR8_SLVT_B  |

| NAND0_LVT_A        | NAND4_LVT_A | NAND4_SLVT_A             | NAND4_SLVT_A |

| NAND0_LVT_B        | NAND4_LVT_B | NAND4_SLVT_B             | NAND4_SLVT_B |

| DFF1_LVT           | DFF4_LVT    | DFF1_SLVT                | DFF4_SLVT    |

- One month irradiation at local X-ray source (CPPM with IM2NP lab in Marseille).

- High dose reached. Exact TID still needs calibration on-going work.

- Annealing started (cold first).

- TBC:

- It seems performance degradation is very tolerable?

- Close to what is seen in TSMC 65nm?

Together w. single transistor results, would give confidence in usage of techno under radiation

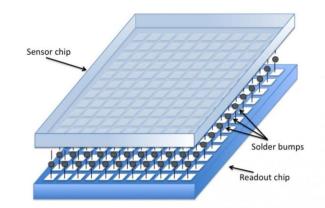

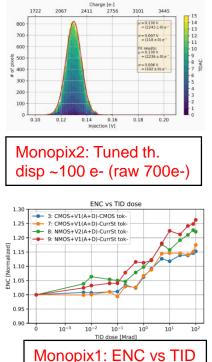

### WP2: Monopix developments

2×1 cm², 340×56 pixels, 50×150 μm²

Analog and digital FE improvements, reduced pixel size, better layout

Submitted in June 2020

→ Back dec. 2020

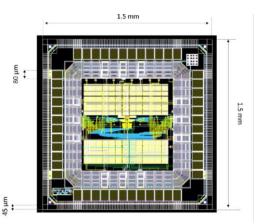

#### 2×2 cm<sup>2</sup>, 512×512 pixels, 33×33 μm<sup>2</sup> New implants for better charge collection after irrad., low threshold Submitted in October 2020 → Back Feb. 2021

**TJ**-Monopix2:

Small pixels, small

capacitance, low

224 Cols

224 Cols

power

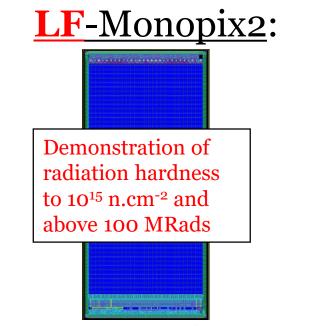

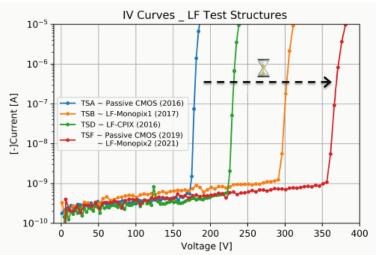

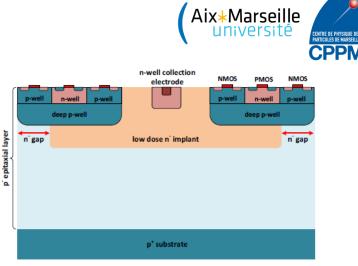

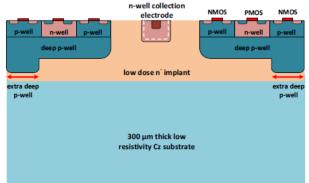

## WP2: LFOUNDRY 150nm techno

100 µm

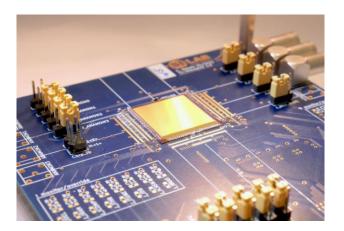

#### Circuit LF-MONOPIX2 (Bonn, CPPM, IRFU)

12 wafers back end 2020

IN2P3

es deux infinis

Test bench and firmware developed by Univ Bonn : MIO3 + GPAC card.

Tests realized by Bonn and CPPM (on-going) show a functional IC with results close to specifications

This second LF-MONOPIX version (LF-MONOPIX2) fixes some crosstalk and threshold adjustment problems.

Tests on-going : sensor characterization, threshold ajustments. New irradiation tests will come in 2022

One pixel cell —Electronics—

**PSUB**

DNW

PW

NISO

P-substrate

Charge coll, diode

PW

NISO

Ë,

R&D Future Colliders, Saclay, 20/04/22: M. Barbero, DICE status

#### Below: Hit efficiency

### WP2: LF150nm

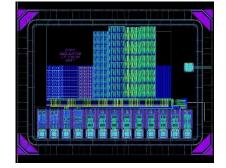

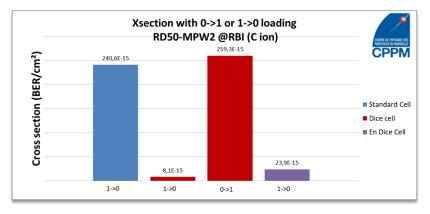

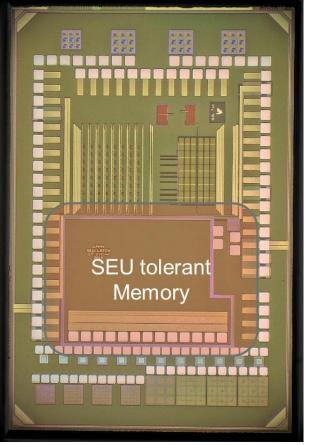

#### Circuit RD50-MPW2 (RD50 collaboration)

#### + SEU hard structures

Tested in Ganil (France) and RBI (Croatie) in 2021! Results show that LF is a SEU-hard technology (comparable or better than comparable prototypes in other technologies)

Cellules: SRAM (col8), split TRL + DICE cell (col7), split TRL + standard cell (col6), TRL + DICE cell (col5), TRL + standard cells (col4), enhanced DICE cell (col3), DICE cell (col2), standard cell Col1)

SEU-hardness vs. architecture type (0 to 1 and 1 to 0 transitions)

## WP2: TOWERJAZZ 180nm CIS technology

IC developed and submitted in 2020. Back in January 2021.

- 2×2cm<sup>2</sup> IC with 33 μm×μm pixels

- TJ-Monopix2 features a high rate digital architecture (column drain / trigger / 40MHz clock)

- This 2<sup>nd</sup> version of the TJ-MONOPIX (TJ-MONOPIX2) should fix some threshold adjustment issues. Test on-going

- Basis for a candidate VTX Belle-II upgrade → OBELIX

Uses a test bench and firmware developed by Univ Bonn : MIO3+GPAC cards or BDAQ.

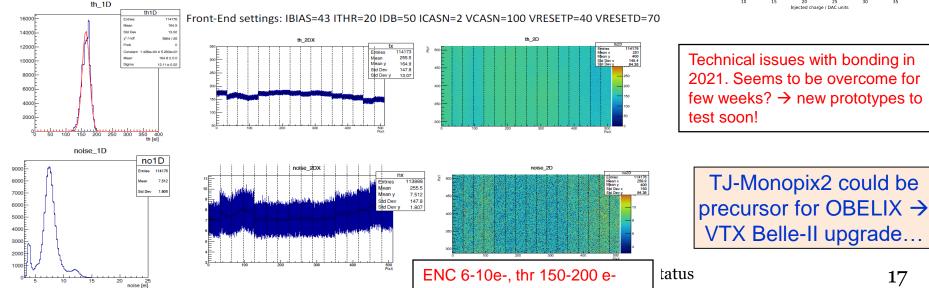

#### 2021 : started TJ-MONOPIX2 characterization

Test bench still in developments (firmware, software). Few bonding issues.

#### 2022:

Development of **OBELIX** prototype from TJ-MONOPIX2. On-going: specification defination / TJ-MONOPIX2 test

A lot still to be done for characterization (in the lab, but also under beam + irradiation)

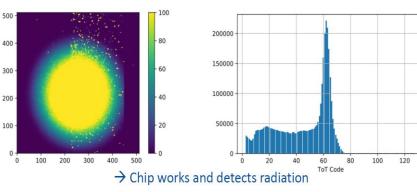

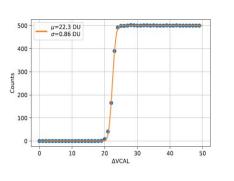

### WP2: TJ-Monopix2 results

#### <sup>55</sup>Fe source detection:

#### S-curves & Threshold tuning:

17

#### TJ-Malta2 results (identical FE!):

#### W5R10 EPI NGAP - Total scan of the matrix

# Conclusion, perspectives 2022

- <u>WP hybride</u>:

- <u>28 nm</u>: prototype finalization (transistors, R-O, SEU-hard cells, pixel matrix) → Q3

2022 submission / functional tests / irradiation test : end 2022 / beginning 23

- Support: IN2P3 / AIDAinnova / RD53? (28nm session in Sept. in RD53 collab week)

#### • <u>WP DepCMOS</u>:

- <u>TJ65</u>:

- Tests CE65 & RO / irradiations / CE65++ conception

- Support: AIDAinnova/ CERN strategic R&D WP1.2 / Participation to ER1 through DICE

- <u>LF 150</u>:

- Finalization LF-Monopix2 tests / small pixels / RD50-MPW3 / tbd small pixel matrice

- AIDAinnova / RD50 framework

- <u>TJ180</u>:

- TJ-Monopix2 functional tests / irradiation tests / OBELIX transition for potential Belle-II VTX Upgrade (v1 in 2022, targets 100 MHz/cm<sup>2</sup>, ~50 MRad, ~3.10<sup>14</sup> n<sub>eq</sub>/cm<sup>2</sup>).

- AIDAinnova / CERN strategic R&D WP1.2 / transition Belle II upgrade

- Synergies on DepCMOS with CMOS MP (A. Besson's talk), interests in these technos from several FR labs (IP2I ... D. Contardo's talk, IRFU... Y. Degerli's talk)

DICE contributes to cutting edge R&D for future tracking and vertexing applications