# Algorithm to control the Dual Channel FMC High Voltage Supply EDA-04456

<u>J. Emery</u>, M. Saccani, W. Vigano' 08.06.2022

#### Algorithm to control the Dual Channel FMC High Voltage Supply EDA-04456

**System description**

**Problem definition**

**Algorithm specification**

**Modeling & simulation**

**HDL** implementation

**Verification strategy**

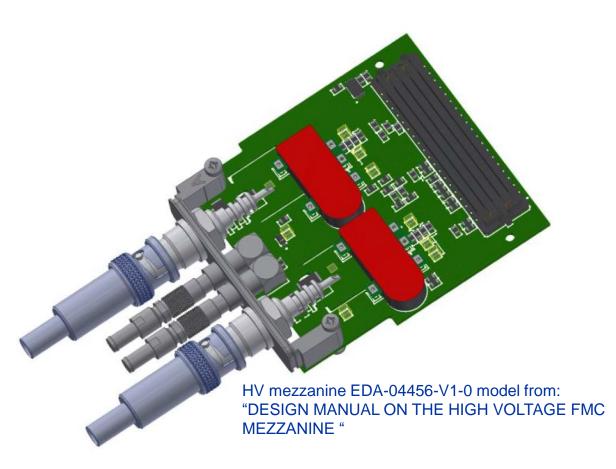

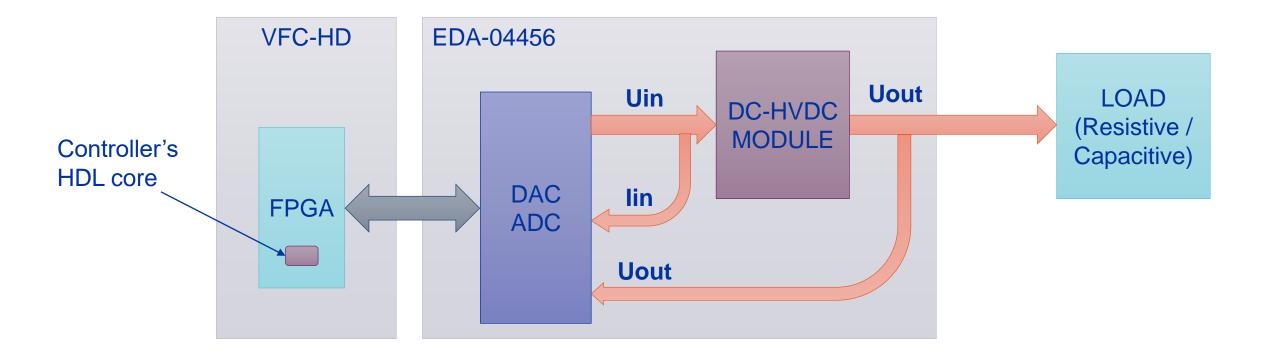

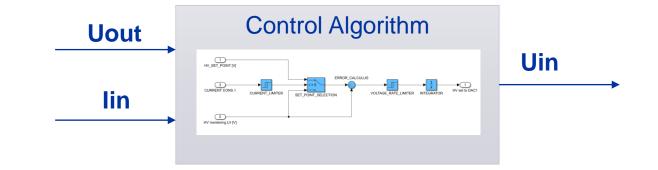

### System architecture and controller's location

### **Electronics interfaces from the controller's viewpoint**

Controller outputs:

- 1) HV ENABLE: ON/OFF switch to the bipolar

- => PWM modulation to set collector voltage of T7

- 2) **DAC1** : Analog voltage setting the emitter voltage Uin

Controller input

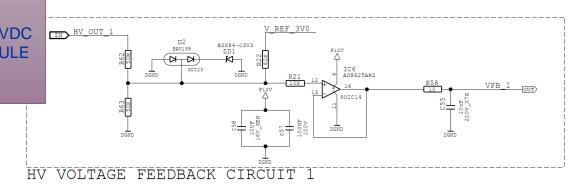

3) CURRENT CONS.1: Shunt voltage to sense current In

4) VFB\_1: Voltage output measure Uout

During HW prototype validation (without feedback), W. Vigano' found that the PWM can be set to a fixed duty cycle => PWM control out of the controller

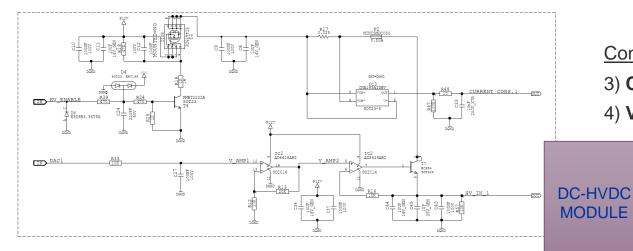

## **Problem definition: DC-HVDC MODULE**

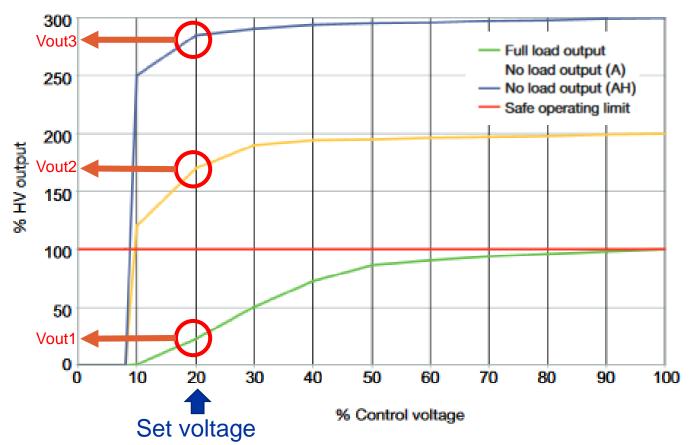

### 1. HV output vs ctrl voltage

It is load dependant. i.e., output current dependant

### => requires a voltage control based on feedback

2. Safe operating limit easily reachable

When operating with low

impedance/capacitive load.

=> requires a voltage limit for a given

module

3. Output current limit => requires a monitoring of the current => if max current is reached, voltage should be limited while delivering the max current (e.g., capacitive load)

| Model Number | Output Voltage | Output Current | Input Voltage    | Input Current,<br>No Load | Input Current,<br>Full Load | Ripple |

|--------------|----------------|----------------|------------------|---------------------------|-----------------------------|--------|

|              |                |                | 1 Watt AG Models |                           |                             |        |

| AG20P-5      | 0 to +2000V    | 0.5mA          | 5V               | <300mA                    | <500mA                      | <0.3%  |

| AG30N-12     | 0 to -3000V    | 0.33mA         | 12V              | <100mA                    | <185mA                      | <0.3%  |

| AG30N-5      | 0 to -3000V    | 0.33mA         | 5V               | <300mA                    | <500mA                      | <0.3%  |

| AG30N-5T     | 0 to -3000V    | 0.33mA         | 5V               | <300mA                    | <500mA                      | <0.3%  |

| AG30P-12     | 0 to +3000V    | 0.33mA         | 12V              | <100mA                    | <185mA                      | <0.3%  |

# **Algorithm spec**

- Voltage feedback (HV module and load independent)

- Voltage limiter

- Current limiter

- Voltage rate selection

- Feedback loop period

- Coefficients editable

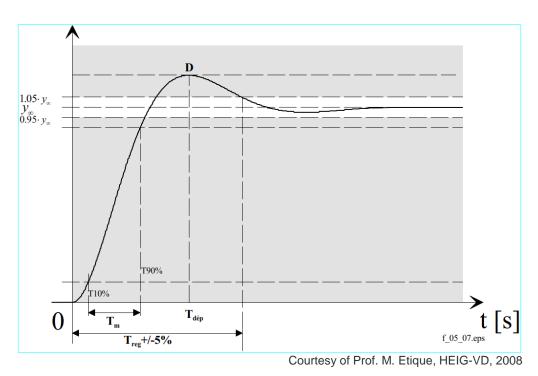

Settling time :

Treg should between 1s and 10s

Ripple :

as low as possible to limit induced current in detectors => correction (the FB) could be turned off when HV ok! Loop period :

< 100ms (determined by HigRes ADC conv. time)

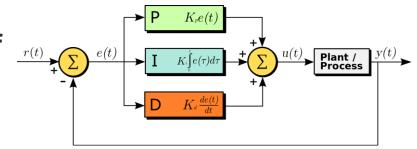

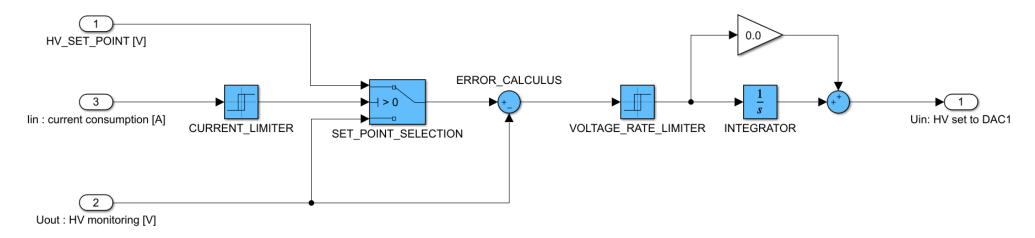

# **Control algorithm basic concept**

- A digital integrator accumulate error to set the HV module voltage input (limited steady state error)

- A proportional term can be set to improve performance if required (! stability vs performance !)

- The error limiter defines the maximum voltage rate

- Current limiter switch the voltage set point to current voltage (minus a defined portion)

PID controller structure (Wikipedia)

# **Algorithm modeling & simulation**

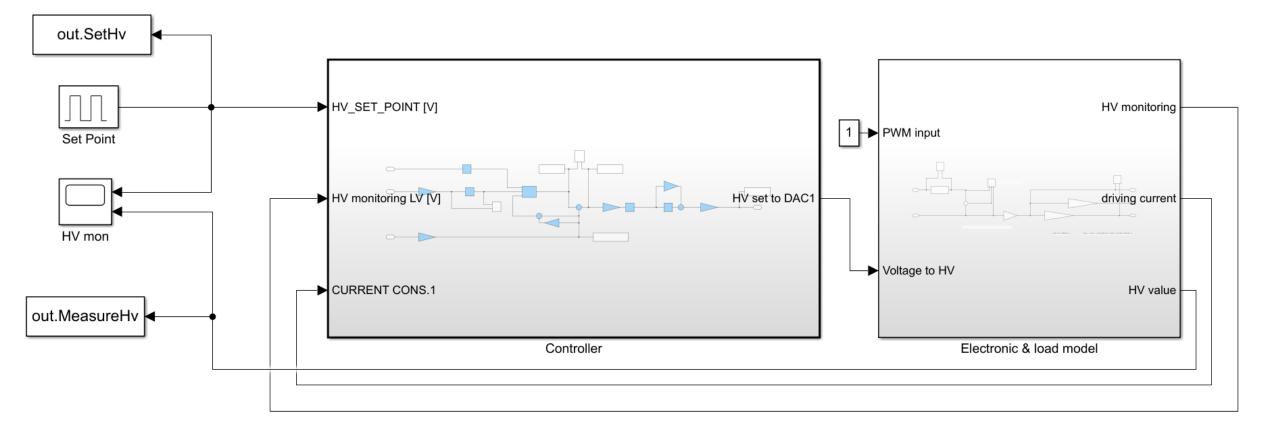

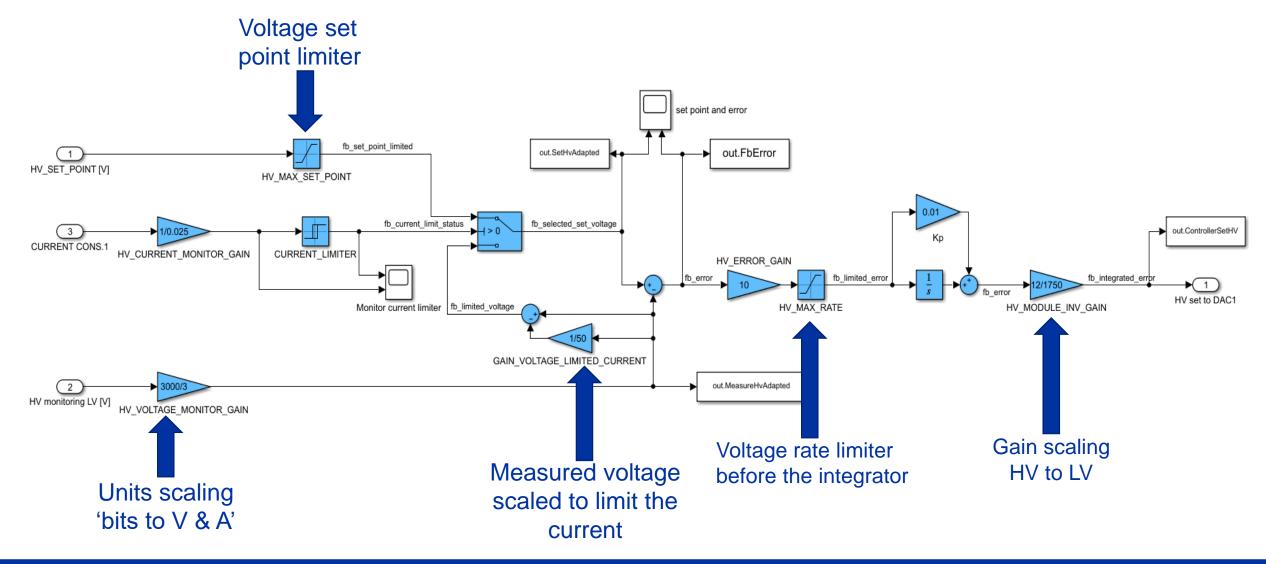

#### MatLab/Simulink modeling of the controller and the load

# **Controller modeling**

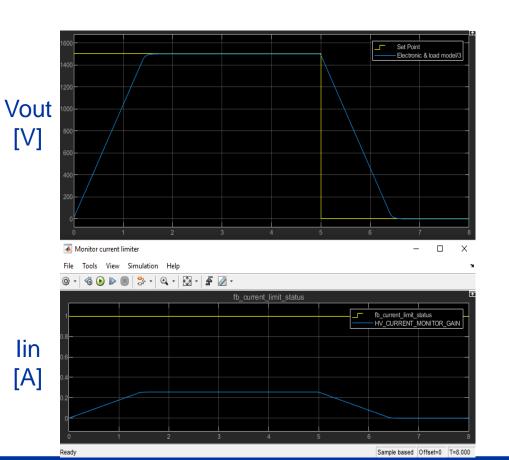

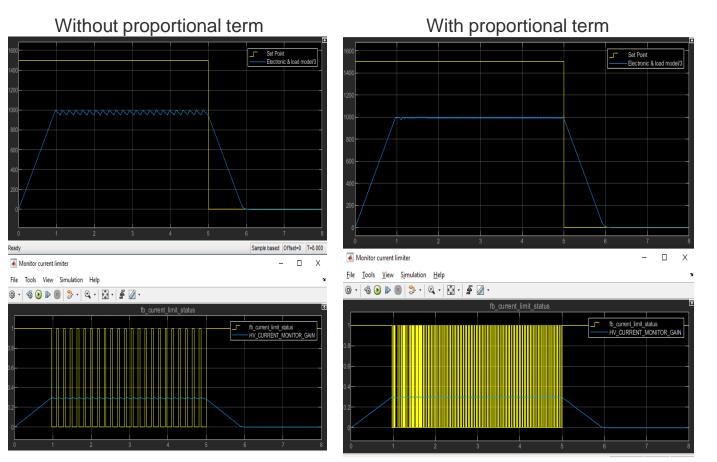

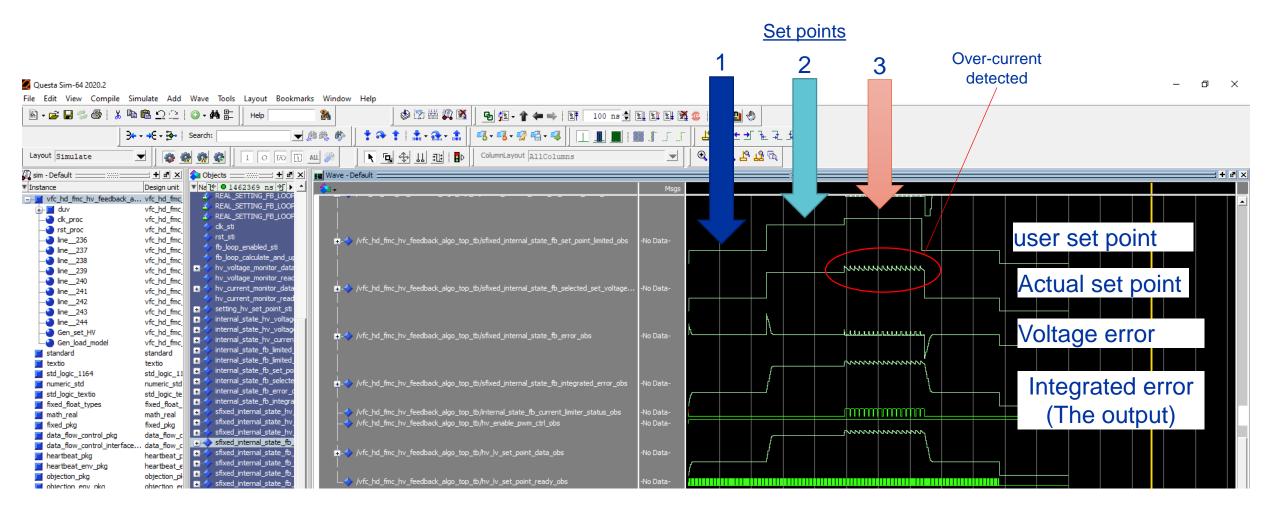

## **Control algorithm: simulation examples**

Set point 1500V HV error rate limit : 1000V/s load below max current

Set point: 1500V HV error rate limit: 500V/s load is above limit current limits: thresholds (with hysteresis) 0.3V and 0.28V

# **VHDL** implementation

Follows the Simulink modeling

Fixed point arithmetic set to 32 bits (16, 16) via IEEE library 'ieee\_proposed' (for Quartus synthesis) but can be increased via generic param. Resolution internal calculation: 15.3 uV / uA

**Components reuse from BWS project**

- input scaling to sfixed

- proportional Integral (PI) core

- comparator for current monitoring

Internal feedback coefficients in registers (settable on the fly)

Feedback loop update externally triggered (user can vary the feedback period if needed)

Internal states outputted to monitor via registers or connected to memory (monitoring of fast signals)

| entity vfc_hd_fmc_hv_feedback_algo_top is                |                                              |

|----------------------------------------------------------|----------------------------------------------|

| generic(                                                 |                                              |

| TOP FIXPT SIZE HIGH                                      | : integer := 16;                             |

| TOP FIXPT SIZE LOW                                       | : integer := -16;                            |

| SETTING HV VOLTAGE MONITOR GAIN                          | : real := 4.0*1750.0; 0.000                  |

| SETTING HV CURRENT MONITOR GAIN                          |                                              |

| FEEDBACK_LOOP_PERIOD_IN_S                                | : real := 5.0; curre.<br>: real := 0.1 scali |

|                                                          |                                              |

| port (                                                   |                                              |

| Clock % Reset                                            |                                              |

| clk i                                                    | : in std logic;                              |

| rstī                                                     | : in std logic;                              |

| Inputs                                                   |                                              |

| fb loop enabled i                                        | : in std logic; when 0, set all o            |

| fb loop calculate and update output i                    | : in std logic; pulse (1 clk i le.           |

|                                                          |                                              |

| settings                                                 |                                              |

| setting hv set point i                                   | : in std logic vector(31 downto 0); s.       |

| setting hv max set point i                               | : in std_logic_vector(31 downto 0); s        |

| setting fb loop hv error gain i                          | : in std logic vector(31 downto 0); s        |

| setting_fb_loop_hv_max_rate_i                            | : in std_logic_vector(31 downto 0); s.       |

| setting_fb_loop_hv_module_inv_gain_i                     | : in std_logic_vector(31 downto 0); s        |

| setting fb loop hv current limit hyst high i             | : in std_logic_vector(31 downto 0); s.       |

| setting_fb_loop_hv_current_limit_hyst_low_i              | : in std_logic_vector(31 downto 0); s.       |

| setting_fb_loop_hv_gain_to_hv_monitor_when_in_cur_limt_i |                                              |

|                                                          |                                              |

| signals from intenal calculations                        |                                              |

| internal_state_hv_voltage_set_point                      | <pre>: out sensor_processed_type;</pre>      |

| internal_state_hv_voltage_in_volts                       | <pre>: out sensor_processed_type;</pre>      |

| internal_state_hv_current_in_amps                        | <pre>: out sensor_processed_type;</pre>      |

| internal_state_fb_limited_voltage                        | <pre>: out sensor_processed_type;</pre>      |

| internal_state_fb_limited_error                          | <pre>: out sensor_processed_type;</pre>      |

| internal_state_fb_set_point_limited                      | <pre>: out sensor_processed_type;</pre>      |

| internal_state_fb_selected_set_voltage                   | <pre>: out sensor_processed_type;</pre>      |

| internal_state_fb_error                                  | <pre>: out sensor_processed_type;</pre>      |

| internal_state_fb_integrated_error                       | <pre>: out sensor_processed_type;</pre>      |

| internal_state_fb_current_limiter_status                 | : out std_logic;                             |

|                                                          |                                              |

| analog world inputs                                      |                                              |

| hv_voltage_monitor_data_i                                | : in std_logic_vector(23 downto 0);          |

| hv_voltage_monitor_ready_i                               | : in std_logic;                              |

| hv_current_monitor_data_i                                | : in std_logic_vector(11 downto 0);          |

| hv_current_monitor_ready_i                               | : in std_logic;                              |

| analog world outputs                                     |                                              |

| hv_enable_pwm_ctrl_o                                     | : out std_logic;                             |

| hv_lv_set_point_data_o                                   | : out std_logic_vector(15 downto 0);         |

| hv_lv_set_point_ready_o                                  | : out std_logic                              |

| - );                                                     |                                              |

| <pre>end vfc_hd_fmc_hv_feedback_algo_top;</pre>          |                                              |

|                                                          |                                              |

|                                                          |                                              |

# **Verification strategy**

Individual cores have simple unit tests (but could be improved for automation)

Overall functional test bench in place to visualize use case

Next steps:

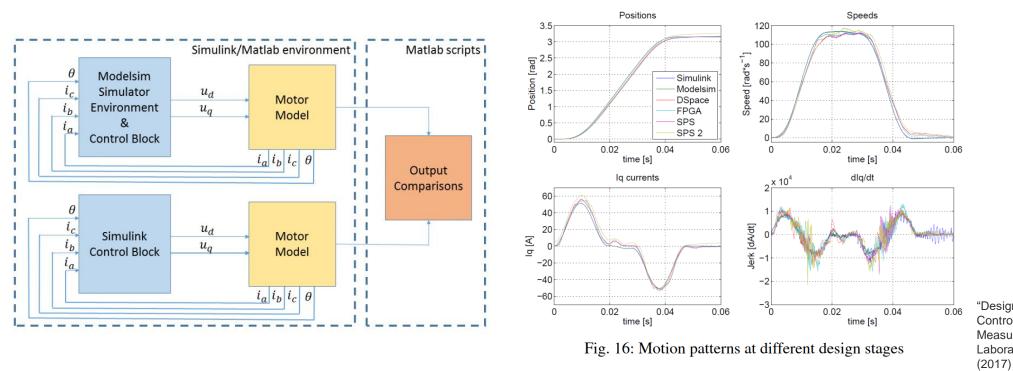

- setup co-simulation within Simulink as for BWS feedbacks (2017)

- integrate code to the Board Support Package (M. Saccani) and test in the lab

- tune feedback coefficients with various load and define a range of 'robust' values

Reference: "Design and Validation Methodology of the Control System for a Particle Beam Size Measurement Instrument at the CERN Laboratory", American Control Conference (2017)

### 'Functional' Simulation: visual example

# Summary

- A digital controller for the HV mezzanine has been designed

- Voltage feedback mode with current limiter

- MatLab/Simulink modeling shows promising behavior

- HDL implementation with fixed point arithmetic

- User will have access to internal coefficients

- Feedback loop period is user actionable, allowing to start-stop

- <u>Next steps:</u>

- Co-simulation MatLab/Simulink

- Offset suppression on the measured inputs

- Integration algorithm into the Board Support Package of M. Saccani

- Test and optimise feedback on the physical prototype

- Tune feedback coefficients with various load and define a range of 'robust' values

- Validate and report performance

- investigate into corrector action at settled voltage (reduce controller induced ripple)

home.cern

### **Functional simulation Generics**

#### entity vfc\_hd\_fmc\_hv\_feedback\_algo\_top\_tb is

| SIMULATION RELATED GENERICS OUTFOLDER                                                                                                                                                                                                                                                                                                                                      | : STRING                                                                                                                                                                                                 | := "";                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FILE PREFIX                                                                                                                                                                                                                                                                                                                                                                | : STRING                                                                                                                                                                                                 | := "";                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                            | . binino                                                                                                                                                                                                 | . ,                                                                                                                                                                                                     |

| NBR CLK PER FB LOOP                                                                                                                                                                                                                                                                                                                                                        | : natural                                                                                                                                                                                                | := 100;                                                                                                                                                                                                 |

| NBR_CLK_PER_LOAD_UPDATE                                                                                                                                                                                                                                                                                                                                                    | : natural                                                                                                                                                                                                |                                                                                                                                                                                                         |

| DCDC MODULE TIME CST IN LOAD UPDATE                                                                                                                                                                                                                                                                                                                                        | : real                                                                                                                                                                                                   | := 0.1; 10 loop period to reach the valu                                                                                                                                                                |

| DCDC MODULE GAIN WITH DRIVE CIRCUIT                                                                                                                                                                                                                                                                                                                                        | : real                                                                                                                                                                                                   | := 7.5/2.5*2000.0/7.5;                                                                                                                                                                                  |

| DCDC MODULE LOAD RESISTIVE                                                                                                                                                                                                                                                                                                                                                 | : real                                                                                                                                                                                                   | $:= 1500.0 \times 22.0; 22mA \text{ at } 1500.0V$                                                                                                                                                       |

| HV_MON_VOLTAGE_LSB_IN_V                                                                                                                                                                                                                                                                                                                                                    | : real                                                                                                                                                                                                   | := 0.000310440;                                                                                                                                                                                         |

| HV MON CURRENT LSB IN I                                                                                                                                                                                                                                                                                                                                                    | : real                                                                                                                                                                                                   | := 0.0000763;                                                                                                                                                                                           |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS                                                                                                                                                                                                                                                                                                       | #uA/1sb                                                                                                                                                                                                  |                                                                                                                                                                                                         |

| current offset=2000 #uA conv_fact=7630                                                                                                                                                                                                                                                                                                                                     | #uA/lsb                                                                                                                                                                                                  |                                                                                                                                                                                                         |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS                                                                                                                                                                                                                                                                                                       | #uA/1sb                                                                                                                                                                                                  | := 16;                                                                                                                                                                                                  |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS<br>TOP_FIXPT_SIZE_HIGH<br>TOP_FIXPT_SIZE_LOW                                                                                                                                                                                                                                                          | #uA/lsb<br>: integer<br>: integer                                                                                                                                                                        | := 16;<br>:= -16;                                                                                                                                                                                       |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS<br>TOP_FIXPT_SIZE_HIGH<br>TOP_FIXPT_SIZE_LOW                                                                                                                                                                                                                                                          | #uA/lsb<br>: integer<br>: integer<br>: real                                                                                                                                                              | := 16;<br>:= -16;<br>:= 0.1;                                                                                                                                                                            |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS<br>TOP_FIXPT_SIZE_HIGH<br>TOP_FIXPT_SIZE_LOW<br>FEEDBACK_LOOP_PERIOD_IN_S                                                                                                                                                                                                                             | #uA/lsb<br>: integer<br>: integer<br>: real                                                                                                                                                              | := 16;<br>:= -16;<br>:= 0.1;                                                                                                                                                                            |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS<br>TOP_FIXPT_SIZE_HIGH<br>TOP_FIXPT_SIZE_LOW<br>FEEDBACK_LOOP_PERIOD_IN_S<br>SETTING_HV_VOLTAGE_MONITOR_GAIN<br>SETTING_HV_CURRENT_MONITOR_GAIN                                                                                                                                                       | #uA/lsb<br>: integer<br>: integer<br>: real<br>: real                                                                                                                                                    | := 16;<br>:= -16;<br>:= 0.1;<br>:= 3.0*1750.0;                                                                                                                                                          |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS<br>TOP_FIXPT_SIZE_HIGH<br>TOP_FIXPT_SIZE_LOW<br>FEEDBACK_LOOP_PERIOD_IN_S<br>SETTING_HV_VOLTAGE_MONITOR_GAIN<br>SETTING_HV_CURRENT_MONITOR_GAIN                                                                                                                                                       | <pre>#uA/lsb : integer : integer : real : real : real : real : real : real</pre>                                                                                                                         | := 16;<br>:= -16;<br>:= 0.1;<br>:= 3.0*1750.0;<br>:= 0.3;                                                                                                                                               |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS<br>TOP_FIXPT_SIZE_HIGH<br>TOP_FIXPT_SIZE_LOW<br>FEEDBACK_LOOP_PERIOD_IN_S<br>SETTING_HV_VOLTAGE_MONITOR_GAIN<br>SETTING_HV_CURRENT_MONITOR_GAIN<br>REAL_SETTING_HV_MAX_SET_POINT<br>REAL_SETTING_FB_LOOP_HV_ERROR_GAIN<br>REAL_SETTING_FB_LOOP_HV_MAX_RATE                                            | <pre>#uA/lsb     : integer     : integer     : real     : real</pre>                       | <pre>:= 16;<br/>:= -16;<br/>:= 0.1;<br/>:= 3.0*1750.0;<br/>:= 0.3;<br/>:= 1750.0;</pre>                                                                                                                 |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS<br>TOP_FIXPT_SIZE_HIGH<br>TOP_FIXPT_SIZE_LOW<br>FEEDBACK_LOOP_PERIOD_IN_S<br>SETTING_HV_VOLTAGE_MONITOR_GAIN<br>SETTING_HV_CURRENT_MONITOR_GAIN<br>REAL_SETTING_HV_MAX_SET_POINT<br>REAL_SETTING_FB_LOOP_HV_ERROR_GAIN<br>REAL_SETTING_FB_LOOP_HV_MAX_RATE                                            | <pre>#uA/lsb     : integer     : integer     : real     : real</pre>                       |                                                                                                                                                                                                         |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS<br>TOP_FIXPT_SIZE_HIGH<br>TOP_FIXPT_SIZE_LOW<br>FEEDBACK_LOOP_PERIOD_IN_S<br>SETTING_HV_VOLTAGE_MONITOR_GAIN<br>SETTING_HV_CURRENT_MONITOR_GAIN<br>REAL_SETTING_HV_MAX_SET_POINT<br>REAL_SETTING_FB_LOOP_HV_ERROR_GAIN                                                                                | <pre>#uA/lsb     : integer     : integer     : real     : real</pre>            | $  \begin{array}{l} := & 16; \\ := & -16; \\ \vdots = & 0.1; \\ := & 3.0 \times 1750.0; \\ := & 0.3; \\ \vdots = & 1750.0; \\ := & 10.0; \\ := & 2000.0; \end{array} $                                  |

| current offset=2000 #uA conv_fact=7630<br>ALGO CORE RELATED GENERICS<br>TOP_FIXPT_SIZE_HIGH<br>TOP_FIXPT_SIZE_LOW<br>FEEDBACK_LOOP_PERIOD_IN_S<br>SETTING_HV_VOLTAGE_MONITOR_GAIN<br>SETTING_HV_CURRENT_MONITOR_GAIN<br>REAL_SETTING_HV_MAX_SET_POINT<br>REAL_SETTING_FB_LOOP_HV_ERROR_GAIN<br>REAL_SETTING_FB_LOOP_HV_MAX_RATE<br>REAL_SETTING_FB_LOOP_HV_MODULE_INV_GAIN | <pre>#uA/lsb     : integer     : integer     : real     : real</pre> | $ \begin{array}{l} := & 16; \\ := & -16; \\ \vdots = & 0.1; \\ := & 3.0 \times 1750.0; \\ := & 0.3; \\ \vdots = & 1750.0; \\ := & 10.0; \\ := & 10.0; \\ := & 2000.0; \\ := & 1.0/3000.0; \end{array} $ |

end vfc\_hd\_fmc\_hv\_feedback\_algo\_top\_tb;