#### 1<sup>st</sup> MONOLITH Workshop – UniGeneve, 5-6<sup>th</sup> September 2022

# Studies and Tests on 4D pixel sensors

#### Adriano Lai, INFN Cagliari

#### **Talk Outline**

- 1. What we mean for 4D-pixel

- 2. Experimental/System Requirements

- **3.** Study of pixel properties and simulation tools

- 4. Key-role of the electronics stage

- 5. Latest test results

- 6. Perspectives

# Definition of 4D pixel and scope of the developments

### 4D trackers/pixels: what do we mean for?

(beyond pile-up mitigation: when timing layers are not enough)

$B_{os}$  meson decaying into a  $\mu^{\scriptscriptstyle +}$  and  $\mu^{\scriptscriptstyle -}$  pair

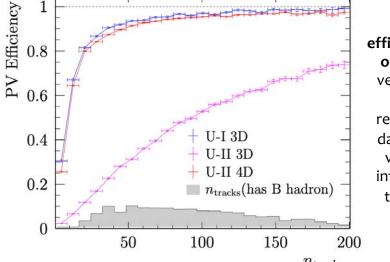

Plots from:

Considerations for the VELO detector at the LHCb Upgrade II – CERN-LHCb-2022-001

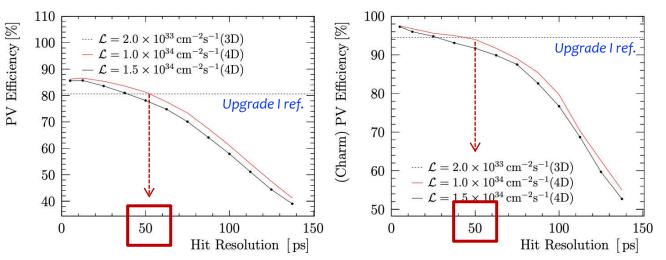

Reconstruction efficiency vs the number of tracks per primary vertex, comparing the Upgrade I 3D reconstruction in both data conditions, and a variant using timing information to resolve the primary vertices

#### 4D pixel:

A solid state pixel sensor (pitch  $\approx$  50 µm) bearing time information

Track merging: bad Primary (and Secondary) Vertex reconstruction

Incorrect PV assigned to tracks: poorly measured lifetime (dominant sistematic effect for time-dependent analysis)

> PV reconstruction efficiency as as function of the single hit resolution, for all vertices (left) and for vertices where at least one of the decay products is a charm hadron (right).

50 ps per hit (corresponding to 20 ps per track) are sufficient to recover the Upgrade-I efficiency

# **Technical Requirements of 4D-Tracking**

In the next generation of Upgrades (LHCb run5, NA62 4x, CMS-PPS & ATLAS-AFP run4 ... FCC - hh...)

- 1. Space Resolution  $\sigma_s \approx 10 \,\mu\text{m}$  ( $\rightarrow$  pixel pitch  $\approx 40-60 \,\mu\text{m}$ )

- 2. Time Resolution  $\sigma_t \leq 50$  ps on the full chain ( $\sigma_t = \sigma_{sensor} \oplus \sigma_{FE} \oplus \sigma_{TDC}$ )

- 3. Radiation hardness to high fluences (for sensors) and high doses (for electronics). Fluences  $\Phi = 10^{16} \div 10^{17}$  1 MeV n<sub>eq</sub>/cm<sup>2</sup> and Doses > 1 ÷ 2 Grad

- 4. A detection efficiency of  $\varepsilon > 99\%$  per layer is tipically required (high fill factor)

- 5. The material budget must be kept below 1  $\div$  0.5 % radiation length per layer

Very challenging front-end electronics must be developed: high resolution @ 10s  $\mu$ W/pixel, huge data bandwidth  $\approx$  100 Gbps/cm<sup>2</sup>. Today a complete solution for that is FAR from being available. Developments ongoing

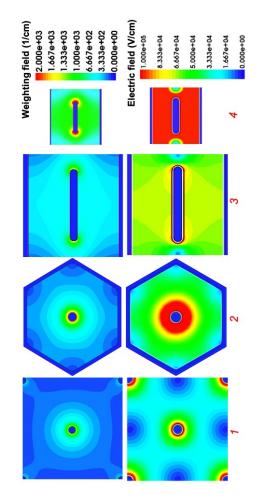

#### Contact opening Sump contacts A different approach: 3D silicon sensors passivation oxide Gain? no thanks! go... Geometric ! 1<sup>++</sup> (diode) ++ (bias) p<sup>-</sup> Si High ++ (bias) Resistivity substrate Concept (S. Parker et al., 1997): Sensitive volume and electrode Perpendicular electrodes make shapes can be designed and modeled Bias contact metal (can be deposited after thinning of support wafer) p<sup>+</sup> Si Low Inter-electrode distance d Resistivity for maximum performance independent of sensor thickness z **Impinging particle** substrate support wafer (to be thinned) **Deep Reactive Ion Etching** (MEMS technology) High and uniform E field = 25 - 50 µm track Read-out electrode Weighting field (1/cm) 2.000e+03 1.667e+03 1.333e+03 0 Biasing 1.000e+03electrode(s) 6.667e+02 3.333e+02 $\boldsymbol{i} = q\boldsymbol{E}_w \cdot \boldsymbol{v}$ 0.000e+00 Electric field (V/cm) 1.000e+05 8.333e+04 6.667e+04 5.000e+04 3.333e+04 1.667e+04 000+00 trenches columns

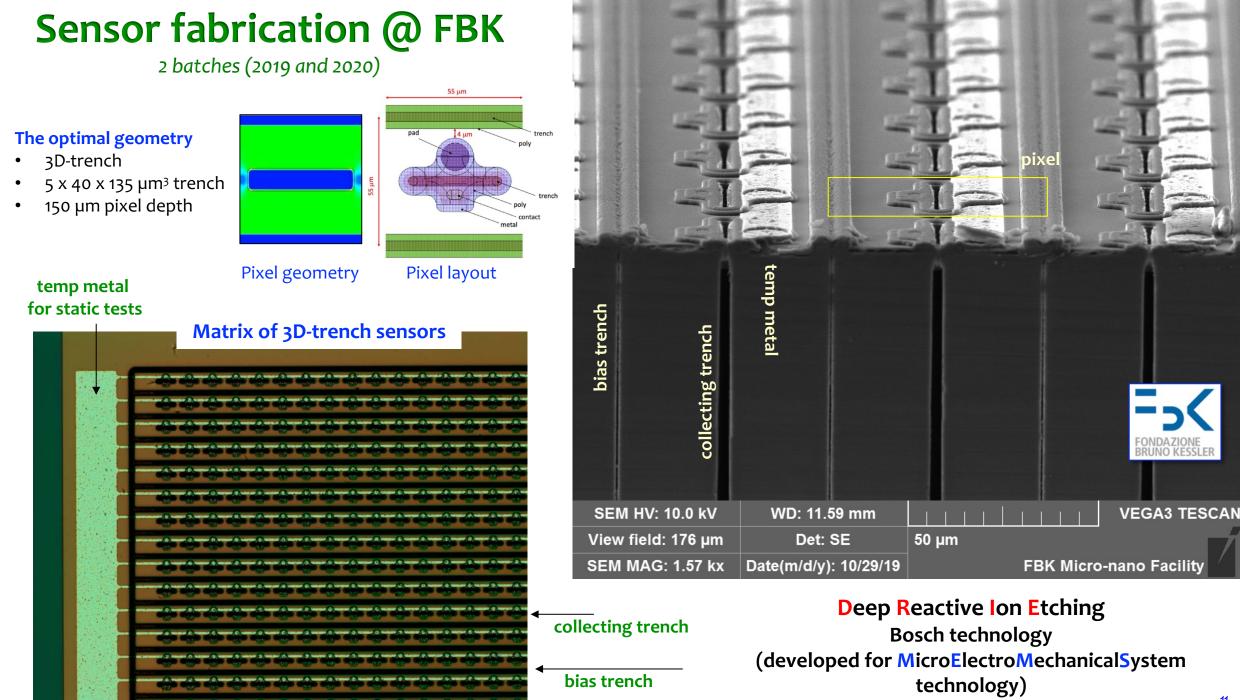

TCAD Sentaurus output: 2D model simulation of three different electrode geometries at bias voltage  $V_{\text{bias}} = -100 \text{ V}$

Column or trench aspect ratio  $\approx$  30:1

(3D) Sensor modeling and its impact in sensor design and understanding

# The playgound and the game

CCT and current signals

https://github.com/MultithreadCorner/Tcode

**GPL3** license

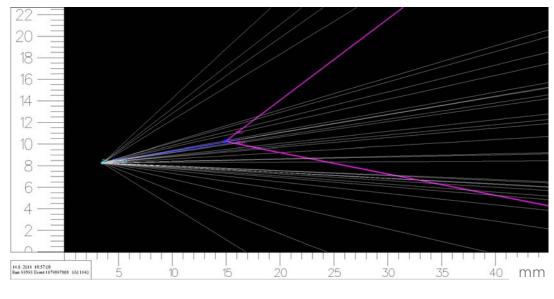

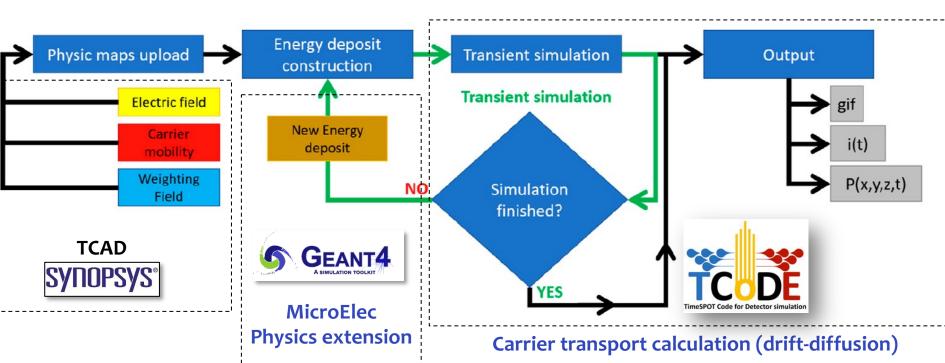

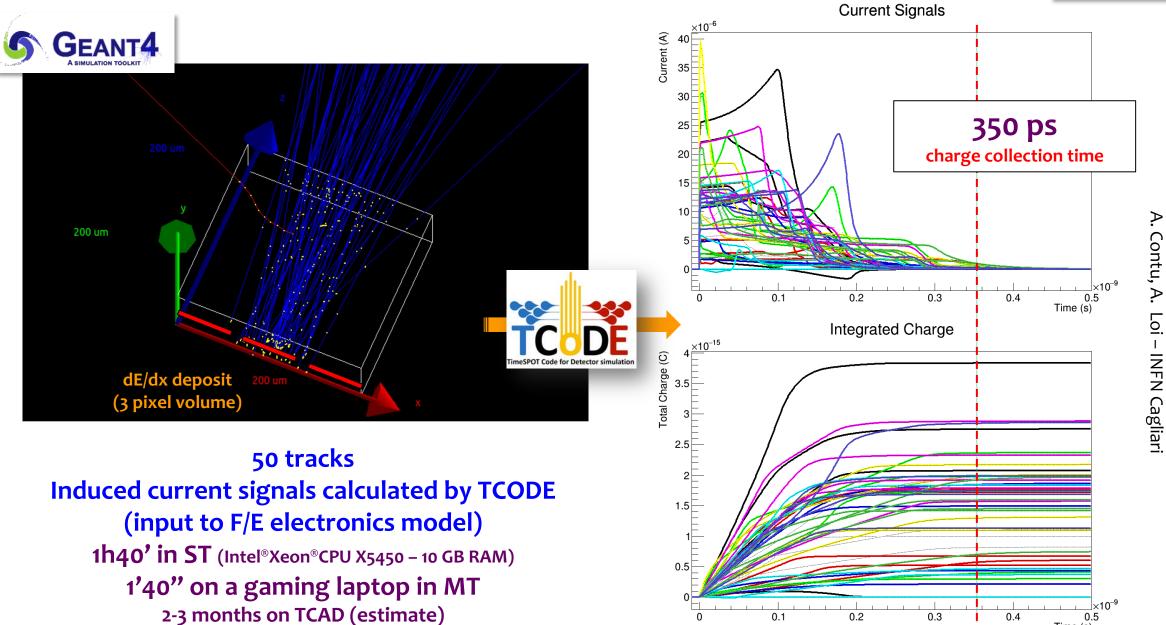

The carrier motion calculated using a 4<sup>th</sup>-order Runge–Kutta algorithm and the thermal diffusion equation. The contribution of each carrier to the current induced on the readout electrode is determined with the Ramo theorem for each time interval.

Multi-threaded approach (Hydra libraries): each carrier is followed independently in a separate computing thread, either in CPU or GPU.

The TCoDe simulation flow

Brundu

Ć,

ച

Modeling

9

Solid

S

đ

īte

Detectors

Using

Advanced Multi-

Phys.

10:804752

hreading:

(2022) TCoDe

Silicon Sensors

C O D O

(2021) 16:P0201<sup>,</sup>

Design

MIP deposit shape

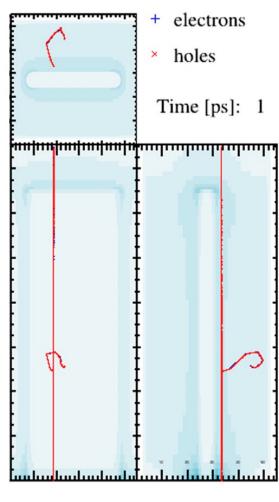

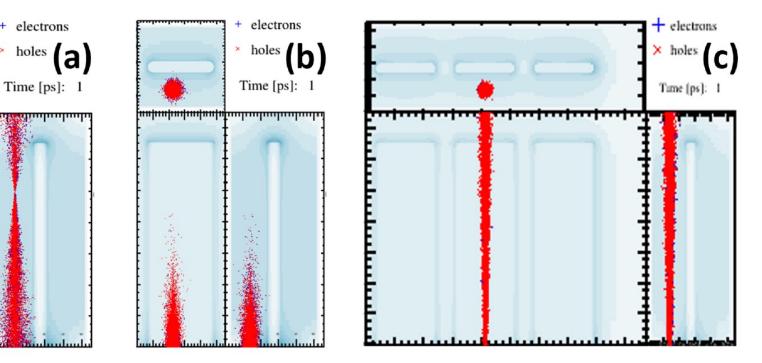

Examples of calculated energy deposit shapes **from laser sources** inside a TimeSPOT 3D-trench structure:

- (a) Deposit with focus inside the active bulk.

- (b) Deposit shape due to high absorption (655 nm wavelength)

- (c) Deposit of IR laser source (1030 nm wavelength), emulating a MIP.

# **TCoDe operation and statistics**

Time (s)

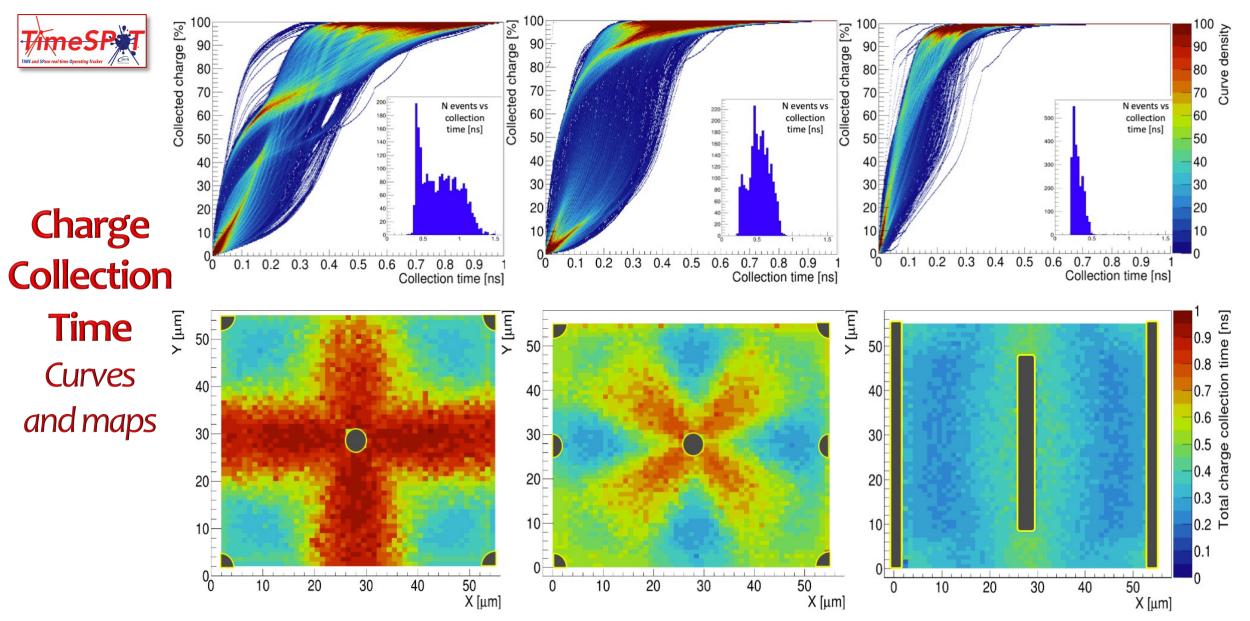

Time performance comparison among three different 3D geometries at  $V_{bias} = -100V$  (from left to right: five columns, nine columns and trench geometry). (Top) percentage of total charge collected on the electrodes versus time. (Top inserts) distribution of charge collection time for the three geometries. (Bottom) time for complete charge collection versus impact point for the same geometries. Each simulation is based on about 3 000 MIP tracks.

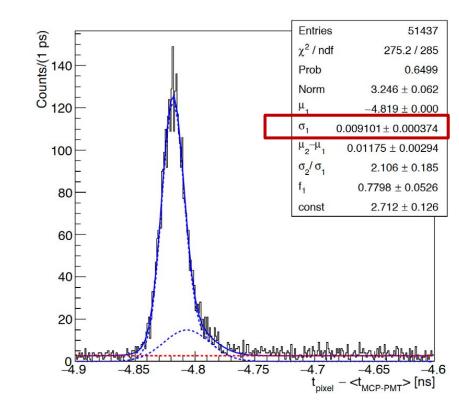

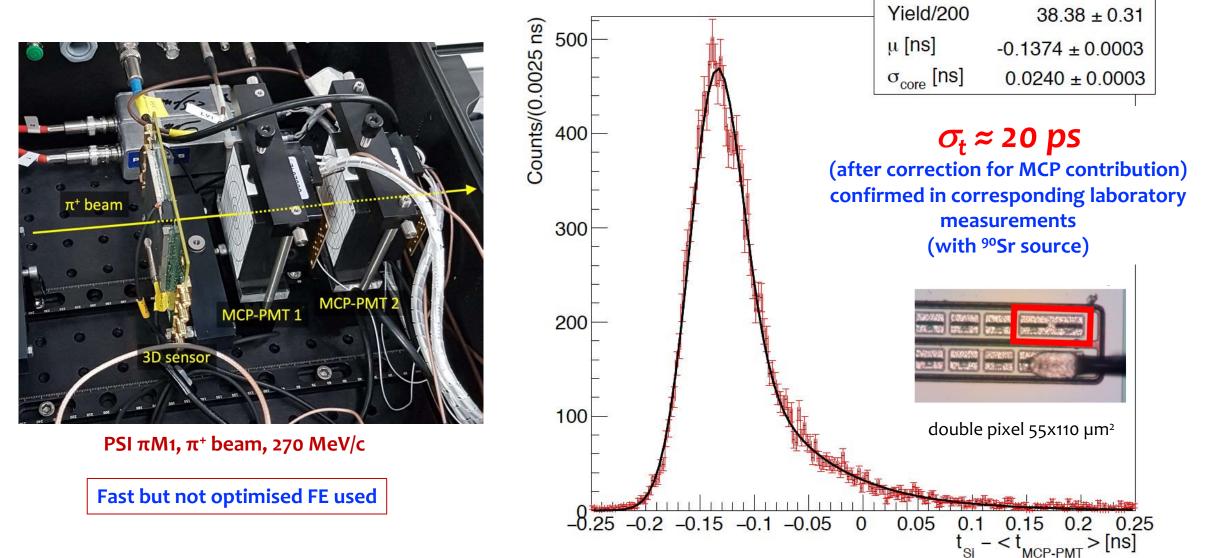

### First results on 3D-trench pixels at PSI (2019)

**Time resolution of 3D-trench silicon pixels with MIPs (test-beam & lab) at room temperature** (ref. Intrinsic time resolution of 3D-trench silicon pixels for charged particle detection, 2020 JINST 15 P09029)

# **TCAD** outputs

### For detailed sensor charaterization

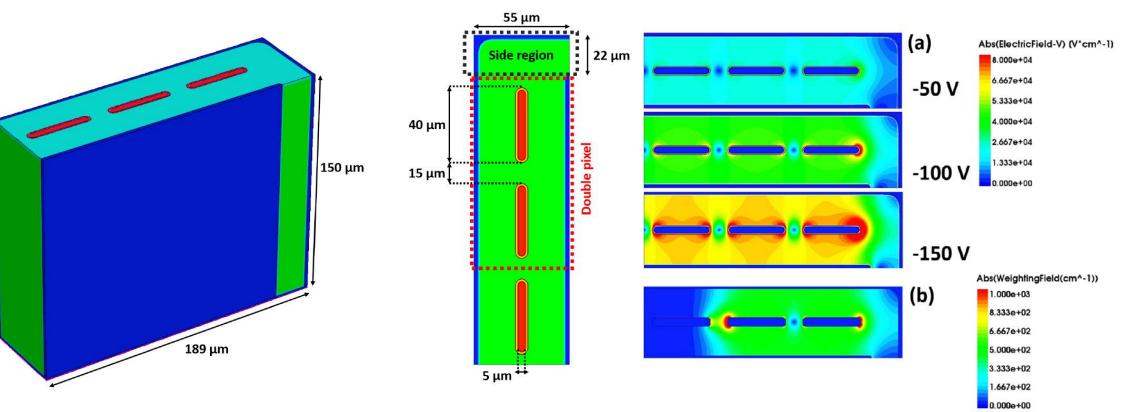

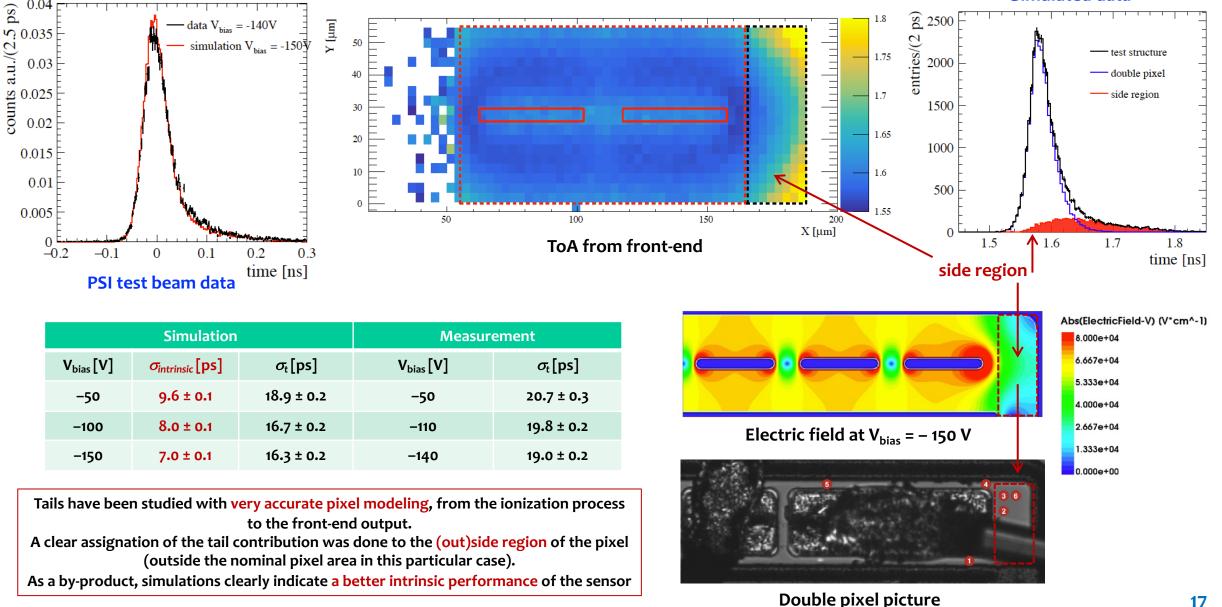

D. Brundu et al., Accurate modelling of 3D-trench silicon sensor with enhanced timing performance and comparison with test beam measurements. JINST, 16, P09028, 2021

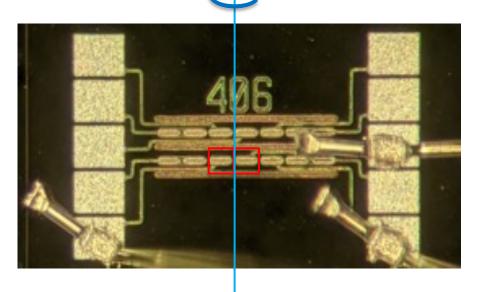

Layout of the simulated TimeSPOT test structure, including sections and sizes, designed using Sentaurus **TCAD**. The double pixel is indicated by the dotted-red line.

(a) Electric field amplitude at different bias voltages for the double-pixel test structure and(b) weighting field

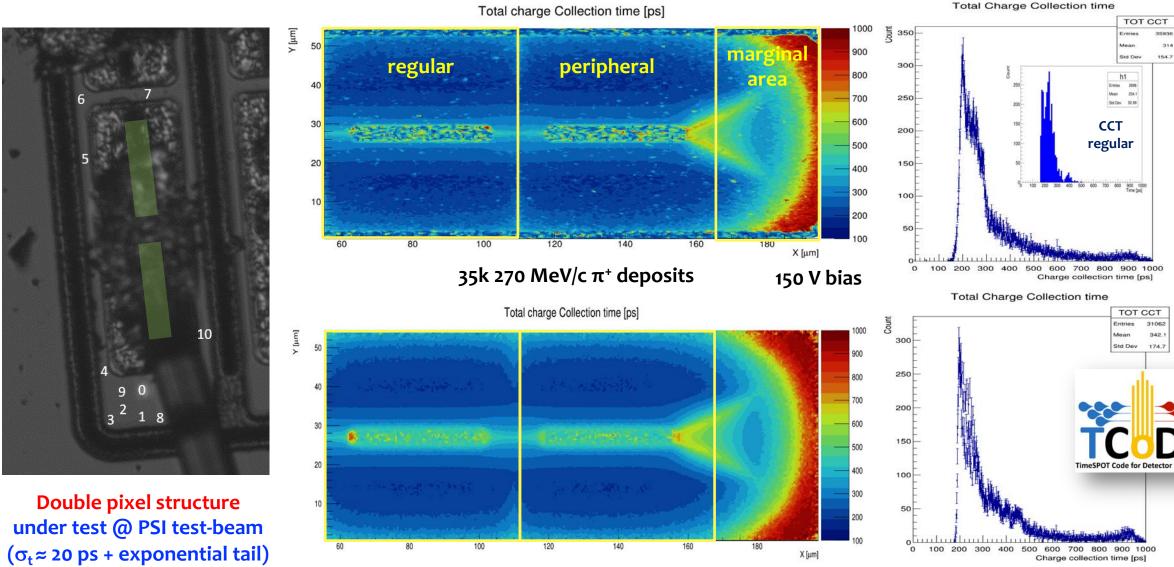

### A <u>virtual experiment</u> on the DUT to identify tail contributions

Charge Collection Time distributions from TCoDe

0

**INFN** Cagliari

14

31k IR laser (MIP-like) deposits

– 6<sup>th</sup> June 2022

19<sup>th</sup> Software School

- Alghero

Lai

Ż

1

**Timing and 4D pixel sensors**

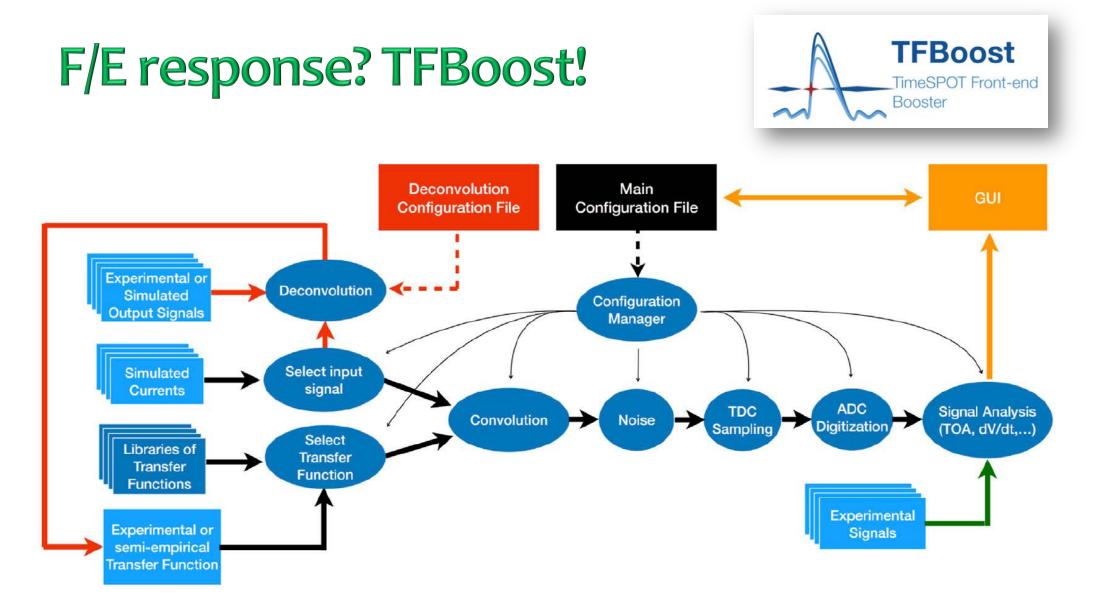

**TFBoost simulations flow.** The black path is the main simulation in which the convolution and the signal analysis are performed. The green path is followed if TFBoost is used as a pure signal analyzer, while the red path is followed to perform the deconvolution between an input current and an output signal.

# Accurate re-analysis

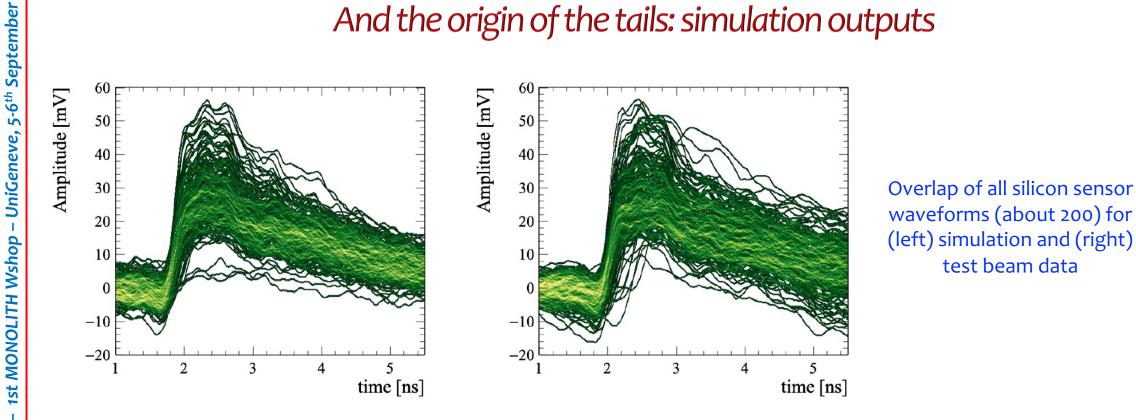

And the origin of the tails: simulation outputs

| Maximum amplitude, average signal-to-noise ratio,<br>noise, rise time (20–80%) and slew rate (dV/dt) |

|------------------------------------------------------------------------------------------------------|

| of the 3D-trench silicon sensor response at different                                                |

| values of the bias for simulation and data.<br>The statistical uncertainties are below 1%.           |

|            | V <sub>bias</sub> | $Amp(P_{max})$ | $\langle S/N \rangle$ | $\langle N \rangle$ | rise time | dV/dt   |

|------------|-------------------|----------------|-----------------------|---------------------|-----------|---------|

|            | [V]               | [mV]           |                       | [mV]                | [ps]      | [mV/ns] |

| Simulation | -50               | 25.0           | 14.6                  | 2.11                | 247       | 103     |

|            | -100              | 24.5           | 14.3                  | 2.17                | 224       | 113     |

|            | -150              | 24.4           | 14.2                  | 2.19                | 217       | 116     |

| Data       | -50               | 24.1           | 14.3                  | 2.19                | 258       | 111     |

|            | -110              | 24.4           | 13.9                  | 2.30                | 221       | 123     |

|            | -140              | 24.7           | 14.2                  | 2.29                | 217       | 126     |

2022

Lai Ż

**TimeSPOT results**

16

### Final response about the slow tails

The very special case of the double pixel

D. Brundu et al., Accurate modelling of 3D-trench silicon sensor with enhanced timing performance and comparison with test beam measurements. JINST, 16, P09028, 2021

**Simulated data**

Measurements at test beams and 3D-trench sensor characterization

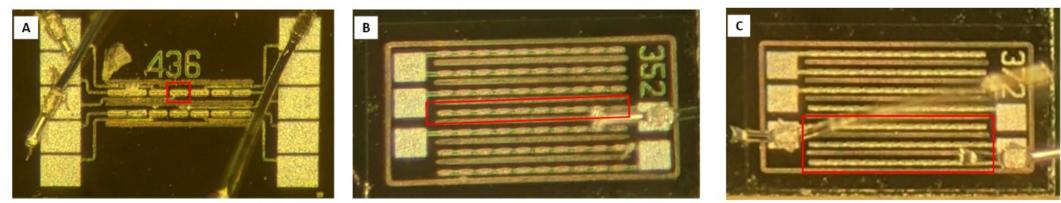

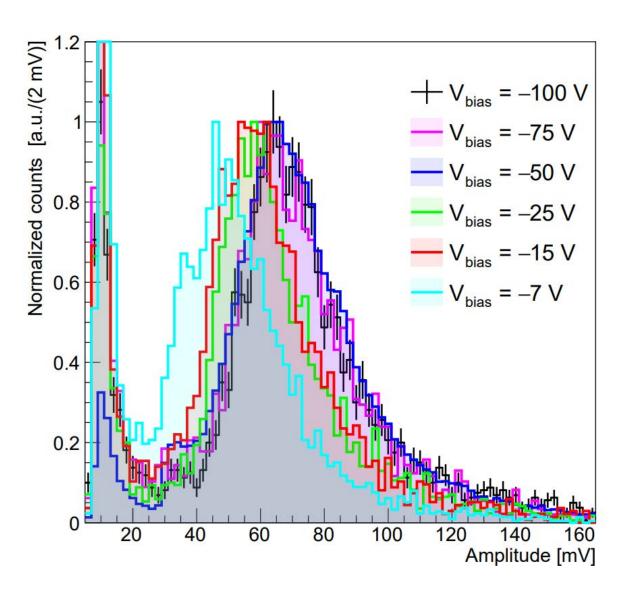

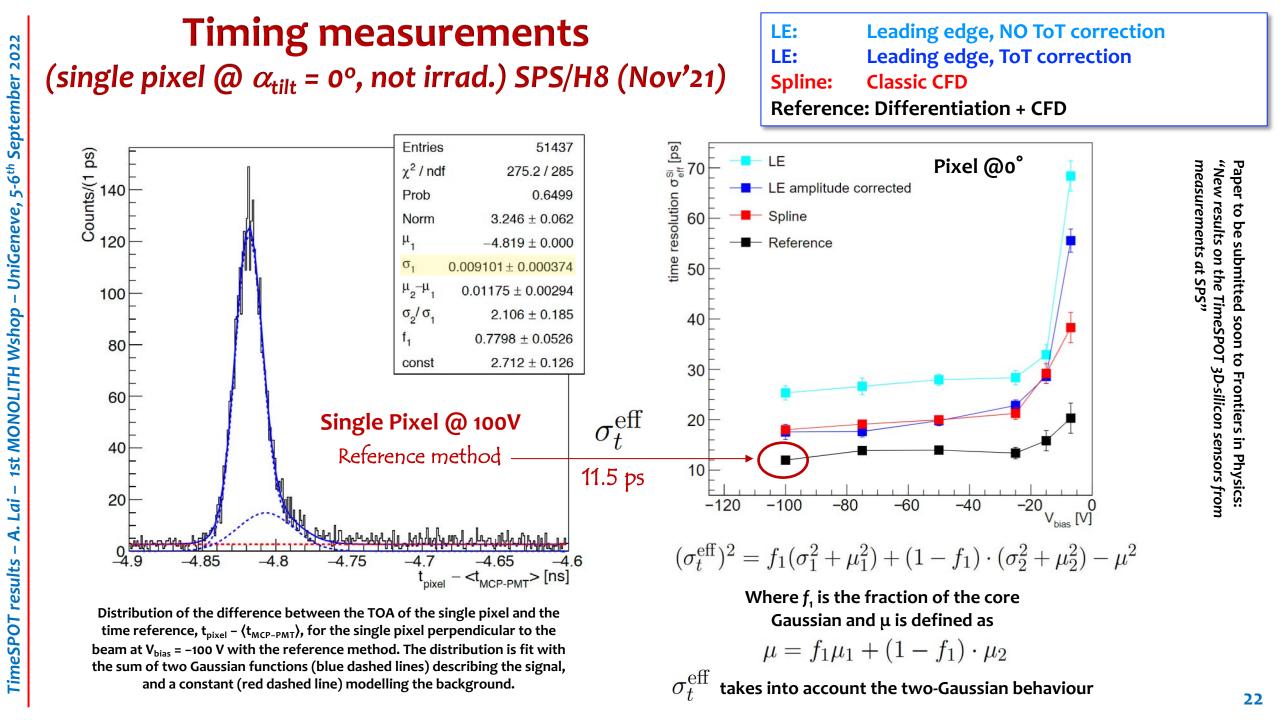

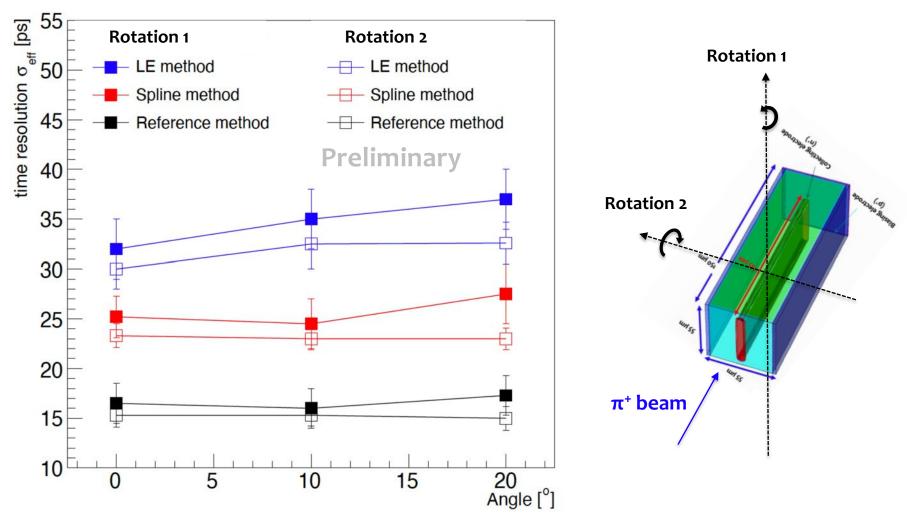

## Latest results

#### Test-beams Nov21 & May22 @SPS/H8

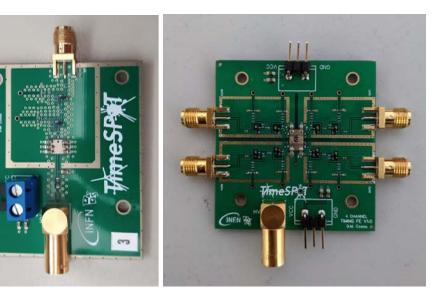

#### New faster dedicated front-end electronics

Si-Ge input stages t<sub>r</sub> ≈ 100 ps. Measured jitter <7 ps @ 2 fC ≈ 70 mW/channel

- 1. Not-irradiated:

- Landau distributions vs V<sub>bias</sub>

- Time resolution

- Geometrical efficiency vs tilt angle

- Time resolution vs tilt angle

- 2. Same with samples irradiated @  $\Phi$  = 2.5 10<sup>16</sup> 1-MeV-n/cm<sup>2</sup>

- 3. First studies on charge sharing

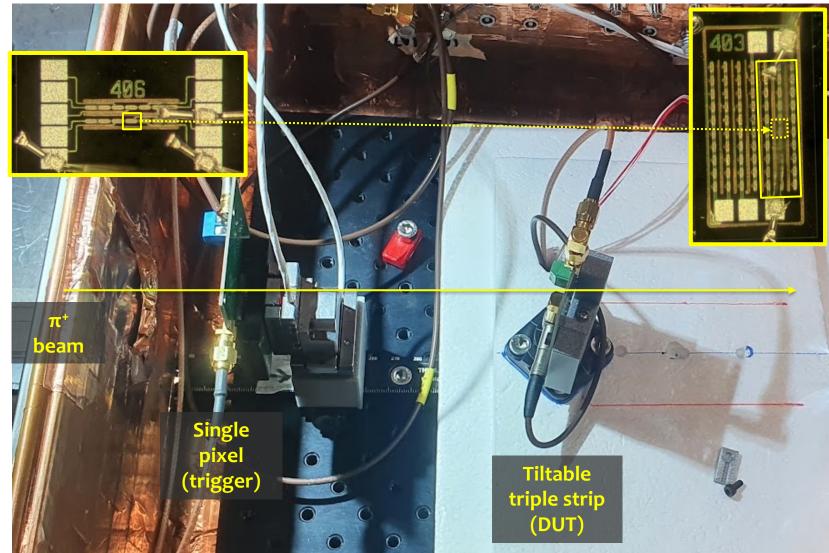

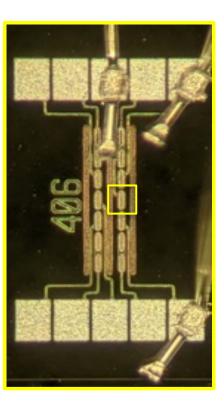

Tested structures. For each sensor the active area is shown in red. (A) Single pixels sensor; (B) strip sensor; (C) triple strip sensor

Paper in preparation: "New results on the TimeSPOT 3D-silicon sensors from measurements at SPS" (Frontiers in Physics)

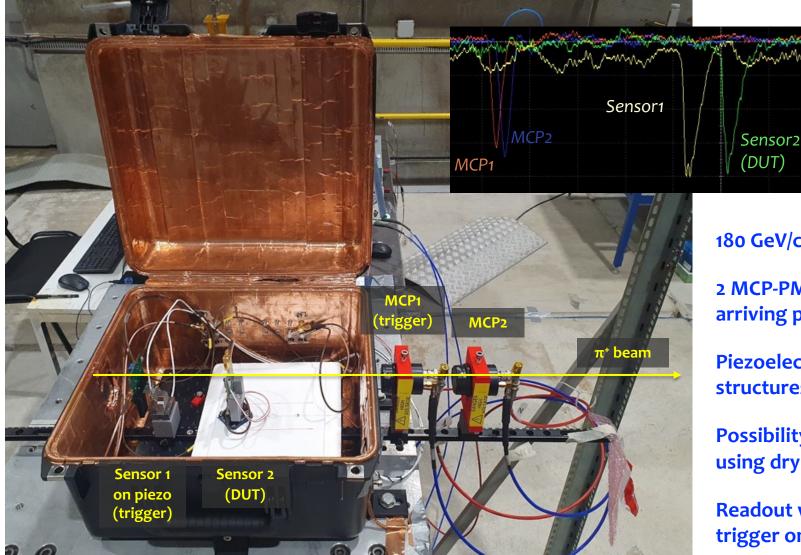

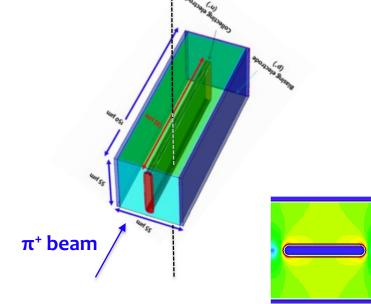

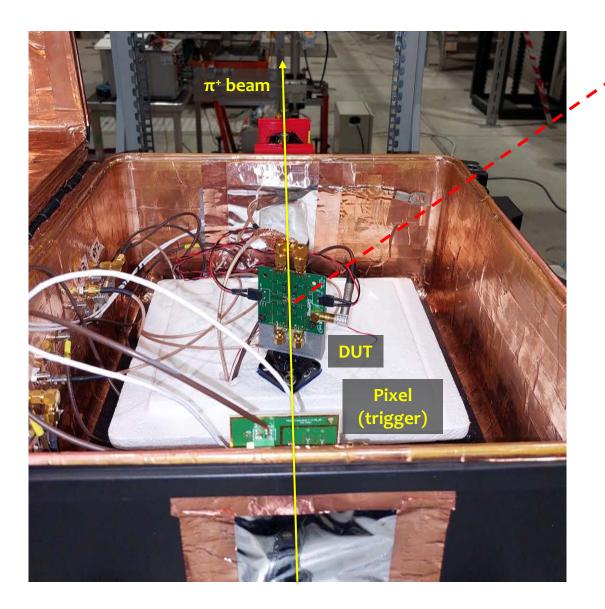

### **Experimental setup** Test-beams Nov21 & May22 @SPS/H8

#### 180 GeV/c $\pi^+$ beam

2 MCP-PMTs on the beam line to time-stamp the arriving particle ( $\sigma_{avg} = 5 \text{ ps}$ )

Piezoelectric stages to precisely align the two 3D structures with beam, all mounted in a RF-shielded box

Possibility of operating the fixed sensor down to -40°C using dry ice to test irradiated sensors

Readout with an 8 GHz bandwidth 20 GSa/s scope: trigger on the AND of one 3D sensor and one MCP-PMT

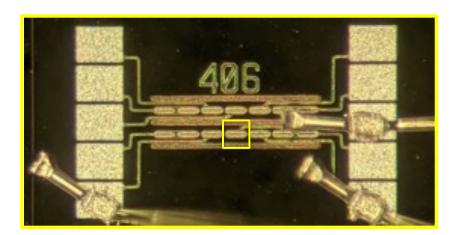

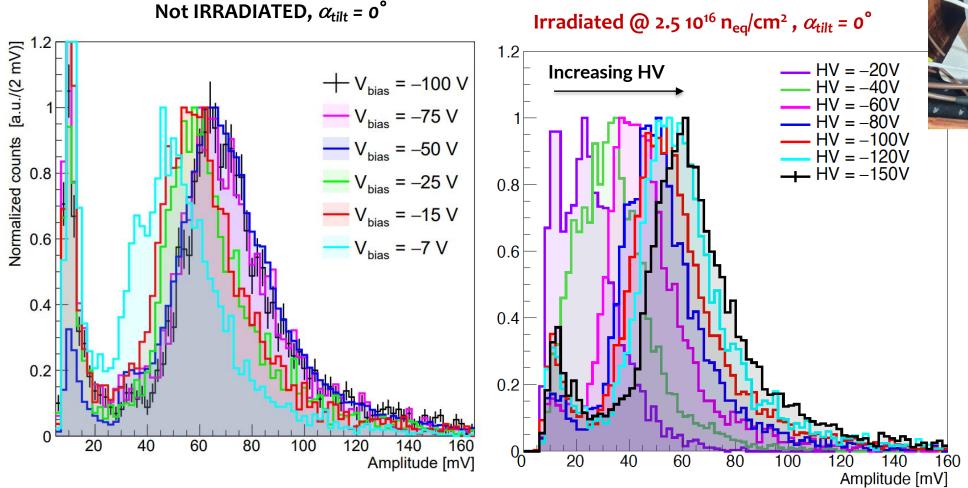

### **Amplitude distributions vs bias** Single pixel, not irradiated

#### Normal pion incidence ( $\alpha_{tilt} = o^{\circ}$ ) **DUT not on the trigger**

Very good sensor performance even at **low V**<sub>bias</sub> (prompt full depletion)

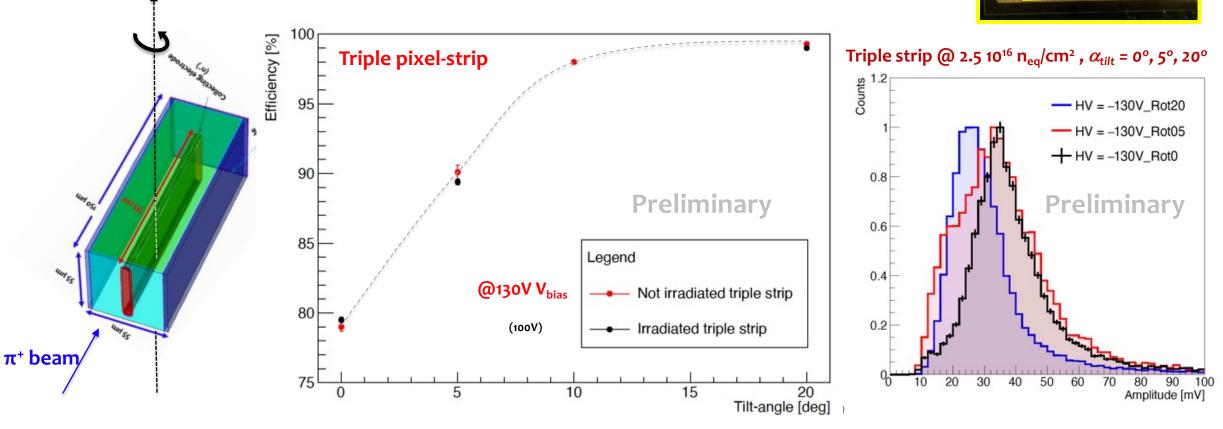

#### **Studies of Geometric Efficiency: setup**

Single pixel, not irradiated

Tilting the sensors with respect to normal incidence should allow to recover geometric efficiency

Trigger on one pixel (55  $\mu$ m x 55  $\mu$ m, on piezos) centered on a triple strip (165  $\mu$ m x 550  $\mu$ m, DUT) and counting the fraction of signals seen in the triple strip (on a single FE channel)

The DUT is rotated around the trench direction

#### **Efficiency: results** Triple Strip at different angles Efficiency vs tilt-angle Counts $-HV = -100V_Rot20$ Efficiency $-HV = -100V_Rot10$ 0.95 HV = -100V\_Rot0 **Preliminary** 0.8 **Total signal** 0.9 0.6 amplitude on triple strip 0.85 0.4 **Preliminary** @100V V<sub>bias</sub> 0.8 0.2 $\pi^+$ beam 20 10 15 5 Angle [deg] 10 20 50 30 40 60 Amplitude [mV]

The inefficiency (at normal incidence) due to the 3D pixel dead-area of the trenches is fully recovered by tilting the sensors around the trench axis at angles larger than 10°

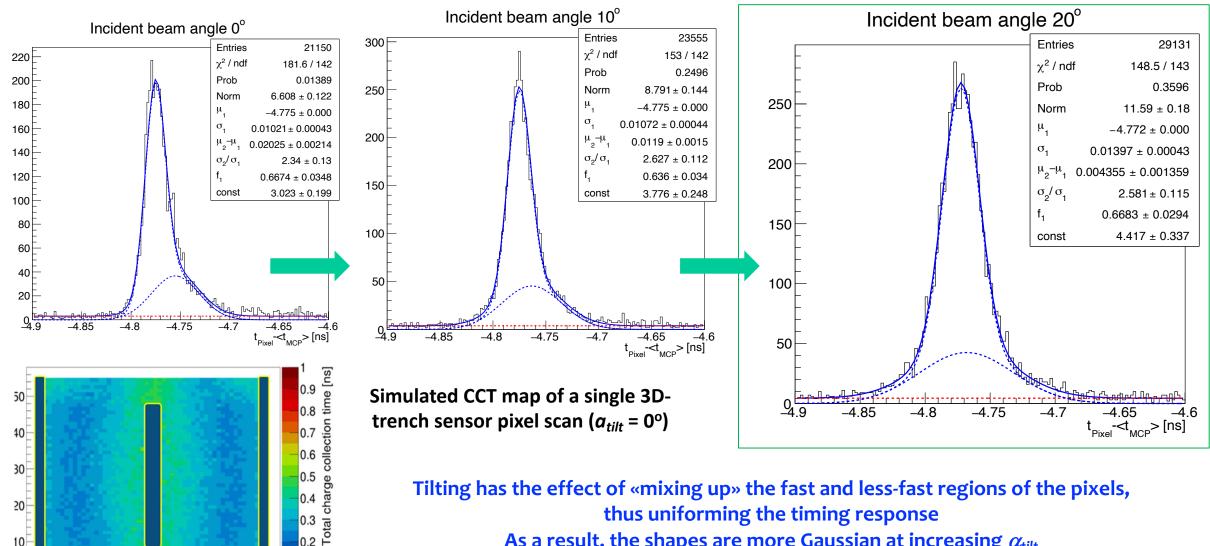

# **Tilted sensors: timing performance**

Single Pixel @ 50V

### **Effect of tilting on distribution shapes**

Spline method, SPS/H8 (Nov'21)

#### Single Pixel @ 50V

As a result, the shapes are more Gaussian at increasing  $\alpha_{tilt}$ Notice that, due to detection efficiency,  $\alpha_{tilt} = 20^{\circ}$  is the normal working condition of a 3D in a detecting system

50

X [um]

40

10

20

30

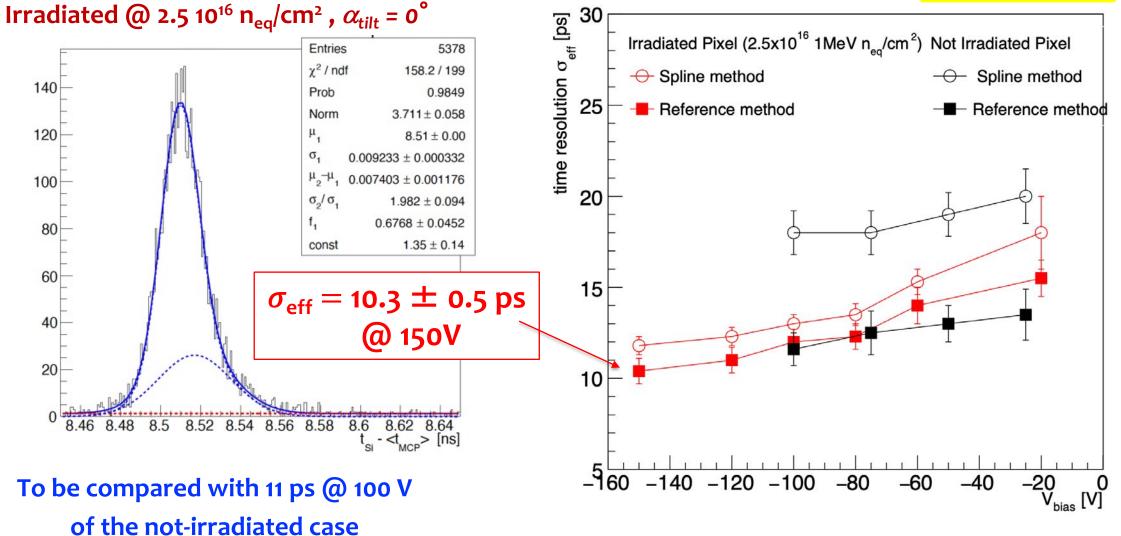

### **Amplitude distributions vs bias** Single pixel, **irradiated**

# Irradiated sensors: timing performance

### Irradiated sensors: geometrical efficiency

The inefficiency (at normal incidence) due to the dead-area of the trenches is fully recovered by tilting the sensors around the trench axis also for sensors irradiated with fluences of 2.5·10<sup>16</sup> 1-MeV neutron equivalent

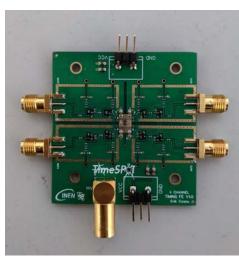

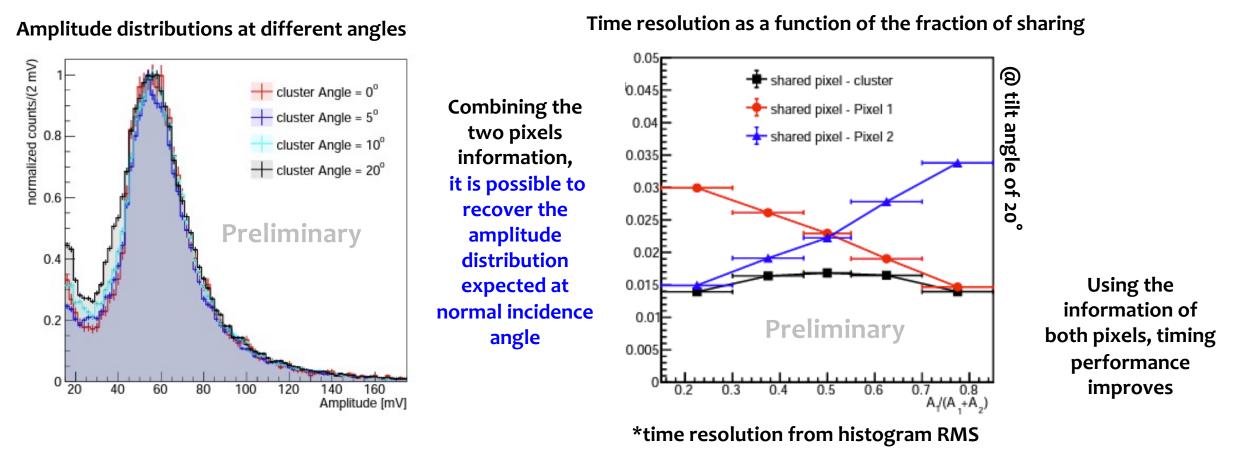

## **Charge sharing studies: setup**

4-channel FEE board

2 adjacent pixels – each one read-out by one FEE channel

Tilting the sensor it is possible to study the behaviour of two pixels when a charged particle crosses both of them

# **Charge sharing studies: results**

When a particle crosses two pixels:

- 1. Amplitude = sum of the amplitudes of the two signals

- 2. Time of Arrival = weighted sum on amplitudes of the ToA in the two pixels

September 2022

5-6<sup>th</sup>

31

Electronics: the decisive stage, TimeSPOT developments (fast item)

#### **CMOS 28-nm for pixels with timing capabilities** When system constraints come into play

| B           | BUT:<br>Rate constraints | ) [ | A first complete<br>«balanced HEP requ                                  | <u>гнср</u>           |                |

|-------------|--------------------------|-----|-------------------------------------------------------------------------|-----------------------|----------------|

|             | Area constraints         |     | Requirement                                                             | scenario ${\cal S}_A$ | scenario $S_B$ |

| TimeSPor 11 | Data BW constraints      |     | Pixel pitch [µm]                                                        | $\leq 55$             | $\leq 42$      |

|             | Power constraints        |     | Lifetime fluence $[1 \times 10^{16} 1 \text{ MeV } n_{eq}/\text{cm}^2]$ | ] > 6                 | > 1            |

| (INFN Ba    |                          |     | TID lifetime [MGy]                                                      | > 28                  | > 5            |

|             |                          | J   | Sensor Timestamp per hit [ps]                                           | $\leq 35$             | $\leq 35$      |

|             |                          |     | ASIC Timestamp per hit [ps]                                             | $\leq 35$             | $\leq 35$      |

|             |                          |     | Hit Efficiency [%] 1.5 W/d                                              | $:m^2 > 99$           | > 99           |

Power per pixel [µW]

Max discharge time [ns]

Pixel rate hottest pixel [kHz]

Bandwidth per ASIC of 2  $\rm cm^2~[Gb/s]$

Si-Ge input stages  $t_r \approx 100 \text{ ps}$ Measured  $\sigma_{ei} \approx 7 \text{ ps}$  @ 2 fC (1 MIP), 900 fs @ 20 fC

#### Why CMOS 28-nm? (last "bulk" CMOS node)

- 1. It optimizes performance vs radiation hardness, costs, and design techniques

- 2. It appears to be more rad-hard than subsequent (still very expensive) finFET technologies (es. 16 nm)

- 3. Most groups in HEP (CERN included) have chosen (for the reasons above) to adopt it for the next 5-10 years of developments

LHCb-U2 specs from physics needs. VELO support document for FTDR

< 23

> 350

< 29

> 250

The toughest constraint against speed is power budget, originating from the (un)capabilities of our best cooling system techniques at present (micro-channelling)

$\leq 14$

> 40

< 250

> 94

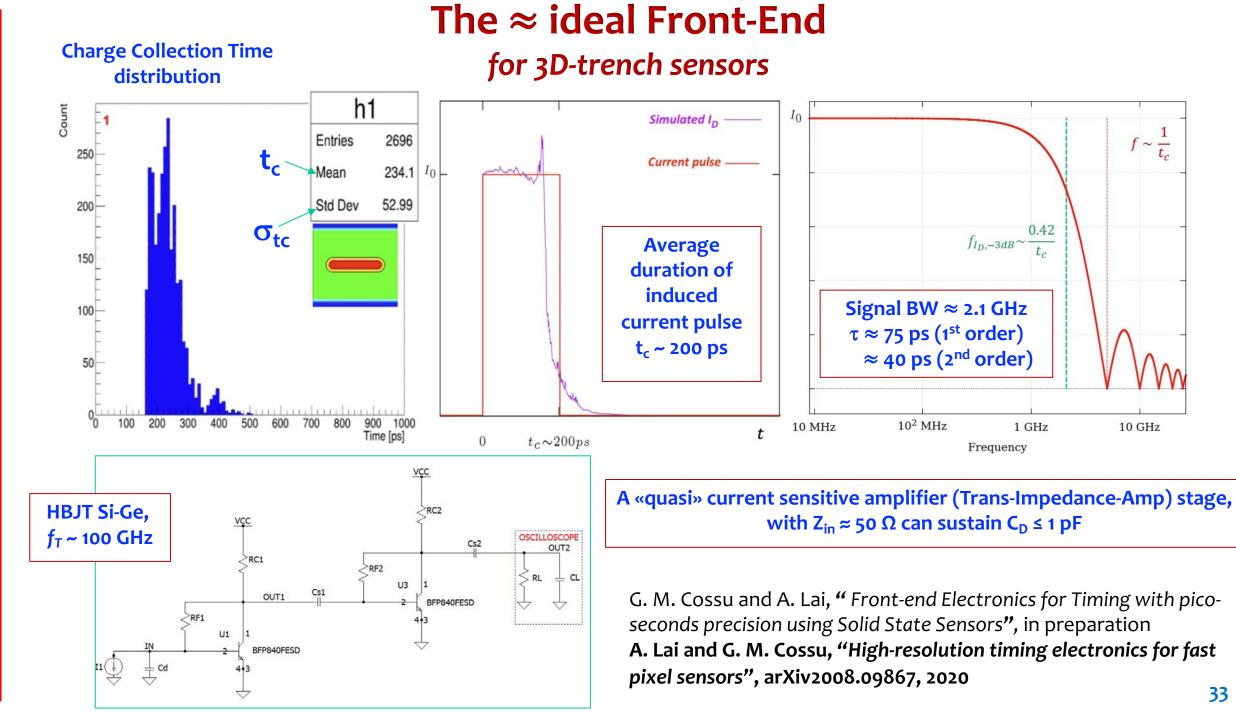

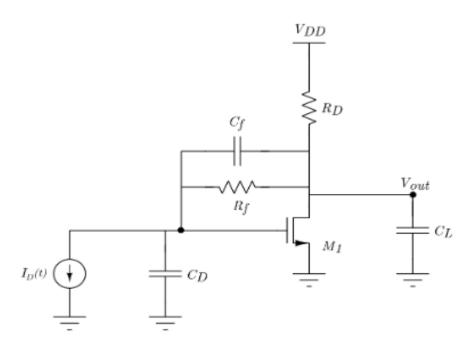

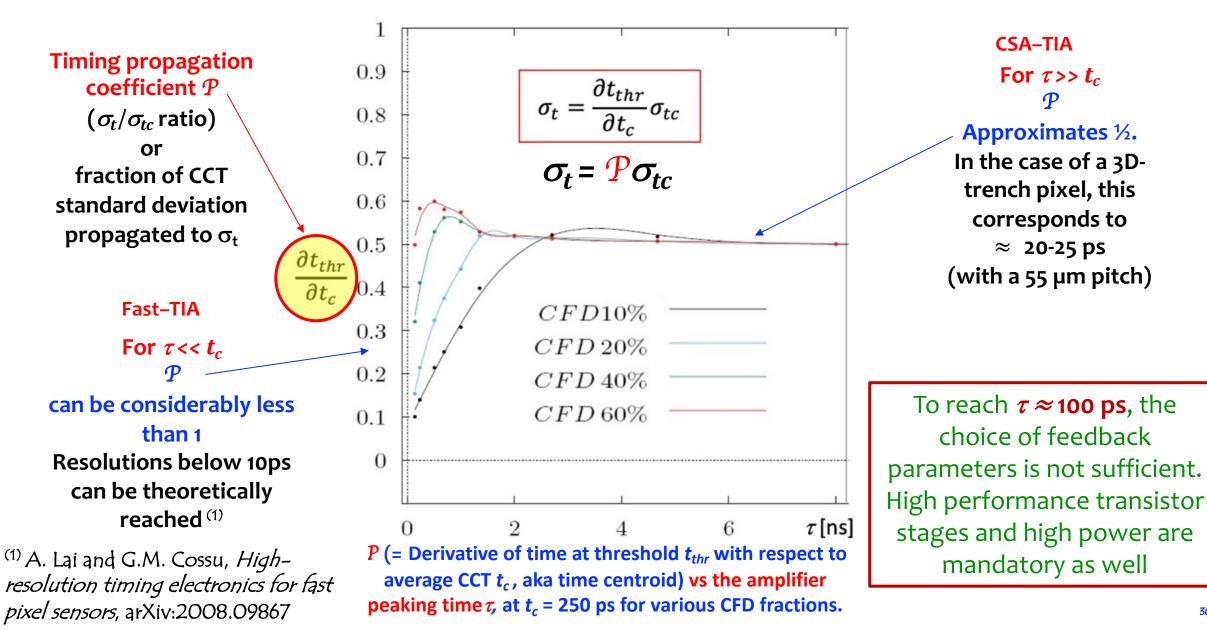

# "Alternative" roads to front-end solutions According to the FB parameters used, this scheme can range fr

Trans-Impedance-Amplifier with shunt-shunt feedback (FB–TIA).

Simplified schematic of the FB-TIA amplification stage

According to the FB parameters used, this scheme can range from an integrator (Charge Sensitive Amplifier) to a fast Current-Sensitive front-end. The role of the specific transistor tecnology used is also decisive, especially when very high speed is pursued (Si-Ge vs CMOS).

We can consider two extreme cases as examples<sup>(1)</sup>:

A) CSA-TIA, when the amplifier peaking time  $\tau >> t_c$ It can be demonstrated<sup>(1)</sup> that in this case

$$\sigma_t = \frac{\partial t_{thr}}{\partial t_c} \sigma_{tc} = \frac{1}{2} \sigma_{tc}$$

**B)** Fast-TIA, when the amplifier peaking time  $\tau \approx t_c$ It can be demonstrated<sup>(1)</sup> that in this case

$$\sigma_t = \frac{\partial t_{thr}}{\partial t_c} \sigma_{tc} \approx \frac{\tau}{2} \sqrt{\frac{V_{th}}{I_0 R_m}} \frac{\sigma_{tc}}{t_c} \approx \left( \frac{1}{2} \frac{\tau}{t_c} \sqrt{\frac{N}{S}} \right) \sigma_{tc}$$

<sup>(1)</sup> A. Lai and G.M. Cossu, *High-resolution timing electronics for fast pixel sensors*, arXiv:2008.09867

## **Front-end solutions: theoretical limits**

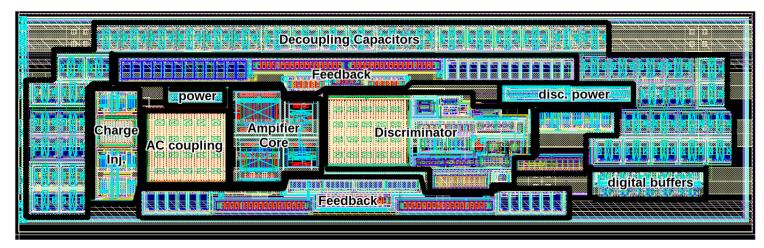

## Timespot1: Analog Front End

Inverter core amplifier with double Krummenacher FB

Inverter-based Charge Sensitive Amplifier (CSA) with DC current compensation.

Leading Edge Discriminator with Discrete-time Offset-Compensation for threshold uniformity OC procedure: 250 ns every ≤800 µs

| Sensor                                | Ref       | Offset<br>Compensation |

|---------------------------------------|-----------|------------------------|

| Test<br>Pulse Charge<br>Injection Cac | feed back |                        |

| Pwr regime             | nominal | high |

|------------------------|---------|------|

| Pwr/channel [µW]       | 18.6    | 32.9 |

| Slew rate [mV/ns]      | 250     | 360  |

| $Z_{in}[\Omega]$ in BW | 23k     | 23k  |

| Gain [dB]              | 93      | 93   |

| RMS noise [mV]         | 3.9     | 3.8  |

| BW [MHz]               | 311     | 455  |

| Jitter [ps]            | 15.6    | 10.5 |

Expected performance @ 2 fC (post-layout simulation)

50x15 µm<sup>2</sup>

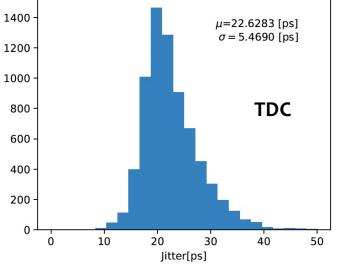

### Timespot1: TDC

Fully digital design, standard-cell based

cnt\_tot

ck 0 cnt tot

cnt 0

ck 0 cnt0

cnt 1

ck 1

cnt1

TOT

TA

\_hit High resolution, "low" To maximize sustainable rate, 1 start consumption TDC TDC per pixel channel has been CC 🔁 DCO\_0 1st MONOLITH Wshop – UniGeneve, based on 2 DCOs and a integrated hit start ck 0 Vernier architecture hit CC Max input rate = 3 MHz CC CC stop start 23 bits output word (ToA + ToT) ToT resolution  $\approx$  1 ns Ck 40MHz CC 0 DCO 1 stop ck 1 ΕN CC **Expected power per rate** 200.0 TΑ 180.0 clk 40 MHz 160.0 signal 140.0 TOT Power [µW] 120.0 TimeSPOT results – A. Lai 100.0 The TDC gives the phase of the 80.0 signal wrt the 40MHz BX clock 38 µW @ 350 kHz 60.0 The TDC and the counter use the (LHCb max rate) Could be split among 40.0 same DCO-generated Clk (~1 GHz) several channels 20.0 4 levels of Vernier precision ( $\Delta f$  in 0.0 DCOs) can be programmed. 4000 1000 2000 3000 Typical LSB 12 ps Hit Rate [kHz]

50x32 µm<sup>2</sup>

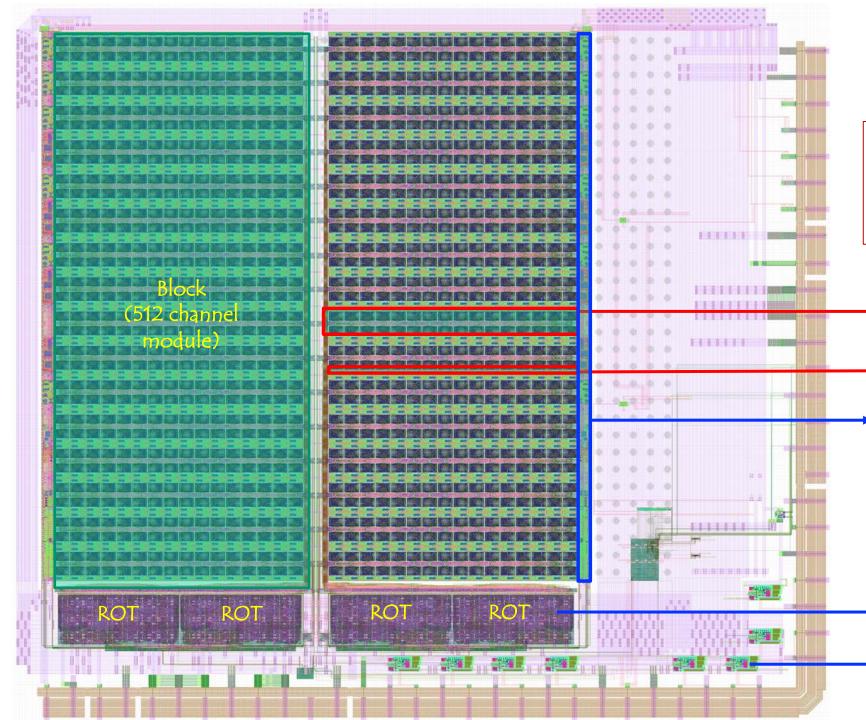

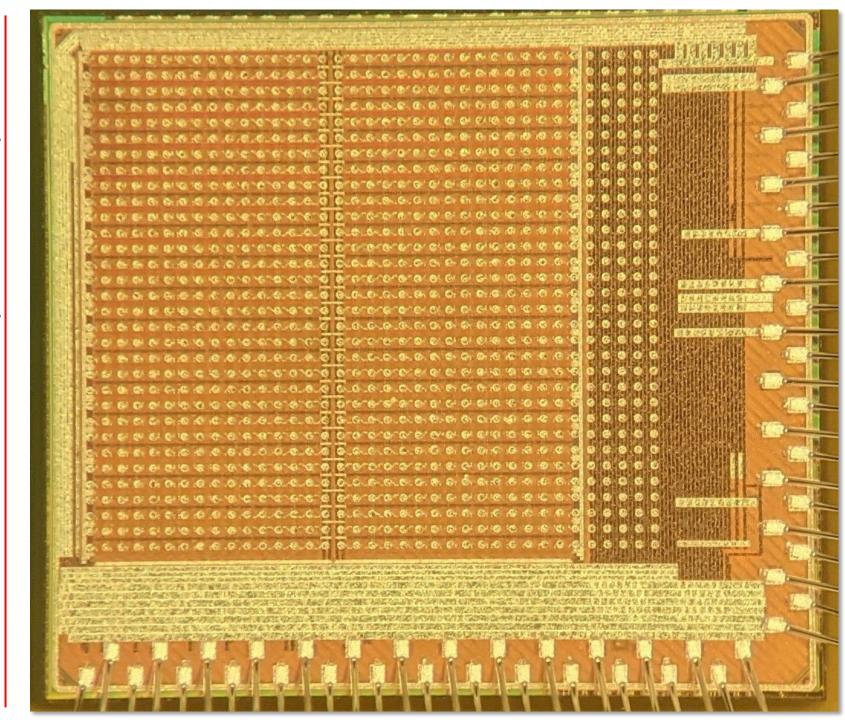

### **Timespot1 ASIC** 28-nm CMOS

- Reduced size (1024 pixels, 6 mm<sup>2</sup>)

- HPC flavour

- Complete set of functionalities for pixel readout

- Slow read-out (demo-test purpose)

### 640 MHz master clock

- Digital row: 16x2 TDC

- + Controls, Conf. registers, I<sup>2</sup>C I/F

- Analog row (16x2 AFE)

- Analog (service) column. Each contains:

- 1 Band-Gap circuit

- $5x \Sigma \Delta$  DACs (producing analog levels used by pixels)

- Programmable bias cell (for power consumption)

- bias replicas with source followers.

- 4x Read Out Trees

- 8x LVDS driver

(each @1.28 Gbps)

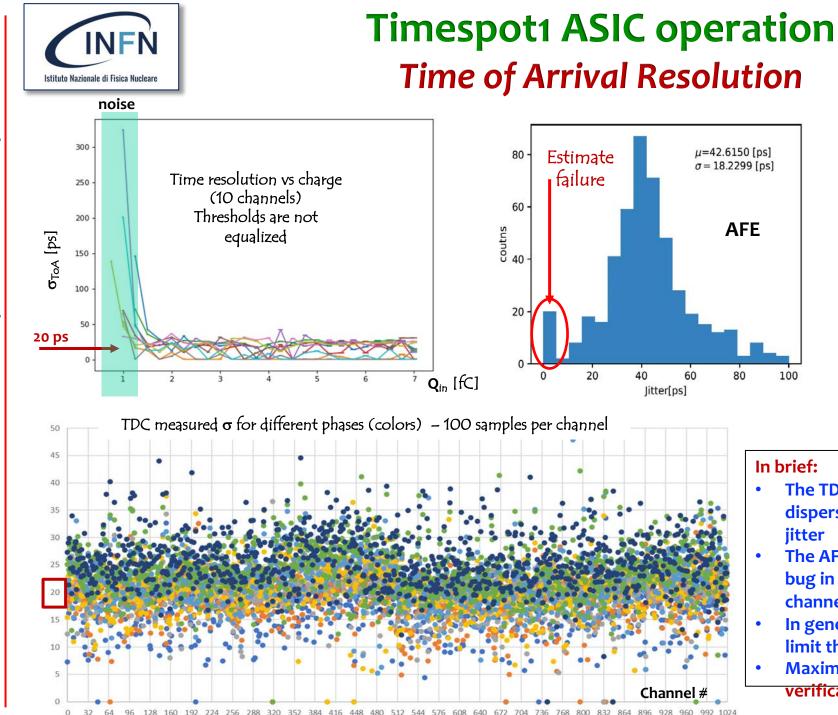

9

Distribution of the TA standard deviation across 1024 channels and 7 phases. Each point is computed from 100 repeated measurements.

#### In brief:

100

80

coutros

- The TDC has a typical  $\sigma_t \approx 20$  ps, with relatively wide dispersion (5 ps) and is limited by the system clock iitter

- The AFE  $\sigma_t$  is intrinsically below 20 ps but an identified bug in the discriminator spoils  $\sigma_t$  in most of the channels. The bug is easily amendable.

- In general, global (digital) clock distribution issues limit the very good resolution at the pixel level.

- Maximum care is mandatory in global layout and final verification procedures

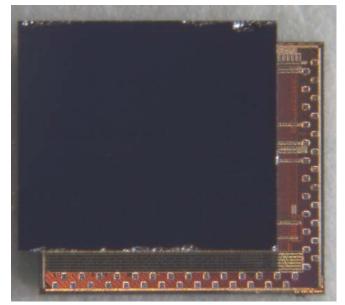

#### Timespot1 on 3D-trench silicon matrix

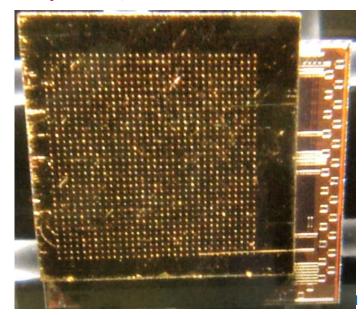

#### Timespot1 on 3D-column diamond matrix

## Conclusions

- 3D-trench (geometric) sensors show excellent performance in timing even at extreme fluences → the limit must still be reached

- 2. Electronics is by far the weak ring of the chain

- 3. Reaching ≈20 ps time resolution in 28-nm CMOS can be «easily» achieved as far as the pixel circuit is concerned within a low-moderate power budget

- 4. 4D timing is mainly not a matter of sensors or single devices, it is a matter of system constraints (power in primis, cooling, stable clock distribution, interconnectivity, data BW, material budget)

- 5. The timing problem size scales dramatically with the area (and volume) of the system

- 6. A system-level development has to be launched soon

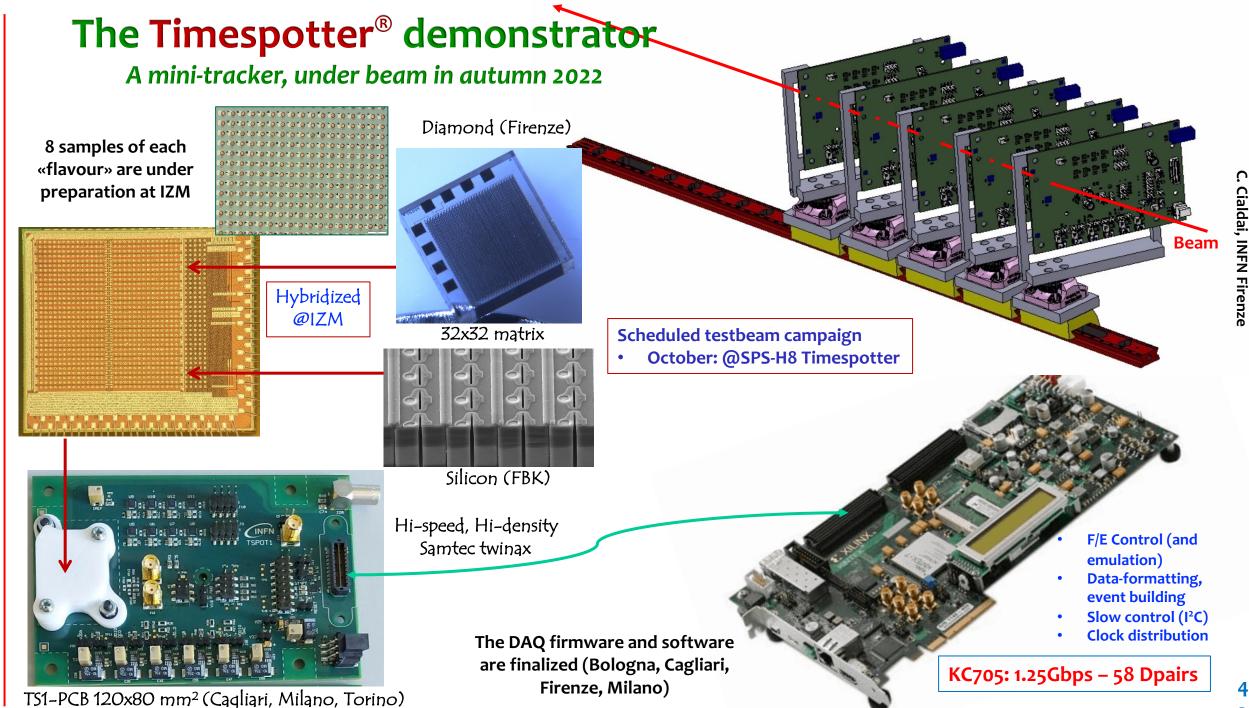

## A glimpse into the (immediate) future

Interposer-free flip-chip integration using a high-speed PCB

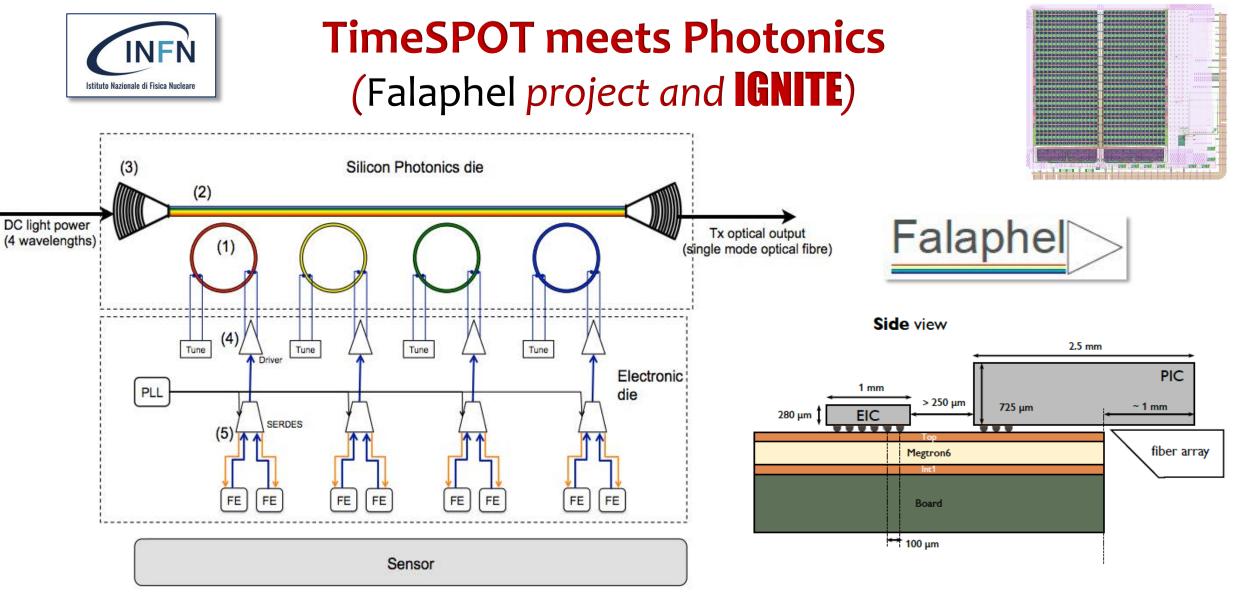

Schematics of the PIC and EIC assembly (FALAPHEL demonstrator). Ring resonators (1) with different and tunable resonator wavelengths are located along horizontally drawn bus waveguides (2) which are connected to optical glass fibers by efficient and robust focusing grating.

#### **Electronics and Technologies for fast (high density) timing** (in the «hybrid approach») Vision/concept of a cut of Tracks the **IGNITE** system module Ground-up iNITiative for **UE**lectronics developments (not to scale) Sensor Bump bonding or equivalent RDL (Ri-Distribution Layer) (Thinned) CMOS 28-nm **ASIC** µChannel cooling system TSV Auxiliary components and interposer & optical read-out (PIC) cooling plate

### Target deliverable of the **IGNITE** project:

- A complete module (sensor, read-out ASIC, vertical IC, photonic circuit for data links, cooling system)

- The module development as a route to optimize material budget issues and High Density Interconnectivity between the device stages

- The whole thing below 0.8 (LHCb)  $\div$  0.5 (NA62) % X<sub>o</sub>

# **INFN Institutes and Organization**

| Bologna  | LNF       | Perugia |

|----------|-----------|---------|

| Bari     | Milano    | Pisa    |

| Cagliari | Milano B. | Torino  |

| Genova   | Padova    | TIFPA   |

| Firenze  | Pavia     |         |

- 14 INFN Institutes

- Involvement of researchers from ATLAS, CMS, LHCb, NA62

- 20 FTE + dedicated Research Contracts on project funds

- 4 year project

- Funds: 2.4 M€ for developments and ASIC submissions

- Additional specific budget for HR (amount still under definition)

- Starting 2023

### INSIGHTS

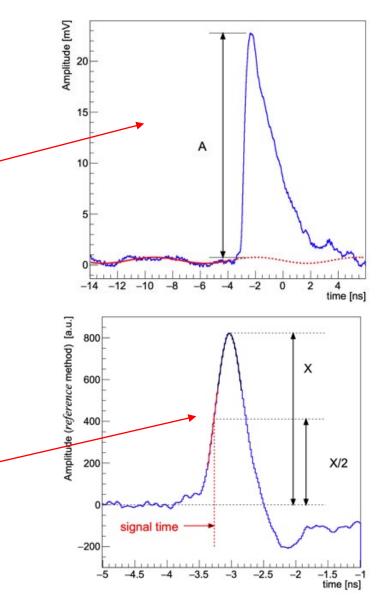

# Waveform processing

For each sensor's waveform:

- Signal baseline (red-dashed line) is evaluated on an event-by-event basis

- The signal amplitude A is measured (w.r.t. to the event baseline)

- Signal time of arrival evaluated with various methods:

- Leading-edge: time at 15 mV signal amplitude, linear interpolation around threshold (time-walk effect is present)

- LE corrected for the amplitude to suppress the time-walk effect

- Spline: a classic CFD at 20% with rising edge interpolated with a spline

- Reference: subtract each waveform from a delayed (by about half of the signal rise time) copy of itself, then on the resulting signal we trigger at X/2 height

## **Efficiency: method**

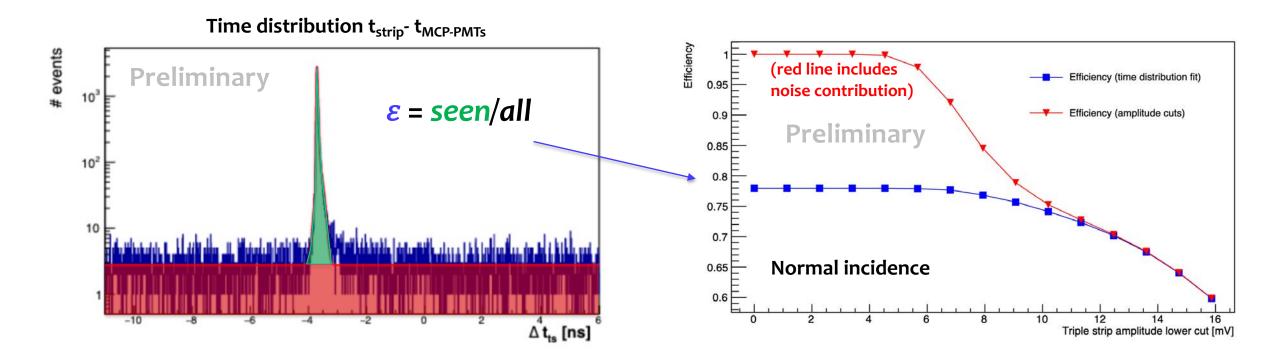

- Time distribution of **all triple-strip signals** w.r.t. MCP-PMTs and count as 'seen' the ones under the peak (the flat background corresponds to undetected hits)

- 3D pixel detection (geometrical) efficiency at normal incidence is in agreement with calculated fraction of active area (~80%)