## Timing in monolithic sensors in 65 nm

Analog pixel test structure (APTS) and Digital pixel test structure (DPTS) in TPSCo 65 nm ISC W. Snoeys

Geneva, Switzerland

### MONOLITH workshop Uni Geneva Sept. 5<sup>th</sup>, 2022

The workshop organizers

and colleagues from CERN, the ALICE ITS and ITS3 upgrade, ATLAS Itk, EP R&D WP1.2 ...

## CMOS Monolithic Active Pixel Sensors revolutionized the imaging world

#### reaching:

- Iess than 1 e<sup>-</sup> noise

- > 40 Mpixels

- Wafer scale integration

- Wafer stacking

- Silicon has become the standard in tracking applications both for sensor and readout

... and now CMOS MAPS make their way in High Energy Physics !

Hybrid still in majority in presently installed systems

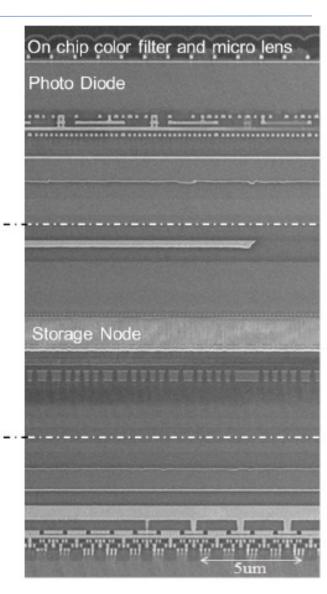

Top part (BI-CIS process technology)

Middle part (DRAM process technology)

Bottom part (Logic process technology)

Sony, ISSCC 2017

New technologies (TSV's, microbumps, wafer stacking...) make the distinction more vague.

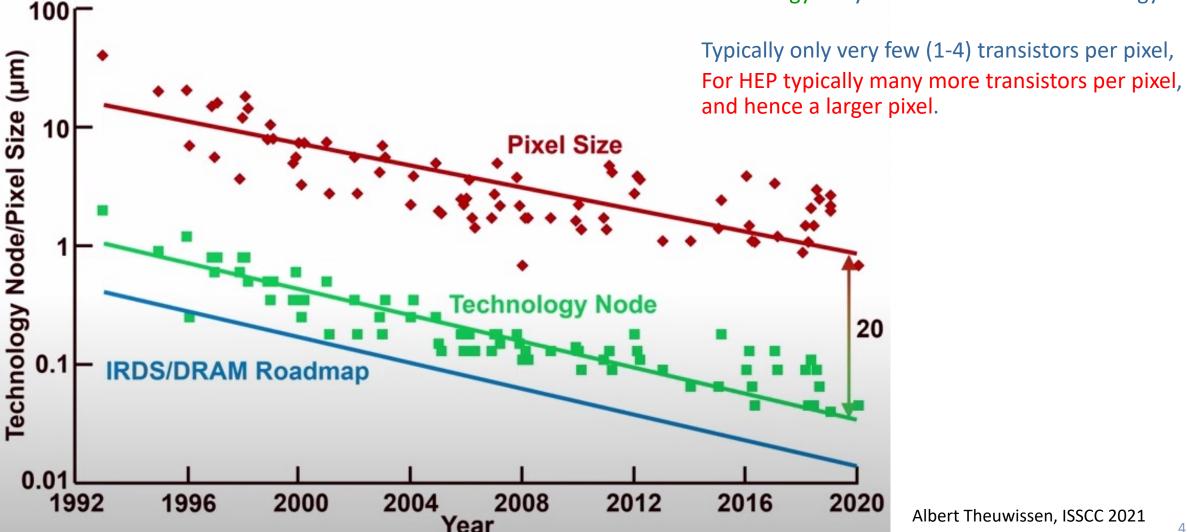

Evolution of pixel size and technology node for visible:

# **Pixel Size Evolution**

Pixel size: 20x above technology feature size

Technology: 10 years behind DRAM technology

Albert Theuwissen, ISSCC 2021

| <b>Requirements for High Energy Physics</b>                                                                                                     |                          | Dose   | Fluence                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------|----------------------------------------------------------|

|                                                                                                                                                 |                          | (Mgy)  | (10 <sup>16</sup> 1MeVn <sub>eq</sub> /cm <sup>2</sup> ) |

| Radiation tolerance                                                                                                                             | ALICE ITS                | 0.01   | <b>10</b> <sup>-3</sup>                                  |

| <ul> <li>CMOS circuit typically more sensitive to ionizing radiation</li> <li>Sensor to non-ionizing radiation (displacement damage)</li> </ul> | LHC                      | 1      | 0.10.3                                                   |

|                                                                                                                                                 | HL-LHC 3ab <sup>-1</sup> | 5      | 1.5                                                      |

|                                                                                                                                                 | FCC                      | 10-350 | 3-100                                                    |

Single particle hits instead of continuously collected signal in visible imaging

- Sparse images < or << 1% pixels hit per event

- Near 100% efficiency, full CMOS in-pixel needed, often circuit (much) more complex

Position resolution (~µm)

#### Low power consumption is the key for low mass

- Now tens of mW/cm<sup>2</sup> for silicon trackers and hundreds of mW/cm<sup>2</sup> for pixels

- Despite enhanced detector functionality for upgrades, material penalty limits power consumption increase

More bandwidth

**Time resolution**

Time stamping ~ 25 ns or even lower, ... much lower (10s of ps)

Larger and larger areas

- ALICE ITS2 10 m<sup>2</sup>, discussions on hundreds to even thousands square m<sup>2</sup>,

- Interest for versatile sensors programmable for different applications (P. Allport CERN EP seminar 2020)

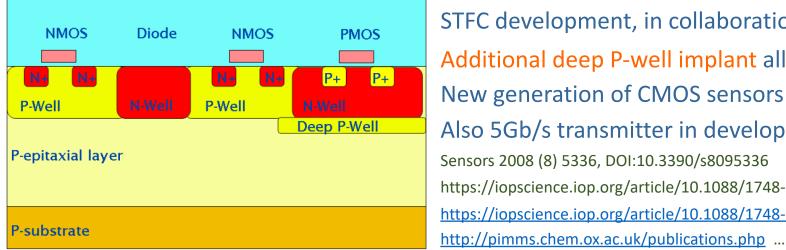

# The INMAPS process: quadruple well for full CMOS in the pixel

STFC development, in collaboration with TowerJazz **180nm** Additional deep P-well implant allows complex in-pixel CMOS and 100 % fill-factor New generation of CMOS sensors for scientific applications (TowerJazz CIS 180nm) Also 5Gb/s transmitter in development Sensors 2008 (8) 5336, DOI:10.3390/s8095336 https://iopscience.iop.org/article/10.1088/1748-0221/7/08/C08001/meta https://iopscience.iop.org/article/10.1088/1748-0221/14/01/C01006/meta https://iopscience.iop.org/article/10.1088/1748-0221/14/01/C01006/meta

courtesy of N. Guerrini, STFC

walter.snoeys@cern.ch

Standard INMAPS process also used for the ALPIDE (27  $\mu$ m x 29  $\mu$ m pixel) and MIMOSIS (CBM)

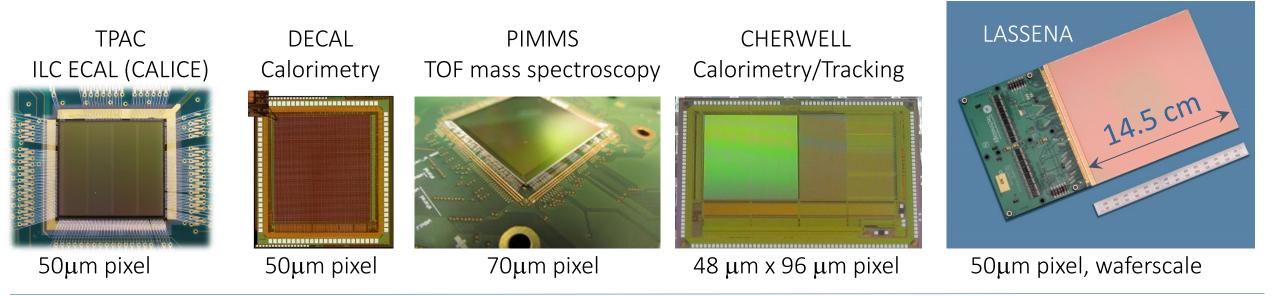

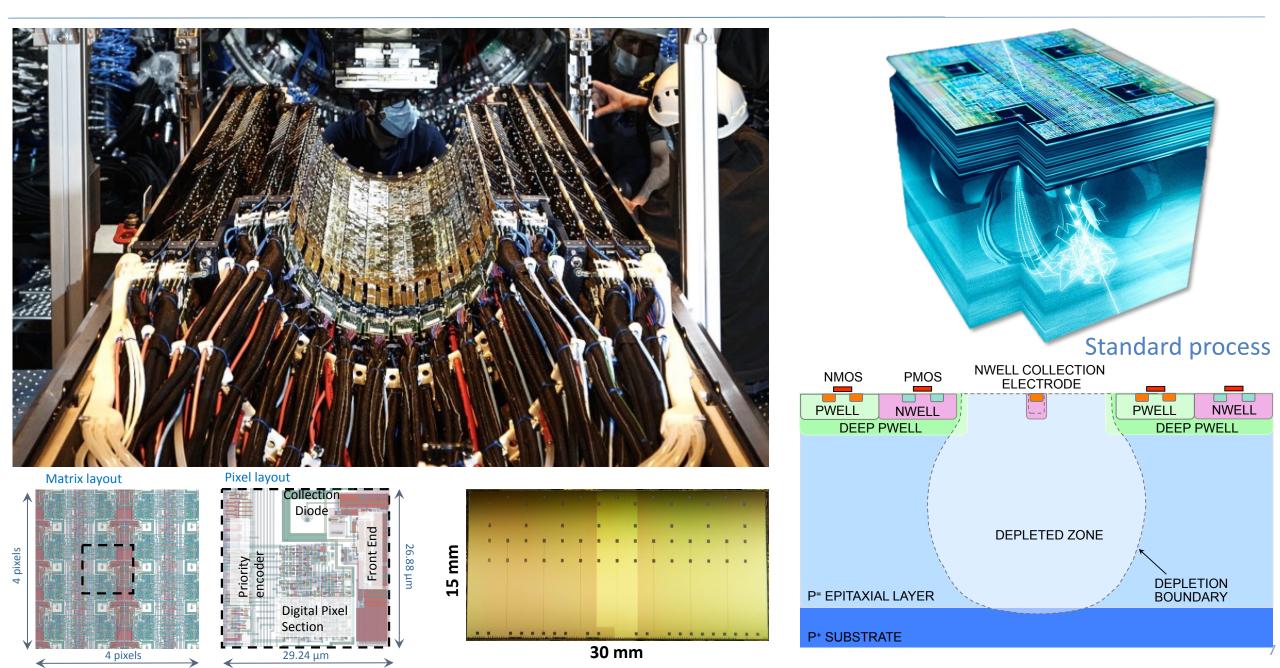

## State of the art: ITS2 and ALPIDE in ALICE: 10 m<sup>2</sup>, 12.5 Gpixels

## Sensor optimization

TowerJazz 180nm imaging CMOS technology

- Side development in ALICE: move junction away from the collection electrode to deplete epitaxial layer

- add deep low dose n-type implant -> radiation tolerance improved by an order of magnitude.

- After interest from ATLAS: MALTA/TJ MONOPIX development (Bonn, CPPM, IRFU and CERN)

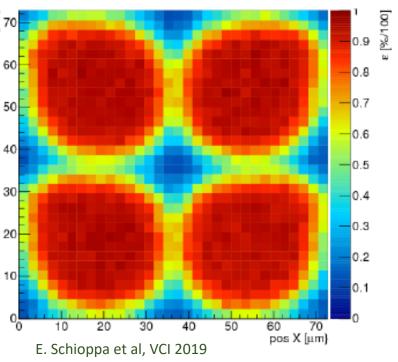

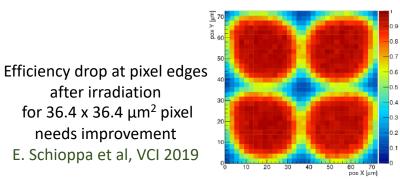

- However, efficiency loss at ~ 10<sup>15</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup> on the pixel edges and corners due to a too weak lateral field

EP R&D

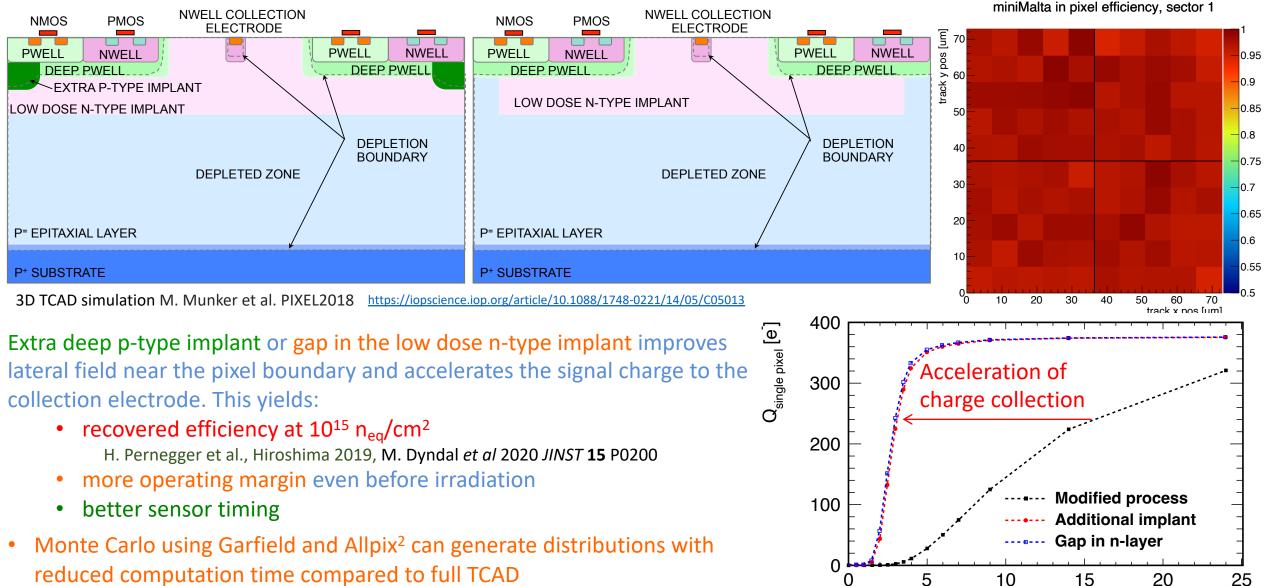

## TCAD simulations and sensor optimization

TowerJazz 180 nm imaging CMOS technology

EP

R&D

Time [ns]

walter.snoeys@cern.ch

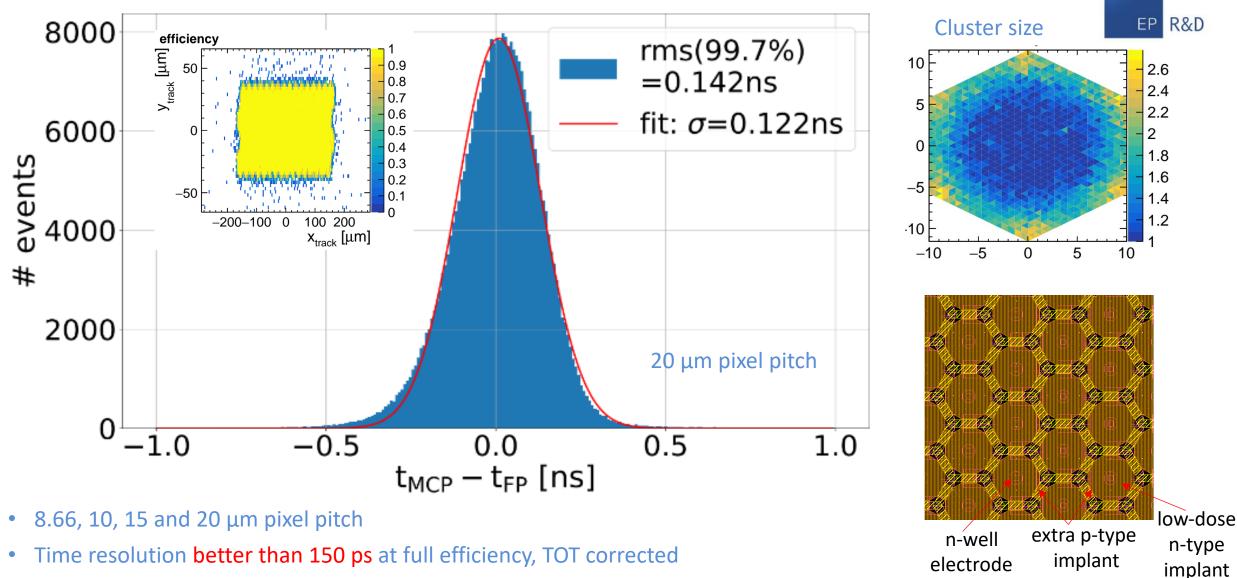

## FASTPIX ATTRACT project: focused on fast timing

### Direct relation between charge collection and process variant (TowerJazz 180nm)

Significant impact even at very small pixel pitch Hexagonal pixels

- better approximation of a circle

- charge sharing in the corners between 3 pixels instead of 4 -> more margin

- collection electrodes on hexagonal grid, circuit remains on Manhattan layout

T. Kugathasan et al., <u>https://doi.org/10.1016/j.nima.2020.164461</u>

FASTPIX started as an ATTRACT project funded by the EC Grant Agreement 777222, with INFN, Ritsumeikan U. and CERN

## FASTPIX: sensor optimization for hexagonal pixels

#### https://www.mdpi.com/2410-390X/6/1/13

J. Braach, E. Buschmann, D. Dannheim, K. Dort, T. Kugathasan, M. Munker, M. Vicente

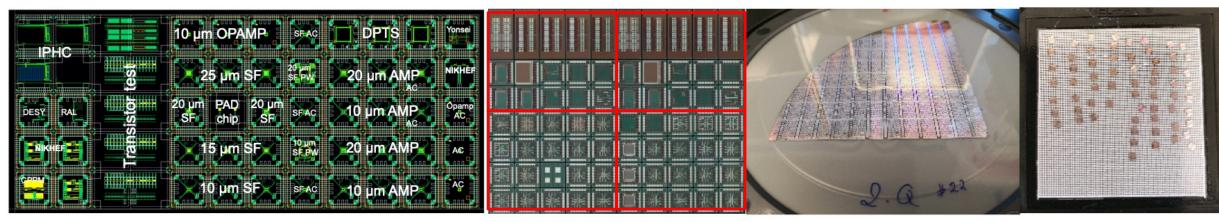

## Moving to deeper submicron CMOS: CERN EP RD and the ALICE experiment

#### First technology selected: TPSCo 65 nm ISC

EP R&D

- TPSCo (joint venture TJ & Panasonic): several 65 nm flavors: high density logic, RF, and imaging (ISC)

- ISC preferred: 2D stitching experience, special sensor features, different starting materials, lower defect densities, etc

- Initially 5 metal layers, now 7 metals

- NDA (M. Campbell, L. Pocha & M. Ayass) for participating groups

- Finance Committee approval for stitched runs

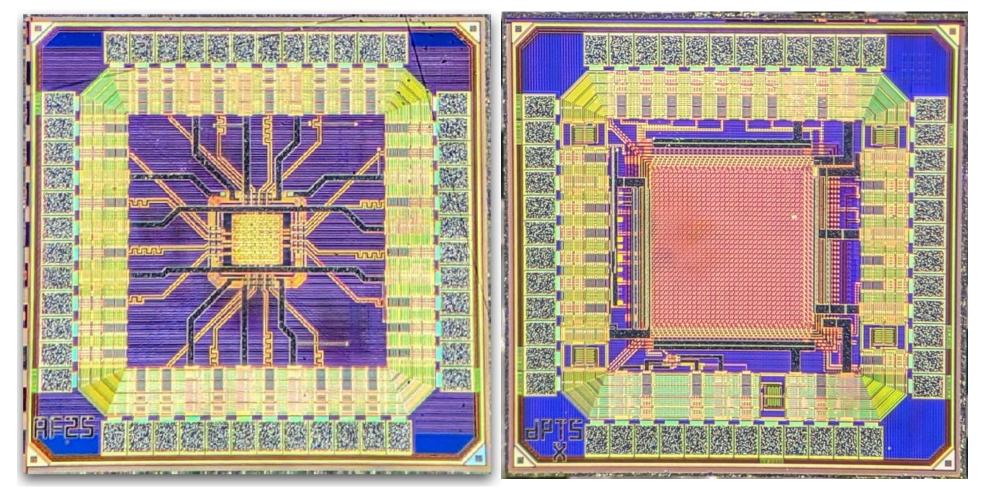

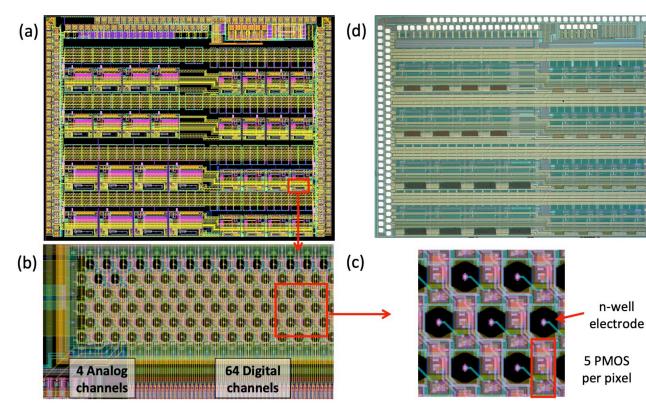

#### First submission: Multi Layer per Reticle MLR1

- Significant contribution from outside groups (from ALICE but not only) to design and test (!), also financially

- Many test chips of 1.5 x 1.5 cm<sup>2</sup> or twice that size.

- GDS submitted Dec 1, 2020, chips ready to test, Sept, 2021

20220620 | EP R&D WP1.2 Report | Monolithic Sensor Development

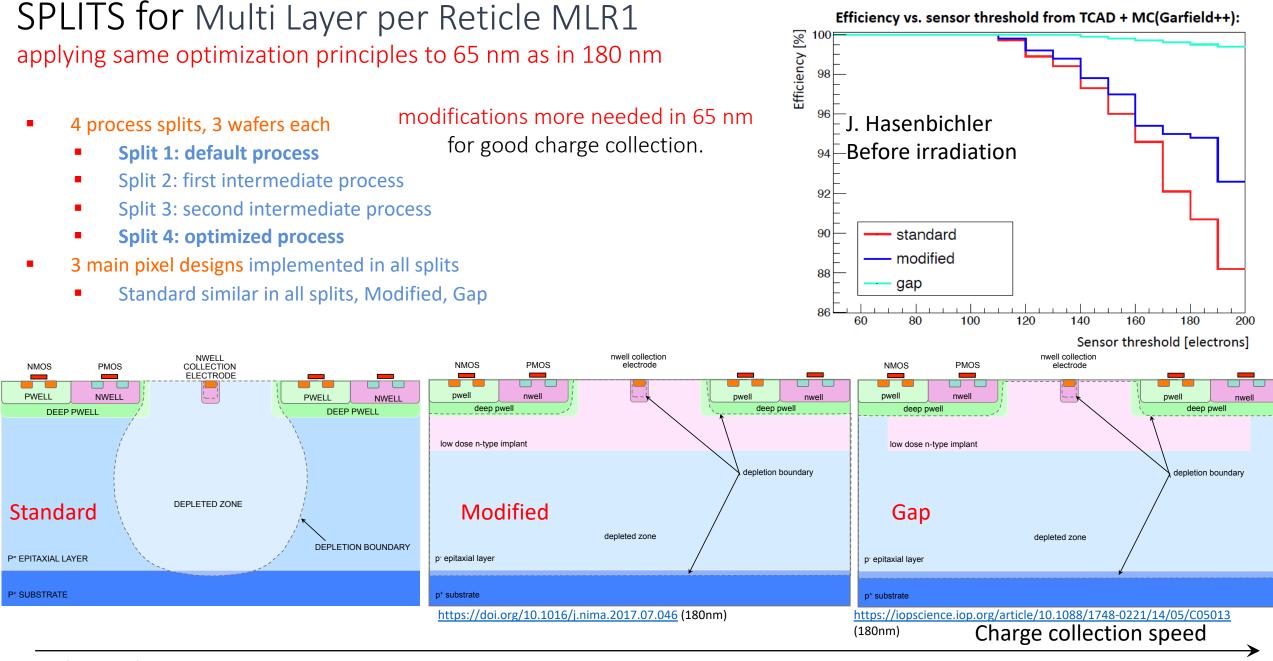

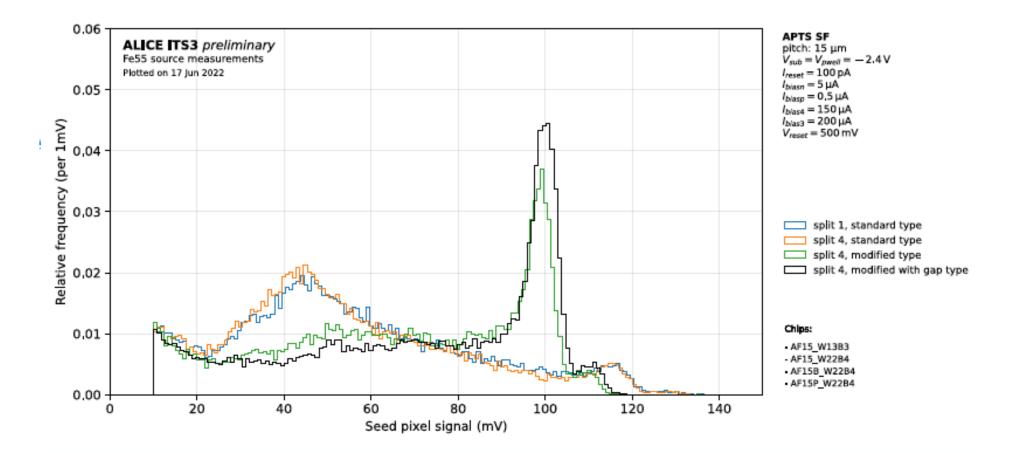

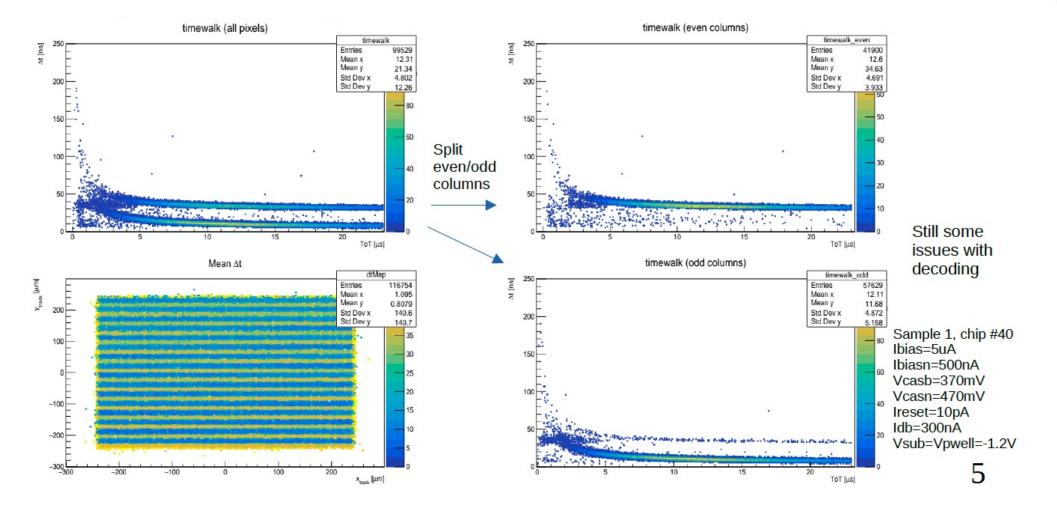

#### Charge sharing

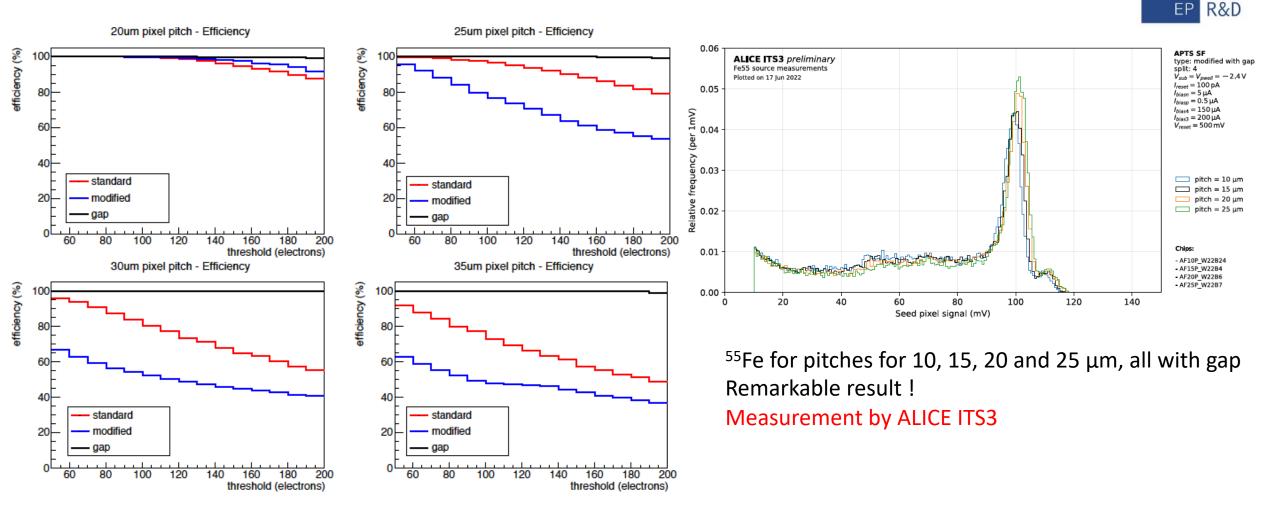

## Different pixel flavors exhibit very significantly different behaviour

Standard process exhibits quite some charge sharing, modified concentrates charge much more on single pixel Measurement by ALICE ITS3

EP R&D

## Different pixel flavors at larger pixel pitches

#### Only gap maintains reasonable efficiency

Simulations by J. Hasenbichler Further experimental verification in testbeam in progress

## MAIN RESULTS MLR1 65 nm

#### Functionality

- Fully efficient sensor, analog front end, digital readout chain in 15 x 15 μm<sup>2</sup> pixel (DPTS) including sensor optimization

- Sensor optimization clearly accelerates charge collection

- Frontend tunable from 10 nA to 5 μA (power time resolution tradeoff)

- Measurements at 100 nA, time resolution ~7.5 ns

#### **Radiation effects**

- Single event upset cross-section according to expectations

- Circuit radiation tolerance TID in line with other 65 nm technologies

- Sensor radiation tolerance NIEL: analysis in progress:

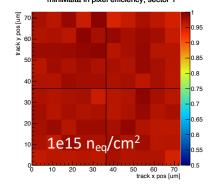

- ~ 99% efficiency after 1e15  $n_{eq}$ /cm<sup>2</sup> and 10 Mrad at room temperature

- higher fluencies to be investigated, also at lower temperature

### Building knowledge about this technology for general interest

- Very significant contribution from the ALICE experiment

- Towards full technology validation for our applications

### Next submission Stitched Engineering Run ER1

• Learning about stitching and continue learning about the technology walter.snoeys@cern.ch

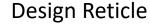

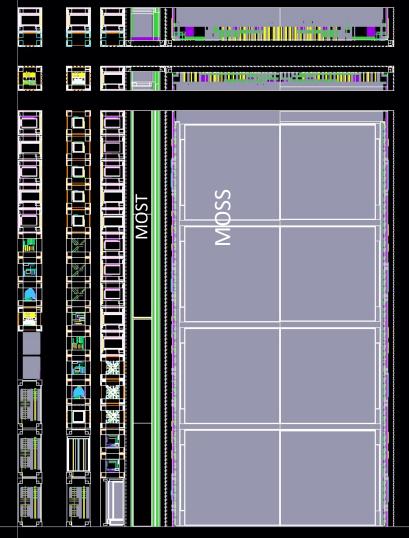

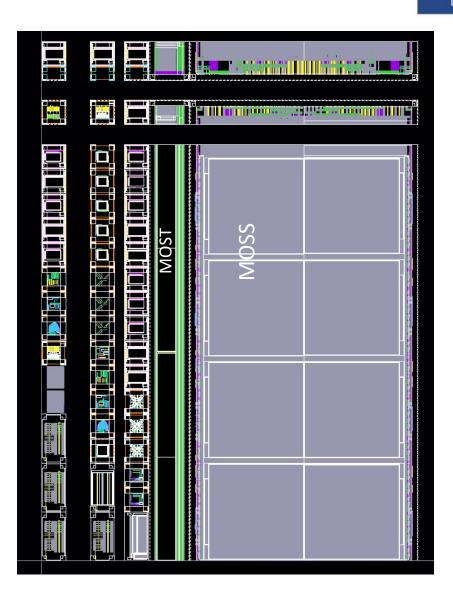

# ER1 Submission

- Learn and prove stitching

- Two large *stitched* sensor chips (MOSS, MOST)

- Different approaches for resilience to manufacturing faults

- Multiple small Test Chips

- Pixel and Circuit Prototypes

- Fast Serial Links

- Technology and Support

- New metal stack, new I/O libraries, new PDKs

- Specific features of kits and libraries

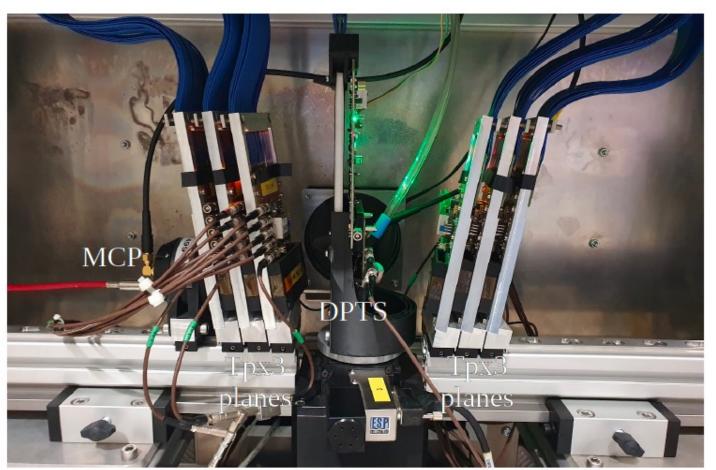

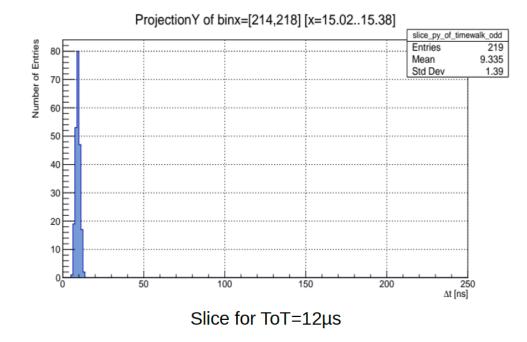

# DPTS timing measurements at higher currents

#### Measurements: E. Buschmann et al.

- Setup: Timepix3 telescope with Hamamatsu

R4809U-50 MCP-PMT as time reference (< 10 ps</li>

RMS at 3.2 kV), Caribou readout

- Very preliminary results

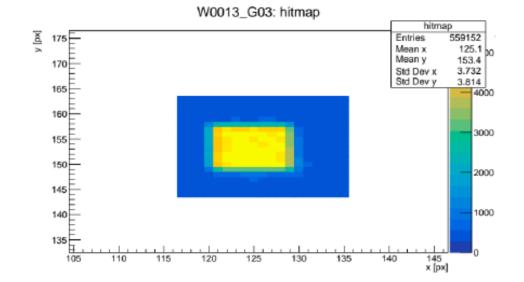

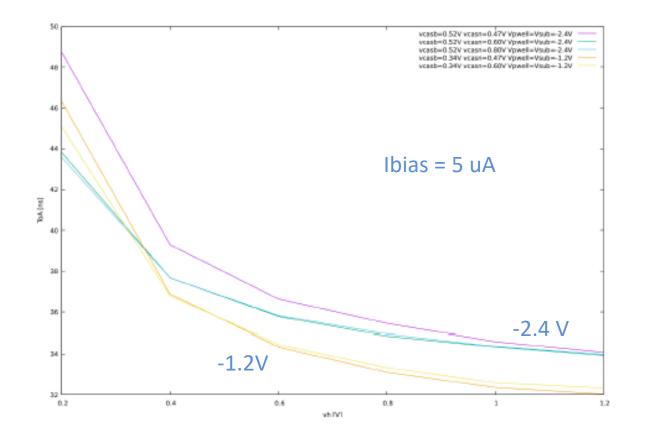

# Time of Arrival

#### Work in progress

Measurements: E. Buschmann et al.

- Influence of reverse substrate bias: higher TOA at -2.4 V compared to -1.2 V (due to slow down of digital circuit), but for correct operating point better slope

- Timing around 1 ns, limited more by the front end than the sensor.

# Analysis in progress, here for -1.2 V, -2.4 V to be done

Work in progress, different delay from pixels in odd and even rows here

EP

R&D

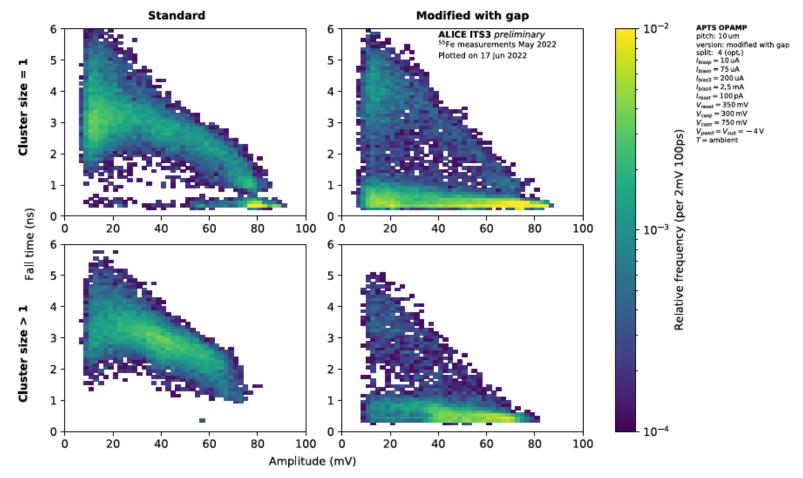

## Analog pixel test structure, faster circuit

- Clusters of different sizes show distinct fall time and amplitude distributions

- Nice demonstration of the change in charge collection

- Test beam is underway to measure the timing performance

Acceleration of charge collection evident, detailed analysis ongoing, measurements by ALICE/INFN Torino

R&D

EP

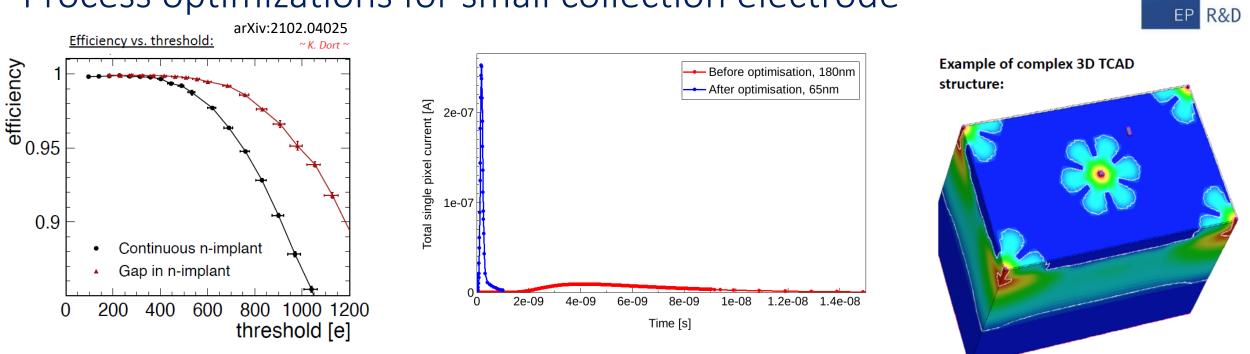

## Process optimizations for small collection electrode

- Efficiency improvement is not only simulated but also measured, even before irradiation (see top left: efficient operating window is almost doubled)

- The optimization over different pixel pitches and flavors, and technologies has improved the timing by several orders of magnitude. Simulations of even more complex structures bring peak-to-peak variations in the order of 50 ps at the moment

- These techniques have now been applied to several chips, and technologies and are generally applicable.

See M. Muenker's CERN EP detector seminar

## **Concluding remarks**

Sensor radiation tolerance, precision timing and improved efficiency can be obtained from optimization for fast charge collection using techniques based on general principles applicable to different technologies.

~ 150 ps on small collection electrode demonstrated in 180nm

Expect better on 65 nm with present process and sensor modifications, analysis in progress.

Decreasing technology feature size or special imaging sensor features can increase the voltage excursion on a small collection electrode and ultimately reduce analog front end power to zero and allow precision timing.

## **Concluding remarks**

Sensor radiation tolerance, precision timing and improved efficiency can be obtained from optimization for fast charge collection using techniques based on general principles applicable to different technologies.

~ 150 ps on small collection electrode demonstrated in 180nm

Expect better on 65 nm with present process and sensor modifications, analysis in progress.

Decreasing technology feature size or special imaging sensor features can increase the voltage excursion on a small collection electrode and ultimately reduce analog front end power to zero and allow precision timing.

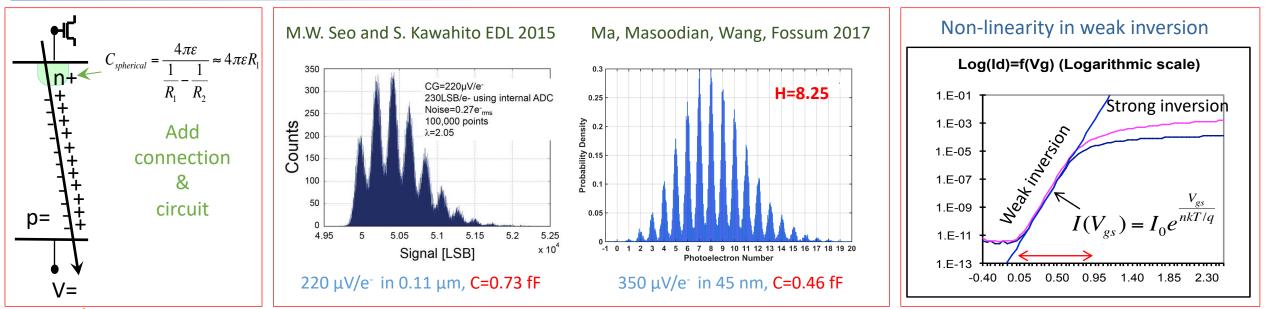

## Analog power consumption ~ $(Q/C)^{-2}$ (NIM A 731 (2013) 125)

- Q/C several 10's of mV in 180 nm

- "Conventional" approach

- ITS3 estimate ~ 10-15 nW front end for about 10 mW/cm<sup>2</sup> (ALPIDE in 180nm ~ 40 nW), 5x area reduction

- Increase power and speed for better timing,  $\mu$ W for < 1 ns

- Reduce capacitance further, using:

- tricks from imaging technology, at present not yet explored?

- now very conventional nwell collection electrode...

- Still need to extract signal charge from underneath the readout circuit !

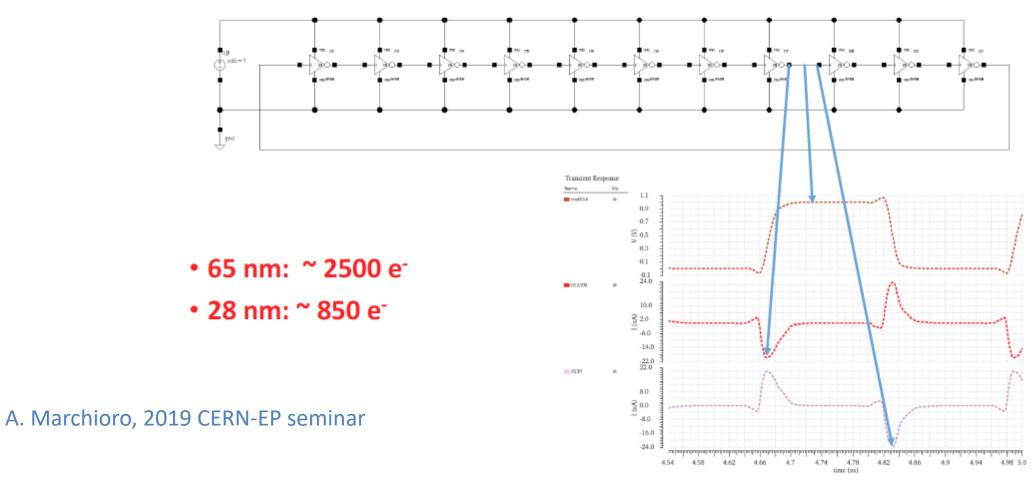

- deeper submicron: 2500 e- to switch inverter in 65 nm, 850 e- in 28 nm, 100 e- in 5 nm A. Marchioro 2019 CERN EP seminar

- Gain layers in the sensor

- Holy Grail: For Q/C > 400 mV, analog power consumption goes to zero.

### Analog power often dominant !

F. Piro

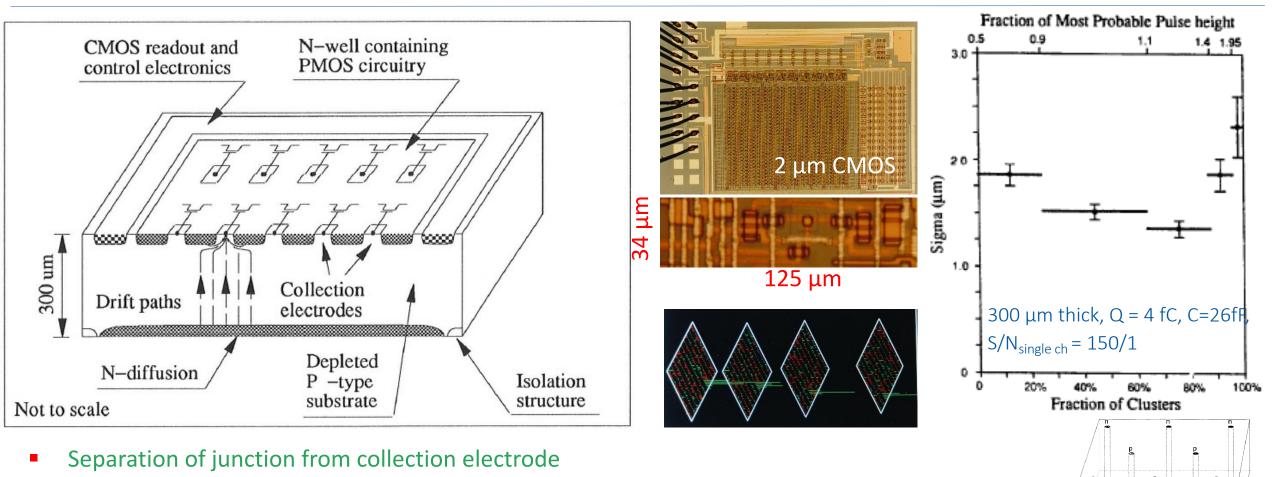

## Towards standard technology, but double-sided processing

- Better than 2 μm position resolution even at large pitch due to good S/N

- Improved back side isolation with trenches lead to sensors with 3D electrodes (S.Parker)

C. Kenney, S. Parker, J. Plummer, J. Segal, W. Snoeys et al. NIM A (1994) 258-265, IEEE TNS 41 (6) (1994), IEEE TNS 46 (4) (1999)

Other examples: ~ 1 μm resolution: SOI sensor, pitch 13.75 μm *M. Battaglia et al. NIM A 654 (2011) 258-265, NIM A 676 (2012) 50-53* Position resolution: good S/N for interpolation Junction separation and back side processing: see below

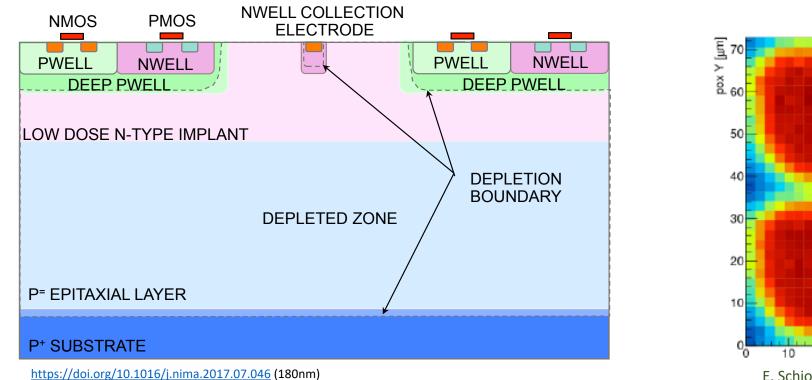

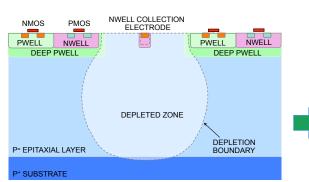

## Sensor optimization: Moving the junction away from the collection electrode

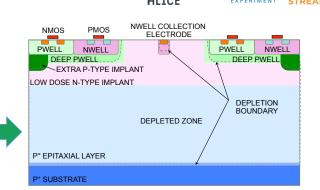

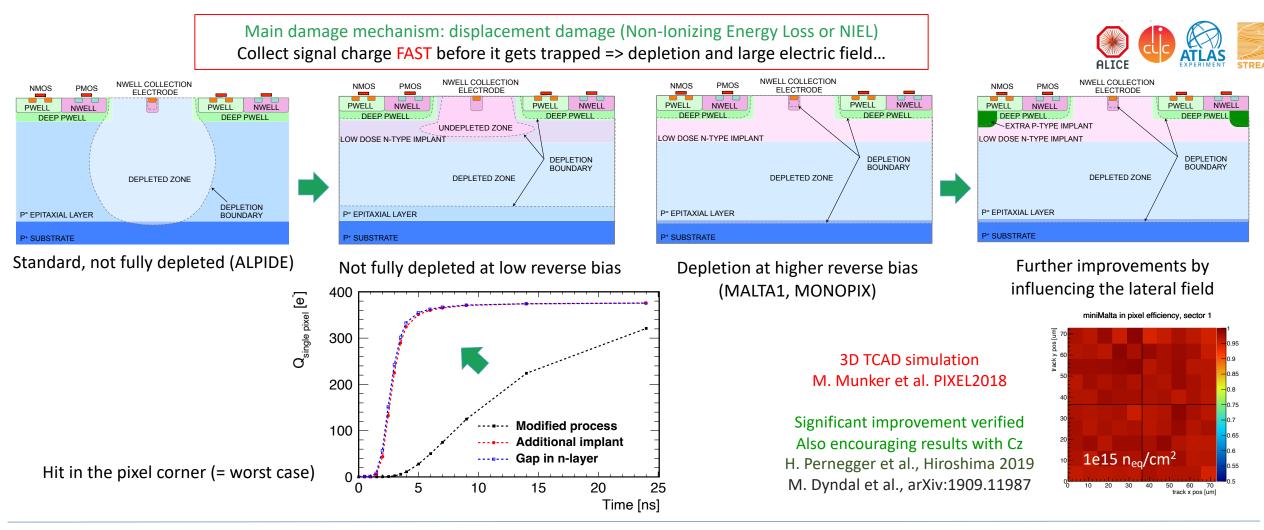

Main damage mechanism: displacement damage (Non-Ionizing Energy Loss or NIEL) Collect signal charge FAST before it gets trapped => depletion and large electric field...

for full depletion, better time resolution and radiation hardness... and better efficiency, especially for thin sensors

Standard, not fully depleted (ALPIDE)

Additional implant for full depletion => order of magnitude improvement Side development of ALICE for ALPIDE NIMA 871 (2017) pp. 90-96 Triggered development in ATLAS H. Pernegger et al, 2017 JINST 12 P06008

Not fully depleted at low reverse bias

after irradiation

NWELL COLLECTION PMOS NMOS ELECTRODE PWELL NWELL PWELL NWELL DEEP PWELL DEEP PWELL LOW DOSE N-TYPE IMPLANT DEPLETION BOUNDARY DEPLETED ZONE P<sup>=</sup> EPITAXIAL LAYER P<sup>+</sup> SUBSTRATE

Depletion at higher reverse bias (MALTA1, MONOPIX)

**3D TCAD simulation**

M. Munker et al. PIXEL2018

Significant improvement verified

Also encouraging results with Cz

H. Pernegger et al., Hiroshima 2019

M. Dyndal et al., arXiv:1909.11987

Further improvements by influencing the lateral field miniMalta in pixel efficiency, sector 1

Other similar developments for fast charge collection and depletion:

T.G. Etoh et al., Sensors 17(3) (2017) 483, https://doi.org/10.3390/s17030483 H. Kamehama et al., Sensors 18(1) (2017) 27, https://doi.org/10.3390/s18010027... L. Pancheri et al., PIXEL 2018, https://doi.org/10.3390/s18010027

C. Kenney et al. NIM A (1994) 258-265, IEEE TNS 41 (6) (1994), IEEE TNS 46 (4) (1999)

### Sensor optimization: Moving the junction away from the collection electrode

for full depletion, better time resolution and radiation hardness... and better efficiency, especially for thin sensors

Other similar developments for fast charge collection and depletion:

T.G. Etoh et al., Sensors 17(3) (2017) 483, <u>https://doi.org/10.3390/s17030483</u>

S. Kawahito et al., Sensors 18(1) (2017) 27, https://doi.org/10.3390/s18010027

L. Pancheri et al., PIXEL 2018, <u>https://doi.org/10.3390/s18010027</u>

05/09/2022 W. Snoeys

C. Kenney et al. NIM A (1994) 258-265, IEEE TNS 41 (6) (1994), IEEE TNS 46 (4) (1999)

## How many electrons are needed to switch a logic gate ?