# **Gain Layer fabrication**

For Picosecond Avalanche Detectors (PicoAD) implemented in Monolithic Active Pixel Sensors (MAPS)

Elviretti, Matteo

05.09.2022

IHP – Leibniz-Institut für innovative Mikroelektronik

| Agenda |  |

|--------|--|

|        |  |

| 1 Introduction | 1        |  |

|----------------|----------|--|

| 2 Processing   |          |  |

| 3 Experiments  | <u> </u> |  |

| 4 Conclusion   |          |  |

Т

# Introduction

#### Avalanche Diodes

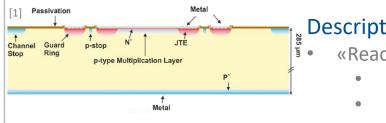

#### Description

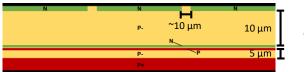

- «Reach-through» structure with p-type layer just below n+ electrode

- Multiplication layer underneath the pixel

- Lightly-doped absorption layer

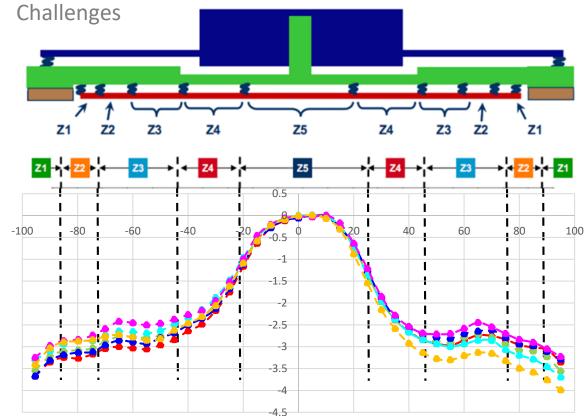

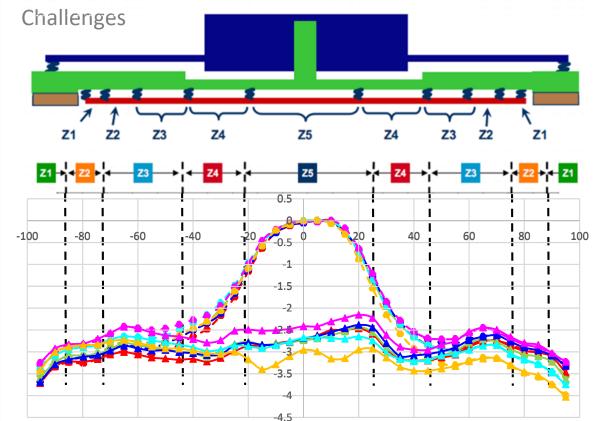

### Challenges

- 1. Strong variation of electric field at pixel edge

- Requirement of introducing discontinuities in multiplication layer

- 2. Charge-collection noise

- Intrinsic time jitter •

### **Solutions**

- 1. Increasing pixel size

- Thinning the avalanche diode 2.

# 1 Introduction

#### PicoAD

| [2] |    |    |

|-----|----|----|

| N   | N  | N  |

|     | P- |    |

|     | N  |    |

|     | P- | ~P |

|     | P+ |    |

|     |    |    |

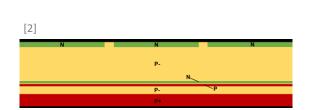

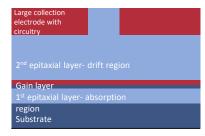

#### Description

•

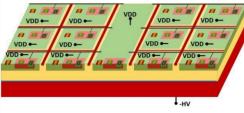

- Multi –junction monolithic silicon pixel detector

- (NP)<sub>pixel</sub>(NP)<sub>gain</sub> structure

- 1<sup>st</sup> epitaxial layer: Primary absorption region;

- Gain Layer: Uniform deep NP junction;

- 2<sup>nd</sup> epitaxial layer: Drift region

#### Advantages

- Gain layer far from the pixels

- Less subject to strong variation of the electric field

- Continuous gain layer

- It removes the inter-pixel zones of degraded time resolution

- Absorption region arbitrarily thin

- Reduces charge-collection noise

- Does not increase significantly pixel capacitance

05.09.2022

# 2.2 Processing

#### Current concept 2<sup>nd</sup> epitaxy 1<sup>st</sup> epitaxy on low ohmic Gain layer implantation SG13G2 IHP process substrate Large collection electrode with circuitry Gain laver Gain laver Substrate Substrate Substrate Substrate B and As implantation 3 to 5 µm epitaxy 15 to 25 µm epitaxy

#### **Challenges/issues:** Wafer flatness after 2<sup>nd</sup> epi might be not sufficient for litho processes of 130nm CMOS Non-negligible risk of introducing defects on the surface of the thicker epitaxial drift layer Time consuming when done with IHP dichlorsilane-based process at 850°C

#### 05.09.2022

Substrate

#### IHP contribution

1<sup>st</sup> and 2<sup>nd</sup> epitaxies (low T tool at IHP) Gain layer implantation SG13G2 BiCMOS process 50 μm epi layer (Globitech) Pre-process polishing SG13G2 BiCMOS process 1<sup>st</sup> and 2<sup>nd</sup> epitaxies (Globitech) Masked gain layer implantation SG13G2 BiCMOS process (yet to be started)

6

-HV

#### ATTRACT MONPicoAD

| N | N  | N |

|---|----|---|

|   | P- |   |

|   | N_ |   |

|   | P- | P |

|   | P+ |   |

#### Structure

- Heavily p-doped substrate (0.1 Ωcm)

- 5 μm thick epitaxial layer (absorption region)

- Masked gain Layer (with litho marks)

- 10 μm epitaxial layer (drift region)

- IHP 130 nm SiGe BiCMOS front-end electronics and pixels

- Metallization

#### ATTRACT MONPicoAD: Epitaxies

### Dichlorsilane-based epitaxy:

- 1<sup>st</sup> epitaxy on a low resistivity B-doped substrate

- 5 μm B-doped (3x10<sup>14</sup> cm<sup>-3</sup>) layer

## • 2<sup>nd</sup> epitaxy after gain layer implantations

10 μm B-doped (3x10<sup>14</sup> cm<sup>-3</sup>) layer

#### ATTRACT MONPicoAD: Epitaxies

#### Disadvantages:

- Time consuming

- Risk of introducing defects

#### ATTRACT MONPicoAD: Epitaxies

#### Disadvantages:

- Time consuming

- Risk of introducing defects

**3.1 Experiments**

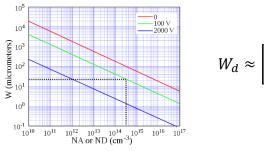

#### ATTRACT MONPicoAD: Gain Layer

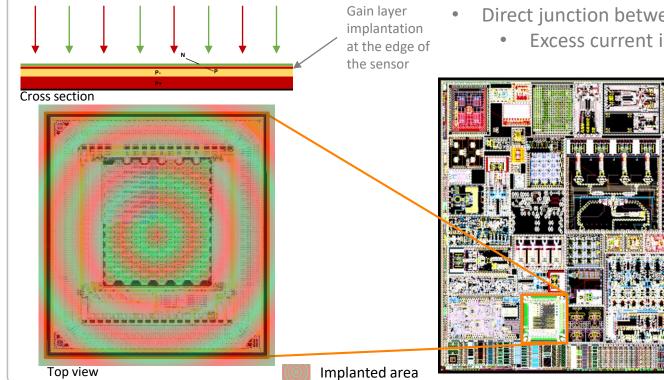

#### Challenges

- Direct junction between drift and gain region

- Excess current in device may be produced

www.ihp-microelectronics.com | © IHP all rights reserved

11

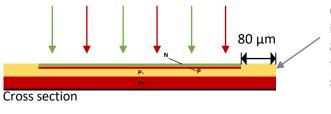

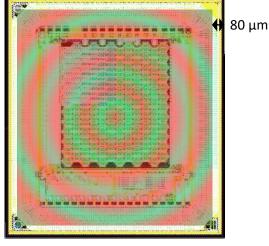

#### ATTRACT MONPicoAD: Gain Layer

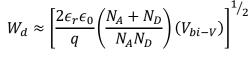

Gain layer implantation 80 µm far from edge of sensor

#### Challenges

- Direct junction between drift and gain region

- Excess current in device may be produced

#### Solution

- A mask is used for implantation

- Gain layer ends 80  $\mu$ m far from chip edge

- Dedicated litho marks processed after 1<sup>st</sup> epi

#### Top view

Implanted area

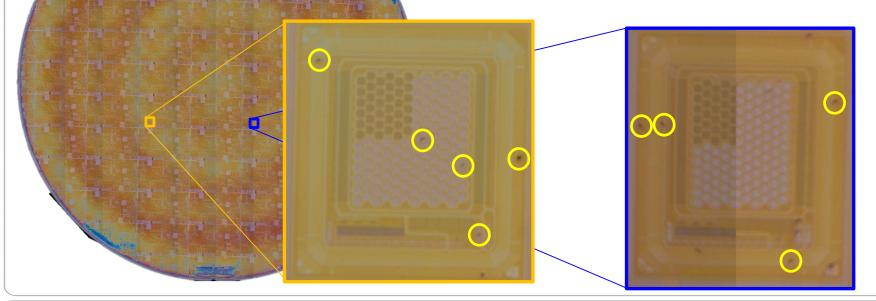

#### FASER monolithic pixel sensor

#### Structure

• Heavily p-doped substrate

- ~46  $\mu$ m thick epitaxial layer ( $\rho$ =200÷500  $\Omega$ cm)

- ~4  $\mu$ m thick epitaxial layer ( $\rho$ =15÷25  $\Omega$ cm)

Epi2 P/Boron/Res 16.44-24.54/Thk 3.57-3.92

Epi1 P/Boron/Res 286.99-430.25/Thk 43.94-48.55

Sub: 200mm/<100>/P/Boron/Res 0.7-1.1/Thk 660-690

- Front-end electronics and pixels

- Metallization

#### Challenges

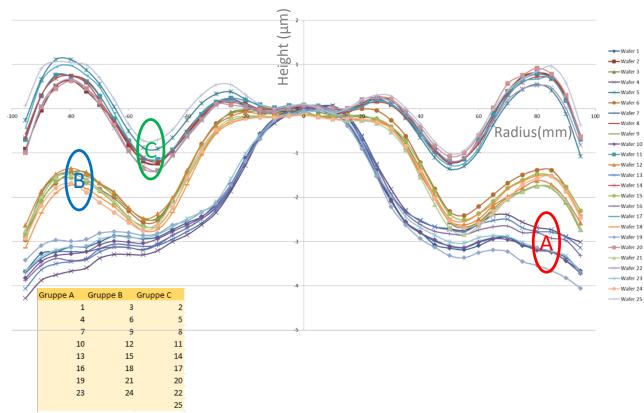

#### **Global Wafer flatness**

.....

- measured through autofocus feature of Nikon litho tool

- 3 profile groups individuated

- 3 AMAT Centura epi reactor chambers

- Not sufficient for litho processes of 130nm CMOS

#### **Chemical Mechanical Polishing**

- Mirra Mesa from AMAT

- 5 different pressure zones

- Proper recipes for each zone

#### Outcome

PCM Measurements in spec

#### Solution

- Better epi homogeneity

- wafer-to-wafer

- only one chamber

- across-wafer

- Thinner epi layer

16

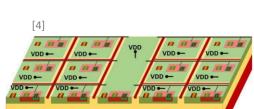

#### PicoAD sensor

#### Structure

- Heavily p-doped substrate

- 3÷5 μm thick epitaxial layer (absorption region)

- Masked gain Layer (no litho marks)

- 15÷25 μm epitaxial layer (drift region)

- IHP 130 nm SiGe BiCMOS front-end electronics and pixels

- Metallization

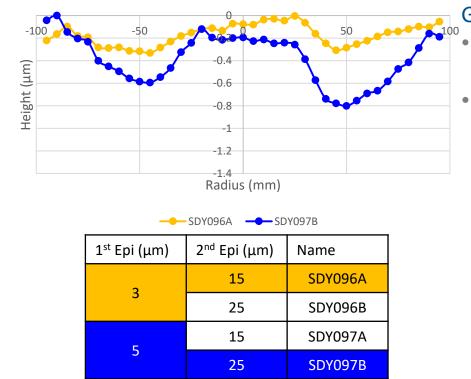

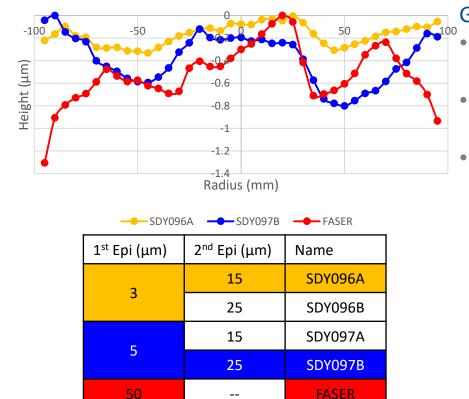

#### PicoAD sensor: Epitaxies

### Global Wafer Flatness

- Thinnest epitaxies (1<sup>st</sup>=3µm; 2<sup>nd</sup>=15µm)

- Most critical slope of 18.2 nm/mm

- Thickest epitaxies (1<sup>st</sup>=5µm; 2<sup>nd</sup>=25µm)

- Most critical slope of 49.6 nm/mm

#### PicoAD sensor: Epitaxies

### Global Wafer Flatness

- Thinnest epitaxies (1<sup>st</sup>=3µm; 2<sup>nd</sup>=15µm)

- Most critical slope of 18.2 nm/mm

- Thickest epitaxies (1<sup>st</sup>=5µm; 2<sup>nd</sup>=25µm)

- Most critical slope of 49.6 nm/mm

- FASER succesfully processed wafer

- Most critical slope of 65.9 nm/mm

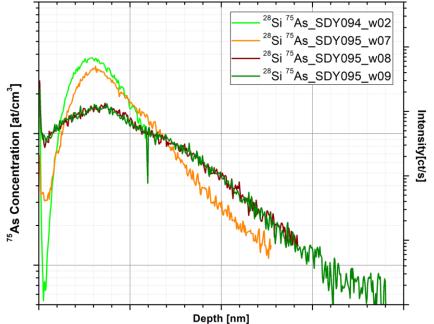

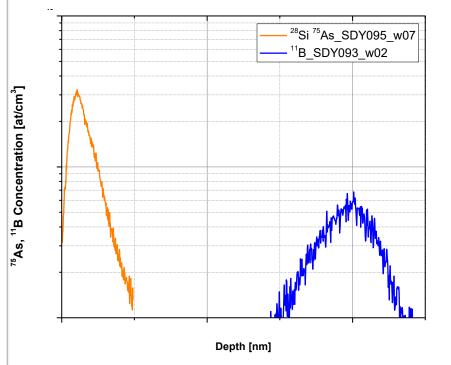

#### PicoAD sensor: Gain Layer

#### Constraints

- As surface concentration

- Upper limit

- Globitech requirement (reactor chamber contamination)

- Lowest possible

- To minimize outdiffusion

#### PicoAD sensor: Gain Layer

### Constraints

- As surface concentration

- Upper limit

- Globitech requirement (reactor chamber contamination)

- Lowest possible

- To minimize outdiffusion

- Upper limit in energy for the B implantation

#### PicoAD sensor: Gain Layer

#### 15um 2nd epi:

| Thickness 2nd epi | Thickness 1st epi | As gain layer doses | name  | Lot    | Slots (as processed) | Zeilen   |

|-------------------|-------------------|---------------------|-------|--------|----------------------|----------|

|                   |                   | 3                   |       | SDY096 | W01-06               | 1,4,7,10 |

| 15um (25 w)       | 3um (12 w)        | 3.5                 |       |        |                      | 2,5,8,11 |

|                   |                   | 4                   | (6 w) |        |                      | 3,6,9    |

|                   |                   | 2.5                 |       |        | W07-12               | 1,4,7,10 |

|                   |                   | 2.5                 |       |        |                      | 2,5,8,11 |

|                   |                   | 4.5                 | (6 w) |        |                      | 3,6,9    |

|                   |                   | 3                   |       | SDY097 | W01-07               | 1,4,7,10 |

|                   | 5um (13 w)        | 3.5                 |       |        |                      | 2,5,8,11 |

|                   |                   | 4                   | (7 w) |        |                      | 3,6,9    |

|                   |                   | 2.5                 |       |        | W08-13               | 1,4,7,10 |

|                   |                   | 2.5                 |       |        |                      | 2,5,8,11 |

|                   |                   | 4.5                 | (6 w) |        |                      | 3,6,9    |

25um 2nd epi: Thickness 1st epi As gain layer doses name Thickness 2nd epi Lot Wafers Zeilen Δ SDY096 W13-18 1,4,7,10 2,5,8,11 25um (24 w) 3um (12 w) 4.5 5 (6 w) 3,6,9 3.5 W19-24 1,4,7,10 3.5 2,5,8,11 4.75 (6 w) 3.6.9 Δ SDY097 W14-19 1,4,7,10 5um (12 w) 5 2,5,8,11 5 (6 w) 3,6,9 3.5 W20-25 1,4,7,10 3.5 2,5,8,11 4.75 (6 w) 3,6,9

#### 49 Wafers

- 25 wafers -> 15 μm 2<sup>nd</sup> epi

- 12 wafers -> 3 μm 1<sup>st</sup> epi

- 13 wafers -> 5 μm 1<sup>st</sup> epi

- 3 gain layer variants each wafer

- 24 wafers -> 25 μm 2<sup>nd</sup> epi

- 12 wafers -> 3 μm 1<sup>st</sup> epi

- 12 wafers -> 5 μm 1<sup>st</sup> epi

- 3 gain layer variants each wafer

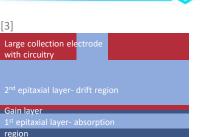

Functional chips delivered Very promising results [2, 5]

Manually controlled CMP needed Measurements ongoing Currently tested in a particle beam μm

-HV

[4]

Functional chips delivered

up to 25 µm Alignment accuracy limited to ~100 BiCMOS process yet to be started

23

Globitech epitaxy can be exploited

#### region

MONOLIT

Large collection electrode

Substrate

05.09.2022

Gain layer

with circuitry

[2]

# Thank you for your attention!

Elviretti, Matteo

IHP – Leibniz-Institut für innovative Mikroelektronik Im Technologiepark 25 D – 15236 Frankfurt (Oder) Phone: +49 (0) 335 5625 346 Fax: +49 (0) 335 5625 e-mail: elviretti@ihp-microelectronics.com

www.ihp-microelectronics.com

# **Bibliography**

[1] – Carulla, M., et al. "50µm thin Low Gain Avalanche Detectors (LGAD) for timing applications." Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment 924 (2019): 373-379.

[2] – Paolozzi, L., et al. "Picosecond Avalanche Detector--working principle and gain measurement with a proof-of-concept prototype." arXiv preprint arXiv:2206.07952 (2022).

[3] – Münker, M. on behalf of the MONOLITH team «Picosecond time stamping in fully monolithic highly granular silicon pixel detectors" – TRENTO workshop, March 2022

[4] – Paolozzi, Lorenzo, Giuseppe Iacobucci, and Pierpaolo Valerio. "Fast pixel sensors for ionizing particles integrated in SiGe BiCMOS." 2020 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS). IEEE, 2020.

[5] – Iacobucci, G., et al. "Efficiency and time resolution of monolithic silicon pixel detectors in SiGe BiCMOS technology." Journal of Instrumentation 17.02 (2022): P02019.