#### **Trigger Electronics & Data Acquisition**

#### **Sridhara Dasu**

Original slides & graphics "stolen" from: Wesley Smith, Sergio Cittolin, Tom Gorski, Ales Svetek, Maria Cepeda, Sascha Savin, Varun Sharma, Piyush Kumar, Pallabi Das, Isobel Ojalvo, Kevin Stenson, Phil Harris, ...

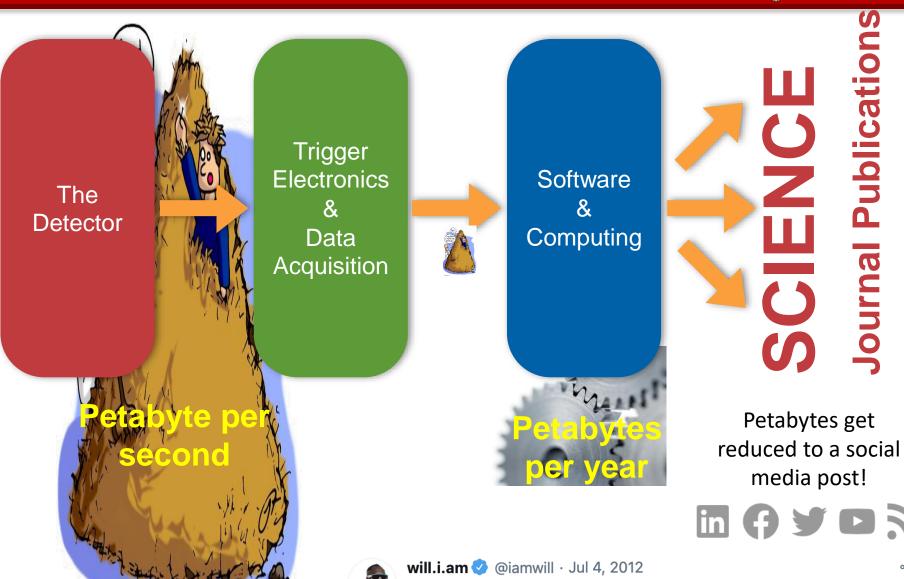

### The Scientific Process

2

Happy 4th of july to all americans...& happy "god particle" day to science

enthusiast...congrats to all the scientist at cern...#willpower

www.jolyon.co.uk

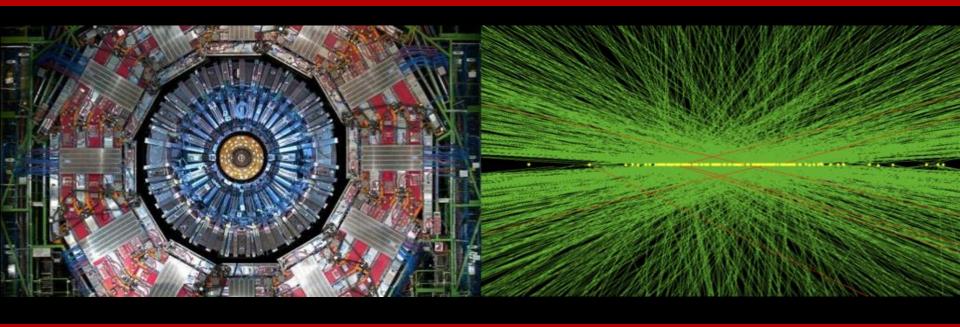

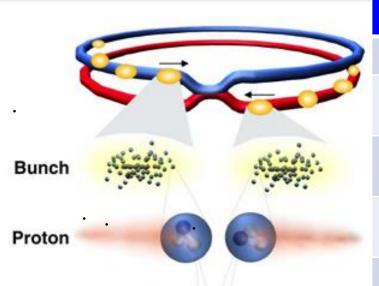

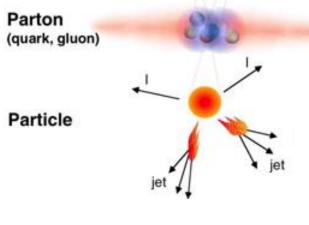

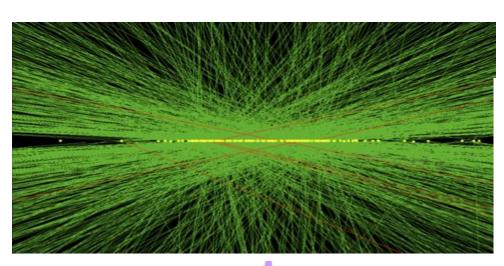

### Proton-Proton Collisions at the LHC

|                            | Run-2                | Run-1                |

|----------------------------|----------------------|----------------------|

| Beam energy                | 6.5 TeV              | 4.0 TeV              |

| Bunches/<br>beam           | 2556                 | 1380                 |

| Protons/<br>bunch          | 2.5x10 <sup>11</sup> | 2.2x10 <sup>11</sup> |

| N pp Collisions<br>Created | ~10 <sup>16</sup>    | $3.5 \times 10^{14}$ |

| N Higgs Events             | ~104                 | ~few 10 <sup>2</sup> |

Fetch me my needle buried in those hay stacks -And, do it As Soon As Possible

1 event in 10 000 000 000 000 !

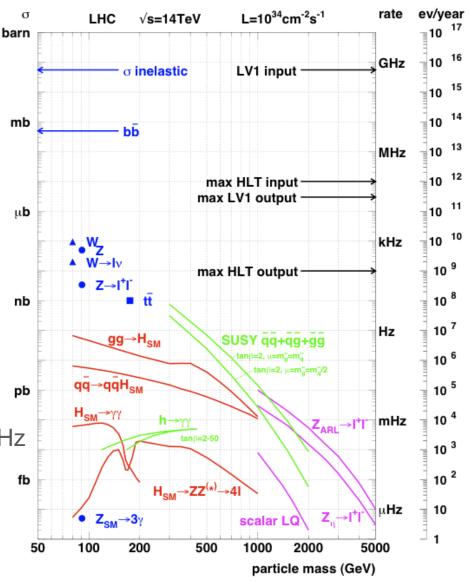

# LHC Physics & Event Rates

#### $L = 2 \times 10^{34} \text{cm}^{-2} \text{s}^{-1}$

- 50 pp events/25 ns crossing

- ~ 1 GHz input rate

- "Good" events contain50 background overlap

- 1 kHz W events

- 10 Hz top events

- < 10<sup>4</sup> detectable Higgs/year

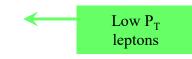

### Can store ~ 1000 Hz events Select in stages

- Level-1 Triggers

- 1 GHz (pp-interactions) to 100 kHz

- High Level Triggers

- 100 kHz to 1000 Hz

2023-03-10 LISHEP 2023, Rio

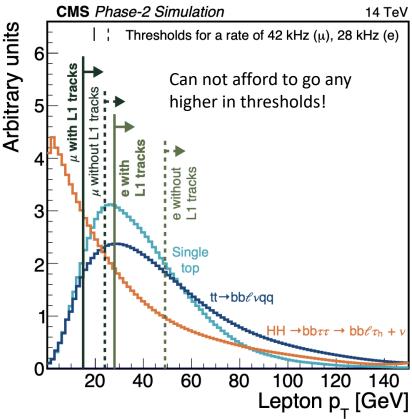

### (HL) LHC Physics – Trigger Challenge

#### **Electroweak Symmetry Breaking Scale**

Low  $\cong 30 \text{ GeV}$ Low  $P_T \gamma$ , e,  $\mu$

- Higgs (125 GeV) studies and higgs sector characterization

- Quark, lepton Yukawa couplings to higgs

— Low P<sub>T</sub> B, τ jets

#### New physics at TeV scale to stabilize higgs sector

- Spectroscopy of new EWK produced resonances (SUSY or otherwise)

Multiple low P<sub>T</sub> objects

- Find dark matter candidate

Missing E<sub>T</sub>

#### Multi-TeV scale physics (loop effects)

- Indirect effects on flavor physics (mixing, FCNC, etc.)

- B<sub>s</sub> mixing and rare B decays

~ Dedicated triggers (CMS) or experiment (LHCB)

- Lepton flavor violation

- Rare Z and higgs decays

#### Planck scale physics

- Large extra dimensions to bring it closer to experiment

- New heavy bosons

- Blackhole production

High P<sub>T</sub> leptons and photons

Multi particle and jet events

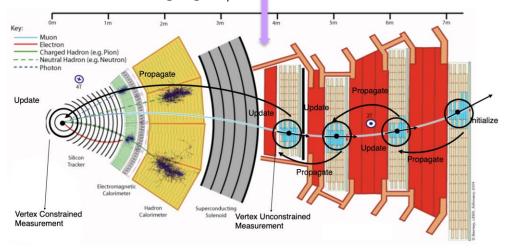

# LHC Data Processing to Trigger

# Level 1 Trigger Data

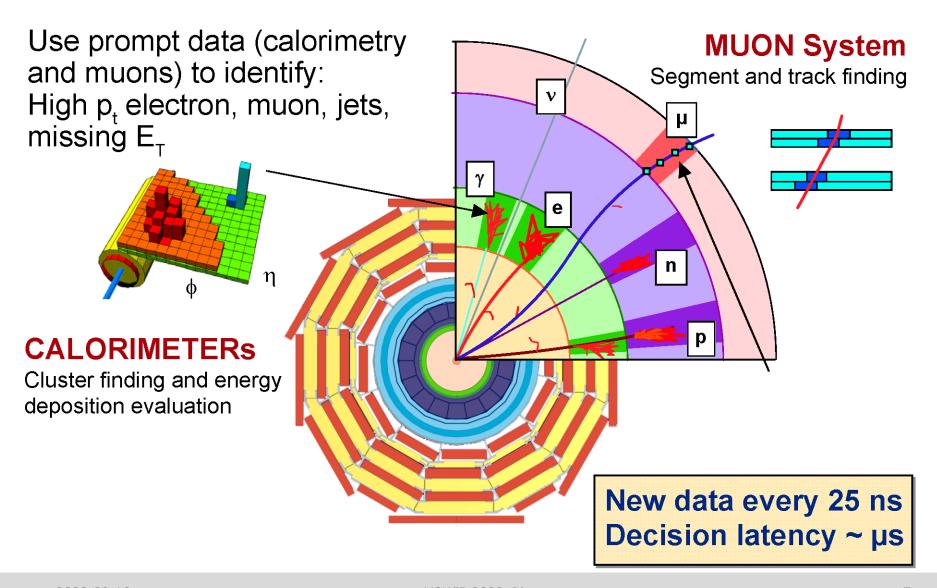

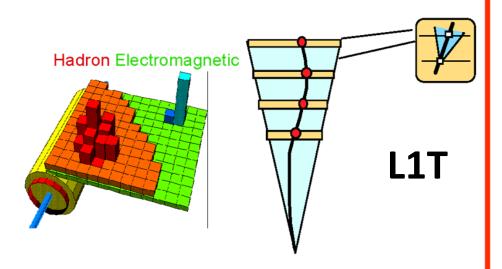

### L1 @ LHC: Only Calorimeter & Muon - wusconsin

### HLT@LHC: Key additional feature - Tracker

New tracker and level-1 track trigger envisioned for HL-LHC

Pattern recognition much faster/easier

Simple Algorithms

Reduced amounts of data

Compare to tracker info HLT Complex **Algorithms** Huge amounts of

data

# Xilinx Field Programmable Gate Arrays wusconsin

### Xilinx FPGAs – Phase-1 Choice: V7 690T

Xilinx Multi-Node Product Portfolio Offering Currently

Deployed

45nm 28n

28nm

**20nm**

HL-LHC Prototypes

16nm

| Spartan-7 | Spartan-6 |

|-----------|-----------|

| Artix-7   | Zynq-7000 |

| Spartan-7 | Artix-7  |

|-----------|----------|

| Kintex-7  | Virtex-7 |

| Kintex UltraScale | Virtex UltraScale |

|-------------------|-------------------|

|                   |                   |

Kintex UltraScale+ Virtex UltraScale+

|                              | Spartan-7 | Artix-7 | Kintex-7 | Virtex-7 |

|------------------------------|-----------|---------|----------|----------|

| Max Logic Cells (K)          | 102       | 215     | 478      | 1,955    |

| Max Memory (Mb)              | 4.2       | 13      | 34       | 68       |

| Max DSP Slices               | 160       | 740     | 1,920    | 3,600    |

| Max Transceiver Speed (Gb/s) |           | 6.6     | 12.5     | 28.05    |

| Max I/O Pins                 | 400       | 500     | 500      | 1,200    |

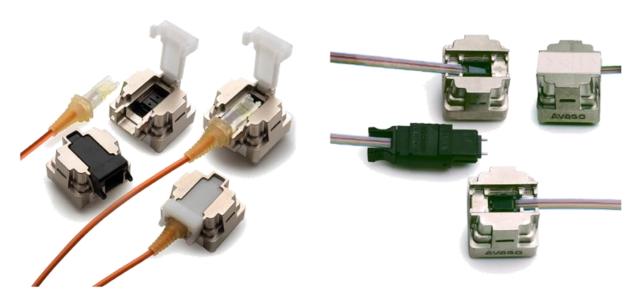

### Key element - Multi-gigabit Opto-electronics

Figure 1. MiniPOD™ Transmitter and Receiver Modules with a) Round Cable and b) Flat Cable: shown with and without dust covers (White = Tx, Black = Rx).

Figure 2. MiniPOD™ Transmitter and Receiver flat ribbon cable modules in a tiled arrangement example.

#### **Key Product Parameters**

The Avago Technologies MiniPOD™ modules operate at 850 nm and are compliant to the Multi-mode Fiber optical specs in clause 86 and relevant electrical specs in annex 86A of the IEEE 802.3ba specifications.

| Parameter                   | Value      | Units  | Notes                                                                                         |

|-----------------------------|------------|--------|-----------------------------------------------------------------------------------------------|

| Data rate per lane          | 10.3125    | Gbps   | As per 802.3ba: 100GBASE-SR10 and nPPI specifications                                         |

| Number of operational lanes | 12         |        | 100GbE operation utilizes the middle ten lanes (Rx and Tx) of the 12 physically defined lanes |

| Link Length                 | 100<br>150 | m<br>m | OM3, 2000 MHzMHz•km 50 μm MMF<br>OM4, 4700 MHz•km 50 μm MMF                                   |

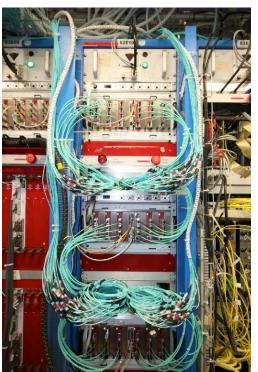

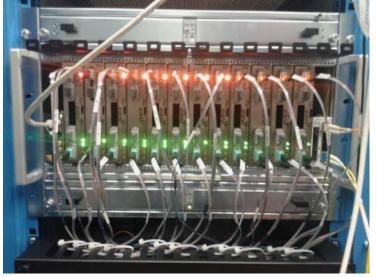

### CMS Calorimeter Trigger Run-2

- Installed and commissioned in 2015, fully operational in 2016

- Connections to CTP7 from Layer-1 patch panels completed in 2015

- Connections from Layer-1 to Layer-2 via compact patch panel

- 3 "pizza box" sized patch panels instead of full 56U rack with LC connectors

- Layer 2 to demux to new μGT connected

Layer-1 CTP7

Layer-1 to Layer-2 Patch Panel

Layer-2 MP7

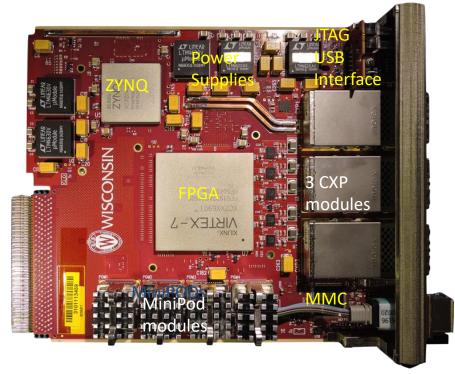

### Level-1 Calorimeter Trigger Electronics www.sconsin

Calorimeter Trigger Processor(CTP7 – left), and Master Processor (MP7 - right)

- CTP7 (Layer-1) μTCA Single Virtex 7 FPGA, 67 optical inputs, 48 outputs, 12 RX/TX backplane

- Virtex 7 allows 10 Gb/s link speed on 3 CXP(36 TX & 36 RX) and 4 MiniPODs (31 RX & 12 TX)

- ZYNQ processor running Xilinx PetaLinux for service tasks, including virtual JTAG cable

- MP7 (Layer-2) μTCA Single Virtex 7 FPGA, up to 72 input & output links

- Virtex 7 has 72 input and output links at 10 Gb/s

- Dual 72 or 144MB QDR RAM clocked at 500 MHz

2023-03-10 13 LISHEP 2023, Rio

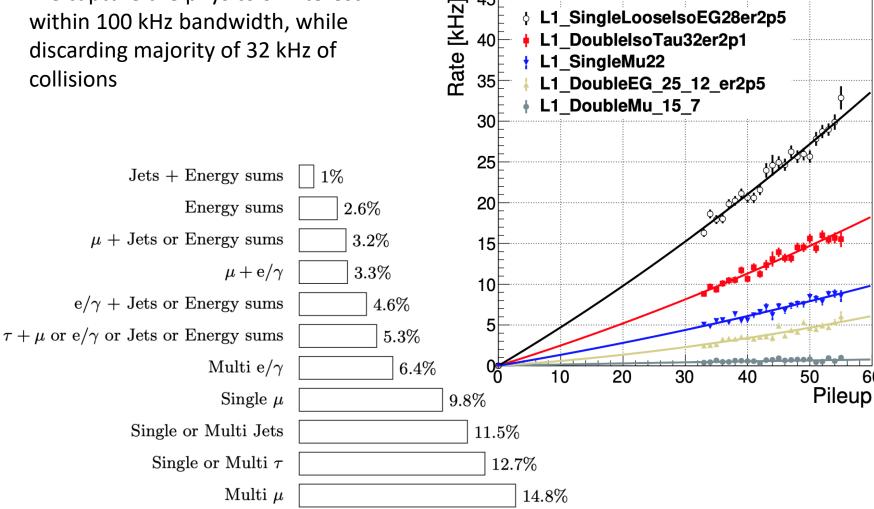

# L1 Trigger Summary from Run-2,3

(13 TeV)

60

We capture the physics of interest within 100 kHz bandwidth, while discarding majority of 32 kHz of collisions

Single  $e/\gamma$

45 CMS

L1 SingleLooselsoEG28er2p5

24.8%

L1 DoublelsoTau32er2p1

L1 SingleMu22

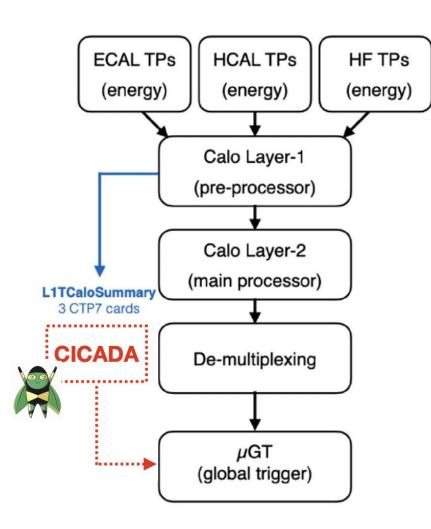

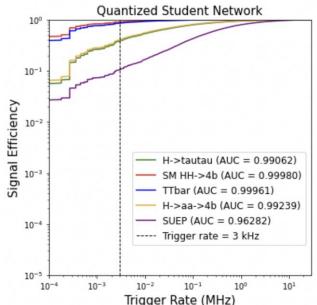

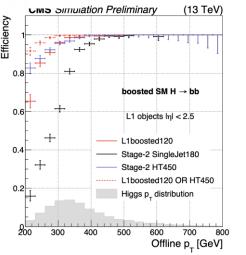

# CICADA – Machine Learning in L1T WWISCONSIN

Unsupervised learning "Anomaly Detection"

Ho-Fung Tsoi

Also includes new (but traditional) boosted object algorithm

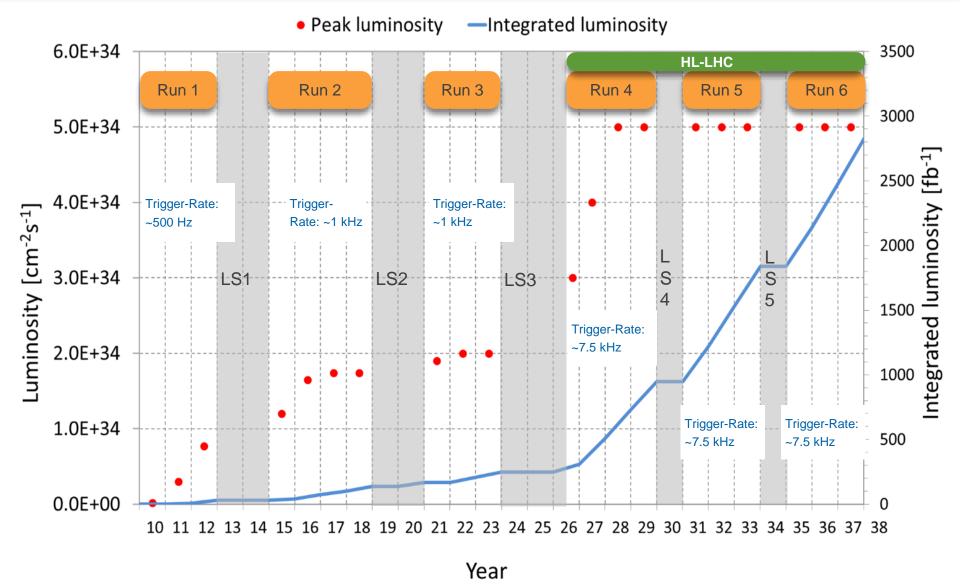

# LHC Now - HL-LHC in the Future wisconsin with the status of the status o

CMS will be on path to exabytes of data acquired in the HL-LHC era

# **HLLHC Parameters**

| Parameter                                         | Nominal LHC         | HL-LHC         | HL-LHC            | HL-LHC |

|---------------------------------------------------|---------------------|----------------|-------------------|--------|

|                                                   | Design              | 25 ns          | 25 ns             |        |

|                                                   | Report              | standard       | BCMS              | 8b4e   |

| Beam energy in collision [TeV]                    | 7                   | 7              | 7                 | 7      |

| $N_b[10^{11}]$                                    | 1.15                | 2.2            | 2.2               | 2.3    |

| Number of bunches per beam                        | 2808                | 2748           | 2604              | 1968   |

| Beam current [A]                                  | 0.58                | 1.09           | 1.03              | 0.82   |

| Minimum $\beta^*$ [m]                             | 0.55                | 0.2            | 0.2               | 0.2    |

| $\epsilon_n [\mu m]$                              | 3.75                | 2.50           | 2.50              | 2.20   |

| $\epsilon_L$ [eVs]                                | 2.50                | 2.50           | 2.50              | 2.50   |

| Peak luminosity with crab cavities                | (1.18)              | 12.6           | 11.9              | 11.6   |

| $[10^{34} \text{cm}^{-2} \text{s}^{-1}]$          | Operating at 2x now |                |                   |        |

| Levelled luminosity for                           | -                   | 5.32           | 5.02              | 5.03   |

| $\mu = 140[10^{34} \text{cm}^{-2} \text{s}^{-1}]$ |                     | Expect Operati | ng at 7.5x ultima | itely  |

| (inelastic) collisions/crossing $\mu$             | 27                  | 140            | 140               | 140    |

| (with levelling and crab cavities)                |                     |                | μ=200             |        |

| Maximum line density of pileup                    | 0.21                | 1.3            | 1.3               | 1.3    |

| events during fill [events/mm]                    |                     |                |                   |        |

# Collisions (p-p) at HLLHC

Selecting high P<sub>⊤</sub> clusters and tracks

# Triggers → Physics

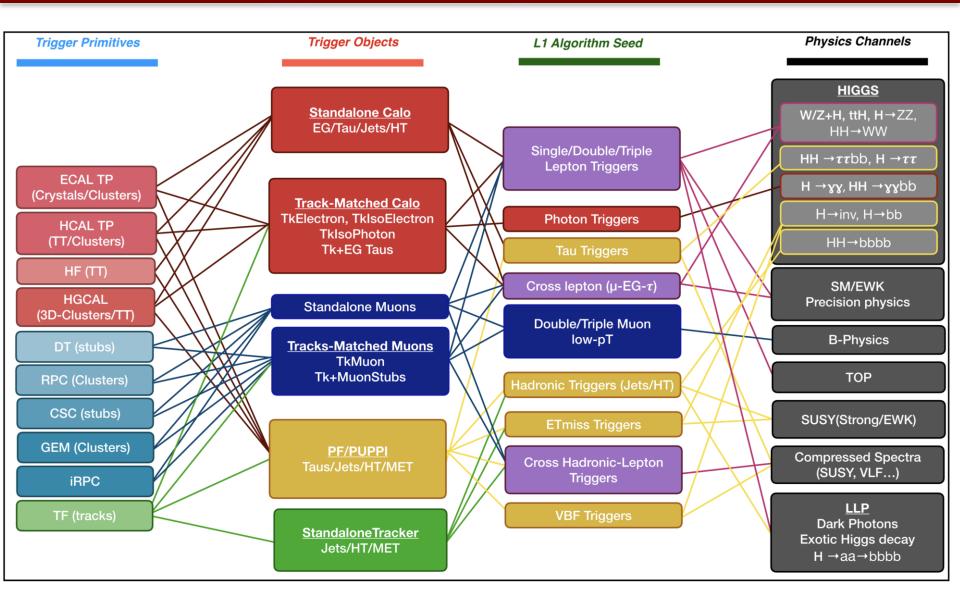

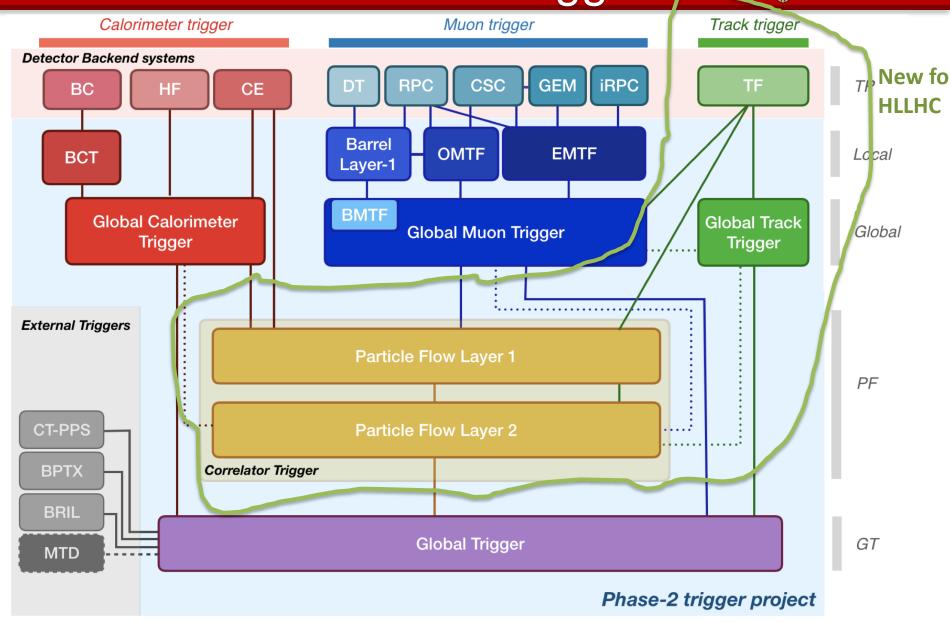

# CMS HLLHC Level-1 Trigger 2020 WISCONSIN UNIVERSITY OF WISCONSIN

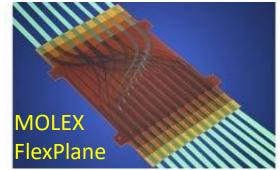

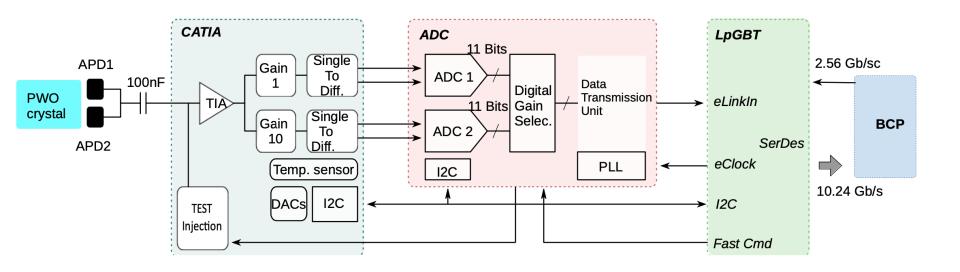

# Getting the crystal data out (New for HLLHC)

There are 61200 crystals to be processed – packing 25 crystals per link out of BCP you still have 2448 links at 16 Gbps to contend in the calorimeter trigger path!

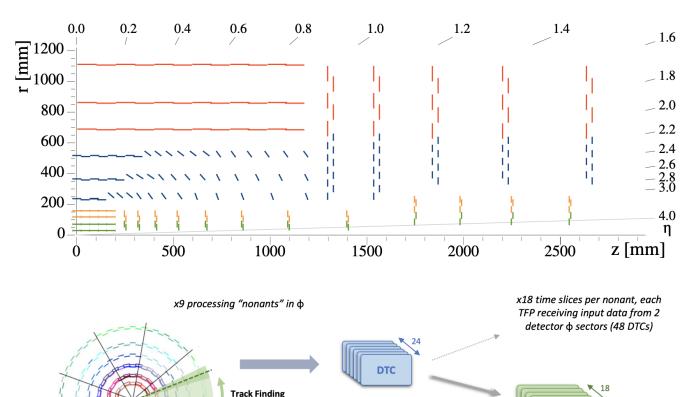

# Getting the tracks out (New for HLLHC)

DTC

DTC

**Data Trigger & Control**

nonant

Detector d sector

**Outer Tracker**

Outer tracker double layers allow track stub readout

Tracklets formed in TFP consistent with >2GeV P<sub>T</sub>. Tracks propagated in-out, matched to form track candidates

Tracklets are then fit <sup>22</sup> to make a track

**TFP**

**TFP**

**Track Finder Processor**

### HL-LHC L1 Trigger Challenge

### Xilinx – Ultrascale+ Processors

#### **Product Tables and Product Selection Guides**

| Max System Logic Cells (K)   |

|------------------------------|

| Max Memory (Mb)              |

| Max DSP Slices               |

| Max Transceiver Speed (Gb/s) |

| Max I/O Pins                 |

| Kintex UltraScale+ | Virtex UltraScale+         |  |  |

|--------------------|----------------------------|--|--|

| 1,143              | <sup>3,780</sup> Times 2   |  |  |

| 70.5               | 65,913 Many times          |  |  |

| 3,528              | 12,288 <b>Times 3</b>      |  |  |

| 32.75              | <sub>32.75</sub> Times 2.5 |  |  |

| 572                | 832                        |  |  |

# Multi-gigabit-per-second serial links wusconsin

|         |                       | Туре        | Max<br>Performance <sup>1</sup> | Max<br>Transceivers   | Peak<br>Bandwidth |                     |

|---------|-----------------------|-------------|---------------------------------|-----------------------|-------------------|---------------------|

|         | Virtex<br>UltraScale+ | GTY         | 32.75                           | 128                   | 8,384 Gb/s        | 111 1116            |

|         | Kintex<br>UltraScale+ | GTH/GTY     | 16.3/32.75                      | 44/32                 | 3,268 Gb/s        | HL-LHC<br>← 25 Gbps |

|         | Virtex<br>UltraScale  | GTH/GTY     | 16.3/30.5                       | 60/60                 | 5,616 Gb/s        | 23 0003             |

| LHC     | Kintex<br>UltraScale  | GTH         | 16.3                            | 64                    | 2,086 Gb/s        |                     |

|         | Virtex-7              | GTX/GTH/GTZ | 12.5/13.1/28.05                 | 56/96/16 <sup>3</sup> | 2,784 Gb/s        |                     |

| 10 Gbps | Kintex-7              | GTX         | 12.5                            | 32                    | 800 Gb/s          |                     |

|         | Artix-7               | GTP         | 6.6                             | 16                    | 211 Gb/s          |                     |

|         | Zynq<br>UltraScale+   | GTR/GTH/GTY | 6.0/16.3/32.75                  | 4/44/28               | 3,268 Gb/s        |                     |

|         | Zynq-7000             | GTX         | 12.5                            | 16                    | 400 Gb/s          |                     |

|         | Spartan-6             | GTP         | 3.2                             | 8                     | 51 Gb/s           |                     |

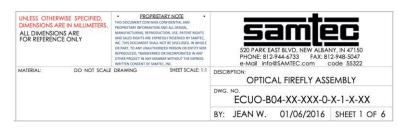

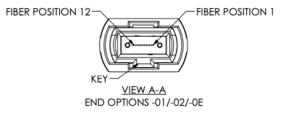

### Key element - Multi-gigabit

# **Opto-electronics**

#### **REVISION D**

DO NOT SCALE FROM THIS PRINT

**ESD SENSITIVE**

| TABLE 1: ASSEMBLY LENGTH LIMITS |                  |                                           |     |  |  |

|---------------------------------|------------------|-------------------------------------------|-----|--|--|

| FIBER TYPE                      | <b>HEAT SINK</b> | HEAT SINK MIN LENGTH (cm) MAX LENGTH (cm) |     |  |  |

| -4                              | ANY              | 16                                        | 999 |  |  |

|                                 | -1,-2,-4,-5      | 12                                        | 100 |  |  |

| -5                              | -3               | 12                                        | 48  |  |  |

| -6                              | -1,-2,-4,-5      | 9                                         | 100 |  |  |

| -0                              | -3               | 9                                         | 48  |  |  |

| TABLE 2: LENGTH TOLERANCE            |       |  |  |

|--------------------------------------|-------|--|--|

| ASSEMBLY LENGTH (cm) TOLERANCE (cm)* |       |  |  |

| 009-016                              | ±0.16 |  |  |

| 017-999                              | ±1%   |  |  |

|                                      |       |  |  |

\* ROUNDED UP TO 2 DECIMAL PLACES

#### ECUO-B04-XX-XXX-0-X-1-X-XX

DATA RATE

-14: 14 Gbps -25: 25.7 Gbps -28: 28.1 Gbps

ASSEMBLY LENGTH

-XXX: LENGTH (cm) SEE TABLES 1, 2

#### FIBER TYPE

-4: AQUA LOOSE TUBE WITH BOOT -5: BLACK JACKETED RIBBON WITH BOOT

-07: MXC® INTERNAL PLUG -0E: MPO PLUS® BAYONET MALE

**END OPTION**

-01: MTP® MALE

-02: MTP® FEMALE

-6: BLACK JACKETED RIBBON

**HEAT SINK** -1: FLAT

-2: PIN FIN

-3: FLAT WITH GROOVE (SEE NOTE 2)

-4: PCIe® PIN FIN (-14 DATA RATE ONLY)

-5: 1.75 cm TALL PÌN FIN (-25 & -28 DATÁ RATES ONLY)

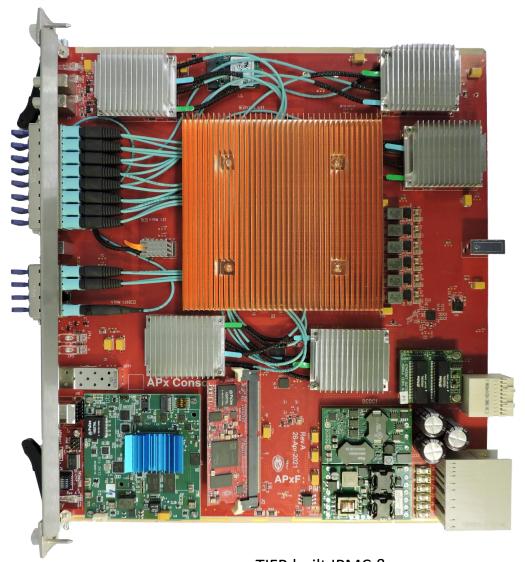

### Advanced Processor Prototype for HL-LHC

TIFR built IPMC & ESM mezzanines

Wisconsin APxF Board

Xilinx VU13P or VU9P FPGA

ZYNQ-IPMC

(ATCA IPMI controller)

ELM (ZYNQ-based

embedded Linux endpoint)

ESM (GbE switch)

High efficiency heatsinks

Front-panel inputs

25G Samtec Firefly positions loaded – 10x12 + 1x4 (124 25 Gbps links)

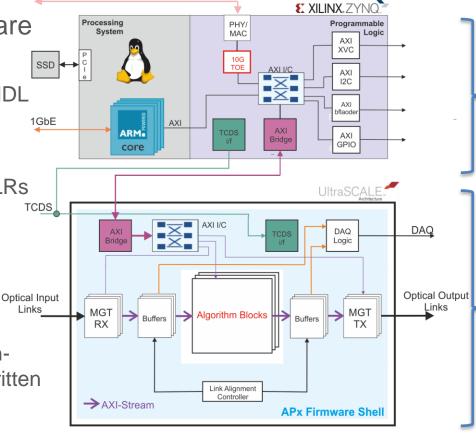

#### APx – Firmware/Software

10GbE

A new paradigm for firmware development

Core firmware written in VHDL by engineers

Gigabit link support

Data exchange between SLRs within chip

Test buffers

Clock and control

#### **Physics**

Algorithmic firmware in highlevel languages like C++ written by physicists

#### ELM:

Control endpoint, providing complete board overhead functionality

#### **Processing FPGA:**

- I/O

- data processor

- DAQ

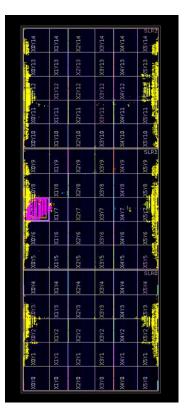

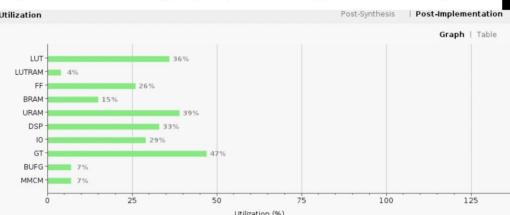

# **APx-FS** Resource Utilization

| tilization | VU9P build  | Post-Synthesis | Post-Implementation  |

|------------|-------------|----------------|----------------------|

|            |             |                | Graph   <b>Table</b> |

| Resource   | Utilization | Available      | Utilization %        |

| LUT        | 33309       | 1182240        | 2.82                 |

| LUTRAM     | 963         | 591840         | 0.16                 |

| FF         | 51563       | 2364480        | 2.18                 |

| BRAM       | 7           | 2160           | 0.32                 |

| 10         | 9           | 416            | 2.16                 |

| GT         | 102         | 104            | 98.08                |

| BUFG       | 236         | 1800           | 13.11                |

| MMCM       | 3           | 30             | 10.00                |

100x 25G GTY links w/ support infra

Central AXI infra with MGT-based Chip2chip core

APd1 VU9P FPGA floorplan

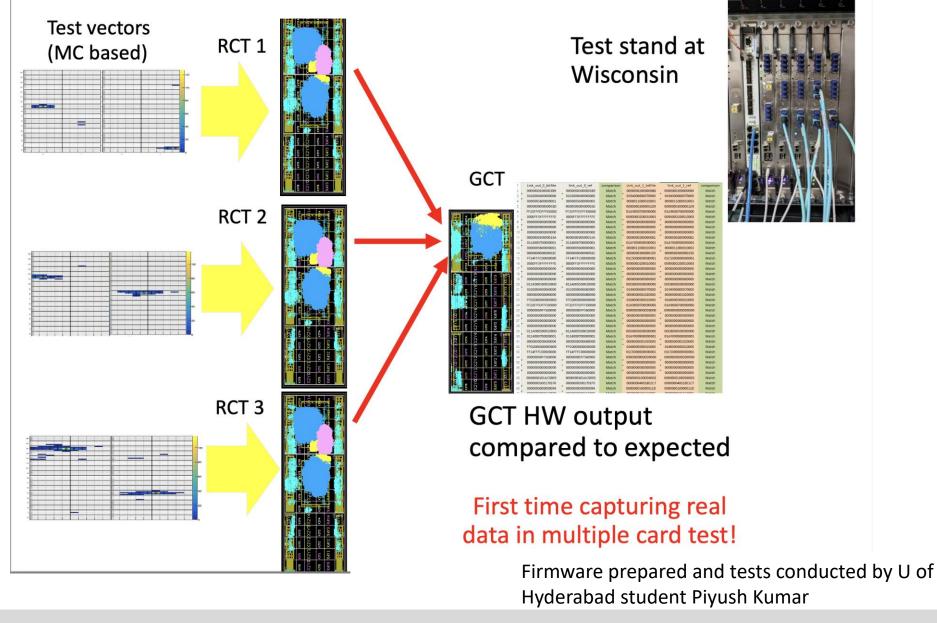

# Calorimeter Firmware Tests

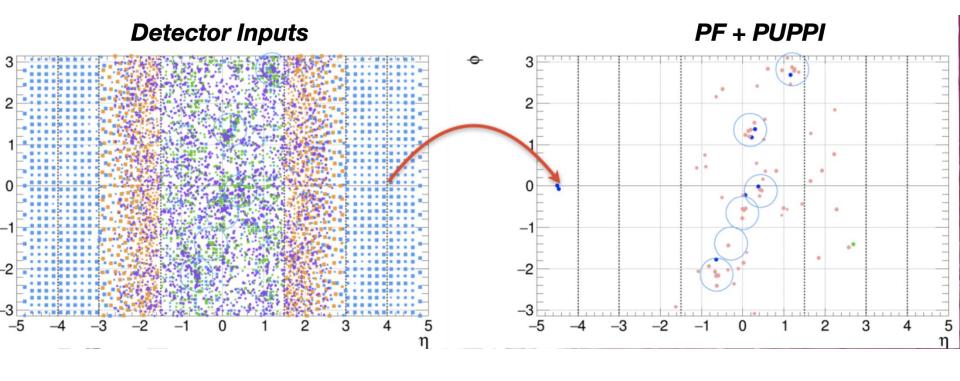

# Particle Flow Reconstruction on FPGAs www.sconsin

# Particle Flow Implementation

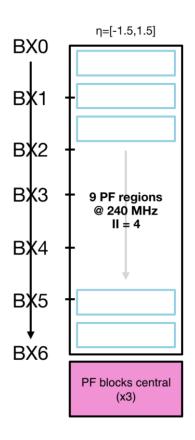

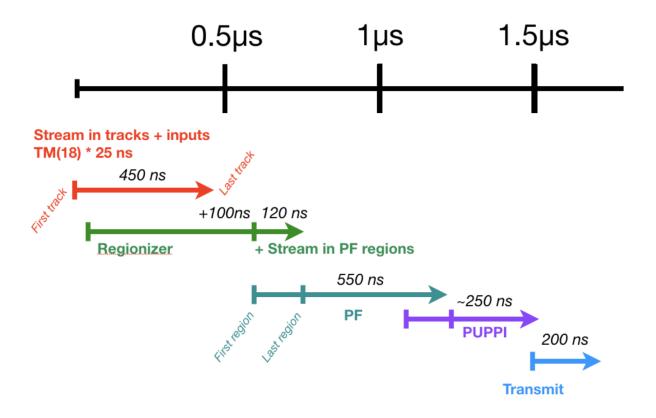

# Particle Flow — Correlator Layer 1

- Five firmware pieces in main algorithm:

- Common APx infrastructure

- Regionizer

- Particle Flow (PF)

- PileUp Per Particle Identification (PUPPI)

- **Output sorting**

- Meets timing with <50% resource use for VU9P-2 (plan to use VU13P-2).

- Latency of 1.1  $\mu$ s is sufficient to meet the requirements

- Simulation and emulation match in single board tests.

- The most challenging firmware project we have, and it works!

- Additional algorithm to do  $e/\gamma$  preprocessing tested; not yet integrated Utilization

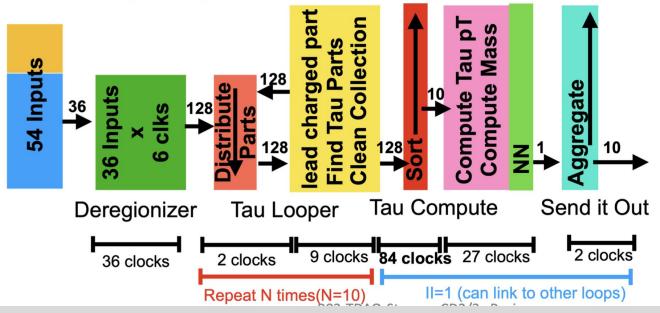

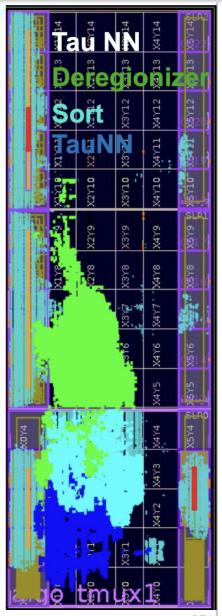

# Particle Flow — Correlator Layer 2 τ<sub>h</sub> wisconsin

- $\tau$  reconstruction with neural net:

- One of the first CL2 algorithms

- Now uses redesigned firmware incorporating deregionizer code and seeded cone jet reconstruction before  $\tau_h$  identification.

- Meets timing

- Latency of 1.0  $\mu$ s is sufficient to meet requirements

- Emulation matches and is in CMSSW with multi-vertex PUPPI capability.

# **Concluding Thoughts**

We in HEP are not innovators of modern computing technologies but we are amongst those who push it the most.

A team of engineers and physicists have tamed the LHC data deluge with intelligent use of telecommunications and computing technologies to enable fundamental physics discoveries.

We continue to push the technologies to the limit.

Advances in telecommunications and computing technologies are continually adapted to track increasing data volumes.

Students and postdocs are getting good training, especially in operations and firmware, for potential careers in both academia and industry – We invite you to join us in the HL-LHC adventure!