# Advanced FPGA design

#### ISOTDAQ 2023 @ Istanbul (Turkey) 17/06/2023

#### Prepared by Manoel Barros Marin

Presented by Maurício Féo

International School of Trigger and Data Acquisition

# Advanced FPGA ( ISOTDAQ 2023 @ Istanbul (Turk

# 17/06/2023

#### Notes like this one were added by Mauricio

#### Prepared by Manoel Barros Marin

Presented by Maurício Féo

International School of Trigger and Data Acquisition

Maurício Féo

Outline:

- ... from the previous lesson

- Key concepts about FPGA design

- FPGA gateware design workflow

- Summary

Outline:

#### ... from the previous lesson

Key concepts about FPGA design

FPGA gateware design workflow

Summary

Maurício Féo

What is an Field Programmable Gate Array (FPGA)?

#### What is an Field Programmable Gate Array (FPGA)?

FPGA - Wikipedia https://en.wikipedia.org/wiki/Field-programmable\_gate\_array A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence "field-programmable".

#### What is an Field Programmable Gate Array (FPGA)?

#### FPGA - Wikipedia

https://en.wikipedia.org/wiki/Field-programmable\_gate\_array A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing – hence "field-programmable".

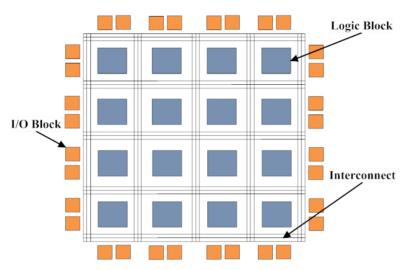

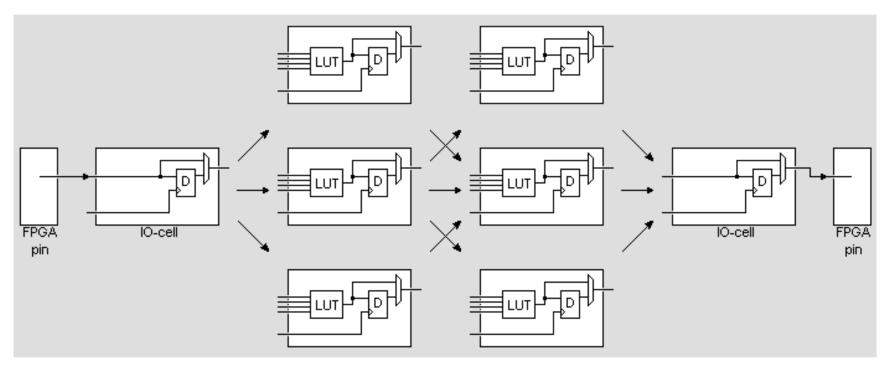

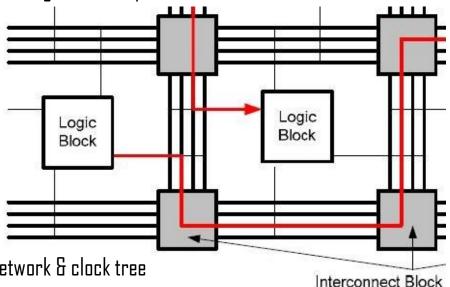

- FPGA fabric (matrix like structure) made of:

- 1/0-cells to communicate with outside world

- Logic cells

- $\circ$  Look-Up-Table (LUT) to implement combinatorial logic

- $\circ~$  Flip-Flops (D) to implement sequential logic

- Interconnect network between logic resources

- Clock tree to distribute the clock signals

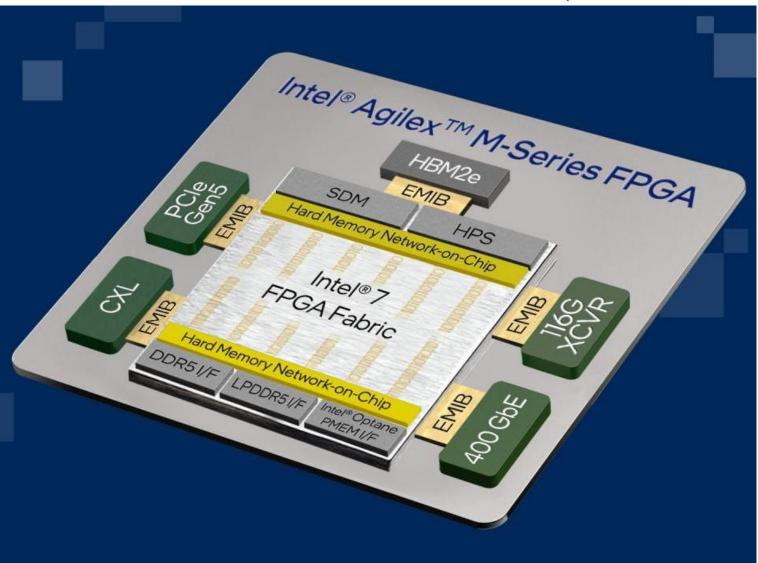

• But it also features Hard Blocks:

Example of FPGA architecture

Outline:

• …from the previous lesson

#### Key concepts about FPGA design

FPGA gateware design workflow

Summary

Maurício Féo

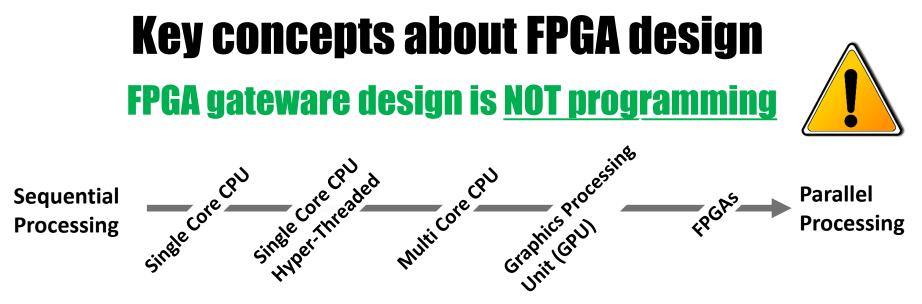

## Key concepts about FPGA design FPGA gateware design is <u>NOT programming</u>

- Programming

- Code is written and translated into instructions

- Instructions are executed sequentially by the CPU(s)

- Parallelism is achieved by running instructions on multiple threads/cores

- Processing structures and instructions sets are fixed by the architecture of the system

#### VS.

#### • FPGA gateware design

- No fixed architecture, the system is built according to the task

- Building is done by describing/defining system elements and their relations

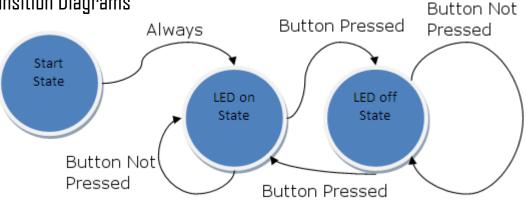

- Intrinsically parallel, sequential behaviour is achieved by registers and Finite-State-Machines (FSMs)

- Defined through a hardware description language (HDL), High Level Synthesis (HLS) or schematics

• Example of a WAIT statement (Programming Language VS. HDL)

- Example of a WAIT statement (Programming Language VS. HDL)

- In programming language (e.g. C) (Unix, #include <unistd.h>)

sleep(5); // sleep 5 seconds

- Example of a WAIT statement (Programming Language VS. HDL)

- In programming language (e.g. C) (Unix, #include <unistd.h>)

sleep(5); // sleep 5 seconds

- In HDL (e.g. VHDL):

- Not synthesizable (only for simulation test benches)

wait for 5 sec; -- handy for TB clocks

- Example of a WAIT statement (Programming Language VS. HDL)

- In programming language (e.g. C) (Unix, #include <unistd.h>)

sleep (5); // sleep 5 seconds

- In HDL (e.g. VHDL):

- $\circ$  Not synthesizable (only for simulation test benches)

wait for 5 sec; -- handy for TB clocks

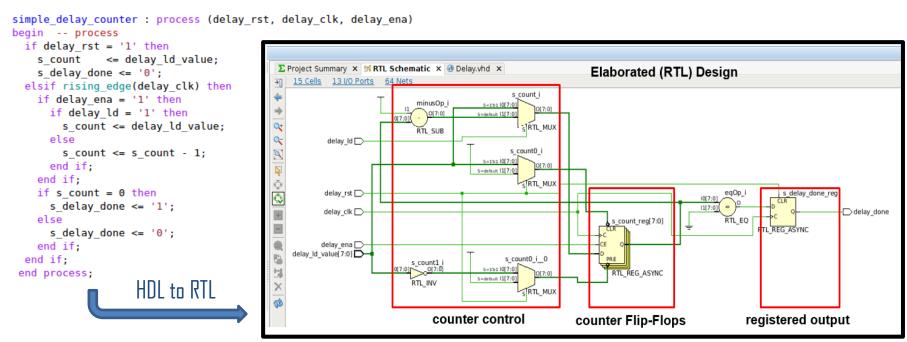

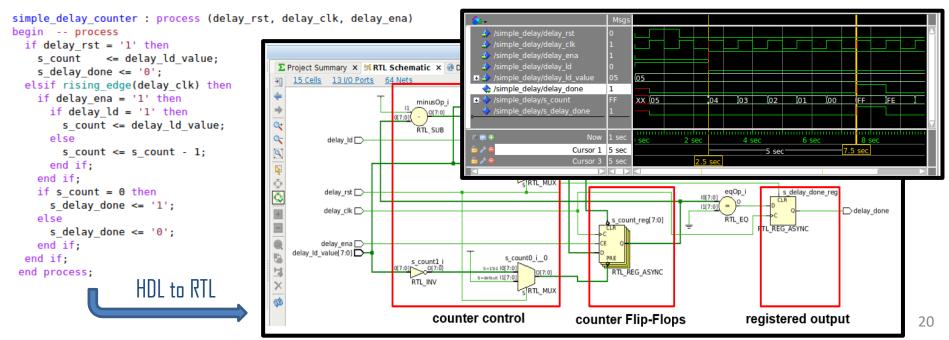

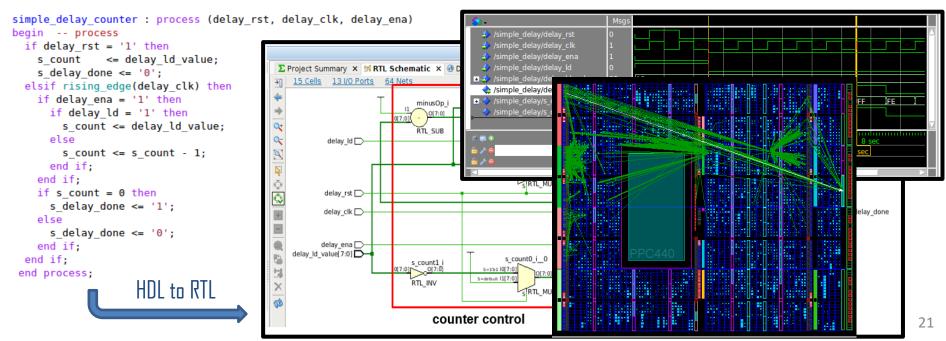

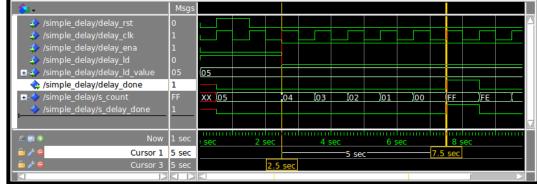

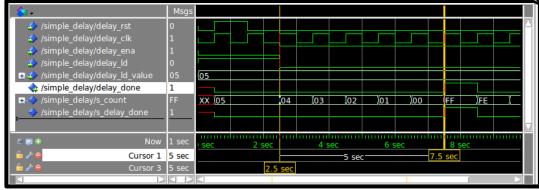

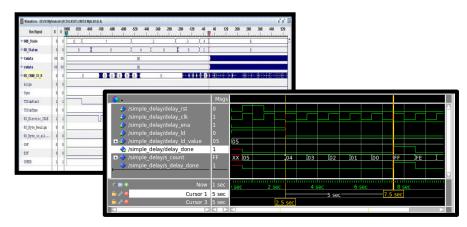

$\circ$  Synthesizable (for simulation and/or FPGA implementation)

```

simple delay counter : process (delay rst, delay clk, delay ena)

begin -- process

if delay rst = '1' then

s count <= delay ld value;</pre>

s delay done <= '0';</pre>

elsif rising edge(delay clk) then

if delay ena = '1' then

if delay ld = '1' then

s count <= delay ld value;</pre>

else

s_count <= s_count - 1;</pre>

end if;

end if:

if s count = 0 then

s delay done <= '1';</pre>

else

s delay done <= '0';</pre>

end if;

end if;

end process;

```

- Example of a WAIT statement (Programming Language VS. HDL)

- In programming language (e.g. C) (Unix, #include <unistd.h>) sleep(5); // sleep 5 seconds

- In HDL (e.q. VHDL): ٠

- Not synthesizable (only for simulation test benches)

wait for 5 sec; -- handy for TB clocks

• Synthesizable (for simulation and/or FPGA implementation)

```

simple delay counter : process (delay rst, delay clk, delay ena)

begin -- process

if delay rst = '1' then

s count <= delay ld value;</pre>

s delay done <= '0';</pre>

elsif rising edge(delay clk) then

if delay ena = '1' then

if delay ld = '1' then

s count <= delay ld value;</pre>

else

s_count <= s_count - 1;</pre>

end if:

end if:

if s count = 0 then

s delay done <= '1';</pre>

else

s delay done <= '0';</pre>

end if:

end if:

end process;

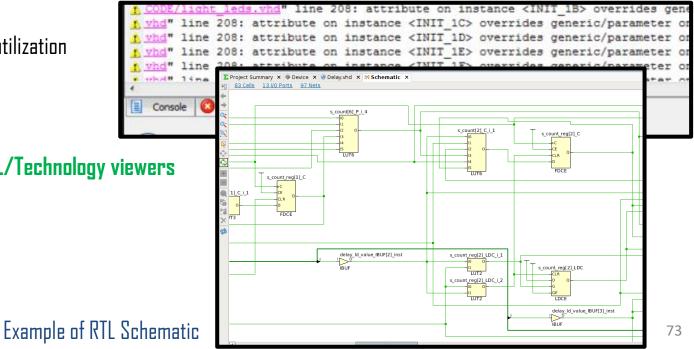

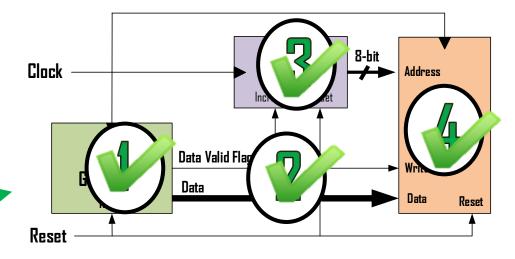

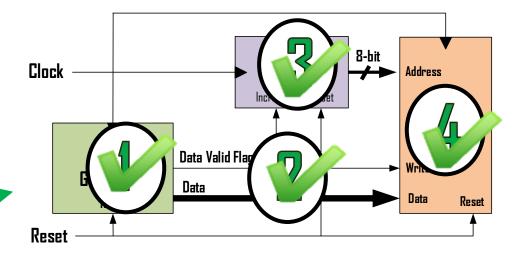

HDL to RTL

```

#### **Register Transfer Level (RTL)**

http://en.wikipedia.org/wiki/Register-transfer\_level

A design abstraction which models a synchronous digital circuit in terms of the flow of digital signals (data) between registers and logical operations performed on those signals

#### Example of a WAIT statement (Programming Language VS. HDL)

- In programming language (e.g. C) (Unix, #include <unistd.h>)

sleep (5); // sleep 5 seconds

- In HDL (e.g. VHDL):

- Not synthesizable (only for simulation test benches)

wait for 5 sec; -- handy for TB clocks

$\circ$  Synthesizable (for simulation and/or FPGA implementation)

SystemVerilog

- Example of a WAIT statement (Programming Language VS. HDL)

- In programming language (e.g. C) (Unix, #include <unistd.h>)

sleep (5); // sleep 5 seconds

- In HDL (e.g. VHDL):

- $\circ$  Not synthesizable (only for simulation test benches)

wait for 5 sec; -- handy for TB clocks

$\circ~$  Synthesizable (for simulation and/or FPGA implementation)

- Example of a WAIT statement (Programming Language VS. HDL)

- In programming language (e.g. C) (Unix, #include <unistd.h>)

sleep (5); // sleep 5 seconds

- In HDL (e.g. VHDL):

- $\circ$  Not synthesizable (only for simulation test benches)

wait for 5 sec; -- handy for TB clocks

$\circ$  Synthesizable (for simulation and/or FPGA implementation)

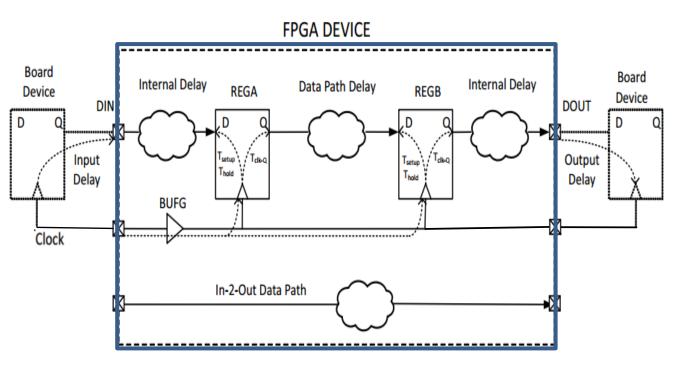

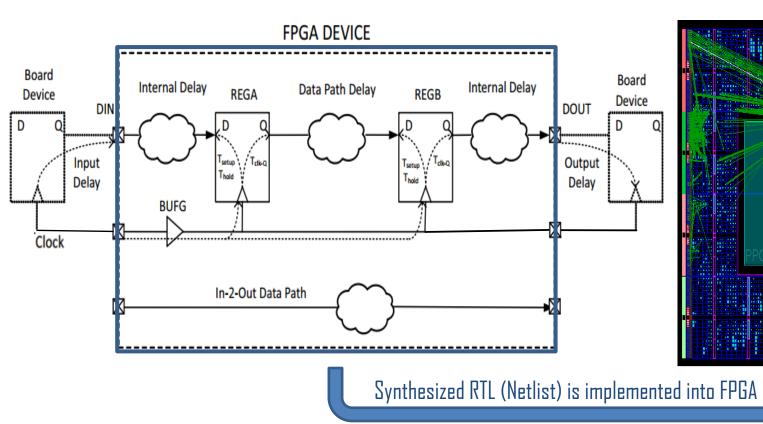

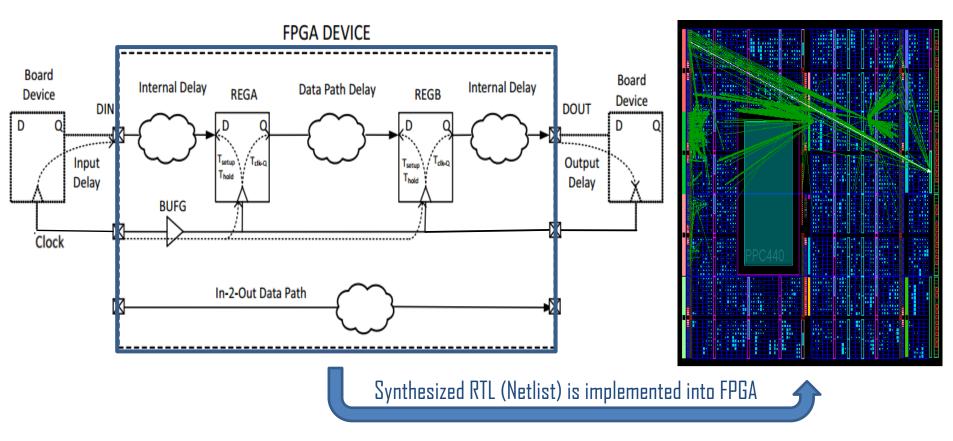

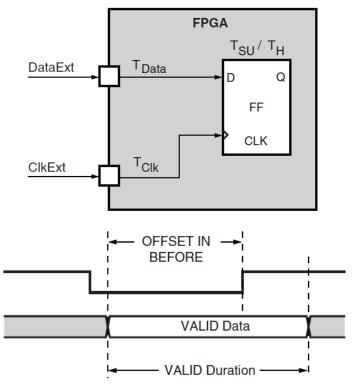

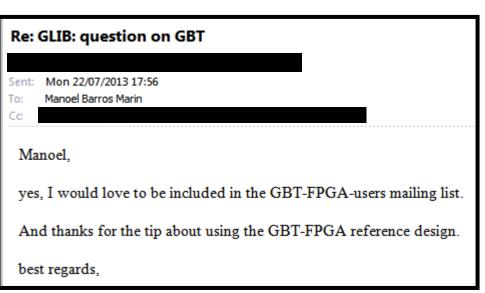

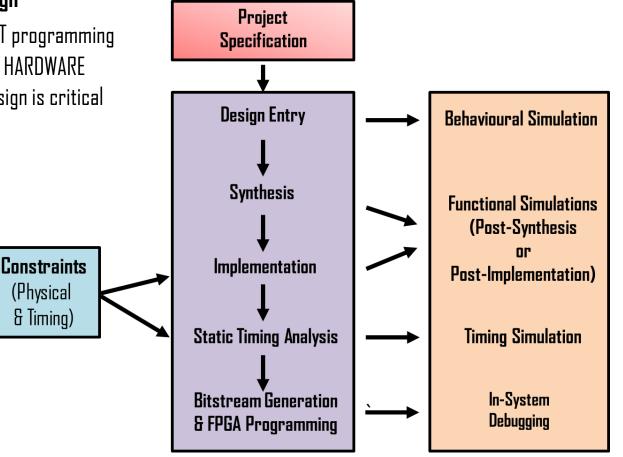

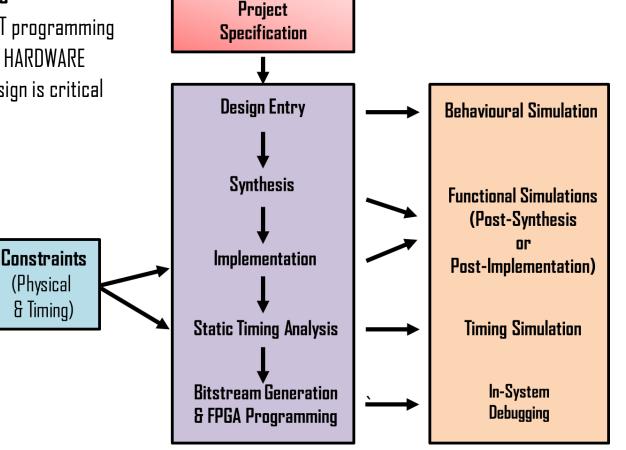

### Key concepts about FPGA design Timing in FPGA gateware design is critical

# Key concepts about FPGA design <u>Timing</u> in FPGA gateware design is critical

• Data propagates in the form of electrical signals through the FPGA

# Key concepts about FPGA design <u>Timing</u> in FPGA gateware design is critical

Data propagates in the form of electrical signals through the FPGA

# Key concepts about FPGA design <u>Timing</u> in FPGA gateware design is critical

Data propagates in the form of electrical signals through the FPGA

• If these signals do not arrive to their destination on time...

#### The consequences may be catastrophic!!!

#### Key concepts about FPGA design

# When designing FPGA gateware you have to think HARD... ٥ 0

#### Key concepts about FPGA design

#### When designing FPGA gateware you have to think

Maurício Féo

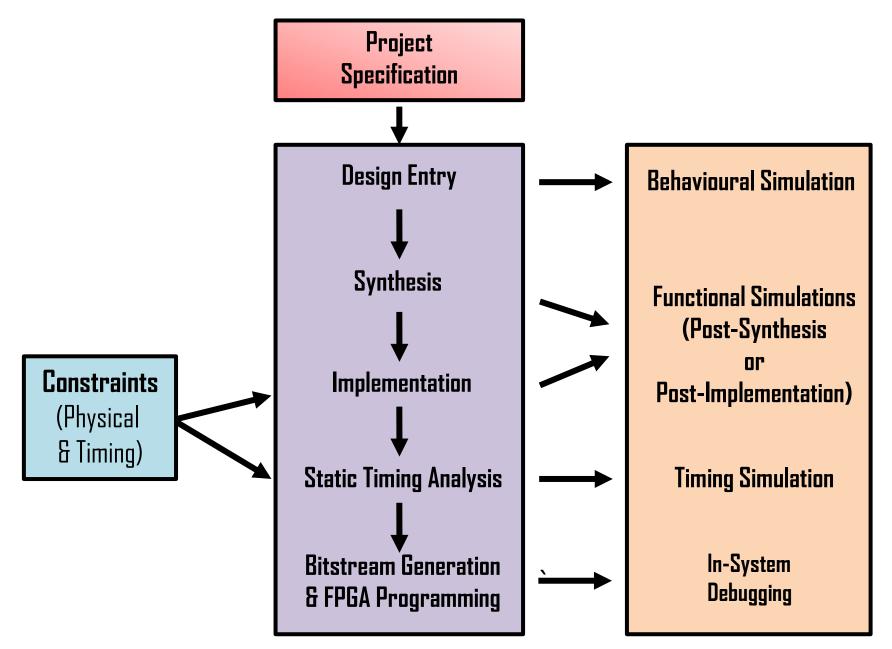

Outline:

- …from the previous lesson

- Key concepts about FPAA design

- FPGA gateware design workflow

• Summary

#### **Project Specification**

This is the most critical step...

The rest of the design process is based on it!!!

#### **Project Specification**

This is the most critical step...

#### The rest of the design process is based on it!!!

#### **Project Specification**

This is the most critical step...

• Gather requirements from the users

users The rest of the design process is based on it!!!

#### **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

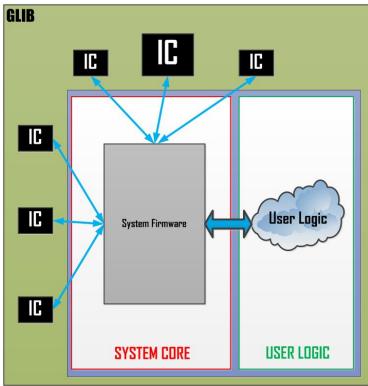

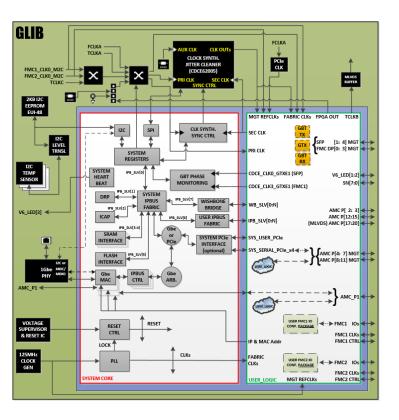

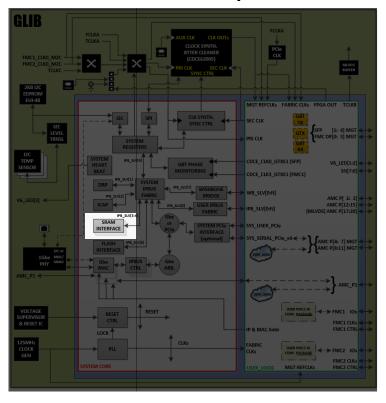

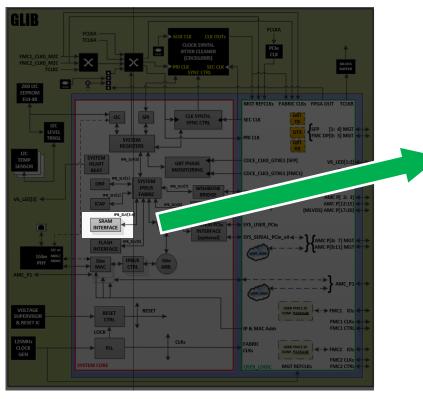

#### Example of General Purpose Gateware

The rest of the design process is based on it!!!

#### **Project Specification**

This is the most critical step...

• Gather requirements from the users

The rest of the design process is based on it!!!

- Specify:

- Target application (General purpose or Specific)

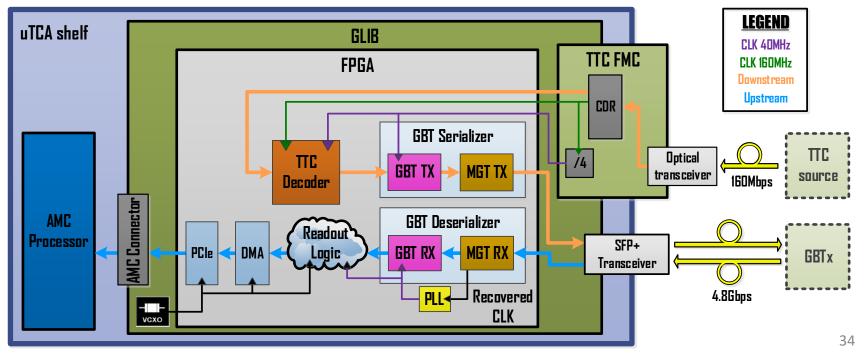

#### Example of Application Specific Gateware

#### **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

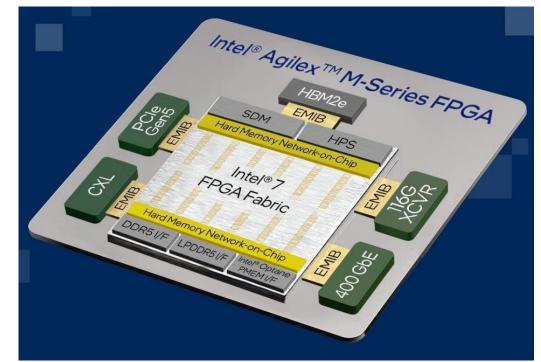

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

Example of FPGA Architecture

The rest of the design process is based on it!!!

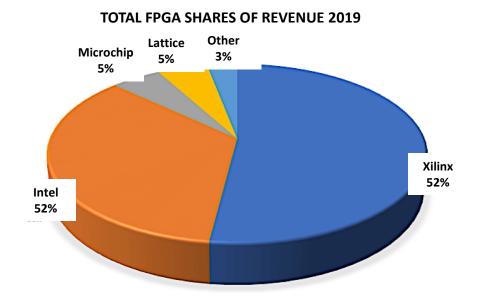

#### **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

Small FPGA vendors may target specific markets (e.g. Microsemi offers high reliable FPGAs, etc..)

The rest of the design process is based on it!!!

Source: The Information Network (www.theinformationnet.com)

## **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

- Electronic board (Custom or COTS (\*))

Example of COTS board (Xilinx Devkit)

The rest of the design process is based on it!!!

(\*) Commercial Off-The-Shelf (COTS)  $^{

m 37}$

## **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

- Electronic board (Custom or COTS (\*))

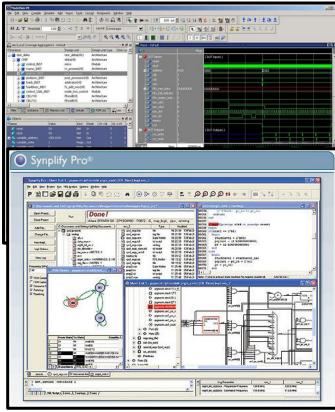

- Development tools (FPGA vendor or Commercial)

#### Example of FPGA Vendor Tools

| 🐮 😂 🖩 🕼 🕫 🖬 🐘 🗙 🖑                                               | Main a a a a a a a a a a a a a a a a a a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Quartus II - D:/Users/SVN/DROJECTS/                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                           | T_TOP - UART_TOP - [uar | t_top.vhd] |                                                                                                            |        | - 6 × |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------|------------------------------------------------------------------------------------------------------------|--------|-------|--|

| Flow Navigator                                                  | Implemented Desig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                           |                         | 0 0 F 12 M | hn (3 🕨                                                                                                    |        |       |  |

| へ国際                                                             | Netist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Project Navigator                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                           |                         |            |                                                                                                            |        |       |  |

| <ul> <li>Project Istanger         <ul> <li></li></ul></li></ul> | ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■         ■ | Erdy State P261, N2710C2<br>State III P261, N2710C2<br>State III P261, N2710C2<br>State III P261, N2710C2<br>State III P261, N2710C2<br>State IIII P261, N2710C2<br>State IIII P261, N2710C2<br>State IIIII P261, N2710C2<br>State IIIIII P261, N2710C2<br>State IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII |                                                                                                                                                                                                                                                                                                                           |                         | Norm       | Values<br>9<br>9<br>9<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>4<br>5<br>4<br>4<br>5<br>4<br>5 |        |       |  |

| Open Hardware Session                                           | pen_sons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                      | A branc . B Henry Store                                                                                                                                                                                                                                                                                                   |                         | <u>III</u> | Cetault                                                                                                    | twelg* |       |  |

| Launch IMPACT                                                   | Type a Tol o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | System (Processing ) Estra Info ) Info                                                                                                                                                                                                                                                               | Denix<br>Press t<br>Press<br>and try<br>Solder sideg doublished protes.<br>Press and a sold rest about the sold<br>Press and the sold try the sold sold sold sold sold sold sold sold sold |                         |            |                                                                                                            |        |       |  |

#### Example of Commercial Tools

The rest of the design process is based on it!!!

#### $^{(*)}$ Commercial Off-The-Shelf (COTS) $^{\rm 38}$

### **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

- Electronic board (Custom or COTS (\*))

- Development tools (FPGA vendor or Commercial)

- Optimization (Speed, Area, Power or default)

### **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

- Electronic board (Custom or COTS (\*))

- Development tools (FPGA vendor or Commercial)

- Optimization (Speed, Area, Power or default)

### **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

- Electronic board (Custom or COTS (\*))

- Development tools (FPGA vendor or Commercial)

- Optimization (Speed, Area, Power or default)

### **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

- Electronic board (Custom or COTS (\*))

- Development tools (FPGA vendor or Commercial)

- Optimization (Speed, Area, Power or default)

### **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

- Electronic board (Custom or COTS (\*))

- Development tools (FPGA vendor or Commercial)

- Optimization (Speed, Area, Power or default)

- Design language (HDL, Schematics or HLS)

#### HDL are the most popular for RTL design but... Schematics or HLS may be better in some cases (e.g. SoC bus interconnect, etc..)

#### Examples of Design Languages

| 31 |             |      |   |     |             |

|----|-------------|------|---|-----|-------------|

| 32 | entity XuLA | 2 is |   |     |             |

| 33 | Port (      | PB1  | : | in  | STD_LOGIC;  |

| 34 | i           | PB2  |   | in  | STD_LOGIC;  |

| 35 | 1           | PB3  |   | in  | STD_LOGIC;  |

| 36 | 1           | PB4  |   | in  | STD_LOGIC;  |

| 37 | :           | LED1 | : | out | STD_LOGIC;  |

| 38 | :           | LED2 |   | out | STD_LOGIC;  |

| 39 |             | LED3 | : | out | STD_LOGIC;  |

| 40 | :           | LED4 |   | out | STD_LOGIC); |

| 41 | end XuLA 2; |      |   |     |             |

#### **Project Specification**

#### This is the most critical step...

The rest of the design process is based on it!!!

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

- Electronic board (Custom or COTS (\*))

- Development tools (FPGA vendor or Commercial)

- Optimization (Speed, Area, Power or default)

- Design language (HDL, Schematics or HLS)

- Coding convention

#### Example of Coding Convention

| description     | extension | example  |

|-----------------|-----------|----------|

| variable        | prefix v  | v_Buffer |

| alias           | prefix a  | a_Bit5   |

| constant        | prefix c  | c_Lenght |

| type definition | prefix t  | t_MyType |

| generics        | prefix g  | g_Width  |

#### Your code should be readable

44

## **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

### ### ###

put put put xfi xfi xfi

48 49

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.

- Electronic board (Custom or COTS (\*))

- Development tools (FPGA vendor or Commercial)

- Optimization (Speed, Area, Power or default)

- Design language (HDL, Schematics or HLS)

| Coding convention                                                                                                              | Par Helb, press P1                                | <pre>/ Leading vere-bidet(bidet_acch) / L / L / L / L / L / L / L / L / L / L</pre> | ⊕W         interventy of the log(j) = {(cond j) = m(i) j + |          |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Software interface (GUI, Scripts or both)                                                                                      | Example of TCL script                             | 1973 Tea San San San San San San San San San Sa                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | s 1036 m |

| ######################################                                                                                         | BT-FPGA Core #################################### | Xil                                                                                 | inx ISE TCL console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|                                                                                                                                | Tcl Console                                       |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Comment: Adding Common files:                                                                                                  |                                                   |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| s "->"                                                                                                                         |                                                   |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| s "-> Adding common files of the GBT-FPGA Core to the ISE pro<br>s "->"                                                        |                                                   |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| le add \$SOURCE_PATH/gbt_bank/core_sources/gbt_rx/gbt_rx.vhd                                                                   |                                                   |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| le add \$SOURCE_PATH/gbt_bank/core_sources/gbt_rx/gbt_rx_deco<br>le add \$SOURCE PATH/gbt bank/core_sources/gbt_rx/gbt_rx_deco |                                                   |                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|                                                                                                                                | 🗐 Console 👩 Errors \Lambda Warnings               | Tel Concolo                                                                         | Find in Files Desults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45       |

Errors

Warnings

Tcl Console

# The rest of the design process is based on it!!!

Example of GUIs

The rest

## **Project Specification**

- This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transci

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Mi

- Electronic board (Custom or COTS (\*))

- Development tools (FPGA vendor or Commercial)

- Optimization (Speed, Area, Power or default)

- Design language (HDL, Schematics or HLS)

- Coding convention

47

48 49 Softwa

Automate as much as you can, specially for big projects!

- Compilation

- Simulation

- Hardware tests

Tcl Console

46

Find in Files Results

| Software interface (GUI, Scripts or both)                                                                                            | Example of TCL script                                | la mengeneen Transmer<br>Jen stree teks 1<br>Jen stree teks 1 |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ######################################                                                                                               | e GBT-FPGA Core #################################### | Xilinx ISE TCL console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                      | Tcl Console                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ## Comment: Adding Common files:                                                                                                     |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| puts "->"<br>puts "-> Adding common files of the GBT-FPGA Core to the ISE pr<br>puts "->"                                            |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| xfile add \$SOURCE_PATH/gbt_bank/core_sources/gbt_rx/gbt_rx.vhd                                                                      |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| xfile add \$SOURCE_PATH/gbt_bank/core_sources/gbt_rx/gbt_rx_deco<br>xfile add \$SOURCE PATH/gbt bank/core sources/gbt rx/gbt rx deco |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Console

Errors

Warnings

## **Project Specification**

This is the most critical step...

- Gather requirements from the users

- Specify:

- Target application (General purpose or Specific)

- Main features (e.g. System bus, SoC, Multi-gigabit transceivers, etc.)

- FPGA vendor (e.g. AMD Xilinx, Intel (Altera), Microchip (Microsemi), etc.)

- Electronic board (Custom or COTS (\*))

- Development tools (FPGA vendor or Commercial)

- Optimization (Speed, Area, Power or default)

- Design language (HDL, Schematics or HLS)

- Coding convention

- Software interface (GUI, Scripts or both)

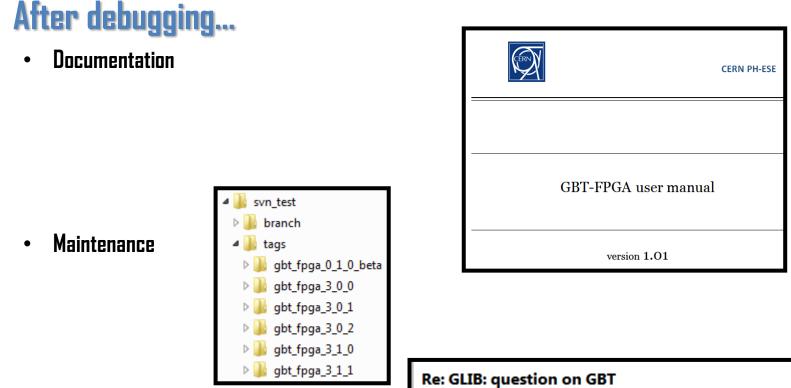

- Use of files repository (SVN, GIT, etc.. or none)

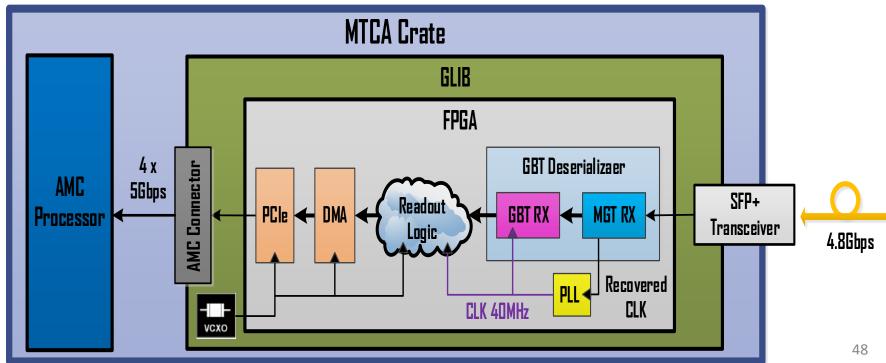

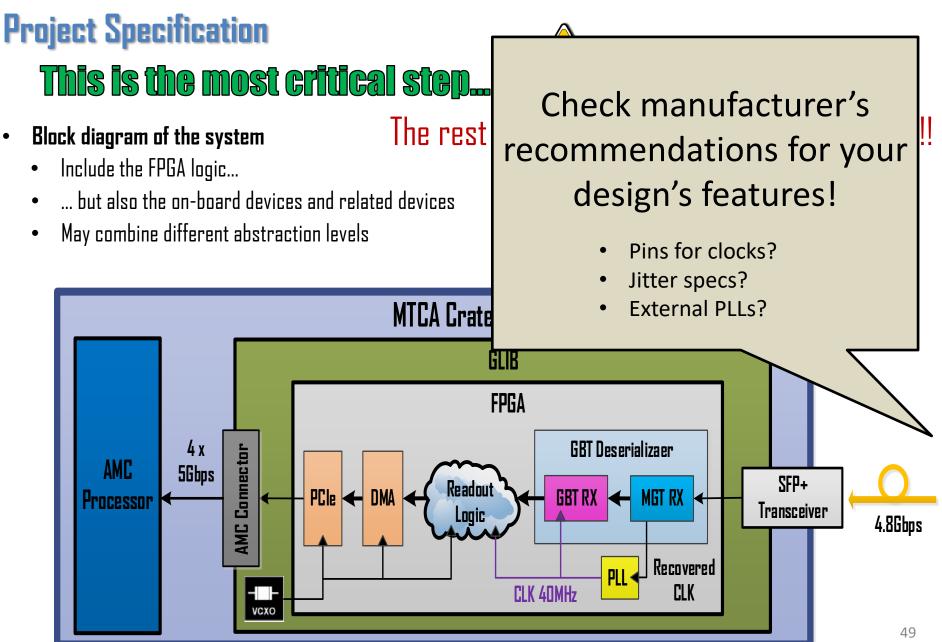

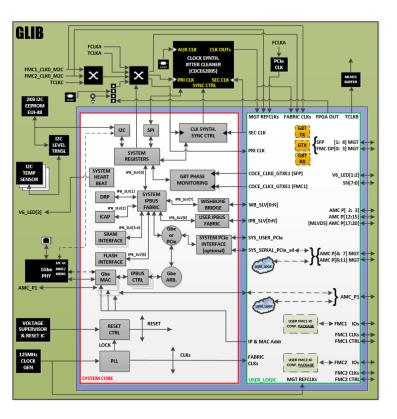

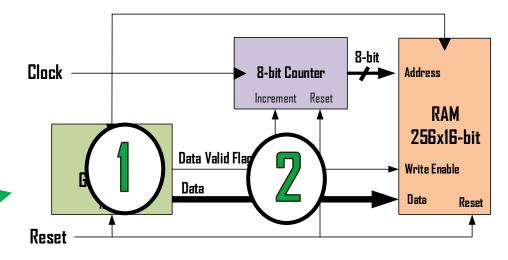

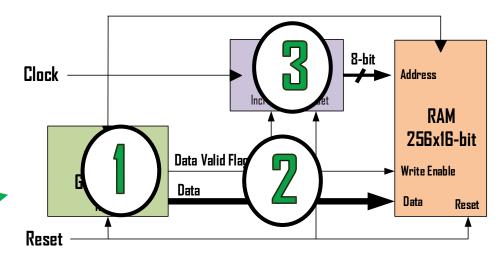

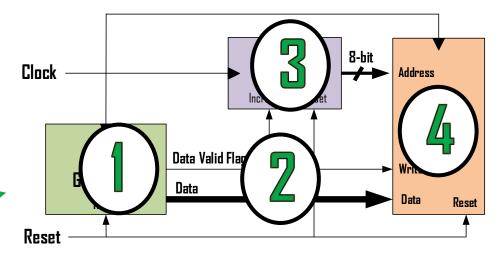

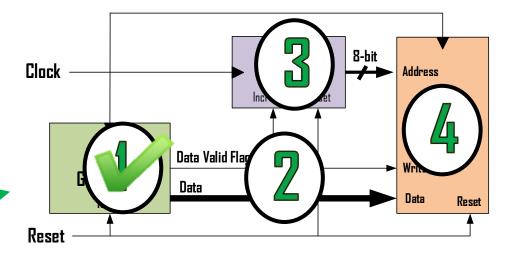

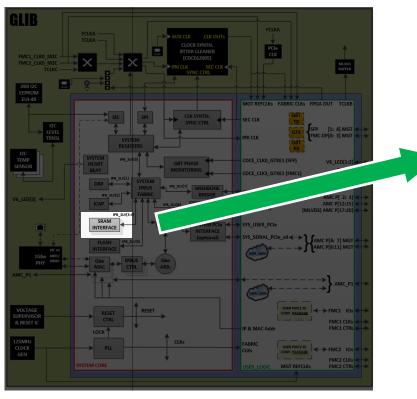

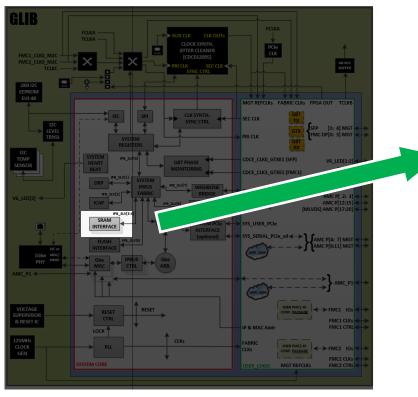

#### **Project Specification**

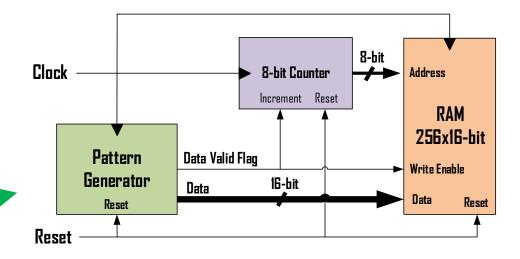

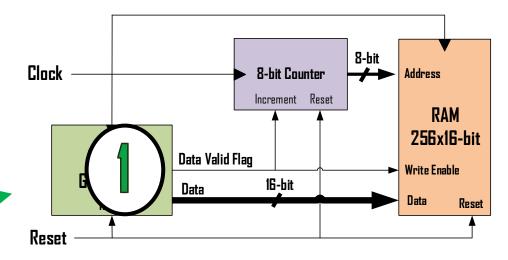

This is the most critical step...

- Block diagram of the system

- Include the FPGA logic...

- ... but also the on-board devices and related devices

- May combine different abstraction levels

Example of system block diagram

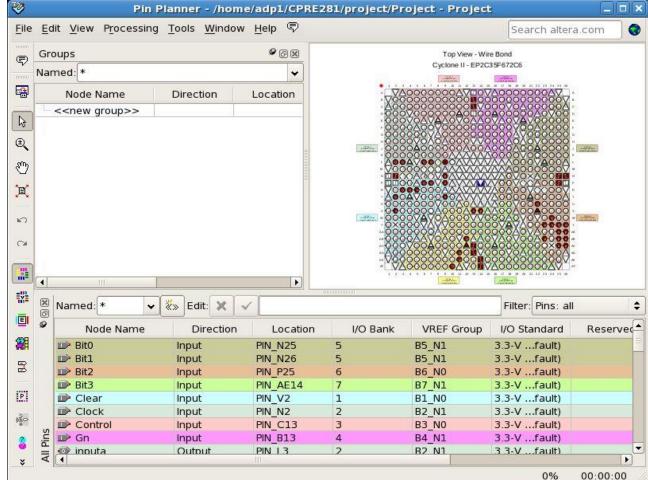

### **Project Specification**

This is the most critical step...

#### • Pin planning

Pin assignments are one type of Location Constraints

#### Critical for Custom Boards!!!

#### Example of Pin Planner GUI

#### The rest of the design process is based on it!!!

50

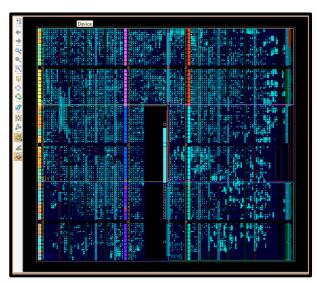

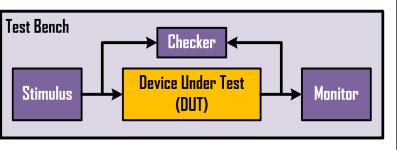

## FPGA gateware design workflow Design Entry

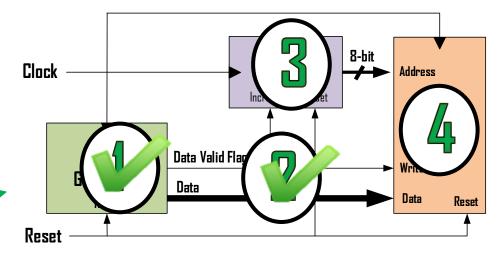

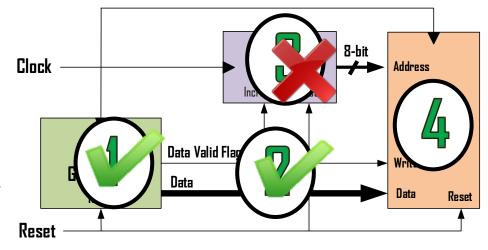

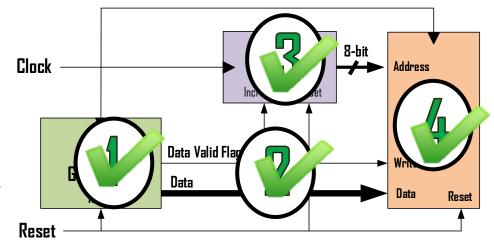

### Design Entry: Modularity & Reusability

- Your system should be Modular

- Design at RTL level (think hard...ware)

- Well defined clocks and resets schemes

- Separated Data & Control paths

- Multiple instantiations

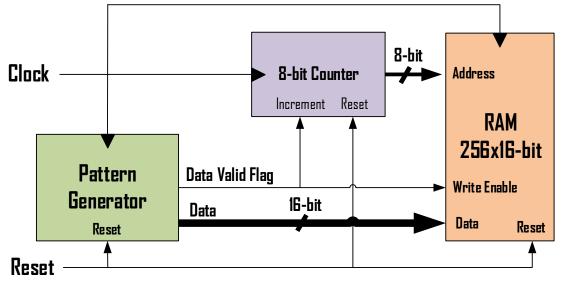

#### Good example of Modular System

#### • Your code should be Reusable

- Add primitives (and modules) to the system by inference when possible

- Use parameters in your code (e.g. generics in VHDL, parameters in Verilog, etc.)

- Centralise parameters in external files (e.g. packages in VHDL, headers in Verilog, etc.)

- Use configurable modules interfaces when possible (e.g. parametrised vectors, records in VHDL, etc.)

- Use standard features (e.g. I2C, Wishbone, etc.)

- Use standard IP Cores (e.g. from <a href="https://www.OpenCores.org">www.OpenCores.org</a>, etc.)

- Avoid vendor specific IP Cores when possible

- Talk with your colleagues and see what other FPGA designers are doing

Patti

Gener

Res

### Design Entry: <u>Modularity & Reusability</u>

- Your system should be Modular

- Design at RTL level (think hard...ware)

- Well defined clocks and resets schemes

- Separated Data & Control paths

- Multiple instantiations

#### Seriously, talk to your colleagues before wasting your time on code!

They might have done what you need already!

#### • Your code should be Reusable

- Add primitives (and modules) to the system by inference when possible

- Use parameters in your code (e.g. generics in VHDL, parameters in Verilog, etc.)

- Centralise parameters in external files (e.g. packages in VHDL, headers in Verilog, etc.)

Reset

Clock

- Use configurable modules interfaces when possible (e.g. parametrised vectors, records in VHDL, etc.)

- Use standard features (e.g. I2C, Wishbone, etc.)

- Use standard IP Cores (e.g. from <a href="https://www.OpenCores.org">www.OpenCores.org</a>, etc.)

- Avoid vendor specific IP Cores when possible

- Talk with your colleagues and see what other FPGA designers are doing

#### Design Entry: <u>Coding for Synthesis</u>

## Synthesizable code is intended for FPGA implementation

• Use non-synthesizable HLD statements only in simulation test benches

A fundamental guiding principle when coding for synthesis is to minimize, if not eliminate, all structures and directives that could potentially create a mismatch between simulation and synthesis. From book "Advanced FPGA Design" by Steve Kilts (Copyright © 2007 John Wiley & Sons, Inc.)

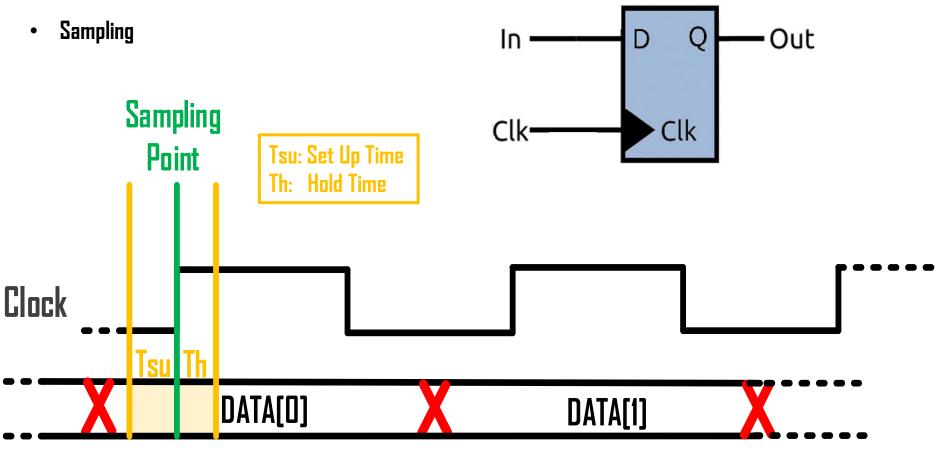

• The RTL synthesis tool is expecting a synchronous design...

#### Design Entry: <u>Coding for Synthesis</u>

## Synthesizable code is intended for FPGA implementation

• Use non-synthesizable HLD statements only in simulation test benches

A fundamental guiding principle when coding for synthesis is to minimize, if not eliminate, all structures and directives that could potentially create a mismatch between simulation and synthesis. From book "Advanced FPGA Design" by Steve Kilts (Copyright © 2007 John Wiley & Sons, Inc.)

• The RTL synthesis tool is expecting a synchronous design...

But what is a synchronous design???

#### **Design Entry: Coding for Synthesis**

## Synthesizable code is intended for FPGA implementation

• Use non-synthesizable HLD statements only in simulation test benches

A fundamental guiding principle when coding for synthesis is to minimize, if not eliminate, all structures and directives that could potentially create a mismatch between simulation and synthesis. From book "Advanced FPGA Design" by Steve Kilts (Copyright © 2007 John Wiley & Sons, Inc.)

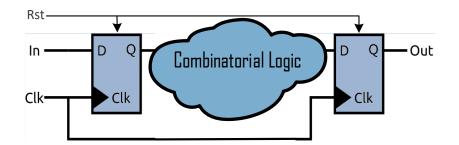

• The RTL synthesis tool is expecting a <u>synchronous design</u>...

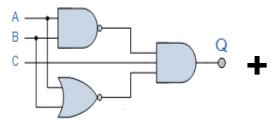

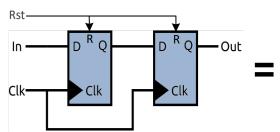

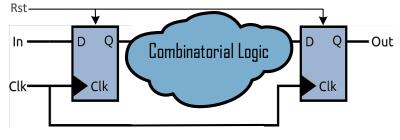

Synchronous design is the one compose by combinatorial logic (e.g. logic gates, multiplexors, etc..) and sequential logic (registers that are triggered on the edge of a single clock),

Combinatorial Logic

Sequential Logic

Synchronous design

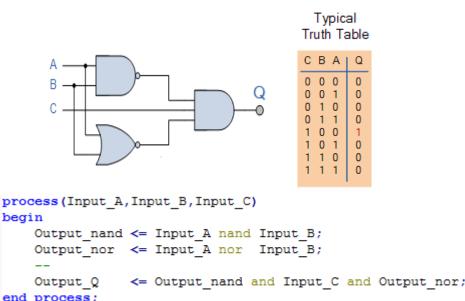

## Design Entry: <u>Coding for Synthesis</u>

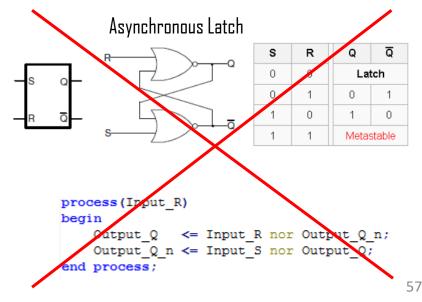

- Combinatorial logic coding rules

- Sensitivity list must include ALL input signals Not respecting this may lead to non responsive outputs under changes of input signals

- ALL output signals must be assigned under ALL possible input conditions Not respecting this may lead to undesired latches (asynchronous storage element)

- No feedback from output to input signals

Not respecting this may lead to unknown output states (metastability) & undesired latches

#### Good combinatorial coding for synthesis

#### Bad combinatorial coding for synthesis

## Design Entry: <u>Coding for Synthesis</u>

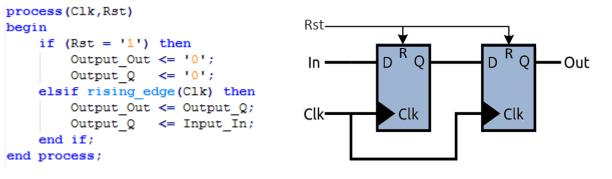

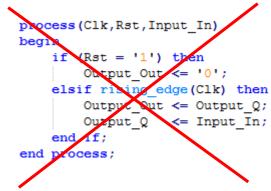

- Sequential logic coding rules

- Only clock signal (and asynchronous set/reset signals when used) in sensitivity list Not respecting this may produce undesired combinatorial logic

- All registers of the sequence must be triggered by the same clock edge (either Rising or Falling) Not respecting this may lead to metastability at the output of the registers

- Include all registers of the sequence in the same reset branch Not respecting this may lead to undesired register values after reset

#### Good sequential coding for synthesis

#### Bad sequential coding for synthesis

## Design Entry: <u>Coding for Synthesis</u>

- Synchronous design coding rules:

- FULLY synchronous design

- No combinatorial feedback

- o No asynchronous latches

Not respecting this may lead to incorrect analysis from the FPGA design tool

- Register ALL output signals (input signals also recommended) Not respecting this may lead to uncontrolled length of combinatorial paths

- Properly design of reset scheme (mentioned later)

Not respecting this may lead to undesired register values after reset

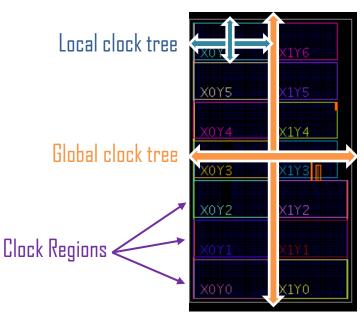

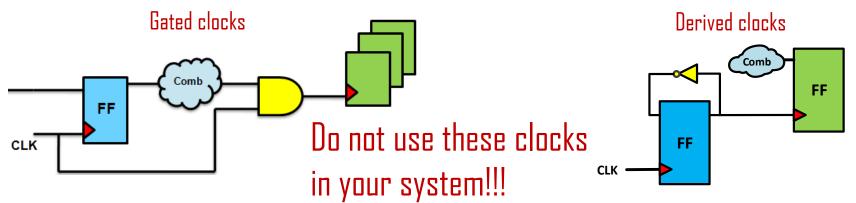

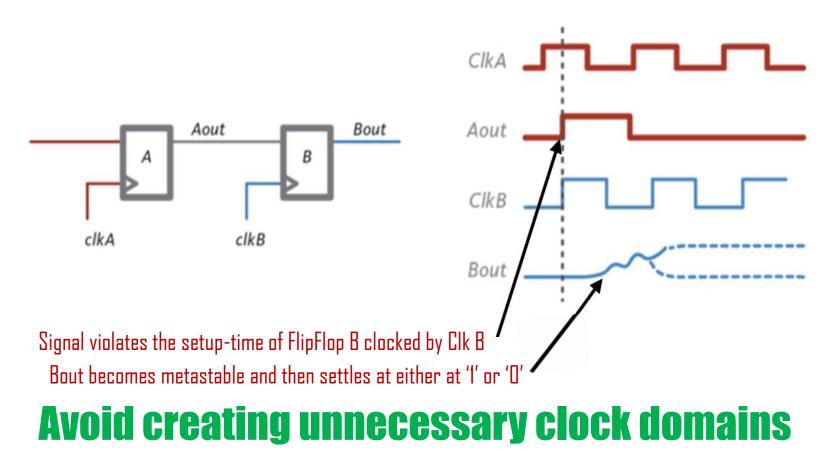

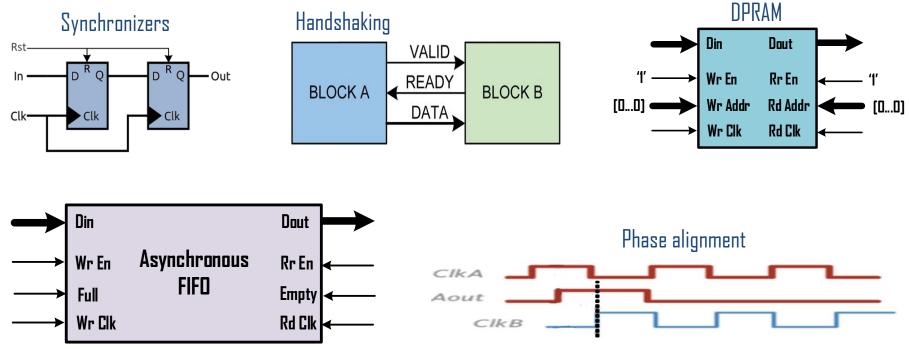

- Properly design of clocking scheme (mentioned later)

Not respecting this may lead to metastability at the output of the registers & Misuse of resources

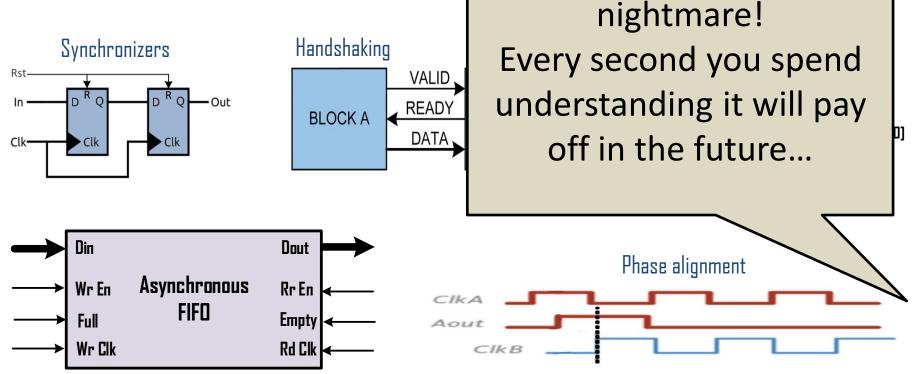

- Properly handle Clock Domain Crossings (CDC) (mentioned later) Not respecting this may lead to metastability at the output of the registers

## Design Entry: <u>Coding for Synthesis</u>

- Finite State Machines (FSMs):