# High Energy Physics and Instrumentation with the LHC-CERN

#### **Radiation Effects in Electronic Devices**

N. H. Medina

Instituto de Física da Universidade de São Paulo

#### **o** Radiation effects in electronic componentes

• Measurement examples.

• New beam line for Applied Nuclear Physics

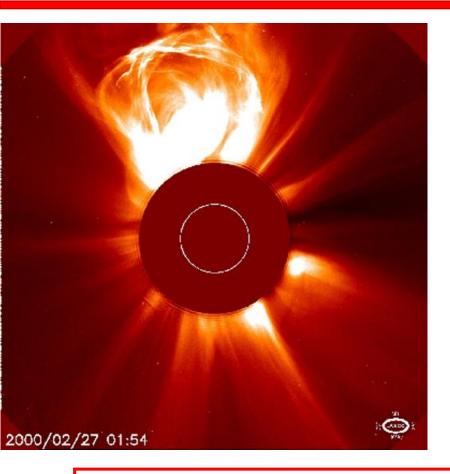

#### **Coronal Mass Ejection**

A Coronal Mass Ejection (CME) blasts into space a billion tons of particles traveling millions of km/h, impacting any planet or spacecraft in its path.

Credit: A coronal mass ejection on Feb. 27, 2000 taken by SOHO LASCO C2 and C3 (SOHO ESA & NASA) and Rudolf R. Bühler

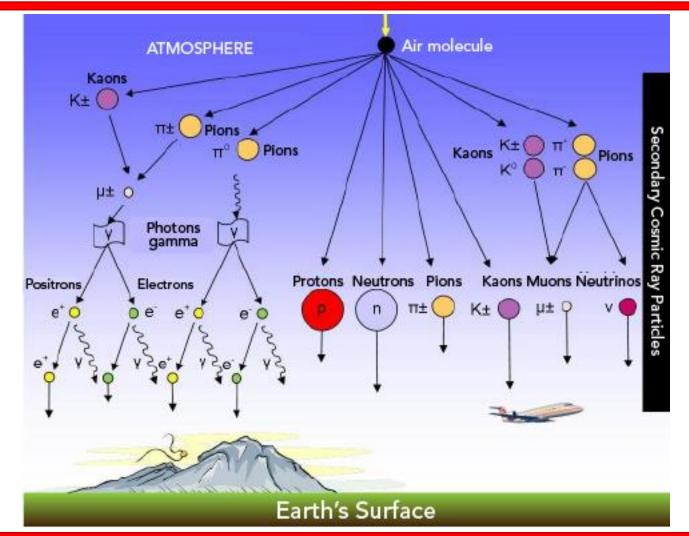

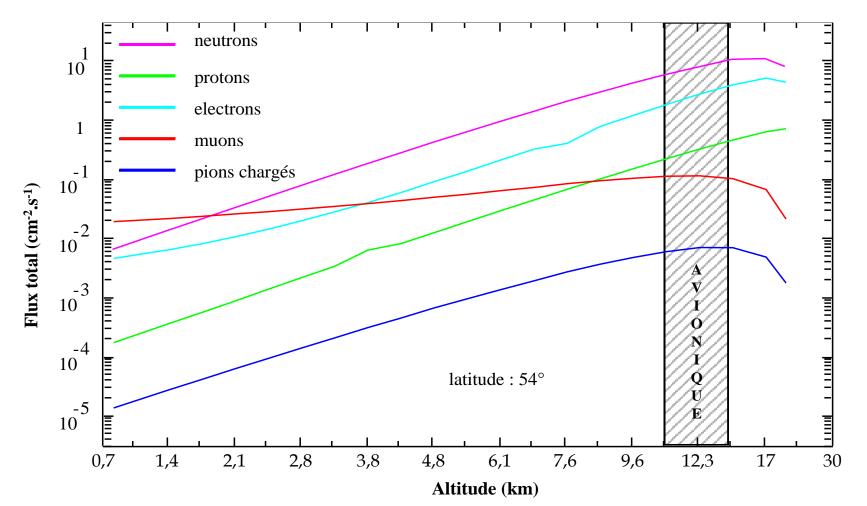

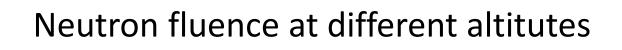

## Neutron production in Atmosphere

https://letstalkscience.ca/educational-resources/backgrounders/what-are-cosmic-rays

P. Goldhagen et al., Nuclear Instruments and Methods in Physics Research A 476 (2002) 42–51

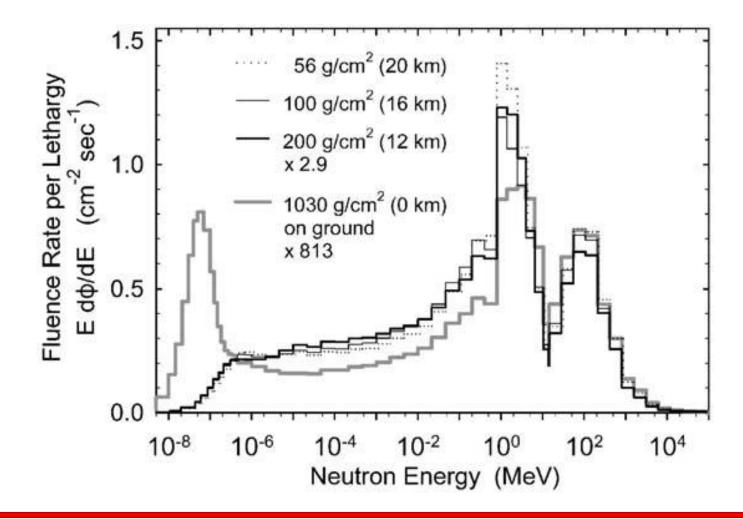

# Neutron Flux Simulation inside the MAGNEX Experimental Hall

A dedicated simulation was performed with the FLUKA code in order to evaluate the radiation spectra and fluence as a function of the topology of the detectors inside the MAGNEX experimental hall at LNS.

#### Four radiation sources were considered :

- Beam-target interaction;

- Leakage along the transport of beam line;

- Beam beam stopper interaction.

- Secondary radiation induced by neutron interactions with the material inside the experimental hall, including its walls, floor and ceiling.

#### The <sup>20</sup>Ne beam interaction with a <sup>76</sup>Ge target with <sup>12</sup>C backing was simulated

Fully stripped <sup>20</sup>Ne beam with an energy of 60 MeV/A and a current of 85  $e\mu$ A The beam dump is inside a concrete bunker.

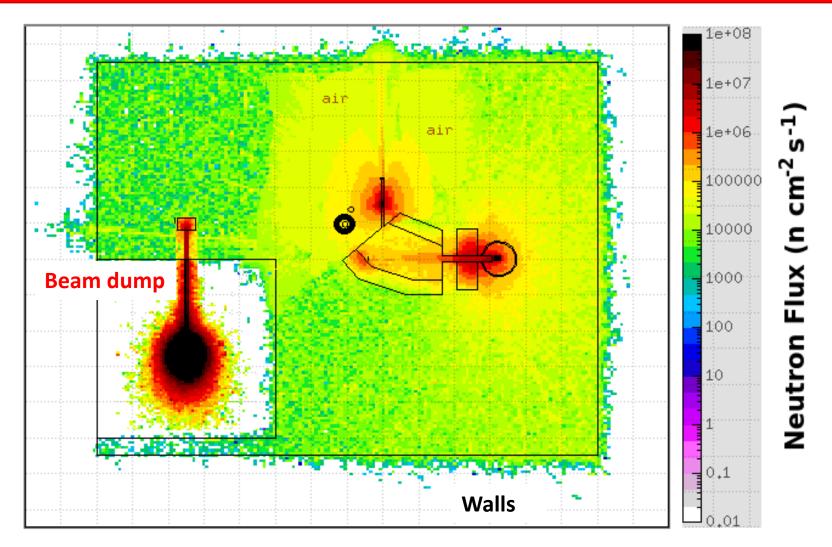

Neutron energy spectrum obtained via FLUKA simulations for the region where the MAGNEX focal plane detector is located

#### **Neutron-induced Nuclear Reactions**

**Fusion-evaporation Monte Carlo Calculations**

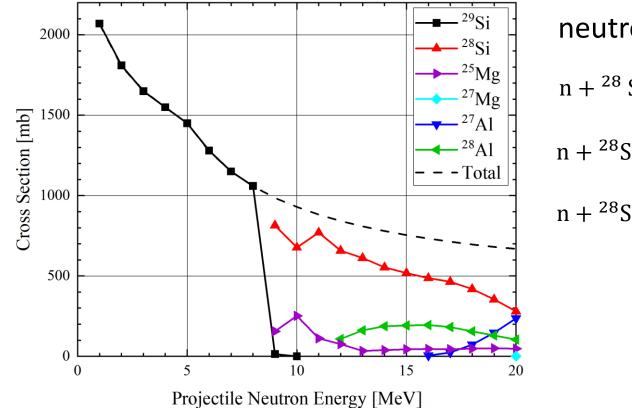

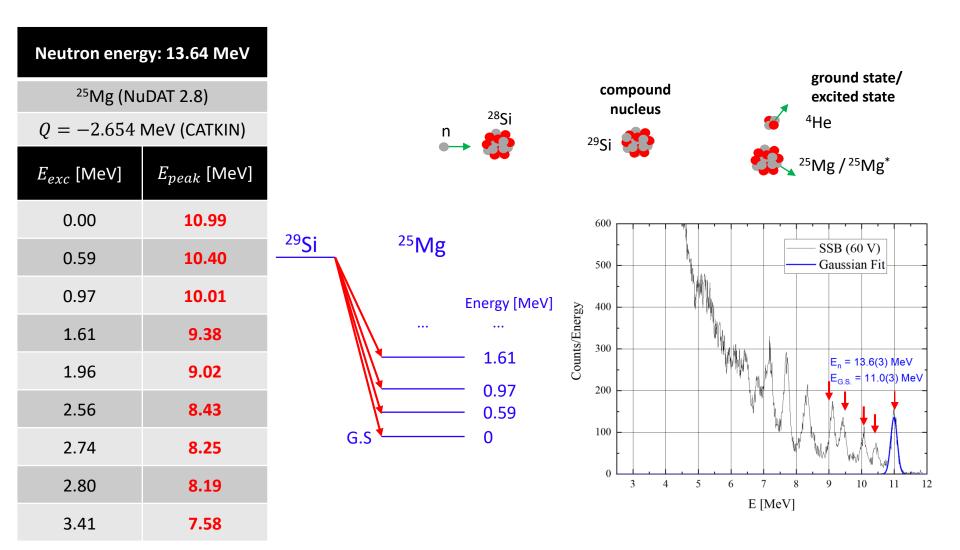

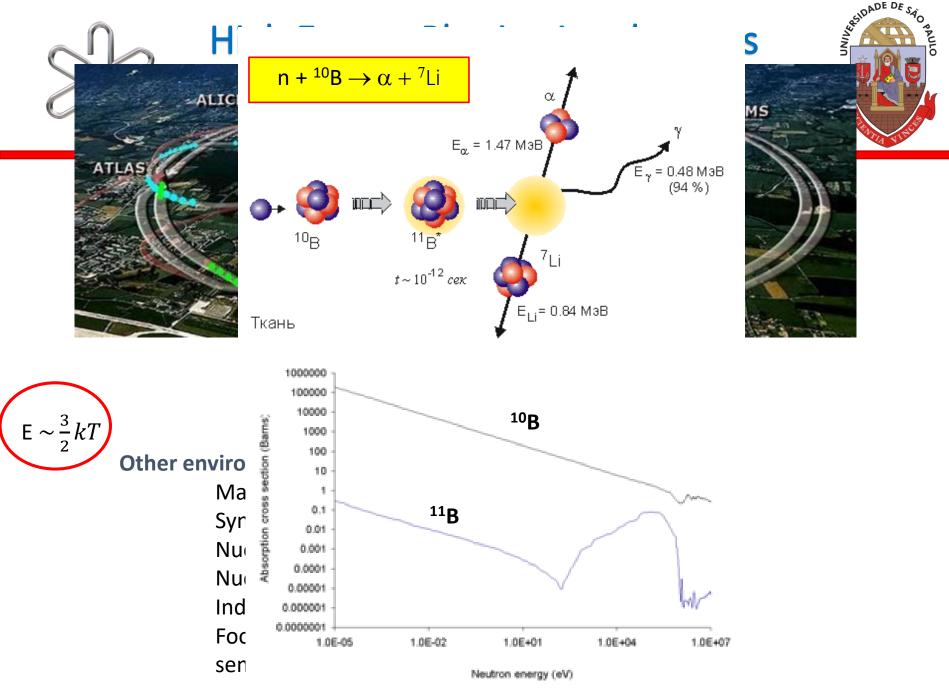

neutron + <sup>28</sup>Si E=14 MeV  $n + {}^{28}Si \rightarrow n + {}^{28}Si$  Elastic scattering  $n + {}^{28}Si \rightarrow p + {}^{28}Al$  $n + {}^{28}Si \rightarrow \alpha + {}^{25}Mg$

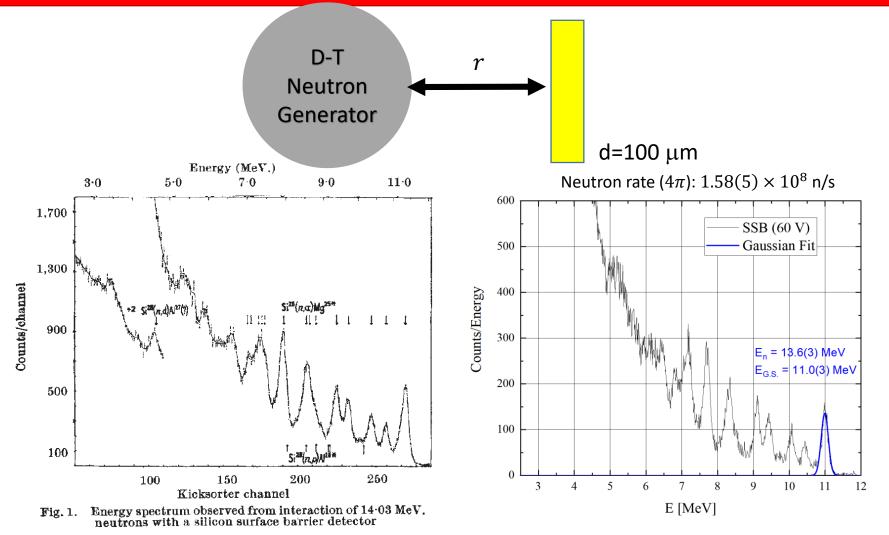

#### **Silicon Surface Barrier Detector**

W. M. Deuchars *et al.*, Interaction of 14-MeV neutrons with a Silicon Semiconductor Nuclear Particle Detector, Nature, 1961.

# Excited states of nuclear reaction channels

http://scienceblogs.com/startswithabang/2011/05/09/the-future-of-colliders-beyond/

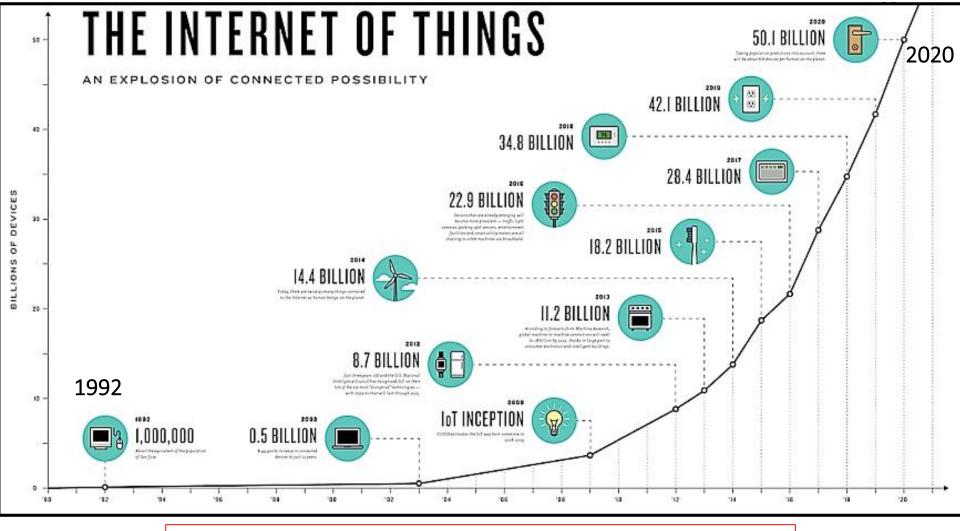

The number of transistors per chip increases exponentialy thanks to the exponential decrease of the transistor size.

Intel's Stratix-10 has the largest transistor count, containing over 30 billion transistors.

All the Electronic Devices May Suffer from Radiation Effects

Accelerator experimental hall Space Environment Ground High Radiation Environment α-particle emission from radioactive contaminants

> Particle and electromagnetic radiation Ionizing and non-ionizing dose

**Degradation of:**

Micro-electronics, micro-processors, optical components, semiconductor detectors, front-end electronics, cabling, etc

Causing: System shutdowns Circuit damage Data corruption, etc

#### Electromagnetic radiation, eletrons, protons, neutrons and heavy ions

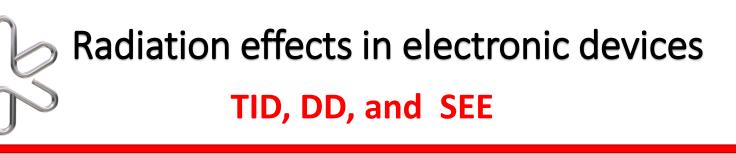

**Total lonizing Dose** is a cumulative effect caused by trapped charges in the oxide. These trapped charges modify the transistor characteristics such as threshold voltage  $(V_{th})$ , mobility, leakage current, power dissipation, etc.

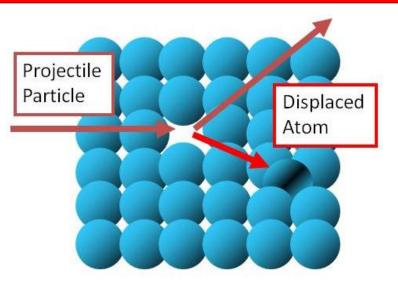

Atom Displacement Damage is provoked by protons, heavy ions, electron with high energy and neutrons, which change the arrangement of atoms in the lattice, modifying electrical properties of a device.

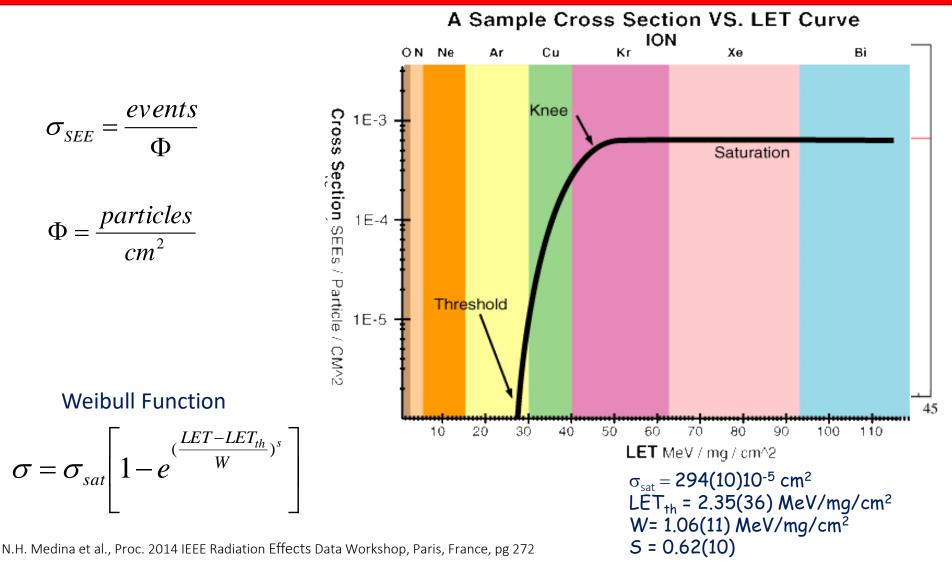

**Single Event Effects** are caused by particles of high LET (Linear Energy Transfer) due to, for example, the **strike of a single ion**. They can be non-destructive, causing current or voltage peaks, changing the state of a bit, or destructive, burning the device or destroying the gate oxide in a MOSFET.

# **Radiation Effects**

Total Ionizing Dose

Cumulative effect due to the ionization in the  $SiO_2$  due to neutrons, protons, gamma rays, X rays, heavy ions and electrons.

Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)

Applied voltage through the gate allows current to flow from source to drain.

Ionization in  $SiO_2$  creates electron-hole pairs which induces defects in transistors. These trapped charges modify the transistor characteristics such as threshold voltage ( $V_{th}$ ), mobility, leakage current, power dissipation, etc.

# **Displacement Damage**

1251DADE DE SA,

Non-Ionizing Energy Loss

Originated from nuclear interactions, typically scattering, which cause lattice defects. Displacement damage is due to a cumulative longterm non-ionizing damage from neutrons, protons, and electrons. The collision between an incoming particle and a lattice atom subsequently displaces the atom from its original lattice position

Stable defects in crystalline lattice (vacancies and interstices) modify electrical properties of electronic devices.

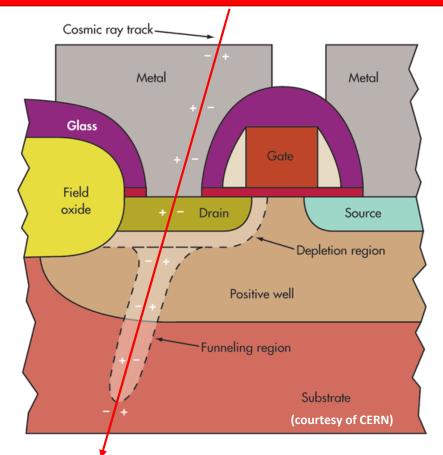

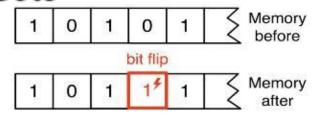

## Single Event Effects

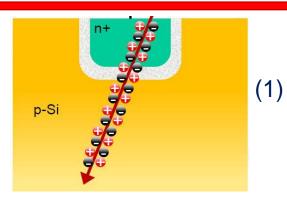

- Charge deposition induced by a heavy ion interaction within a sensitive volume, followed by the charge collection at the output node of the circuit.

- High-LET particles generates a track of electron-hole pairs in semiconductor (Si) and dielectric (SiO<sub>2</sub>).

- 1 MeV deposited  $\longrightarrow$  2.8 10<sup>5</sup> pairs

→ 44.5 fC

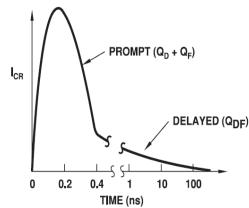

Charge collection occurs in three steps: drift (1), funnel (2) and difusion (3)

Adapted from [Gerardin, 2013] and [Schwank et al., 2008]

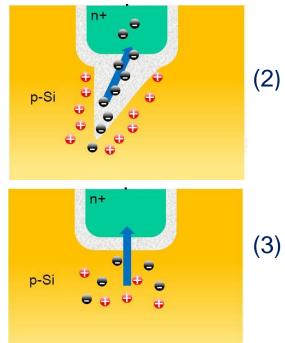

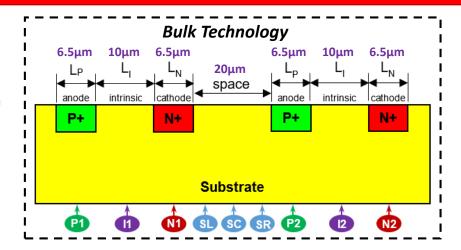

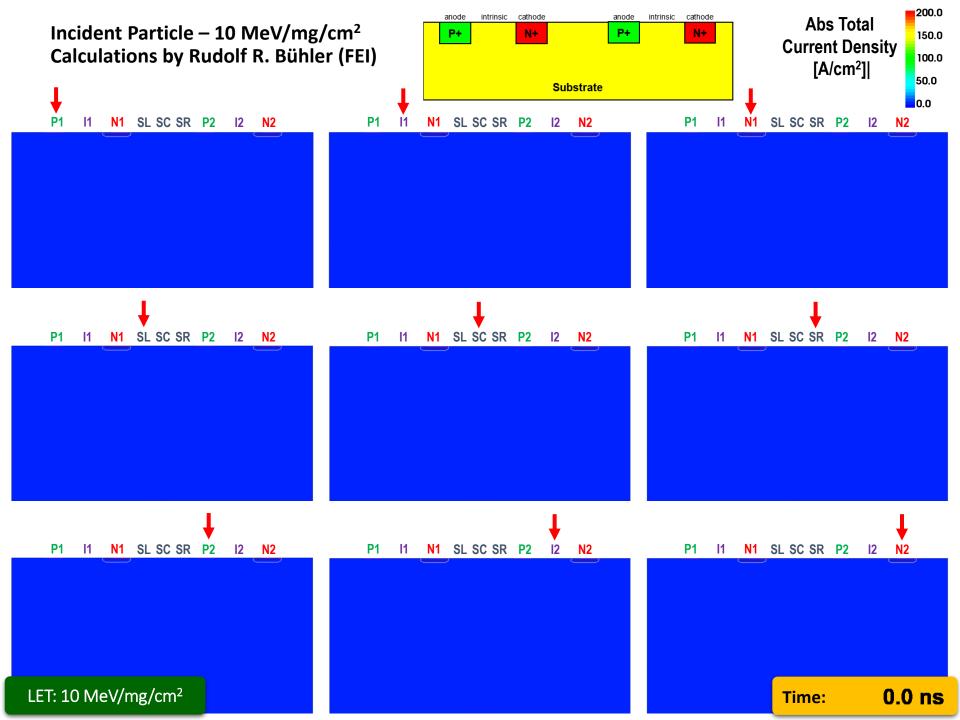

#### **PIN DIODE SIMULATION** GF BiCMOS 8HP 130 nm technology

#### **SEE Parameters:**

- Heavy-Ion LET = 10 MeV/mg/cm<sup>2</sup>

- Particles Strike vertically at specified positions

Rudolf R. Bühler and Renato Giacomini Centro Universitário FEI

# Single Event Effects

#### Non-destructive Effects

Single event upset (SEU)

e.g. memory bit-flip (logic error)

Single event transient (SET)

A transient effect (voltage/current pulses) which may provoke a SEU Single event functional interrupt (SEFI)

Logical malfunction in programmable devices

#### **Destructive Effects**

Single event latch-up (SEL) high current flux overheated power transistors, affecting *e.g.* CMOS devices Single event gate rupture (SEGR) dielectric breakdown of the oxide layer of a MOSFET Single event burnout (SEB) Similar to SEL. The high current damage irreversibly, *e.g.* power MOSFET

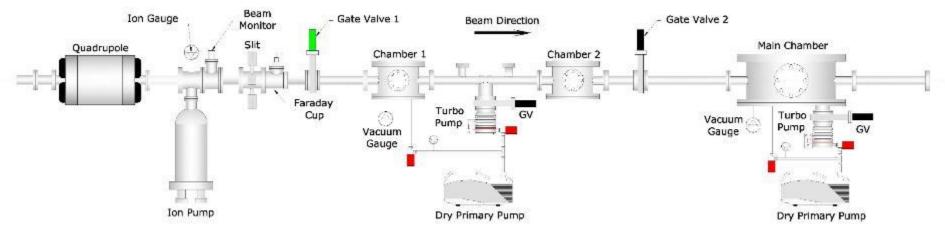

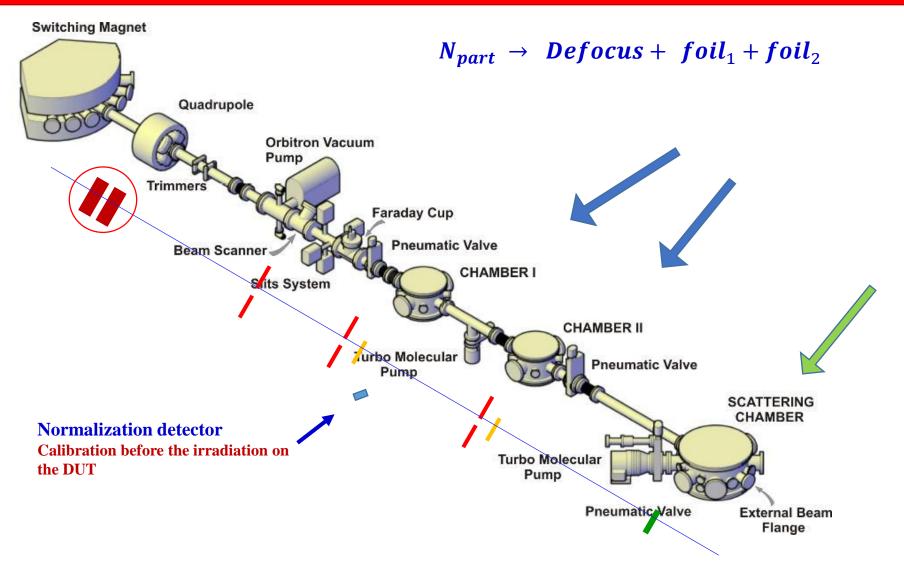

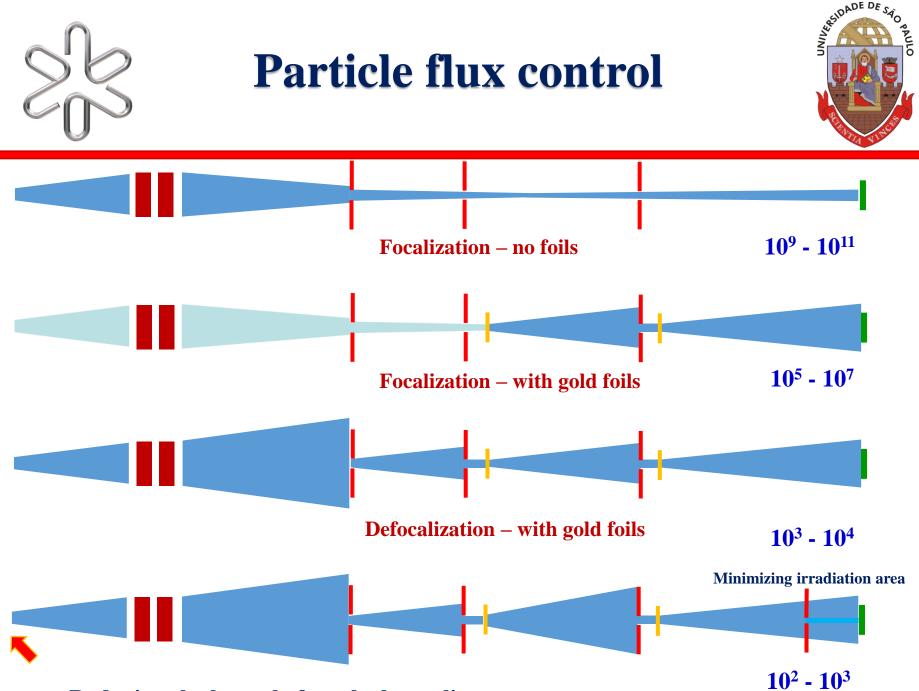

## New beamline for SEE tests

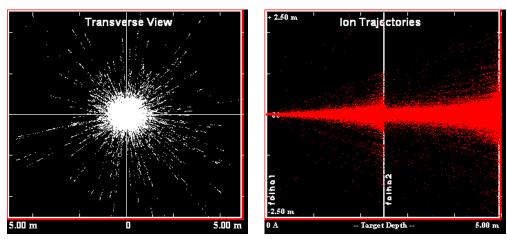

#### **Beam optics simulation**

#### **ESA requirements:**

Flux 100 to 100,000 part/cm<sup>2</sup>s Fluence 10<sup>6</sup> to 10<sup>7</sup> part/cm<sup>2</sup> < 10% uniformity variation 30 μm depth

ESCC Basic Specification n. 25100 – ISSUE 1 – October 2002 Vitor Aguiar, Tese de doutorado, IFUSP (2019)

#### **Beam Line Project**

Reducing the beam before the beam line

#### **Performed Measurements**

Analogic devices 3N163 transistors Power Transistors Pin diode Solar cells

Digital devices – Hardware and Software System On Module (SOM) Field Programmable Gate Array (FPGA) Processors Memories

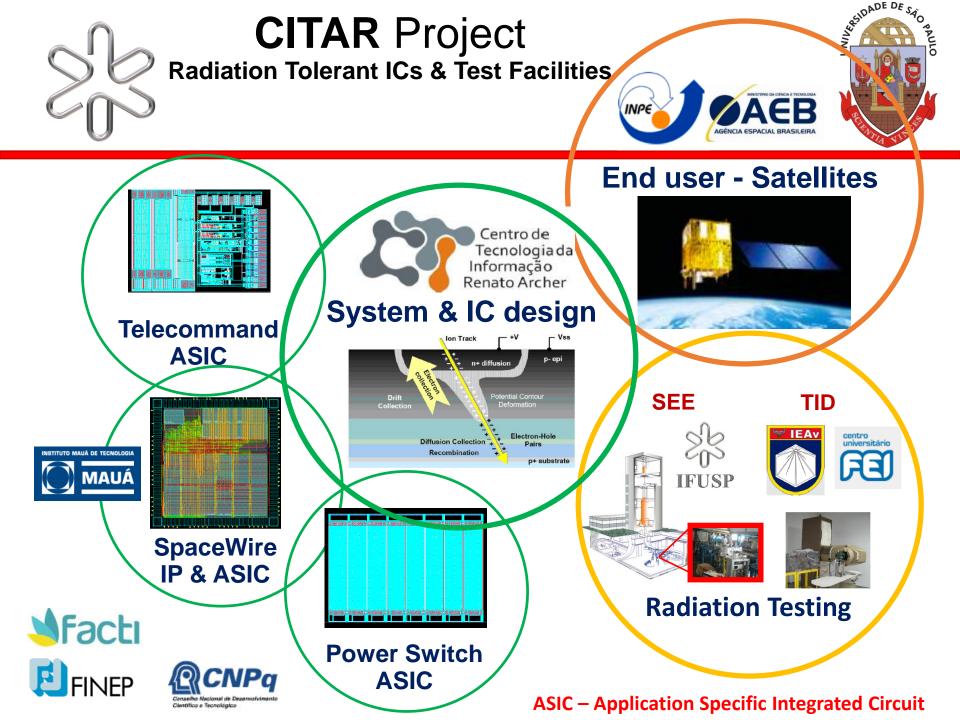

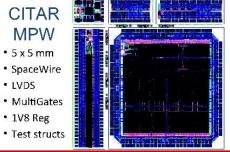

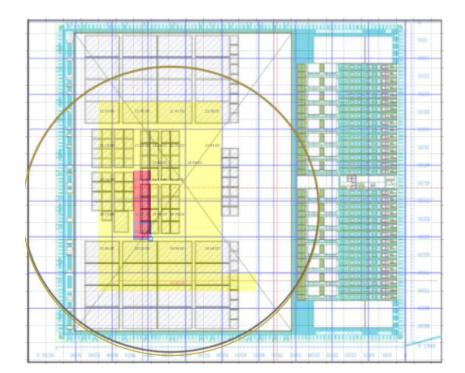

# SEU in SpaceWire ASIC chip CTI-USP-FEI Collaboration

Radiation tolerant chip developed to the Brazilian Space Agency (AEB) and INPE 180 nm technology

SpaceWire is a standard for high-speed links and networks for use onbord spacecrafts Interconection of: sensors, memories, processing units, and telemetry sub-systems

- Bit-flip tests in flip flop registers (SEU)

- Memory tests (mitigation techniques)

- SpaceWire communication

#### Results

No failures in the flip-flop registers with heavy-ion beams. Mitigation procedures worked properly for the SRAM memories. SpaceWire comunication is tolerant to radiation.

The SpaceWire chip was aged with X-rays up to 500 krad with no significant modification

Next steps – other tests with heavy ion beams ASIC tele command ASIC Power switch

D. De Lázari and S. Finco – Private communication

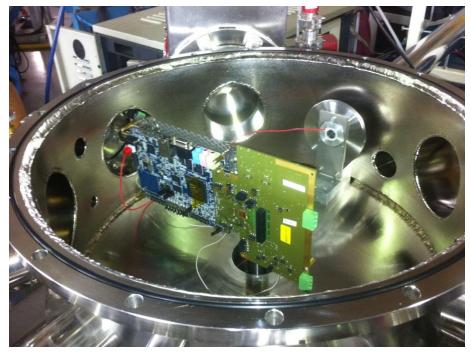

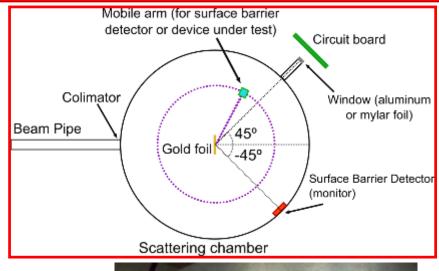

Scattering chamber

# Collaboration with UFRGS

#### Algorithm Tests

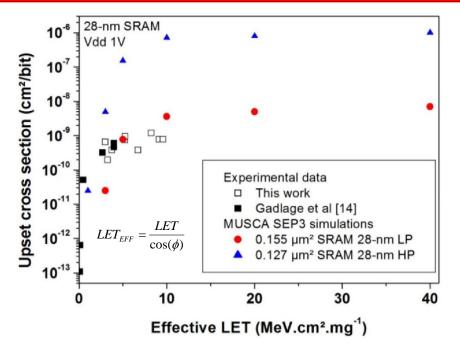

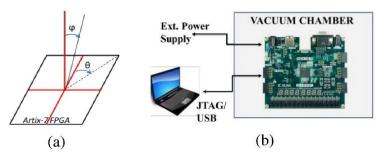

Analyzing the Influence of the Angles of Incidence and Rotation on MBU Events Induced by Low LET Heavy Ions in a 28nm SRAM-based FPGA

Fig. 1. In (a) Beam incident angle ( $\phi$ ) and rotation angle ( $\theta$ ) of the board in the vacuum chamber. In (b) the test setup for heavy ion testing.

- Reliability on ARM Processors Against Soft Errors Through SIHFT Techniques.

- Analyzing Reliability and Performance Trade-Offs of HLS-Based Designs in SRAM-Based FPGAs Under Soft Errors

- Heavy Ions Induced Single Event Upsets Testing of the 28 nm Xilinx Zynq-7000 All Programmable SoC.

J. Tonfa et al., IEEE Transactions on Nuclear Science , vol 64, n. 8., 2017

E. Chielle et al., IEEE Transactions on Nuclear Science, vol. 63, n. 4, 2016.

L. Tambara et al., IEEE Radiation Effects Data Workshop (REDW), 2015

L. Tambara et al., IEEE Transactions on Nuclear Science, vol. 64, n. 2, 2017

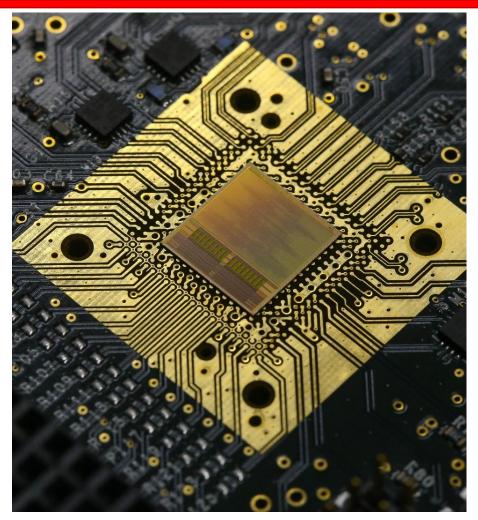

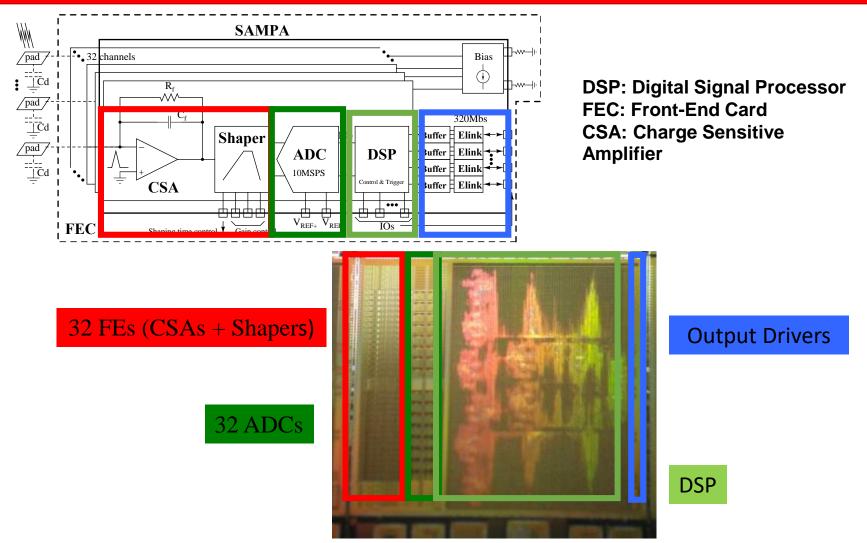

# SAMPA CHIP

- Upgrade of the Detection System of the ALICE experiment (LHC)

- Increase of about 100 times the Data Aquisition Rate.

- Brazilian Project: IFUSP (HEPIC), POLI (LSI) and UNICAMP

SAMPA Chip: The new 32 channels ASIC for the ALICE TPC and MCH upgrades J. Adolfsson et al., JINST 140P 1116 (2016) FAPESP Project n 2012/04583-8 and Project n. 2014/ 12664-3

## SAMPA CHIP

32 channel ASIC (Application Specific Integrated Circuits), CMOS 130 nm technology

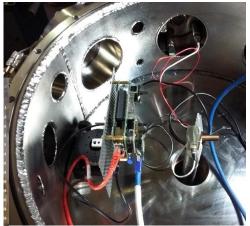

# Radiation Tests Proton and <sup>16</sup>O Beams

- The component will be subject to very high radiation doses in the ALICE experiment.

- Some complementary tests with proton beams were performed in the new beam line of the 8 MV Pelletron accelerator.

- Analogic systems (*e.g.* amplifier) were tested with <sup>16</sup>O beams to scan specific regions of the chip.

#### Scattering chamber

# **Radiation Tolerant Tests**

- The results indicate that one of the memories chosen in the initial project was too sensitive to radiation. These memories were changed to another version in the final chip project.

- These tests were crucial for the final chip design.

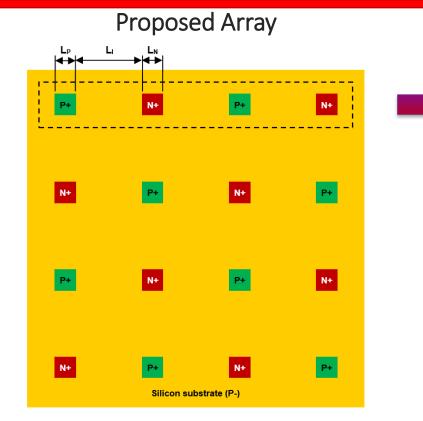

#### **Ultra-Fast silicon detectors**

The state of the art in the development of Ultra-Fast Semiconductor Detectors (UFSD) devices, that are capable of timing resolutions of few picoseconds, came with the introduction of Low Gain Avalanche Detectors (LGAD), a novel structure pioneered by the RD50 collaboration that incorporates a very thin intrinsic charge multiplication layer in order to fulfill the performance requirements for the High Luminosity-LHC (and beyond) experiments.

Based on the simulation results, the group will design and fabricate prototypes of LGAD and AC-LGAD sensors (and the equivalent PIN diode as a non-multiplication device reference), characterize and perform the irradiation of the sensors using the facilities available in Sao Paulo (Laboratorio de Sistemas Integraveis (LSI) from EPUSP, IFUSP and FEI).

The goal in this part of the project is to fully characterize the SAMPA chip and LGAD semiconductor sensors tolerance for radiation using different probes, from gamma and X rays to protons, neutrons and heavy ions. Nilberto H. Medina, Saulo Alberton, Vitor A.P. Aguiar, Nemitala Added, and Eduardo L.A. Macchione

Marcilei A. Guazzelli, Rudolf R. Bühler, Renato Giacomini, Roberto Baginski dos Santos and Alexis Villas Bôas

centro universitário

#### **SAFIIRA SYSTEM**

UNCE IMAN

# Thank-you for Jour attention

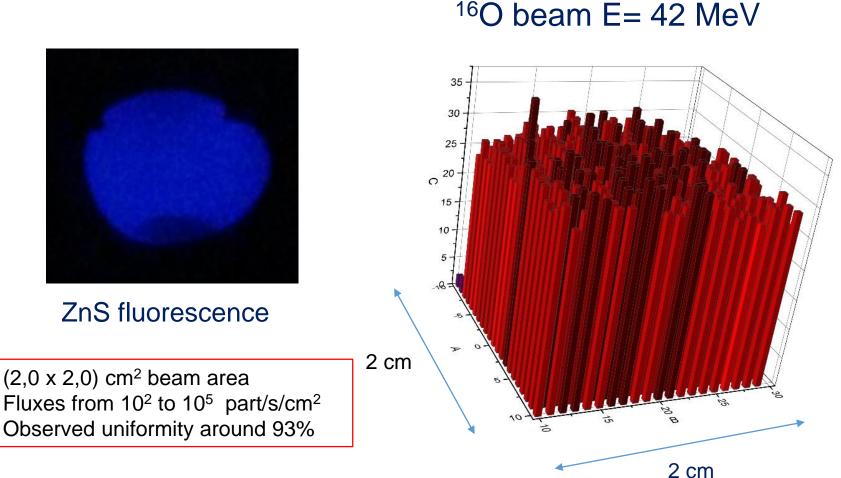

ESA beam requirements: Flux 10<sup>2</sup> to 10<sup>5</sup> part/cm<sup>2</sup>s < 10% uniformity variation

30B beam line

External beam setup

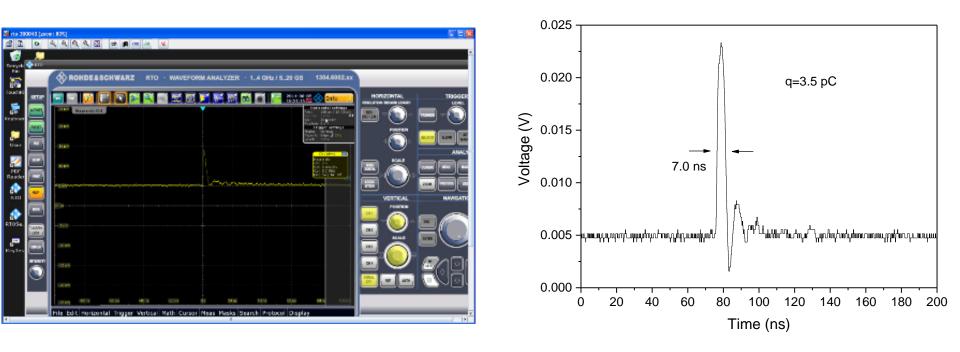

#### SEU measurements in a p-channel MOSFET transistor (3N163) USP-FEI Collaboration

#### SEU signal observed with an oscilloscope due to <sup>35</sup>Cl heavy ion beam at 75 MeV.

N.H. Medina et al., Jour. Nucl. Phys, Mat. Scie. Rad. Appl. v4 (2016) 13

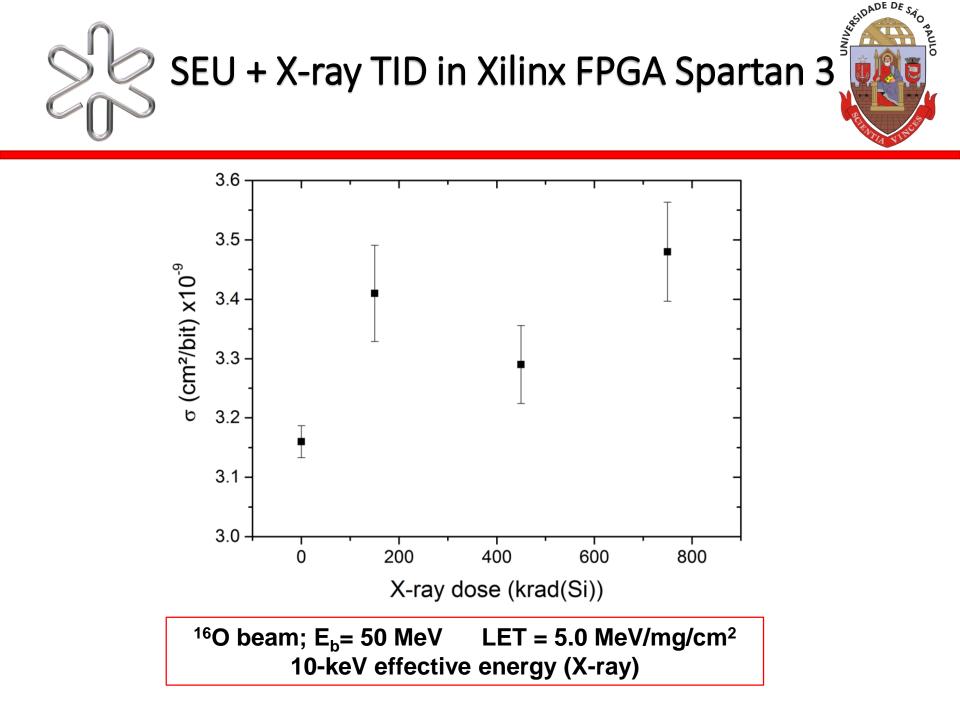

- Analysis of SRAM-Based FPGA SEU Sensitivity to Combined EMI and TID-Imprinted Effects

- Analysis of Single-Event Upsets in a Microsemi ProAsic3E FPGA

Industrial, communications and medical applications with commercial and industrial temperature devices. ProASIC3 FPGAs can be delivered with specialized screening for automotive and military systems.

SRAM – Static Random Access Memory

**COTS – Commercial Off-The-Shelf**

- ARM microcontroller Advanced RISC Machine

- Used in cellphones, calculators, computers, industrial applications

- **RISC Reduced Instruction Set Computer**

- FPGA Field-Programable Gate Array

J. Benfica et al., IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL. 63, NO. 2, APRIL 2016

P. Villa et al., 18th IEEE Latin American Test Symposium, 2017

# SEU in FPGA Microsemi ProAsic3 CTI-USP-FEI Collaboration

To study the basic characteristics when chips are submitted to heavy ion beam 130 nm technology

- Mitigation techniques

- FLASH and SRAM memories

- Flip-flop registers

#### 8UD Pelletron accelerator low flux

|    | lon Beam          | LET<br>(MeV/mg/cm²) |

|----|-------------------|---------------------|

|    | <sup>12</sup> C   | 3                   |

| or | <sup>16</sup> O   | 5                   |

|    | <sup>35</sup> Cl  | 17                  |

|    | <sup>107</sup> Ag | 40                  |

#### Results

Validation of error detection, correction algorithms and redundancy techniques Flash memory is radiation tolerant Failures in SRAM memories and flip flops Necessity to implement new circuits to become more tolerant Validation of the techniques to be used in the SpaceWire chip.

D. De Lázari and S. Finco – Private communication

#### **ASIC – Application Specific Integrated Circuit**

## **SAFIIRA** SYSTEM

SistemA de Feixes Iônicos para IRradiações e Aplicações Ion Beam System for Irradiations and Applications

# **Experimental Beam Uniformity**

ESCC Basic Specification n. 25100 – ISSUE 1 – October 2002