## Development of Silicon Interposers with Embedded Microchannels and Metal Re-distribution Layer for the Integration of Hybrid Detector Systems

<u>Miguel Ullán</u><sup>1</sup>, Jonathan Correa<sup>2</sup>, Vainius Dauderys<sup>1</sup>, Marta Duch<sup>1</sup>, Luis López<sup>3</sup>, Roser Mas<sup>1</sup>, Alberto Moreno<sup>1</sup>,

<sup>1</sup> Instituto de Microelectrónica de Barcelona (IMB-CNM, CSIC), Campus UAB, 08193 Barcelona, Spain.

<sup>2</sup> Deutsches Elektronen-Synchrotron (DESY), Notkestraße 85, 22607 Hamburg, Germany.

<sup>3</sup> European XFEL GmbH, Holzkoppel 4, 22869 Schenefeld, Germany

- Introduction and Framework

- Microchannel Cooling

- Embedded Microchannel Technology

- Technological process

- Microchannels

- Wafer bonding

- Initial Prototypes

- Current Objectives

- Technological process

- Metal with microchannels

- > Results

- Summary and Future Work

- In current HEP and other Physics experiments there is a need to keep the silicon detectors at low temperature (-10 °C to -40 °C)

- Leakage current increase with temperature and irradiation

- $\Rightarrow$  Power needs  $\rightarrow$  partial depletion  $\rightarrow$  inefficiency

- $\Rightarrow$  Thermal runaway

- Different solutions

- $\succ$  Air cooling

- Liquid cooling

- Bi-phase cooling

- Complex system integration (sensors, electronics, services)

- Larger heat densities

- Technology limits for pipe reduction and coverage

- Thermal connection with sensors and electronics

- Complex hybrid detector assemblies

- Scaling

- High power (heat) densities

- Heat transfer efficiency

- In HEP and other Physics facilities:

- Reduce material (radiation length)

- > Many thermal cicles + position resolution  $\rightarrow$  small (no) CTE mismatch

- Large areas to refrigerate (lower heat density)

- → Thermal Uniformity → Non-uniform heat removal "capilars"

- Assembly and integration needs

- Our work:

- Embedded microchannels basic technology development and prototyping

- Using the IMB-CNM technological capabilities (DRIE, wafer bonding, CMOS processing)

- DESY (Hamburg) in fluidic and thermal tests and system integration

- > X-FEL in simulations and design assessment

# Past Work

- In the past, we developed the technology of embedded microchannel cooling for High Energy Physics detectors

- N. Flaschel, et al. "Thermal and hydrodynamic studies for micro-channel cooling for large area silicon sensors in high energy physics experiments", NIMA, vol. 863, pp. 26-34, 2017. http://dx.doi.org/10.1016/j.nima.2017.05.003

- Ph.D Thesis: Micro-channel Cooling For Silicon Detectors. Nils Flaschel. Hamburg University. 2017

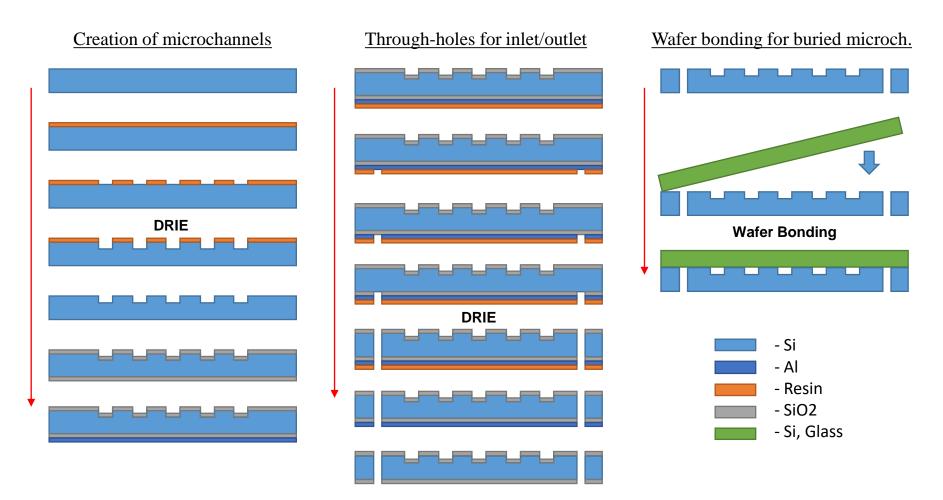

# **Technological Process**

• Technological steps for buried micro-channels at CNM

# Basic Technology: Microchannels

#### Creation of microchannels

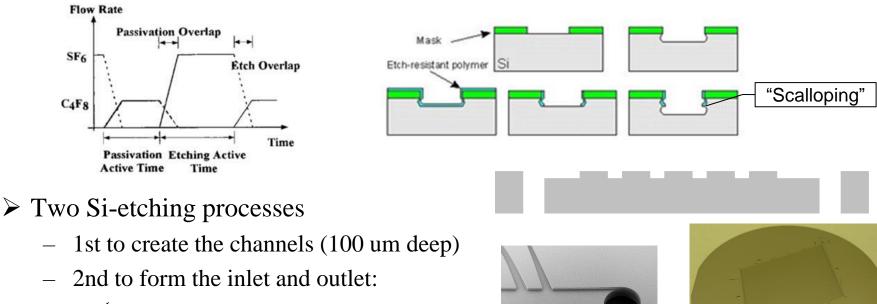

- Deep Reactive-Ion Etching (DRIE) (Alcatel 601 E)

- Chemical-Physical etch of silicon

- Very anisotropic  $\rightarrow$  high aspect ratio (deep and vertical holes)

- Bosch process: alternating between etching  $(SF_6)$  and passivation  $(C_4F_8)$

- ✓ Through hole

- ✓ "double-side" alignment

# Contro National Control Contro

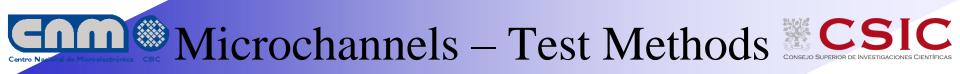

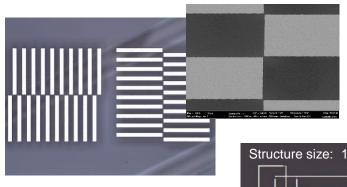

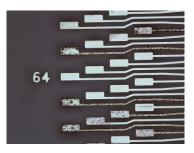

#### Microchannels evaluation

• Microscope – defect/yield analysis

- Yield analysis made on 10 wafers (49 channels/wafer = 490 ch)

- Several channels: Non-critical minor defects and dust

- Three channels: Blocking debris (can be cleaned)

- Seven channels: "Columnar" channel etch defect (not blocking)

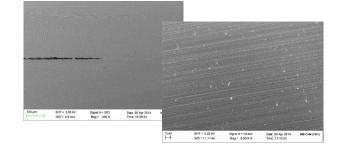

#### Micro-channels evaluation

• SEM (Scanning Electron Microscopy) (Zeiss Auriga 40)

# **Example 2** Basic Technology: Wafer Bonding

#### Wafer bonding (Süss Microtech Sb6e)

- Anodic: Borosilicate Glass Si

- High V (1000 V), Low T (~350 °C),

- PYREX<sup>®</sup>, MEMpax<sup>®</sup>

- The Micro-machining in the glass wafer

- Eutectic: Metal-Si

- Low T (~400 °C), Au

- ☞ Al?

- Fussion/Direct: Si-Si

- High pressure (2-8 Bar), Low T (~450 °C),

- Surface preparation is critical

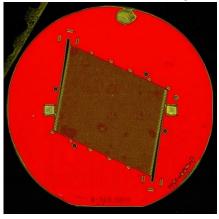

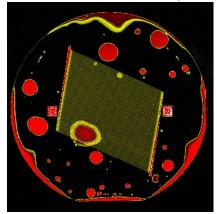

#### Wafer bonding evaluation

• SAM (Scanning Acoustic Microscopy) (Sonoscan-Gen5)

Anodic bonding:

Eutectic bonding:

Fusion bonding:

• Cross sections (Reverse engineering)

# **Initial Prototypes**

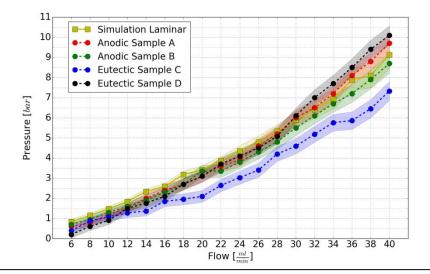

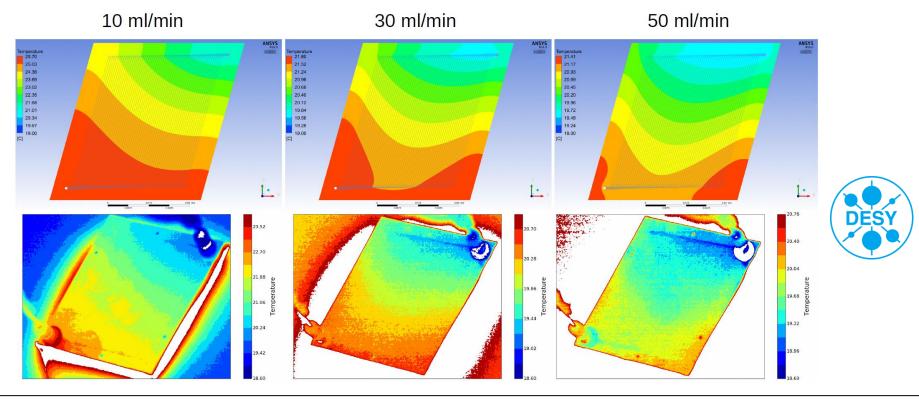

- Fluidic and thermal tests

- ➤ Laminar flow

- ➢ Good agreement with simulation

- Thermal homogeneity across the sample, < ±1 °C (for lowest flow rate)</p>

# **Current** Objective

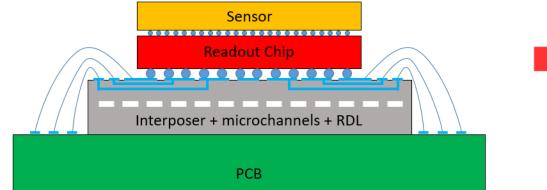

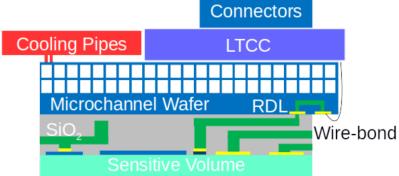

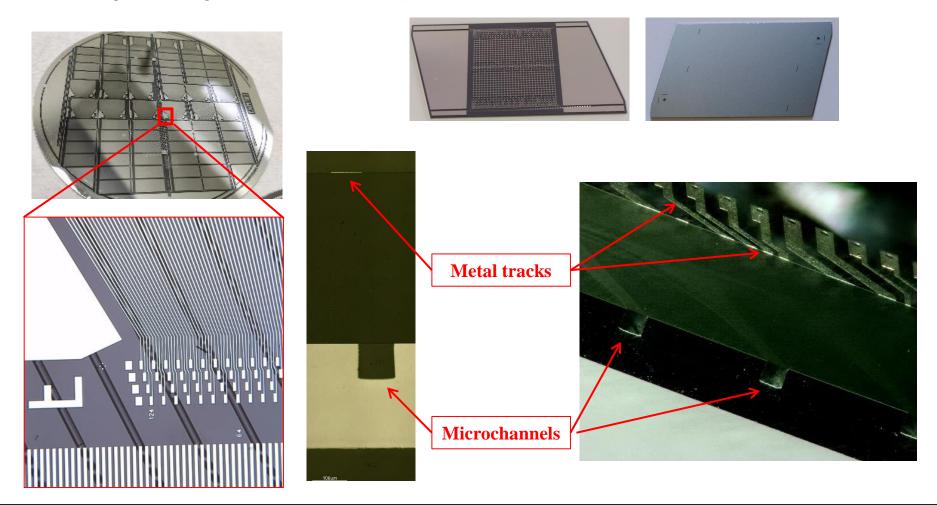

Integration of embedded micro-channels with metal Redistribution Layer (RDL) in silicon interposers

- Combining the cooling capabilities with the electrical connection of the detector hybrid assembly or monolitic detector with the backend electronics and outside world

- Both for signal and power routing

#### Hybrid assembly

#### Monolithic integration

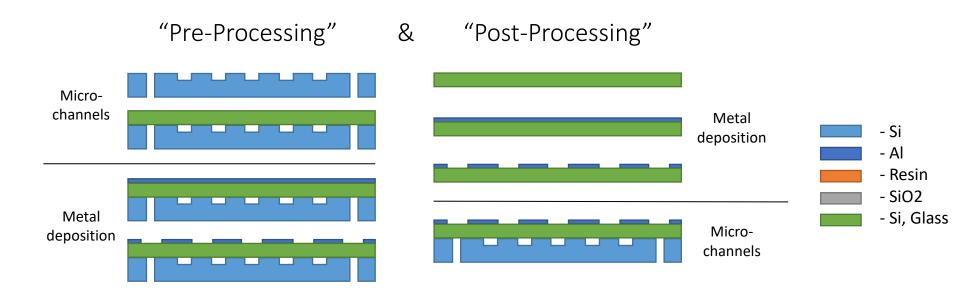

- Technological options

- Pre-processing: The microchannels are created first and then the metal is deposited on the assembly and structured with a photolithographic process

- Post-processing: The metal is deposited and structured first on a single wafer, then the buried microchannels are created by wafer bonding

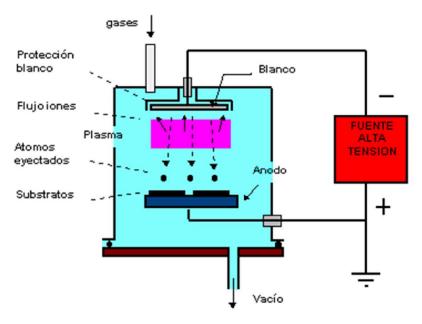

#### Metal deposition

#### • Sputtering process (Kenosistec KS800H)

- Sputtering system to deposit metallic layers

- ➤ Target used: Al (99.5%) / Cu (0.5%)

- ≻ Other targets available: Au, W, Ti, ...

- Better adherence than evaporation

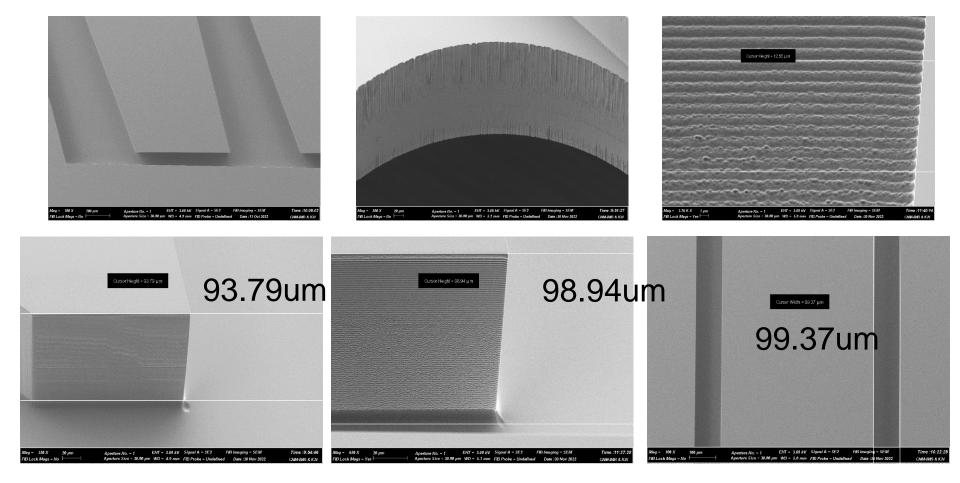

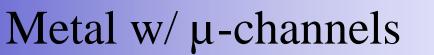

# $\underbrace{\textbf{Converted w/ } \mu - channels - Test methods \\ \underbrace{\textbf{Converted w} etal w/ } \mu - channels - Test methods \\ \underbrace{\textbf{Converted w} etal w/ } \mu - channels - Test methods \\ \underbrace{\textbf{Converted w} etal w} etal \\ \underbrace{\textbf{Converted w} etal w}$

#### Metal evaluation (in assembly with micro-channels)

- Four point probe Resistivity Measurement (Chang Min Four)

- Metal sheet resistance

| Al 1 um | Rs (Ω/□) | Rs St. deviation ( $\Omega/\Box$ ) |

|---------|----------|------------------------------------|

| A-11    | 33.1E-3  | 1.3E-3                             |

| A-13    | 42.3E-3  | 4.4E-3                             |

| A-14    | 42.3E-3  | 4.9E-3                             |

• Test structures (optical, CBR)

| A-20, Al 0.5um                     | Small (avg.) | Wide (avg.) |

|------------------------------------|--------------|-------------|

| Rs (Ω/□)                           | 62.74E-3     | 63.18E-3    |

| Rs St. deviation ( $\Omega/\Box$ ) | 3.44E-3      | 3.48E-3     |

| Weff (um)                          | 15.02E+0     | 24.32E+0    |

| Weff St. deviation (um)            | 236.31E-3    | 321.04E-3   |

# <u>Metal w/ µ-channels</u> – Test methods

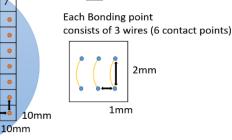

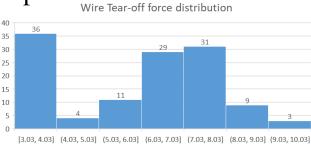

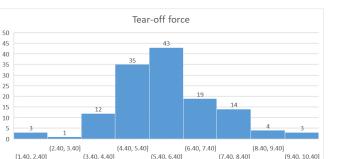

#### Metal evaluation (in assembly)

- Wire-bonding pull tests

- $\succ$  7x7 array, 3 wires in each point. 25 um Al wire.

- Test performed on **Pre-processing** blanket sample

- No parameter optimization

- Bonding on full wafer

- Final results on-going

- Test performed on **Post-processing** blanket sample

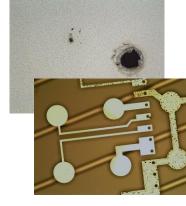

- The Bad adherence of Al layer on Silicon.

- Problematic wire-bonding & pull tests

- See optimization below

Bonding point

30

5

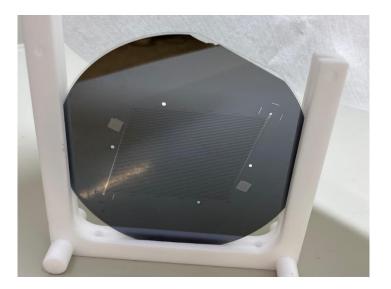

### **Current Status - Results**

• Successful integration of micro-channels in silicon interposers with integrated signal (RDL) – **Pre-processing**

## **Current Status - Results**

Process modification to place the metal on the Silicon side.

the glass wafer, inherent to the anodic bonding process

- $\geq$ Good metal results in blanket wafers

- Final assemblies and tests on-going

$\geq$

$\geq$

#### **Post-processing**

- Optimization of metal deposition process

- Better metal test results on blanket wafers  $\geq$

- Still some localized problems observed in the metal layer

Could be derived from the ion displacement within

$\geq$

- Technology for embedded microchannel fabrication demonstrated

- Fluidic and thermal simulations and tests of the initial prototypes

- ➢ Good hydrodynamic and thermal behavior

- ➢ In good agreement with simulations

- Successful integration of micro-channels in silicon interposers with integrated signal (RDL)

- Good tests results at the different technological steps

- Optimization needed for some technological alternatives

- Metal on Silicon

- Eutectic and fusion bonding

- Thermal and fluidic tests with new prototypes have started

- Working on further integration of microchannel cooling for a full system

- ➤ Exploring other technological options (microchannels on glass, TSV, ...)

- Full monolithic integration with CMOS processing

## Thank you for your attention

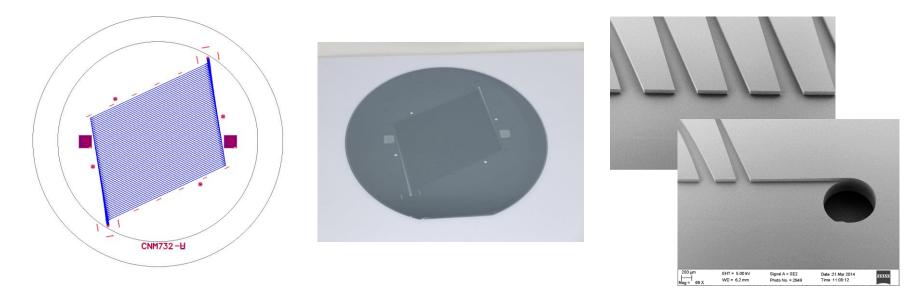

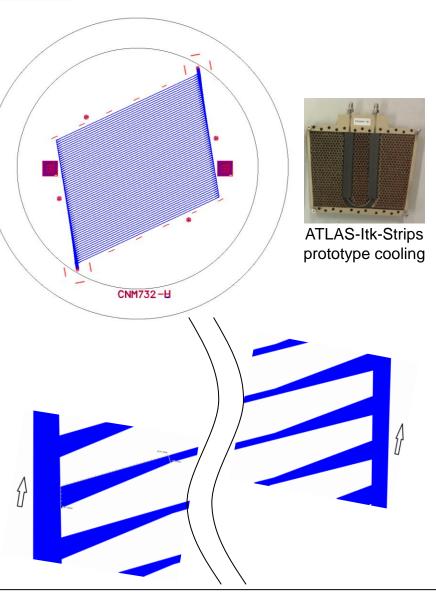

#### **Design Features:**

- Full 4" wafer ATLAS-prototype design

- Parallel flux

- Uniform heat removal

- ➢ 60 channels

- Width & depth 100 um, pitch 675 um, separation 575 um

- 15° inclination with respect to manifolds to facilitate flux

- Gradual channel inlet and outlet with 250 um initial width, and 2000 um length to facilitate flux

- Special manifold design developed by simulation to assure uniform flux

- 10° rotation to mis-align channels with respect silicon crystal lattice for mechanical stability

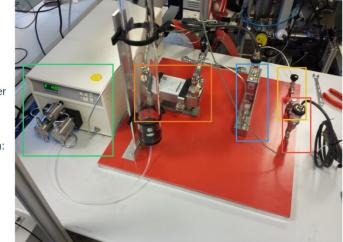

# Hydrodynamic tests

#### Setup

- Green: Pump

- Orange: Heat

Exchanger

- Blue: Flow Meter

- Yellow: Valve & Filter

- Red: Pressure Sensor

- Transparent column: Fluid Reservoir

#### Pressure vs. flow tests

- Simulation with laminar flow model

- Good simulation agreement with prototype A, B and D

- Most likely prototype C has some flow problems

- Critical pressure around 31 bar