### The DMAPS Upgrade of the Belle II Vertex Detector

#### Maximilian Babeluk

#### on behalf of the Belle II VTX collaboration

13th International "Hiroshima" Symposium on the Development and Application of Semiconductor Tracking Detectors

Dec 8<sup>th</sup> 2023

# The Belle II Experiment

ÖAW AUSTRIAN ACADEMY OF SCIENCES

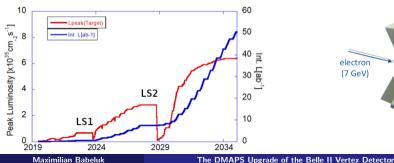

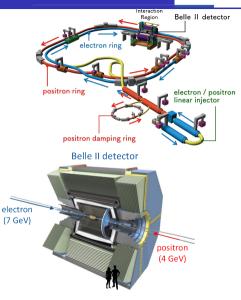

- Located at the SuperKEKB collider in Tsukuba/Japan

- Asymmetric  $e^+ e^-$  collisions

- $\sqrt{s} = M_{\Upsilon(4S)} = 10.58 \, \text{GeV}$

- World record peak luminosity, exploring new physics

- Currently: commisioning after Long Shutdown 1 (LS1)

- Restart early 2024

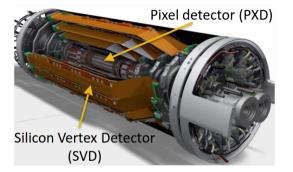

# The Current Vertex Detector

- Two technology system

- PXD:

- 2 Layers of DEPFET pixel sensor

- $\bullet~\sim 10\,\mu m$  spatial resolution

- 20 µs integration time

- ⇒ Cannot contribute to track finding

- See <u>PXD Talk</u> from Jannes Schmitz

- SVD:

- 4 layers of double sided strip sensor

- 3 ns Cluster time resolution

- 3% Occupancy limit (6% with hit-time reconstruction + BG rejection)

- Expected occupancy up to 4.7% after LS2 (large uncertainty)

- ⇒ Little safety margin in occupancy

- $\Rightarrow$  Trigger latency limited to 5  $\mu s$  by SVD readout

- See SVD Talk from Alice Gabrielli

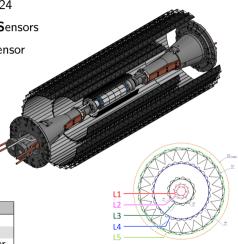

- $\bullet\,$  Planned for LS2  $\sim$  2028, CDR will be published early 2024

- 5 straight layers with Depleted Monolithic Active Pixel Sensors

- Identical chips on all layers: Optimized BELIe II pIXel sensor

- Different features enabled on different layers

- L1 & L2 (iVTX):

- All silicon ladders

- Air cooling (constrains power)

- L3 to L5 (oVTX):

- Carbon fiber support frame

- Cold plate with liquid cooling

|                   | L1   | L2   | L3   | L4   | L5    | Unit             |

|-------------------|------|------|------|------|-------|------------------|

| Radius            | 14.1 | 22.1 | 39.1 | 89.5 | 140.0 | mm               |

| # Ladders         | 6    | 10   | 8    | 18   | 26    |                  |

| # Sensors         | 4    | 4    | 8    | 16   | 48    | per ladder       |

| Expected hitrate* | 19.6 | 7.5  | 5.1  | 1.2  | 0.7   | $MHz/cm^2$       |

| Material budget   | 0.1  | 0.1  | 0.3  | 0.5  | 0.8   | % X <sub>0</sub> |

\*: Large uncertainties due to beam background extrapolation, possible changes in IR (interaction region)

# **OBELIX Key Requirements**

1. High hit efficiency at demanding hitrates with sufficient timesamping

- Matrix inherited from TJ-Monopix2

- See <u>CMOS Talk</u> from Lars Schall

2. Handling trigger latency of the Belle II experiment (up to  $10 \,\mu s$ )

- New implementation of digital periphery

- Simulation to validate performance

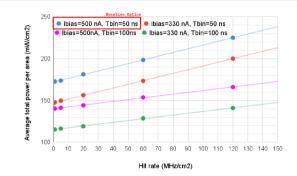

- 3. Power dissipation:

- air cooling of inner layers

- liquid cooling of outer layers

4. Little space for cables inside detector

Optimized digital logic with optional features

- On chip voltage regulators

- 2 LVDS downlinks for groups of chips (Rx)

- 1 or 2 LVDS uplink(s) per chip (Tx)

The DMAPS Upgrade of the Belle II Vertex Detector

# **OBELIX Optional Features**

5. Incresed timing resolution at expense of power

- Precision timing module in periphery (PTD)

- Offline timing annotation

6. Contribution to Belle II Trigger

#### **These features require significant power:** Only switched on for liquid cooled layers L3 to L5

ADEMY O

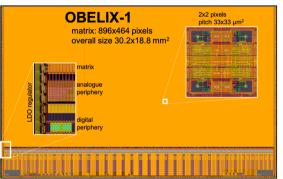

### The OBELIX chip

- Matrix inherited from TJ-Monopix2, size adjusted

- 464 rows and 896 columns

- Timestamp resolution:  $\sim$  50 ns

- Up to 10 µs trigger latency

- $\bullet \ \ \text{Power:} \ < 200 \ \text{mW}/\text{cm}^2$

- TID tolerance: 1 MGy

- $\bullet~$  NIEL tolerance:  $5\times10^{14}\,n_{eq}/cm^2$

- $\bullet\,$  Hitrates up to  $120\,MHz/cm^2$

- ⇒ Hitrate spikes due to injection background

- ⇒ Generous margin for all scenarios (optimistic, normal, pessimistic beam background)

#### Analog:

- Column drain architecture from TJ-Monopix2

- Monitoring ADC

- Temperature sensors

#### Power:

• On-chip LDOs

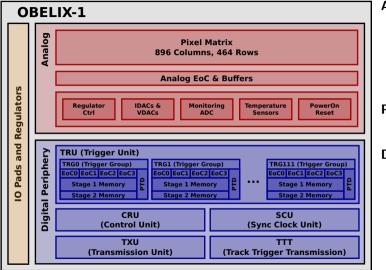

### Digital:

- TRU: Pixel readout, trigger processing

- PTD: Part of TRU for precision timing

- TTT: Fast transmission in parallel for contribution to Belle II Trigger

**₩** НЕРНҮ

Relle 1

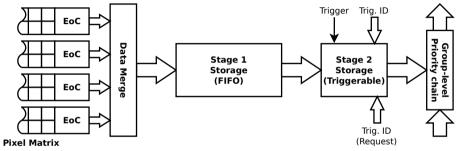

#### **OBELIX Trigger Group (TRG)**

- Trigger memory: 112 Tigger Groups, for 8 columns each

- Sophisticated 2 stage memory design

- Stage 1: Pre-trigger buffer SRAM, low power

- Stage 2: Associative memory to match trigger, power hungy

- Buffer sizing driven by power and hitrate, evaluated with extensive simulations

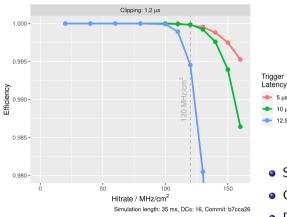

## **Trigger System: Simulations**

5 118 10 us 12.5 µs

- Simulation includes: clustering & charge/ToT conversion

- Calibrated with TJ-Monopix2 results

- Power 10% above budget for 120 MHz/cm<sup>2</sup>

- Clock frequency or analog bias current could be reduced

AUSTRIAN

CADEMYO

SCIENCES

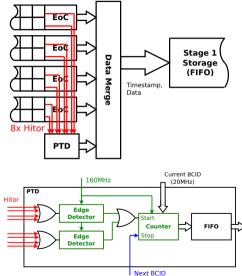

# Peripheral Time to Digital converter

#### **Pixel Matrix**

- Hitor: all comparator outputs of one column in an OR-chain (asynchronous)

- PTD: precision timing better than Timestamp (50 ns)

- Sampling: 2.95 ns period (169.7 MHz DDR)

- Power hungry feature: disabled in iVTX

- Little overhead when disbaled (Little die space, clock can be turned off)

- Resolution limited by timewalk and PVT (process, voltage, temperature) variation

- Calibration necessary

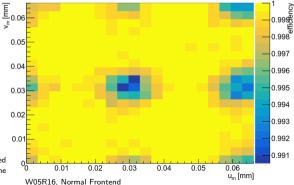

- First week: Regular measurements with telescope (efficiency and angular scans for depletion)

- Second week: Timing measurements, parasitic to RD50 MPW3 Testbeam

- Beamtelescope with Alpide chips (Duranta)

- Spatial Resolution  $< 10\,\mu m$  for all chips

| Chip SN           | Irradiation                        | Substrate            |

|-------------------|------------------------------------|----------------------|

| W02R05            | None                               | Epi                  |

| W05R16            | $p^+,~~5	imes 10^{14}~{ m n_{eq}}$ | Epi                  |

| W08R19            | None                               | Epi                  |

| W14R12            | None                               | Cz                   |

|                   |                                    |                      |

|                   |                                    |                      |

| Chip SN           | Frontend                           | Efficiency           |

| Chip SN<br>W05R16 | Frontend<br>Normal                 | Efficiency<br>0.9999 |

|                   |                                    | J                    |

|                   | Normal                             | 0.9999               |

The measurements leading to these and following results have been performed at the Test Beam Facility at DESY Hamburg (Germany), a member of the Helmholtz Association (HGF).

AUSTRIAN

CADEMY OF

SCIENCES

OA\

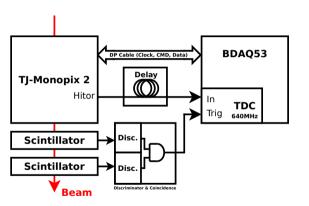

# Timing Measurement Setup

- TDC module of BDAQ53 firmware measures delay between scintillator and Hitor

- TDC words inserted into data stream

- TDC data is matched to hits offline

- Whole chip has one Hitor line: ambiguities arise

- ToT is measured by both, TJ-Monopix2 and TDC module

- Therefore used to match and cut  $(\pm 25 \text{ ns cut})$

AUSTRIAN

CADEMY O

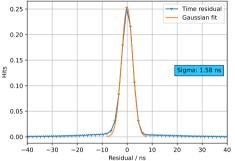

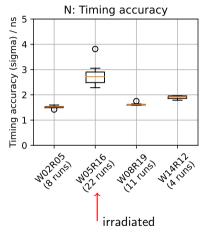

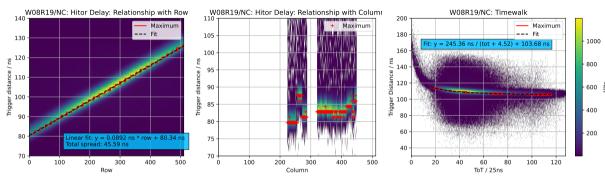

### Timing results

- Three corrections applied:

- Column delay (Hitor)

- Row delay (Hitor)

- Timewalk

- Tail in distribution: wrong associations

- Resolution: < 2 ns (unirradiated), < 3 ns (irradiated W05R16)

Maximilian Babeluk

# Summary and Outlook

- The OBELIX chip is based on TJ-Monopix2

- Additional features in OBELIX (all on-chip):

- Voltage regulators

- ADC and temperature sensors

- Trigger logic, up to  $10\,\mu s$  latency at  $120\,MHz/cm^2$

- Precision timing module

- Fast transmission for trigger contribution

- Development and verification is entering final stage

- Aiming submission early 2024

DESY TB Crew Summer 2023

**OBELIX Designers Meeting Fall 2023**

The DMAPS Upgrade of the Belle II Vertex Detector

### **Backup slides**

Maximilian Babeluk

The DMAPS Upgrade of the Belle II Vertex Detector

Dec 8<sup>th</sup> 2023 16 / 16

# **Timing Corrections**

#### • Iterative fit

• Halos caused by wrong associations

# Timing Accuracy Analysis

WIARIZ

₽

runs

(A runs)

- N: Normal Frontend ۲

- ٠ NC: Normal Cascode Frontend

- ٢ HV: High Voltage Frontend

- HVC: High Voltage Cascode Frontend

WIARIA

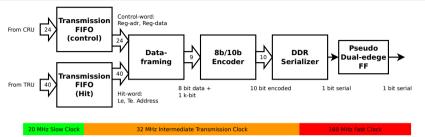

## Transmission Unit (TXU)

- Most TXU components run at 32 MHz (160 MHz/5) intermediate clock

- Serializer needs one byte (10 bit encoded, DDR) per 32 MHz clock cycle

- This allows simple state machines

- Clock boundary to 20 MHz clock is done via FIFO

- Hits are sent in frames sharing the same leading edge BCID

AUSTRIAN

CADEMY OF

SCIENCES