Development of high-time-resolution ASICs in CMOS 28-nm technology, dedicated to precision 4D-tracking

Adriano Lai INFN Cagliari HSTD13 Symposium, Dec 5<sup>th</sup> 2023

#### On behalf of

13<sup>th</sup> International "Hiroshima" Symposium on the Development and Application of Semiconductor Tracking Detectors (HSTD13)

- 1. Scope of this talk: High-intensity 4D-tracking (some specs)

- 2. Previous achievements (and limits) in HI-4D-tracking (*TimeSPOT*, 2018-2022)

- 3. Strategy for further steps (modularity, vertical integration)

- 4. First (and preliminary) results from **IGNITE** (started 2023)

- The term 4D-tracking can be and is used in a broad sense, to indicate tracking with time-sensitive pixels or pads

- In this talk we refer to 4D-tracking when this technique is necessary at the level of the **inner tracking detector** and in each pixel (no timing layers)

- Such kind of 4D-tracking start to be necessary in some setups of the **next generation of collider experiments**: in particular, LHCb-U2, HIKE (NA62 Upgrade), CMS Endcap (less stringently) and other possible envisaged detectors. The trend is foreseen to be kept and enforced in future circular colliders (if ever any)

- In this case, it is important to identify a set of key specific requirements, to be met all at the same time:

- 1. Pixel pitch: ~ 50  $\mu$ m with 99% fill factor

- 2. Time resolution: < 50 ps rms per hit on the full chain, even after irradiation

- 3. Radiation resistance: fluence >  $10^{16}$  1 MeV  $n_{eq}/cm^2$  (limited by electronics, CMOS 28-nm)

- 4. Sustainable rate per pixel: order (10<sup>2</sup>) kHz (low multiplicity of pixels per single TDC)

- 5. High output data bandwidth: order (10<sup>2</sup>) Gbps per 1 cm<sup>2</sup> ASIC

- 6. High performance at limited power budget:  $20-30 \mu$ W per channel

#### ... We can call it High-Intensity 4D-Tracking

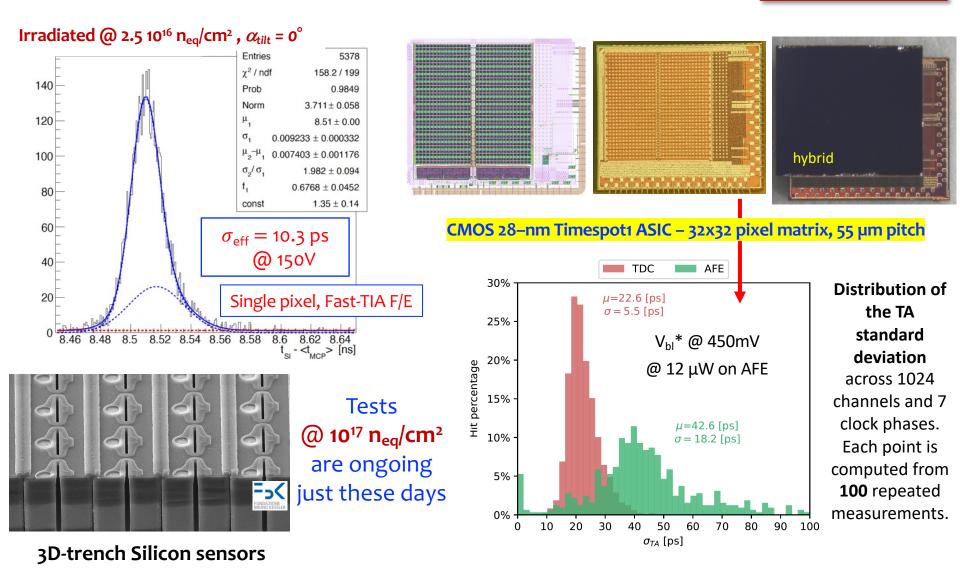

#### **Results on Sensors and Electronics for (HI)4D-tracking**

2018 – 2022

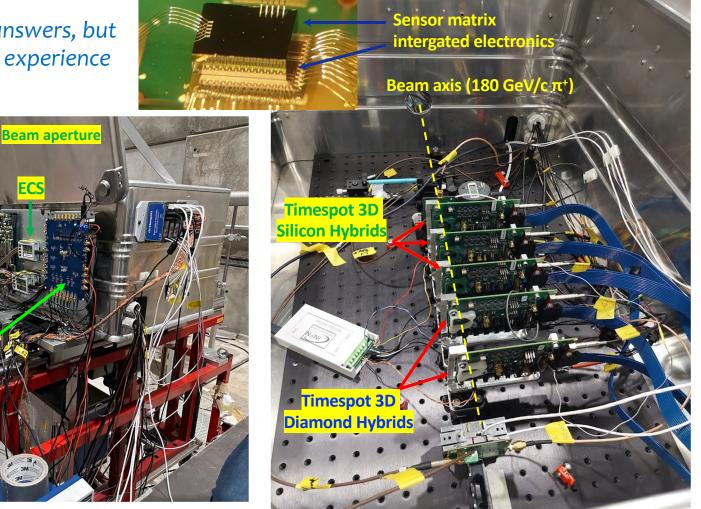

# TEST beam @SPS, May 2023

A mini-tracker demonstrator (5 stations)

More questions than answers, but extremely instructive experience

O KC705

Clock distributor

M. Addison et al., A Prototype 4D Tracker Demonstrator For Future Vertex Detectors, paper in preparation.

### Pixel electronics at high rates and high resolution:

### A major technical challenge!

Issues with our Timespot1 ASIC (small 32x32 device!) and 5 tracking stations:

Power distribution is critical (high voltage drop across the matrix, rate dependent)

**Clock distribution is critical**

$\rightarrow$  Both have impact on pixel time resolution at first order !

Relevant lack of uniformity in performance across the matrix

→ Difficult to have high and uniform performance at system level!

During the design phase, the full matrix simulation was heavy, difficult and time consuming

ightarrow Critical system verification during the design phase

How to face the design and implementation of a large tracking matrix (about and more than 2 cm<sup>2</sup>, 16 times larger) ? Furthermore: how to have it ready in the next 3-4 years ?

tracking quadrants of the 5 stations, containing the beam image

M. Addison et al., A Prototype 4D Tracker Demonstrator For Future Vertex Detectors, paper in preparation.

HI-4D-tracking ASICs – A. Lai – HSTD13 December 5<sup>th</sup> 2023

6

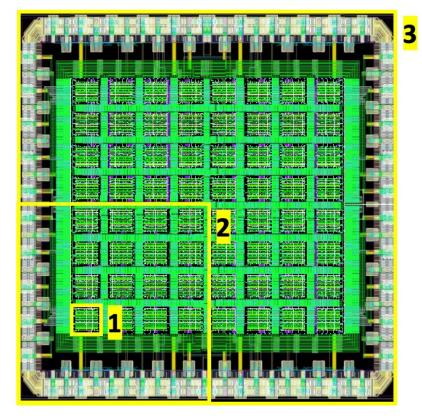

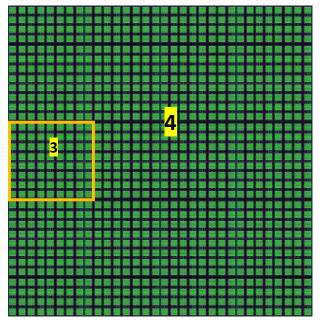

# Modular (fractal) design

Arrive to the result by single, simpler, consistent steps

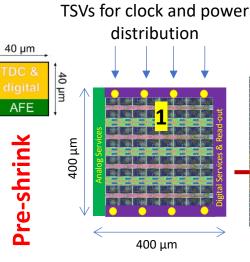

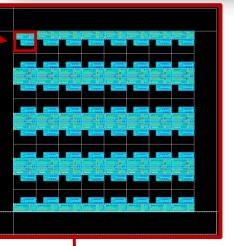

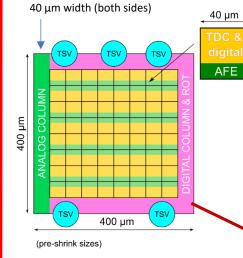

**Elementary Square** 8x8 pixels, (400 x 400 μm<sup>2</sup>). Each pixel integrates an Analog Front-End and a TDC er For 55 μm, corridor width ≈ 88.9 μm (80 μm post-shrink)

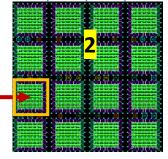

4x4 Squares form a **32x32 Matrix** (Timespot1 ASIC size, 55 μm pixel pitch and 1.76 x 1.76 mm<sup>2</sup> area). Corridors are partially "elastic" to allow different pitches 4x4 matrices form a **super-Matrix (64x64 pixels** ≈ 3.5 x 3.5 mm<sup>2</sup> for 55µm pitch). Next ASIC. Now under design

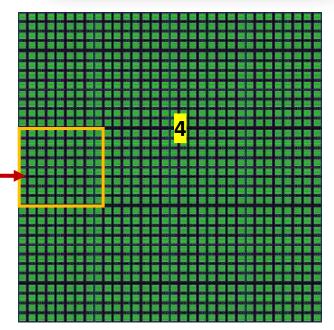

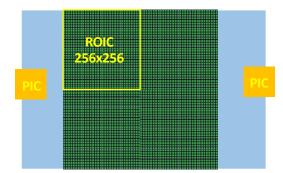

Full size ASIC. Different aspect ratios are possible by implementing different arrangements of the substructures (here a 256x256 pixels, 1.4x1.4 cm<sup>2</sup> ≈ 2 cm<sup>2</sup>). Global routing distribution remains structurally local by exploiting vertical connectivity.

### Modular (fractal) design Step 1, 2, and 3

4x4 matrices form a super-Matrix (64x64 pixels ≈ 3.5 x 3.5 mm<sup>2</sup>). This can reasonably be the size of a prototype MPW, to be tested also under particle beam after hybridization

- The large structure is based on the elementary Square (8x8), the Step-1

- Step-1 is a self-contained structure, exception made for the final stage of readout

- Step-3 is relatively easy by double-mirroring the Step-2 (32x32) structure

- Verification in Step-3 should imply only marginal additional efforts w.r.t. Step-2

- The Step 3 ASIC is conceived also for use in test beams to test prototypes of timing sensors having pitch of 55 µm or its multiples.

- Target time resolution: < 30 ps after full chain

- Submission Q3 2024

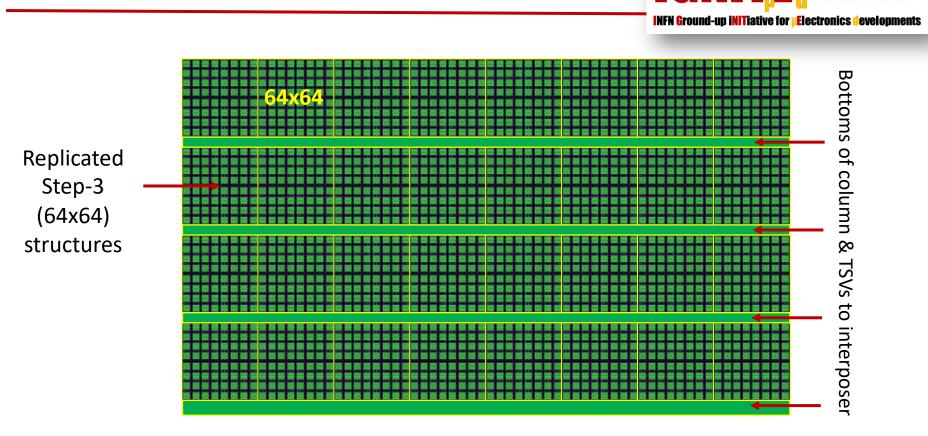

# **Modular (fractal) design** Step 4 (final)

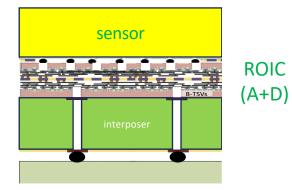

Full size ASIC (some cm<sup>2</sup>) Global routing distribution remains structurally local by exploiting vertical connectivity.

- Such assembly is conceivable only by abutment. The corridors, if any, are empty. Large use of TSVs is mandatory

- It requires a 3D-connected companion digital ASIC, which takes the place of the bottom-of-column services and is used to:

- 1. Distribute global lines in optimal way (autoroutes not mountain trails)

- 2. Integrate services (output buffers, power management circuits, HF serializers and drivers, possible additional fuctionalities for data reduction (e.g. clustering)

- In the absence of massive use of 3D interconnections, a more traditional architecture with periphery/end-of-column can still be used here. It is however evident the disadvantage in terms of:

- a. Routing congestion

- b. Locality breaking and severe hardening of verification operation

- c. Limitation in adding possible functionalities and programmability

- d. Integration of output stages (Serializers, Drivers)

# A back-up solution...

#### Example: 512x256 pixels $\approx$ 2.8 x 1.4 cm<sup>2</sup> (active area).

The BoC areas are gained by implementing a pixel pitch on the electronics side which is smaller than that on the sensor side. A RDL (re-distribution layer) on top metals re-aligns the two pitches. **TSVs are here necessar as well, but in a much less aggressive approach**

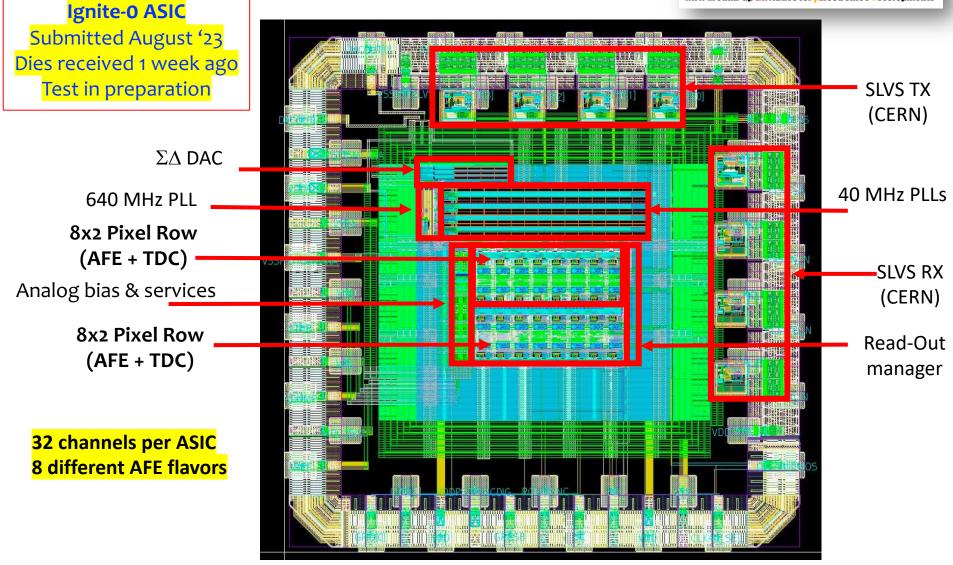

# Modular (fractal) design: Step-0

IGNITE INFN Ground-up iNITiative for Electronics evelopments

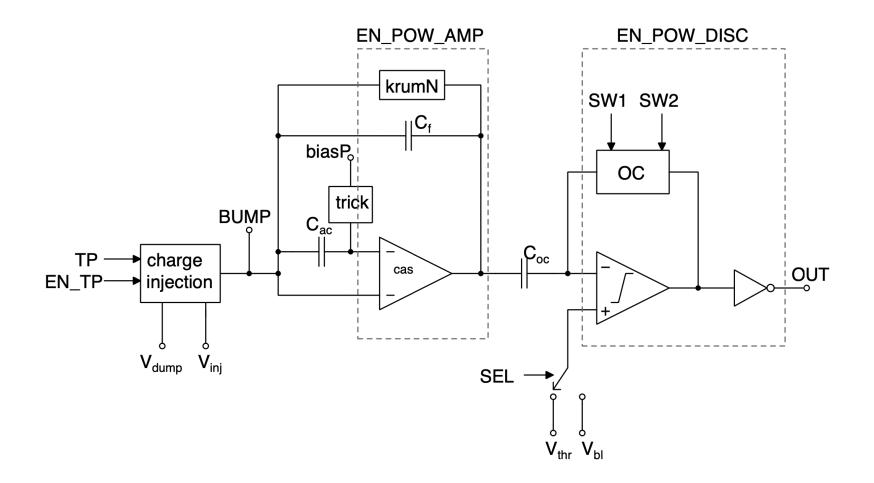

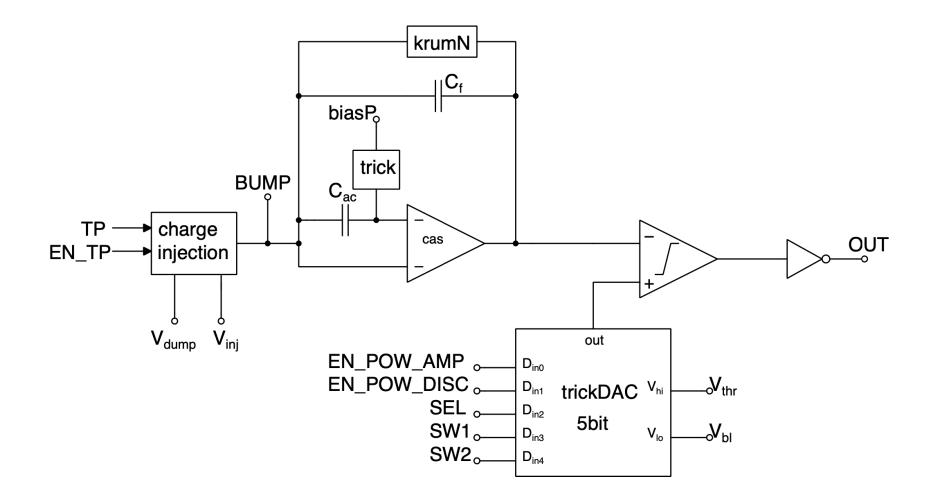

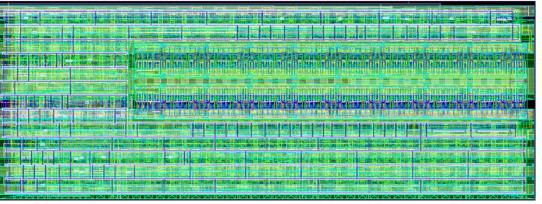

## Ignite-0: Analog Front End (AFE) Layout

- Area: 36µm×13.5µm (in figure: Offset Compensated version)

- Bias and power transmission: top metals ( $M_7 \rightarrow M_9$ ), horizontally, decoupled and filtered.

- Digital IO: bottom side in M3,M5, with digital buffers in analog domain.

- Sensor connection: AP, middle-bottom side.

- Encapsulated inside a 3-Nwell for substrate-noise insulation.

- Nominal power consumption: 10.8 μW per channel adjustable

Post-layout simulations

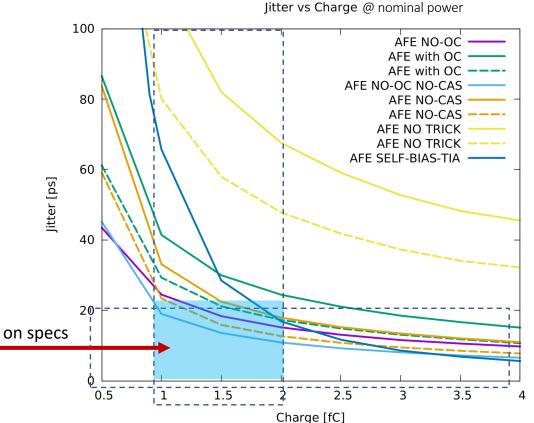

AFE performance (1)

- Power = 10.8 μW, C<sub>in</sub> = 100 fF

- MIP MPV 2 fC, but value considered is 1 fC. Indeed:

- $\rightarrow$  charge sharing can decrease the effective MPV  $\rightarrow$  also, it can vary with sensor geometry.

- The OC has a cost on power and resolution.

- The CAS (cascoded) core is sensitive to output loading.

- SELF-BIAS TIA: poor performance at low-charge\*, due to uneven threshold crossing.

\*(no discriminator was integrated for the self-bias in this version).

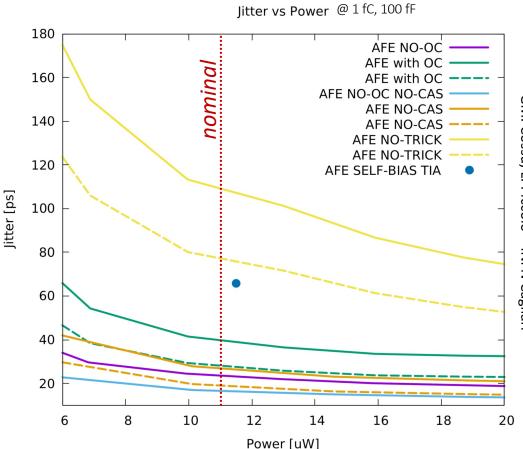

# AFE performance (2)

Post-layout simulations

**IDENTITY OF A CONTRACT OF A C**

- Q<sub>in</sub> = 1 fC, C<sub>in</sub> = 100 fF.

- SELF-BIAS TIA has fixed power (≈ 11 µW). The modest performance is due to the lack of a discriminator in this specific solution

- Pre-Amp and Discriminator power are varied to maintain performance.

- Nominal performance close to saturation → can still be tunedup.

- Some CSA options exhibits good performance at sub-nominal power.

- Power increase above nominal value does not help much in this specific (optimized) design

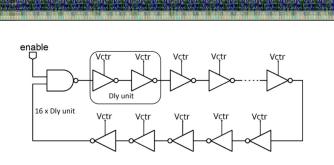

# **DCO & TDC: Layout and Performance**

#### **Vernier architecture**

#### DCO

- Size: 19.78 x 1.94 μm<sup>2</sup>.

- Number of Steps: 16 Delay Units

- Single delay cell with starved architecture

- Power on/off configuration

- fine tuning coarse tuning

- Decoupling capacitors

- Step controls: Fine ≈ 3ps & Coarse ≈ 50ps

- Period Range: ~ 900ps 780ps (Typical)

- **Power Cons.**: ~ 45 μA 55 μA (Typical)

- **Jitter**: ~ 750 fs 600 fs (Typical)

#### TDC

- Size: 27 x 9.9 μm<sup>2</sup>

- Resolution from post-layout simulation: ~ 12 ps (rms)

- Full custom design

- Particular care for power distribution as well as 40 MHz master clock distribution → important improvement in power w.r.t. the TimeSPOT version (> factor 10 !)

#### Power vs Event rate

| TDC status                     | Querent |  |  |  |  |  |

|--------------------------------|---------|--|--|--|--|--|

| TDC status                     | Current |  |  |  |  |  |

| OFF                            | 0.5 µA  |  |  |  |  |  |

| IDLE                           | 1.3 µA  |  |  |  |  |  |

|                                |         |  |  |  |  |  |

| Calib. DCO (Istant. @1.12 GHz) | 98 µ A  |  |  |  |  |  |

|                                |         |  |  |  |  |  |

| RUN (4.5 MHz)                  | 28.3 µA |  |  |  |  |  |

| RUN (1.0 MHz)                  | 7.5 µA  |  |  |  |  |  |

| RUN (500 kHz)                  | 3.9 µA  |  |  |  |  |  |

| RUN (333 kHz)                  | 3.0 µA  |  |  |  |  |  |

| RUN (200 kHz)                  | 2.3 µA  |  |  |  |  |  |

|                                | -       |  |  |  |  |  |

# Conclusions

### and next steps in preparation

- Pixel size is 40x40 μm<sup>2</sup> (pre-shrink, 36x36 μm<sup>2</sup> on silicon).

Compatible with sensor pitch from ≈ 40 μm to ≈ 100 μm

- Preparation of Step-1 (elementary Square) has started, by assembly of the elementary rows of Step-0 (after de-bugging). To be added:

- 1. Optimization of configuration registers

- 2. Triple voting strategy

- 3. Definition of services for the Analog (biasing and config) and Digital part (Read-Out Manager)

- 4. Definition and set-up number and position of TSV connections in the Square periphery (temporarily without implementing them)

- The 64x64 pixel matrix (2D) is planned for the 2<sup>nd</sup> half of 2024 as composition of 8x8 elementary Squares (total area ≈ 4x4 mm<sup>2</sup>)

- This ASIC should be usable as readout matrix for 4D-high-resolution sensors at test beams

- We aim at a full size ASIC (≈ 2 cm<sup>2</sup>) for 2026-27, by exploiting 3D vertical interconnections

- Will the «fractal» strategy of **IGNITE** solve the challenge for HI-4D-Tracking? We hope so!

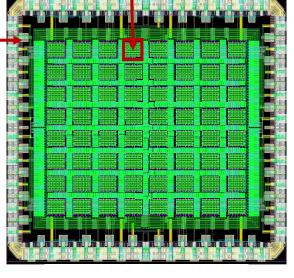

# Insights/Spares

### Effect of tilting on distribution shapes

normal working condition of a 3D in a detecting system

X [µm]

Single Pixel @ 50V

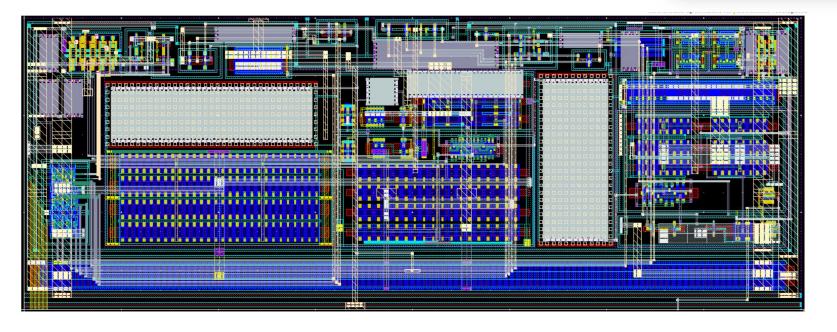

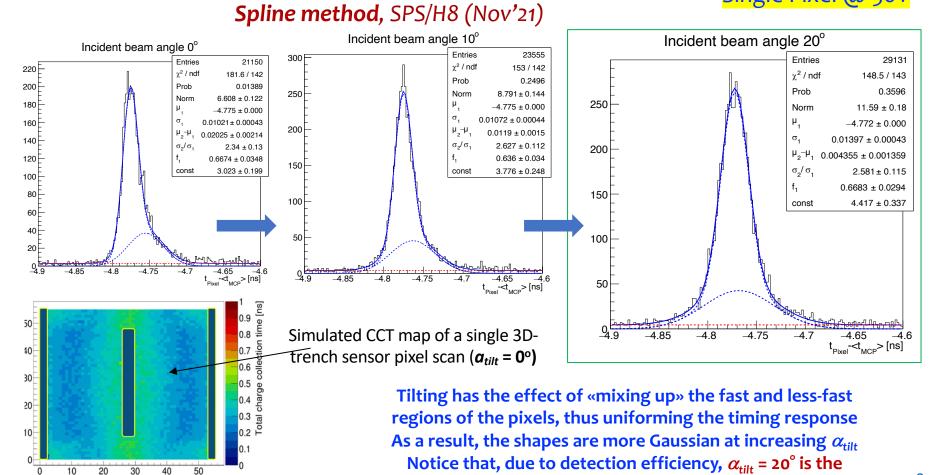

### **IGNITE** Fractal IC(s): tiles, 45 µm pitch and 55 µm pitch

NB: Pixel sizes with higher modularity (e.g. 110 µm) can be obtained by channel masking

40 µm

2023 Nov 2 Ľa: Ŕ T 28-nm Design(s) in CMOS **ICNITE**

#### Elementary Square 8x8 40 µm (36µm) pixels

- Digital and Analog columns are abutted

- PLLs for Local clock distribution are placed in the digital spaces between tiles. They serve a group of 8x8 tiles

- Digital spaces are also used to route output data towards periphery

|   |      |    |          |    |      |          |            |   | 0    |    |                     |     |              |     | Ð               |    | ¢          |     |        |    |         |     |        |    | Ð    |            |     |    |      |       | 9 |

|---|------|----|----------|----|------|----------|------------|---|------|----|---------------------|-----|--------------|-----|-----------------|----|------------|-----|--------|----|---------|-----|--------|----|------|------------|-----|----|------|-------|---|

| Ģ | 4    | 4  | ÷        | ÷  | 4    |          | $\Box_{2}$ |   | 4    | \$ | æ                   | -0  | 4            | -6- | $ _{e}$         | æ  | 4          | 6   | 0      | ÷  | 4       | 4   | 1.     |    | 4    |            | 4   | 4  | 4    | 6     | b |

| ο | -15- | ÷  | - 27     | æ  | 4    | -        | - 19       |   |      | ÷  | -                   | ÷   |              |     | -0              | 4  | -0-        | -   | æ      | æ  | -4-     | ÷   |        |    |      | -0-        |     | ÷  |      | 4     | 3 |

|   | - 45 | \$ | \$       | 6  |      | \$2      | -*         |   | a    | +  | Ð                   | Ð   | -            | 50  | Ċ.              | 4  | - 65       | \$> | \$     | G  | 0       | \$> | ø      |    | - 30 | -          | ø   | Ð  | -    | \$    | 0 |

|   | 3    | 6  | 0        | 0  | 7    | ÷        | 5          |   | 0    | b  | ð                   | ¢   | 9            | 6   | 6               | å  | 3          | 5   | 0      | 0  | 1       | 6   | 5      |    | 0    | 5          | đ   | ٩  | 0    | 6     | e |

| æ |      | 0  | è        | ÷  |      |          |            |   |      | \$ | æ                   | a.  |              | 6   | <sub>e</sub> ,  | à  | a          | 5   | 0      | ÷  |         |     | 1.     |    | -0   |            | æ   | a  | - 34 | 6     | ÷ |

| Ģ | -    | ÷  |          | 0  | 4    | -        | - 0        |   | -+   | -  | \$                  | ٢   | .,           |     | -0              | ¢  | -          | -   |        | ~  | 4       | -   |        |    | -+   | -          | 47  | ÷  | -    |       | 0 |

| o | 1    | ۲  | NP.      | 13 | 0    | 0        |            |   | 0    | 0  | 0                   | ÷   | ÷            | 130 | <b>.</b> ,      | e  | 10         | \$  | ÷      | 13 | 0       | 100 | 40     |    | 19   | 0          | X   | N  | ÷    |       | ò |

| a | 6    | ¢  | Q        | 9. | Ð    |          | -0         |   | 6    | 0  | 0                   | ø   | ÷            |     | , <sub>12</sub> |    | a          | 0   | φ      | ō, | æ       | 0   | - 23   |    | 10   | - m        | K.  | Ð  | ÷    |       | c |

| æ | -0   | 4  | ø        | ÷  | - 40 |          | -0         |   |      | -  | æ                   | 3   | -52          | _0  | ÷               | ė  | 4          | -0- | Q.     | ÷  | - 60    |     |        |    | _62  | -0         | æ   | 3  | -52  | _0_   |   |

| Ģ | - 0  | 2  | \$       | Ð  | -0   | Φ        | - o        |   |      | \$ | Q                   | ¢   | 0            | Þ   | ø               | 6  | -1         | 1   | •      | \$ | ą.      | ÷   | $\phi$ |    | -0   | ÷          | Q   | 0  | 0    | ->    |   |

| ø | 95   | Ð  | ۲        | () | ¢    | ¢        | Ð          |   | 0    | ¢. | Ð                   | 9)  | 39           | 19  | 0               | ġ  | 35         | Ð   | Ð      | () | ¢.      | ¢   | ø      |    | 0    | 0          | Ð   | 9) | 60   | 59    |   |

| ð | 4    | 4  | 9        | 10 | 1    |          | 20         | Ģ |      | 1  | 0                   | ŵ   |              |     | ¢               | ø  | 1.2        | 4   | Q.     | 1  |         | -   | ь      | Ф  |      | - 2        | e.  | 4  |      | 19 S. | c |

| - |      | 4  | ų,       |    |      |          |            | 0 |      |    | e.                  | 4   |              | 22  | ÷               | ¢  |            |     | ų,     |    |         | 4   |        | ę, | Ξ.   | - <b>(</b> | 6   | 24 |      | ΞZ.   | ¢ |

| φ | 4    | ÷  | b        | ×  |      |          | 45         | æ |      | 1  | 4                   |     | -            |     | Q               | Ó  |            | ÷   | i.     | ÷  |         | 1   | ş      | ٠  |      | 16         | 4   |    | 1    | ×     | ¢ |

| Q |      | 1  | 2        |    | 0    | 1        | 10         |   | H    | 0  | Q.                  | ×.  | æ            |     | a,              | 8  | đ.         | 40  | ×.     | N  | 0       | 1   | 45     |    | 0    | 10         | Q   | \$ | ф.   | 0     | a |

| 0 | 4    | ۰. | \$       | 5  | Ø    | 0        | 24         | Ģ | 9    | 0  | ×.                  | 2   | Ģ            | 1   | ø               | ¢  | 4          | Q.  | 2      | 3  | ð       | 6   |        |    | - 42 | 10         | 0   | 0  | 4    | U     | s |

| æ | 4    | ÷  | ŵ        | ŧ) |      | - 10     | -0         |   | - 42 | ÷  | æ                   | ą   | 4            | -0  | æ               | ¢  | a          | e.  | ę.     | Ę) | æ       | ÷   | e.     |    | -6   | ÷          | æ   | ą  | -0   | -0-   |   |

| Q | 4    | ¢  | ¢        | ŵ  | ŵ    | 4        | -0         |   | - +  | ÷  | ŵ                   | 6   | 4            | ÷   | ø               | ¢  | -0         | 9   | ð      | ŵ  | ŵ       | ÷   | ø      |    | -\$  | Þ          | ŵ   | 6  | ÷    | ÷     |   |

| Q | 43   | \$ | 3>       | 0  | 0    | ÷        | æ          |   | 0    | ٠  | Q                   | ٩   | 1            | e,  | e,              | ė  | Ð          | 0   | Þ      | 0  | 4       | 0   | ø      |    | - 3  | 6          | ç   | ¢) | 130  | 0     | 0 |

| Q | 4    | ÷  | Ŷ        | ٩  | 0    | 0        | ÷          |   | - 0  | ¢. | 0                   | ¢   | 4            | 4   | Q               | 2  | ø          | ę   | æ      | ٩  | 0       | 0   | Ģ      |    | - 4  | 0          | 0   | Q  | 4    | 9     |   |

| ą | -0   | 4  | ÷        | ÷  | 4    | ÷        | -0         |   | -5   | ÷  | æ                   | ą   | -4           | -0- | ÷               | ¢  | -3         | ą.  | $\phi$ | ÷  | 4       | ÷   | k)     |    | -4   | -          | æ   | ą  | 4    | -0-   |   |

| φ | 4    | Ż  | ¢        | ¢  | 4    | \$       | -0         |   | -\$  | ÷  | φ                   | Ŷ   | 4            | ÷   | Ф               | ¢  | 4          | Þ   | ¢      | ¢  | *       | ÷   | Q.     |    | ÷    | ÷          | ф   | ¢  | 4    | ÷     |   |

| Q |      | ٢  | 6        | 2  | Q    | Q.       |            | æ | 147  | ÷. | Q                   | ¢   | 4            | 63  | ē.              |    | -          | ÷   | Ð      | Ç6 | 0       | ÷¢  | 3      |    | 1    | ø          | 8   | 7  | 1    | 6     | 0 |

| 9 |      | ġ. | 1        | 2  | P    | - 62     | e.         | Ŷ | 0    | 0  | 0                   | Ŷ   | <del>Q</del> | Q.  | Ģ               |    | 1          | 9   | Q.     | 4  | 0       | 4   | ę.     |    | -42  | 0          | d.  | 4  | Ŷ    | 4     | 9 |

| Q |      |    | ł        |    | 2    |          | P          | φ | -    | +  | (Ť)                 | 0   | 4            | ÷   | Ð               | ¢  | 4          | 9   | ç,     | Ş  |         | \$  | ø      |    | - 4  | Þ          | (Ŧ) | \$ | ÷    | ÷     | Ð |

| Q | 4    | i. | R        |    | ÷,   |          | 9          | φ | -+   | ÷  | ÷                   | 4   | ¢            | Þ   | Ð               | ĝ  | 4          | ÷   | ÷      | Ð  | 4       | ÷   | Ŷ.     |    | -\$  | ÷          | ÷   | ¢  | ÷    | ÷     | £ |

| G | 727  | in | 22       | œ  | æ,   |          | <b>P</b>   | æ | 0    | Φ  | $\langle 0 \rangle$ | ٩   | 1            | ې   | ٩               | Ċ, | Ð          | ŝ   | Ð      | ې  | 4       | \$3 | ¢,     |    | 3    | 0          | 0   | ٩  | 1    | ې     | 0 |

|   | -    | t. | a in the | 66 | -    | <b>.</b> | 5          | æ | 9    | ÷  | ę                   | Ð   | 4            | ÷   | æ               | 8  | ø          | ÷   | æ      | ٩  | 9       | \$  | ę.     |    | 4    | e          | ę   | Ð  | 4    | ÷     |   |

| ¢ |      | ł  |          |    |      |          | P          | Ģ | -    | \$ | æ                   | Ģ   | -9           | ÷   | Ф               | 9  | -0         | \$  | Ŷ      | ٩  | 4       |     | ¢.     |    | -4   | ÷          | æ   | 4  | -0   | -0-   | Ð |

| ÷ |      | ł. | P        |    | à    |          | þ          | ¢ |      | ÷, | ÷.                  | 4   | -            | ÷   | Ð               | æ  | -1         | 2   | ¢      | ¢  |         | ÷   | 0      |    | -0   | ÷          | ÷   | 4  | - +  | ÷     |   |

|   | 15   | 5  |          | 6  | ò    | 63       | 10         | æ | 6    | ŵ  | \$                  | - 0 | 10           | 3   | e.              | ÷  | <b>1</b> 0 | \$  | 10     | 3  | $\odot$ | 0   | 5      |    | 3    | 0          | \$  | ø  | 10   | 3     | 6 |

#### 45 µm pitch sensor

- The 8x8 tiles fill the whole the chip Area. 40µ x 2 columns are left on the 2 sides for service circuits and TSVs

- 1024 channels area: ~ 2,5 mm<sup>2</sup>.

- 4k channels area: ~ 9 mm<sup>2</sup> + periphery

| and the second se |                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | * ************************************ |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                        |  |

#### 55 µm pitch sensor

- The 8x8 tiles don't fill the whole chip area

- Some "blockage" are needed to "stretch" the area.

- 1024 channels area: ~ 3.7 mm<sup>2</sup>.

- 4k channels area: ~ 16 mm<sup>2</sup> + periphery

### Final step(s) in development

A 4x4 cm<sup>2</sup> 2.5D-3D integrated module

#### Such module can be conceived as:

- A demonstrator for 4D-Tracking (LHCb, HIKE, CMS-Endcap + others)

- A perfect demonstrator following Falaphel developments

- A device for extensive characterization of timing sensors under development

- A module for a timing tracker

- In case of no need for timing, the analog layer can be different, but the companion digital layer could be made the same, by adding programmable/configurable facilities.

- Otherwise, the same 3D-integrated approach can be exploited even in a different ROIC, with great simplification in design and verification procedures