# Operational Experience and Performance with the ATLAS Pixel detector at the Large Hadron Collider at CERN

#### James Iddon on behalf of the ATLAS collaboration

HSTD'13, Vancouver

3rd - 8th December 2023

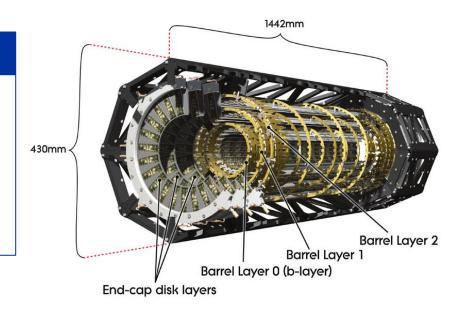

### **The ATLAS Pixel Detector: Barrel and Disks**

#### **Barrel and Disks**

- Three barrel layers, radii 5.5, 88.5, 122.5 mm

- Innermost layer known as B-Layer

- Total active area 1.45 m<sup>2</sup>, 67 M channels

- 2 x 3 end cap disks

- Total active area 0.28 m<sup>2</sup>, 13 M channels

- In operation since 2008

- FE-I3 front ends, C<sub>3</sub>F<sub>8</sub> cooling

#### Module

- 16 FE-I3 front end chips in 250 nm CMOS + one Module Control Chip

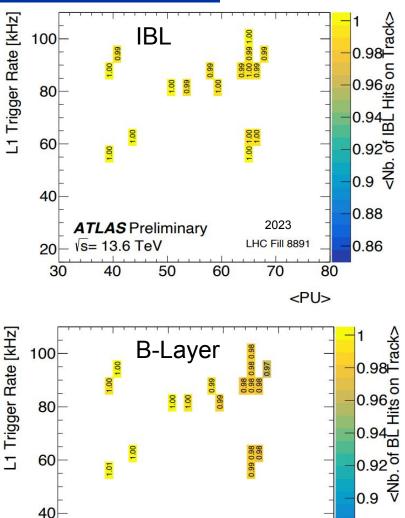

- 1 planar n-on-n sensor, 60.8 x 16.4 mm<sup>2</sup> active area, 250 µm thick

- 46,080 pixels per module, pitch of 50 x 400 μm<sup>2</sup>

- 8 bit Time-Over-Threshold information per hit

- Radiation hard to 50 Mrad, ~1 x 10<sup>15</sup> neq cm<sup>-2</sup>

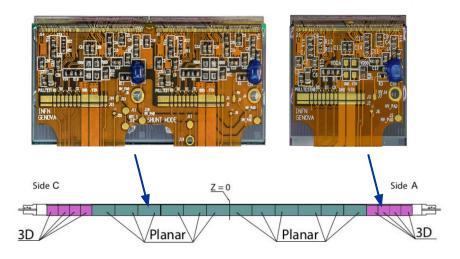

### **The ATLAS Pixel Detector: IBL**

#### **Insertable B-Layer**

- Insertable B-Layer (IBL) inserted in 2013 2014 LHC shutdown (Long Shutdown 1), adding a 4th barrel layer

- 14 staves, each at radius 3.35 cm •

- Total active area 0.15 m<sup>2</sup>, 12 M channels •

- 448 FE-I4 front ends,  $CO_2$  cooling Radiation hard to 250 Mrad, ~ 5 x 10<sup>15</sup> neq cm<sup>-2</sup>

#### **Front End and Sensors**

- n+-in-n and n+-in-p for planar and 3D sensors

- FE-I4 in 130 nm CMOS

- 200 / 230 µm thick

- 26,880 pixels per FE-I4, pitch of 50 x 250  $\mu$ m<sup>2</sup>

- 4 bit Time-Over-Threshold information

s = 8 TeV

<u>s = 13 TeV</u>

2012 pp

2016 pp

2018 pp

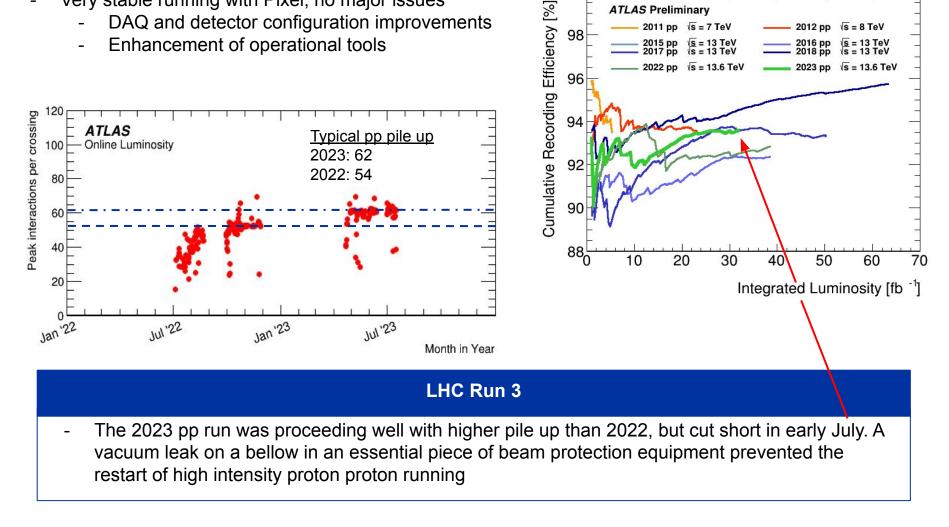

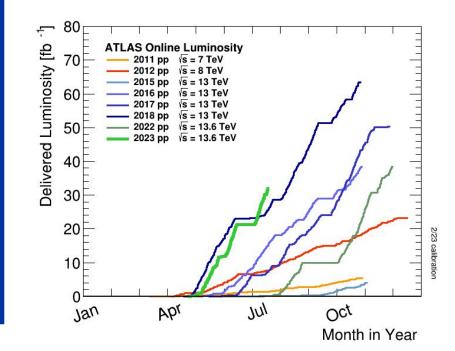

### **Pixel Performance Overview Run 3**

- 99.8 % data guality efficiency for Pixel in Run 3

- Average deadtime of 0.4 % for 2023 pp

- Very stable running with Pixel, no major issues

- DAQ and detector configuration improvements

- Enhancement of operational tools

100

98

ATLAS Preliminary

2015 pp

2017 pp

2011 pp \s = 7 TeV

s = 13 TeV s = 13 TeV

# Operational Challenges and Mitigations

### **Operational Challenges**

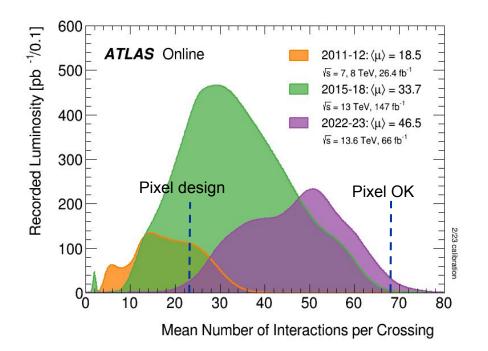

#### Pile up

- Original Pixel designed to cope with average pile up, <µ>, of 23

- Pixel measured to cope with <µ> of 68.5, with the aid of DAQ and detector configuration optimisations

- Legacy detector pushed to within a factor 3

<µ> of forecast for HiLumi LHC trackers

#### **Radiation Damage**

B-Layer is designed to cope with 1 x  $10^{15}$  neq cm<sup>-2</sup>, 50 Mrad. By the end of Run 3, expected fluence and dose will be  $1.5 \times 10^{15}$  neq cm<sup>-2</sup> and 63 Mrad respectively

All other layers will be within design limits

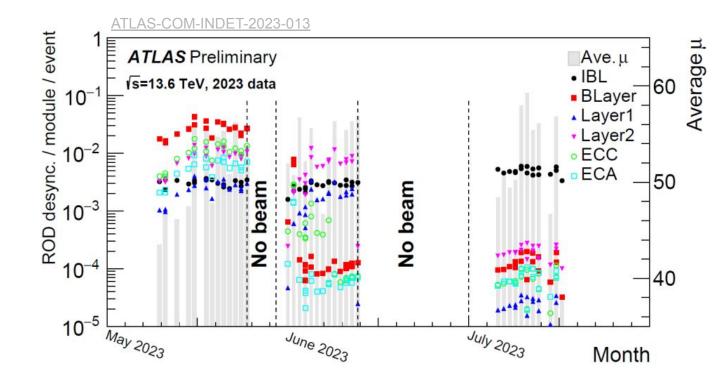

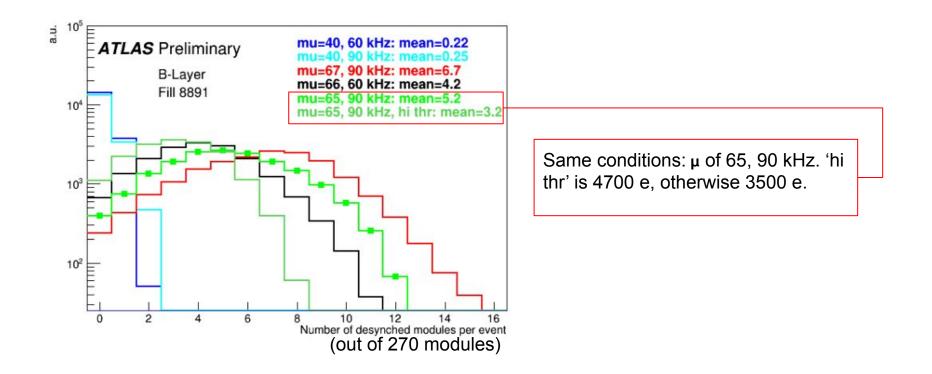

### Handling Higher Pile Up: Smart L1 Forwarding

- Pixel and IBL modules can only handle a maximum number of triggers at a time

- An extra trigger causes the module to be desynchronised until the next ATLAS Event Counter Reset (ECR), every 5 seconds

- Smart L1 Forwarding Firmware loaded in the Read Out Driver (ROD) keeps track of triggers propagated to each module, and does not propagate a new trigger if the module is already handling the max number of triggers

- Only a few events are lost, and the module stays synchronised

Smart L1 FW deployed in stages throughout Pixel in 2023. Order of magnitude reduction in desynchronisation. In development for IBL.

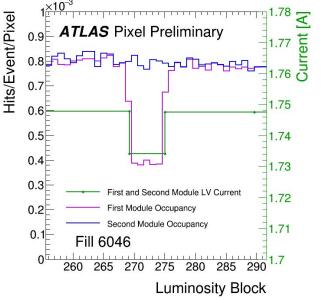

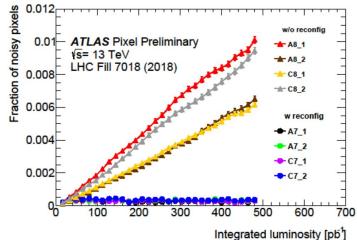

# Handling SEEs: reco@ECR

- The front end chips are susceptible to Single Event Effects (SEEs)

- In Run 2, global registers in IBL were reconfigured every ECR

- In 2023, IBL pixel registers are reconfigured every ECR, such that every register is configured within 11 mins

- Also global registers in Pixel are reconfigured every ECR

- Significant reduction in noise and silent pixels in IBL, with no additional deadtime for ATLAS since it happens within the 2ms gap

SEEs in local pixel latches can result in increase in noisy or quiet pixels

SEU in FE-I4 global register results in drop in occupancy and LV current for one module

<u>Measurements of Single Event Upset in ATLAS IBL</u> <u>ATLAS-COM-INDET-2020-005</u>

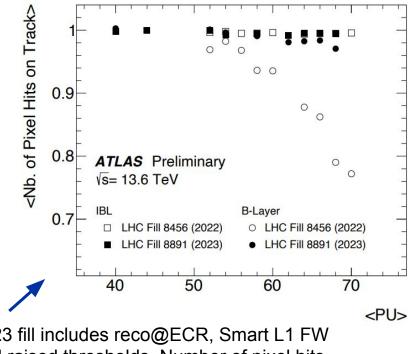

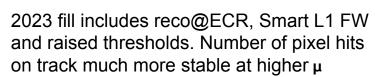

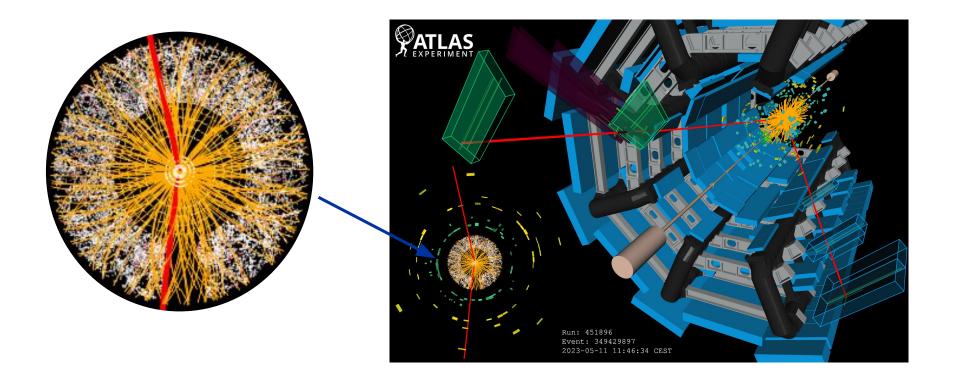

# **Probing Harsher Conditions**

- Special fill to scan over rate and  $\mu$ , reaching < $\mu$ > of 68.5

- Fill 8891, including smart L1, reco@ECR, raised thresholds

- Both IBL and B-Layer kept up tracking performance

- Comfortably running at <µ> of 62 at 96 kHz with minimal degradation in hits on track

ATLAS Preliminary

50

60

√s= 13.6 TeV

40

20

30

80

2023

LHC Fill 8891

70

0.88

0.86

# Radiation Damage Studies and Outlook

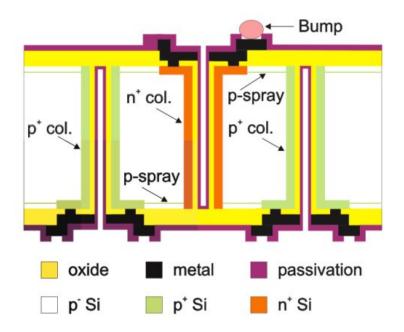

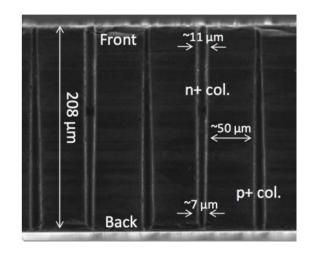

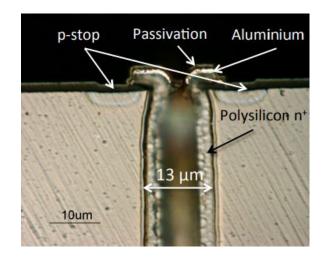

### Before we start: IBL 3D vs Planar sensors

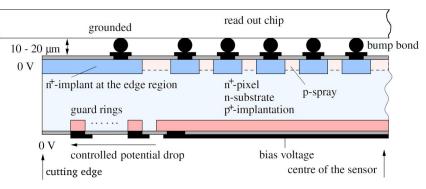

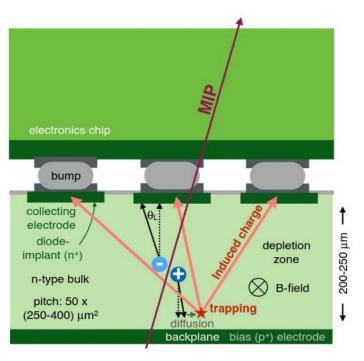

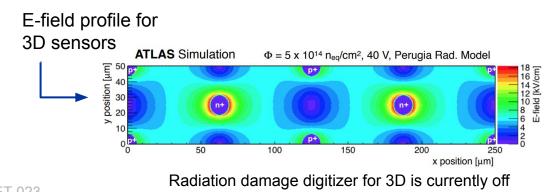

- 3D sensors use column electrodes penetrating the silicon substrate, instead of implants on the surface as for planar sensors

- In the IBL, 3D modules are installed in the outermost positions on a stave

- Response of 3D sensors is intrinsically more resistant to the effects bulk damage because of the reduced charge drift path and collection time, without reducing thickness of active silicon

- Radiation hardness make 3D pixels the choice for HL LHC upgrade programs for innermost layers

#### IBL planar sensor (same as Pixel sensors)

Total thickness for both FBK and CNM is 230  $\mu m.$  CNM columns stop ~ 15  $\mu m$  from opposite edge, leaving ~ 200  $\mu m$  overlap of n+ and p+ electrodes

# **Radiation Damage: MC**

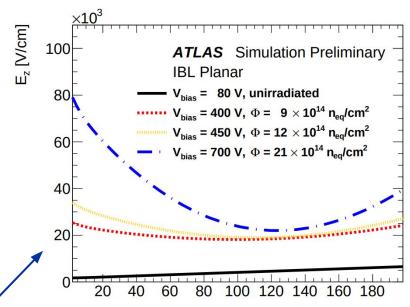

- Charge deposited in sensor bulk drift toward collecting electrode due to E field, deformed by radiation damage. Path is deflected by B field (Lorentz angle) and diffusion

- Radiation damage increases charge trapping, inducing / screening a fraction of charge (Ramo potential)

- Total induced charge is digitised and clustered

- E field map, Lorentz and Ramo potential are input from TCAD simulation

Bulk Depth [µm]

E-field as a function of bulk depth for planar sensors. Electrons drift towards lower values of bulk depth. Fluences correspond to end of Run 2, end of 2023 pp, and projected end of Run 3.

ATLAS-COM-INDET-023

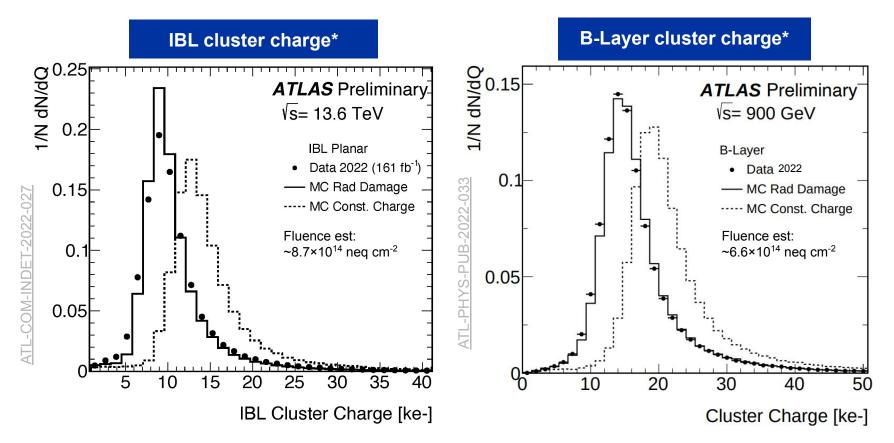

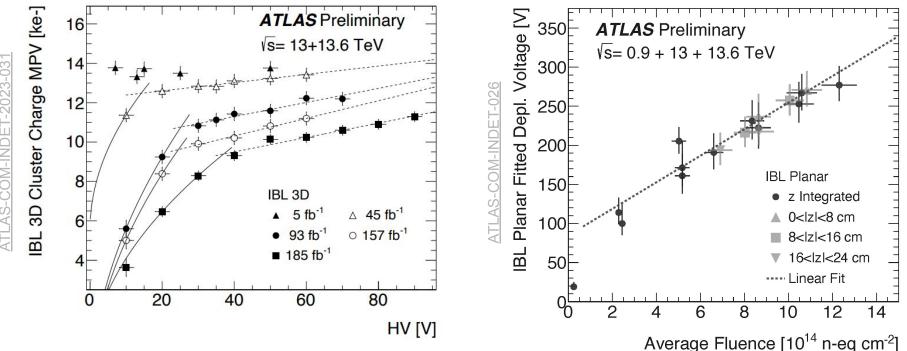

## **Cluster Charge Properties**

- The main effect of bulk radiation damage is seen in modifications of charge collection properties

- Increase in leakage current, proportional to particle fluence

- Change in depletion voltage due to change in effective doping concentration

- Decrease in charge collection efficiency due to signal reduction caused by charge trapping

Effect of radiation damage on cluster charge well reproduced by MC, with predicted MPV matching to within 1 % Significant improvement with respect to constant charge MC

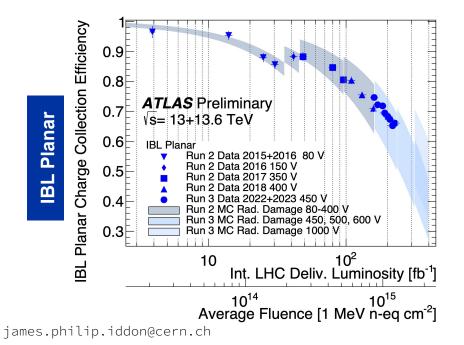

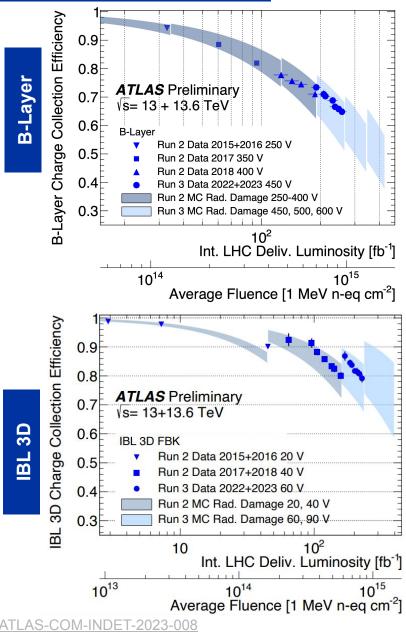

# **Charge Collection Efficiency**

- IBL planar and B-Layer reduction of ~ 35 % in charge collection efficiency with respect to the start of operation

- IBL 3D see a reduction of ~ 22 %

By adapting bias voltage and thresholds, charge collection efficiency will be kept within ~ 50 % of original value until the end of Run 3 (total of ~ 400 fb<sup>-1</sup>), keeping hit efficiency well above 97 %

## **Depletion Voltage in IBL**

- Depletion voltage at 270 V for planar, 37 V for CNM 3D and 28 V for FBK 3D

- In 2023, biased at 450 V for planar and 60 V for 3D

- Well below power supply limits of 1000 V for planar and 500 V for 3D

- Below max of 900 V for planar and 150 V for 3D sensors reached in test beam \_

## Conclusion

- Operations in 2023 has been especially smooth on the Pixel side

- Studies of charge collection efficiency and depletion voltage evolution show good agreement with MC and forecast permissible degradation until the end of Run 3

- Pixel is able to perform at a higher pile up than it was designed for (<µ> of 23 -> 68.5), thanks to DAQ improvements and detector configuration adjustments

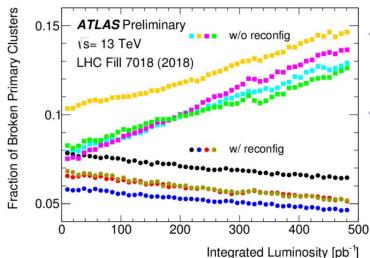

# Handling Higher Pile Up: Threshold

- Thresholds need to be adjusted to account for:

- Loss in charge collection efficiency with radiation damage (increased trapping)

- Increased FE activity with more demanding running conditions

- Bandwidth saturation from modules to ROD

- If FE activity is high, single FEs can desynchronise, leading to unusable events until the next ECR

- Raising the thresholds reduces digital activity, reducing FE level desychronisation

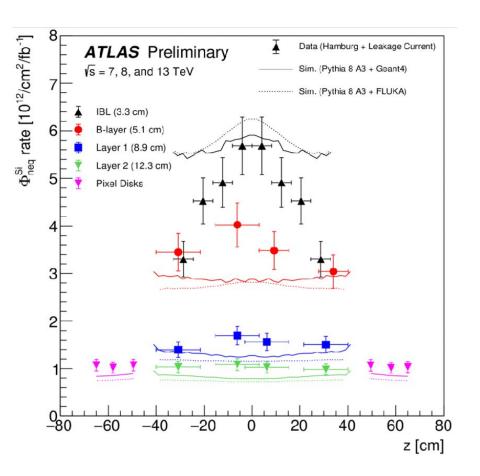

# **Luminosity to Fluence**

- No direct measure of fluence

- Measure integrated luminosity and extrapolate to fluence

- Needs simulation of inelastic pp collisions (Pythia 8), then transport through detector (FLUKA / GEANT4)

- Can also make an indirect measurement of fluence via leakage current

- Leakage current is proportional to voltage and fluence

- Leakage current modelled with Hamburg model

Data / MC discrepancy in z profile under investigation

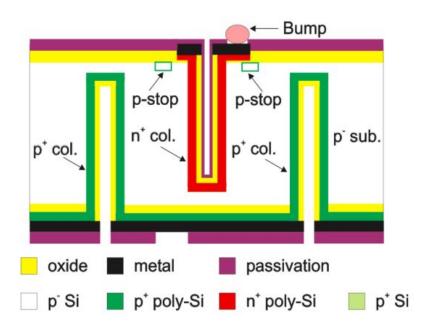

### **CNM 3D Sensors**

- Columns etched from both sides of wafer in an 8 mask process

- Columns are doped by a deposition of n+/p+ poly-silicon

- Metal contacts at the top of the column, on top of the poly-silicon

- p-stops provide surface isolation between junction columns on the front side

# **FBK 3D Sensors**

- Column etched from both sides of the wafer in a 12 mask process

- Columns are doped via thermal diffusion and then passivated by silicon oxide

- Metal contacts at highly doped regions on surface

- p-spray layer provides surface isolation between junction columns, on both sides