13th International "Hiroshima" Symposium on the Development and Application of Semiconductor Tracking Detectors

# Design and construction of the CMS Inner Tracker for the HL-LHC Upgrade

Alkiviadis Papadopoulos on behalf of the CMS Tracker Group

December 2023, Vancouver, Canada

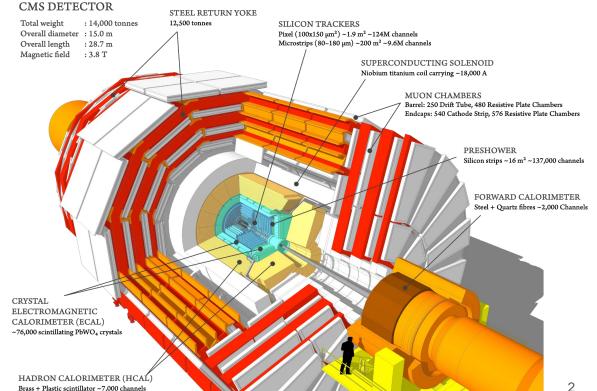

## CMS Tracker

- Innermost sub-detector of CMS >

- Used for reconstruction of charged >particle trajectories (tracks)

- $\succ$ Si sensors

- Inside a strong magnetic field  $\succ$

- Particle momentum and charge 0 determines trajectory

- Two parts: >

- Outer tracker (strips) 0

- Inner tracker (pixels) 0

- >Inner tracker was upgraded in 2017 (Phase-1 upgrade)

- Layers were added to maintain good 0 tracking performance at higher luminosity  $(2x10^{34} \text{ cm}^{-2}\text{s}^{-1})$

- Both inner and outer tracker are >being redesigned for HL-LHC (Phase-2 upgrade)

### Current detector (Phase-1 upgrade)

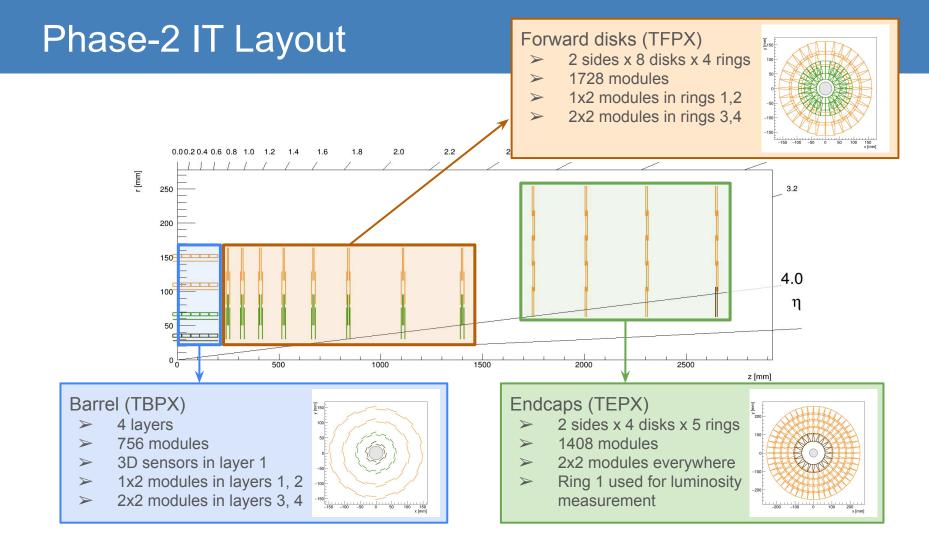

## Phase-2 Inner Tracker for HL-LHC

Peak luminosity [10<sup>34</sup>cm<sup>-2</sup>s<sup>-1</sup>

7

6

5

3

2

Run 4

2026 2028 2030 2032 2034 2036 2038 2040

Year

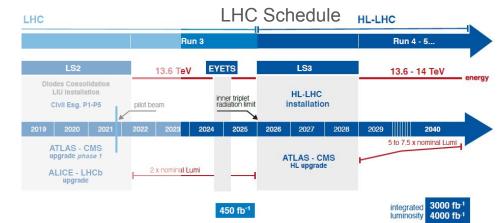

### HL-LHC

Inst. luminosity (nominal)  $5 \times 10^{34} \text{ cm}^{-2}\text{s}^{-1}$

Inst. luminosity (ultimate) 7.5 x  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>

Integrated luminosity ≥ 3000 fb<sup>-1</sup>

Collisions per bunch crossing 140 - 200

### Requirements:

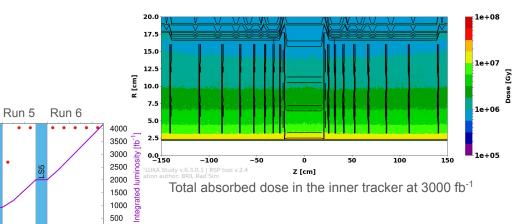

- Radiation tolerance

- Dose up to ~1 GRad

- Fluence\* up to ~2 x  $10^{16} n_{ea}$  cm<sup>-2</sup>

- Replacement of inner modules foreseen

- Increased granularity

- Better track separation at high pile-up

- Reduced material

- > Extended tracking **acceptance** ( $|\eta| \le 4$ )

- > High **bandwidth** (hit rate up to 3.5 GHz/cm<sup>2</sup>)

|         | RUN 4<br>(800 fb <sup>-1</sup> ) |      | RUN 5<br>(1300 fb <sup>-1</sup> ) |      | RUN 4+5<br>(2100 fb <sup>-1</sup> ) |      | RUN 4+5+6<br>(3000 fb <sup>-1</sup> ) |      |

|---------|----------------------------------|------|-----------------------------------|------|-------------------------------------|------|---------------------------------------|------|

|         | Fluence                          | Dose | Fluence                           | Dose | Fluence                             | Dose | Fluence                               | Dose |

| TBPX L1 | 0.69                             | 0.36 | 1.12                              | 0.58 | 1.81                                | 0.93 | 2.58                                  | 1.34 |

| TBPX L2 | 0.18                             | 0.11 | 0.29                              | 0.17 | 0.48                                | 0.28 | 0.68                                  | 0.40 |

| TFPX R1 | 0.46                             | 0.31 | 0.75                              | 0.49 | 1.22                                | 0.79 | 1.74                                  | 1.13 |

| TFPX R2 | 0.21                             | 0.14 | 0.35                              | 0.23 | 0.57                                | 0.37 | 0.82                                  | 0.53 |

Maximum fluence\*  $(10^{16}n_{eq}cm^{-2})$  and dose (GRad) by layer/ring

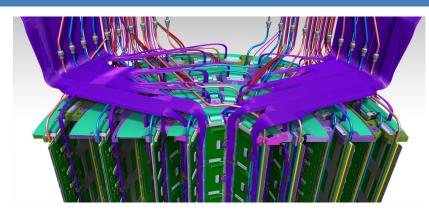

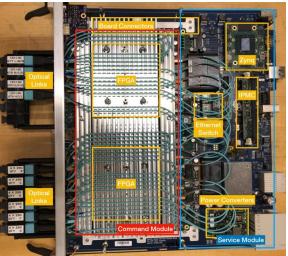

## Mechanical structure

Relatively easy installation and removal

TFPX

- Low density (carbon fiber) support

- $\succ$  CO<sub>2</sub> cooling pipes

Barrel (TBPX)

Close-up view of the barrel showing modules, e-links, cooling loops, flex, high voltage, serial power

TEPX

5

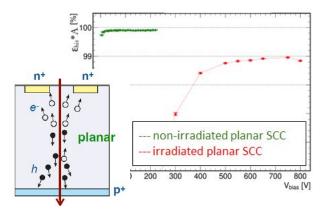

## Sensors

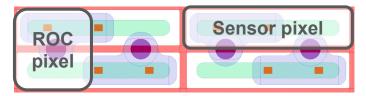

- ➢ Rectangular pixels (25 x 100 µm) everywhere

- $\circ$  100  $\mu$ m in beam direction to match longer clusters in barrel mid-rapidity

- Square pixels offer small to no improvement

- Planar (n-in-p, 150µm bulk thickness)

- High hit efficiency (>99%)

- ≻ 3D

- Slightly less efficient (up to 98%)

- High margin for thermal stability

- Lower bias voltage

- Barrel layer 1 requires 3D sensors for thermal stability after irradiation

- > Planar sensors are used everywhere else for higher efficiency

Hit efficiency after irradiation  $(1x10^{16} n_{e\alpha}cm^{-2})$

Rectangular sensor pixels are bump bonded to square ROC pixels according to this pattern

## Read-Out Chip (ROC)

- Designed by the RD53 collaboration between ATLAS & CMS

- $\succ$  Main goals:

- **Hybrid** design (independent sensor R&D)

- Increased granularity (smaller pixels)

- High hit rate

- Radiation tolerance

- > **RD53A** was the first **demonstrator** chip:

- Submitted in 2017

- Half-size

- 3 different AFE designs on the same chip

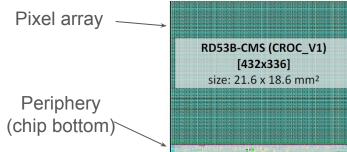

- > RD53B-CMS (aka. CROCv1) was the pre-production prototype:

- Submitted in 2021

- Full size

- CMS-specific (ATLAS flavor also available)

- Linear AFE

- > RD53C-CMS (aka. **CROCv2**) is the **final** CMS version:

- Submitted in Oct. 2023

- Many improvements and bug fixes but functionally similar to CROCv1

### RD53A

CROCv1

## CROCv1

- Mixed-signal IC (digital & analog)

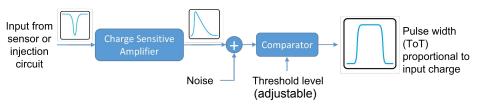

- Linear Analog Front-End (AFE):

- Low threshold (< 1000 e-)

- Time Over Threshold (ToT) linear w.r.t charge

- High bandwidth

- Multi-lane output

- Event data compression

- Can receive and forward data to/from each other (data-merging)

- Radiation tolerance

- Good performance up to ~1 GRad

- Triplicated registers

- SEU detection

### Overview of AFE operation

Configuration memory: ~1446 bits global + 8 bits per pixel

- Highly configurable

- Pixel masking

- $\circ$   $\qquad$  Global threshold and ToT gain

- Per-pixel threshold adjustment

- Input/output merging & routing

### Calibration & monitoring

- Charge injection circuit

- Radiation and temperature sensors

- Internal voltage/current monitoring

### Testing

>

- Bit error rate (PRBS)

- Error counters

- $\circ$  Design for test logic with scan chain

### Specifications Pixel size 50 x 50 µm<sup>2</sup> Process 65 nm (TSMC) Hit rate 3.5 GHz/cm<sup>2</sup> Trigger rate 750 kHz Readout latency 12.5 µs (500 BX)

Output bandwidth 1-4 x 1.28 Gbps

Power consumption  $| < 1W / cm^2$

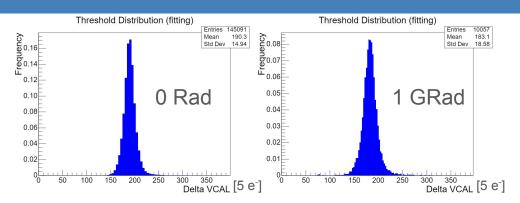

## **CROCv1** Results

- Extensively tested and characterized

- > AFE measurements

- Threshold & noise

- ToT Gain

- Hit detection delay (time-walk)

- Threshold dispersion

- Noise occupancy (spontaneous hits)

- Several irradiation campaigns

- Different sources (X-rays, various beams)

Per pixel

Global

- With and without sensor

- Reaching up to ~1 GRad

- Non-uniform with different gradients

- ➤ Test-beams

- ➤ Wafer-level testing

- Custom probing setup

- Comprehensive and fast testing procedure

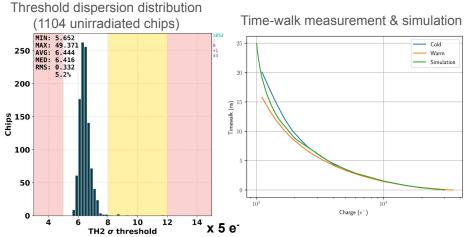

### Modules

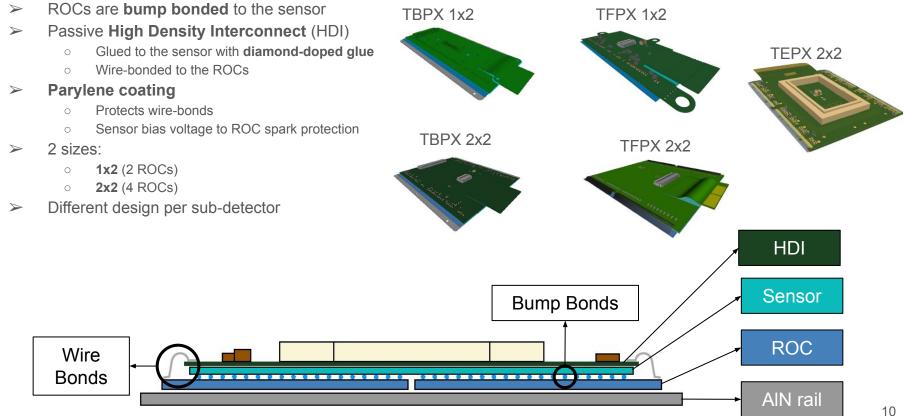

## **Optical readout**

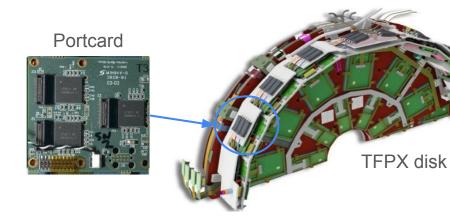

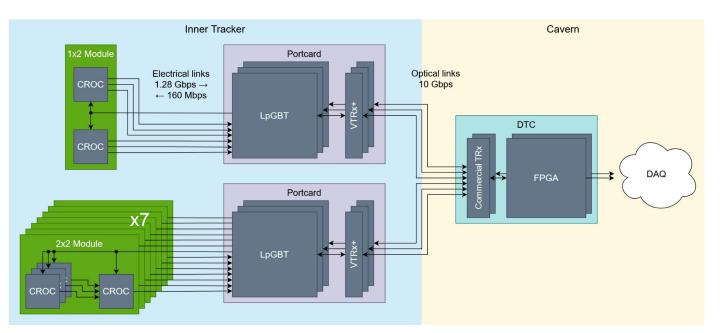

### Front-End:

- > Optical links are used to minimize materials

- The portcard acts as a bridge between electrical and optical links

- Each portcard has 3 LpGBT ASICs

- Each LpGBT is connected to:

- up to 7 electrical outputs @ 160 Mbps (downlinks)

- up to 7 electrical inputs @ 1.28 Gbps (uplinks)

- 1 optical TRx @ 10 Gbps (VTRx+)

- > DTC (Data, Control and Trigger)

- ACTA board (Apollo)

- 2 x FPGAs + CPU

- 72 optical links to the Front-Ends (FE)

- 16 x 25 Gb/s links to DAQ (event data)

- 8x25Gb/s links for luminosity monitoring

### DTC (Apollo)

## System data flow

- > Portcards in TFPX and TEPX

- > Adaptable bandwidth

- From 0.25 to 4 uplinks per CROC (0.32 to 5.12 Gbps)

- 1 downlink per module (160 Mbps)

Output links per module

|      | Layer 1 | 6 |

|------|---------|---|

| TBPX | Layer 2 | 2 |

| IDFA | Layer 3 | 2 |

|      | Layer 4 | 1 |

|      | Ring 1  | 3 |

| TFPX | Ring 2  | 3 |

| IFFA | Ring 3  | 2 |

|      | Ring 4  | 2 |

|      | Ring 1  | 4 |

|      | Ring 2  | 3 |

| TEPX | Ring 3  | 2 |

|      | Ring 4  | 2 |

|      | Ring 5  | 1 |

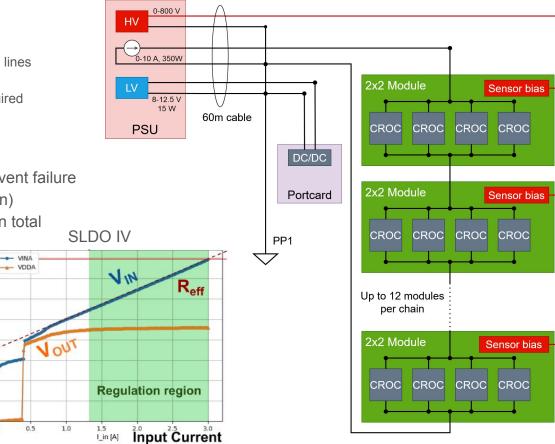

## Power system

- Serial powering

- Up to 12 modules in series

- Low power loss in the transmission lines

- Minimal cable mass

- No rad-hard DC-DC converter required

- On-chip Shunt-LDO (SLDO)

- Voltage regulator (1.2 V)

- Shunt dissipates excess power

- On-chip protection mechanisms prevent failure scenarios (eg. overvoltage protection)

Max -2.00-

1.75

1.50

Voltage [V]

0.75

0.25

0.0

> 260 x 2 Power Supply Units (PSU) in total

Cable cross-section

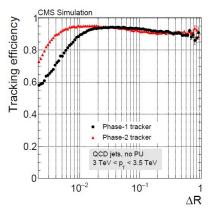

## Performance

- > Offline simulation with CMSSW

- Significant improvements in efficiency and resolution

- High efficiency and low fake rate for PU up to 200

Efficiency vs. track distance from nearest track

#### Fake rate

## Conclusions

- > The Inner Tracker has been redesigned for HL-LHC

- New sensors and readout electronics

- High granularity (more layers, more and smaller pixels)

- Reduced material

- Increased acceptance (from 3 to 4)

- Simulation shows promising results

- Extensively tested in the lab and in test-beams

- At various levels of integration (from individual components to complete demo setups)

- > The final readout chip was submitted in October

- ATLAS flavor already successfully tested

- Design and testing phases are mostly over

- Phase-2 upgrade installation during LS3

- o Jan. 2026 April 2029

Thank you!

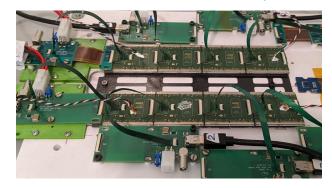

### TBPX ladder demo setup