# Mighty Tracker

# Performance Studies of the MightyPix for LHCb

13th International "Hiroshima" Symposium on the Development & Application of Semiconductor Tracking Detectors

Hannah Schmitz, hannah.schmitz@cern.ch On behalf of the LHCb Collaboration

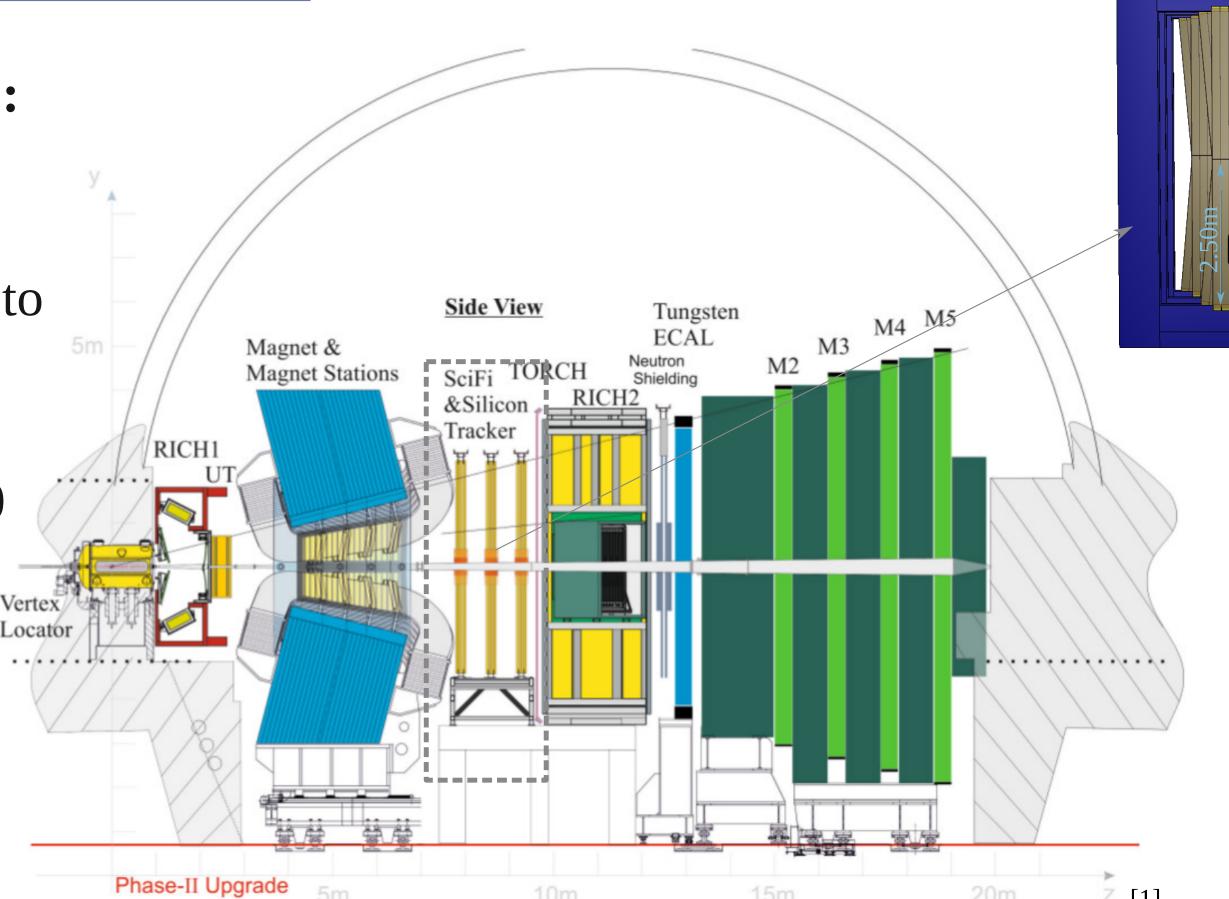

### LHCb Upgrade II Detector

#### **Planned Upgrade II specifications** [1]:

- 40 MHz triggerless DAQ

- $L_{inst} = 1.5 \cdot 10^{34} \text{ cm}^{-2} \text{s}^{-1}$

- 6x higher occupancy/fibre compared to Upgrade 1 for SciFi only

- 6·10<sup>14</sup> MeV n<sub>eq</sub>/cm<sup>2</sup> after Run 6

- Interactions/bunch crossing  $\langle \mu \rangle = 40$

- → Upgrade during LS4 to ensure efficient tracking & particle identification

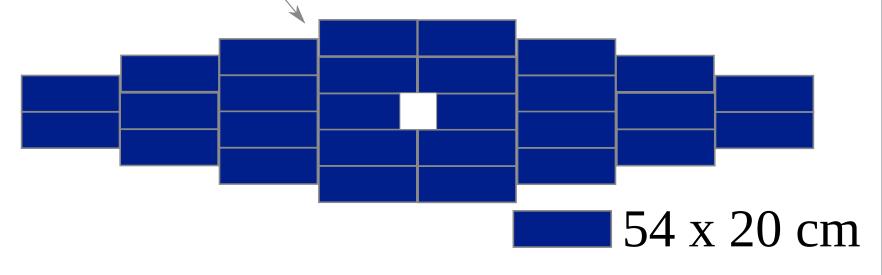

- 6 layers silicon in total

- 28 submodules/layer

- 35 pixel/submodule

- 18 m<sup>2</sup> pixel area

- Pixel size of 55 x 165 μm<sup>2</sup>

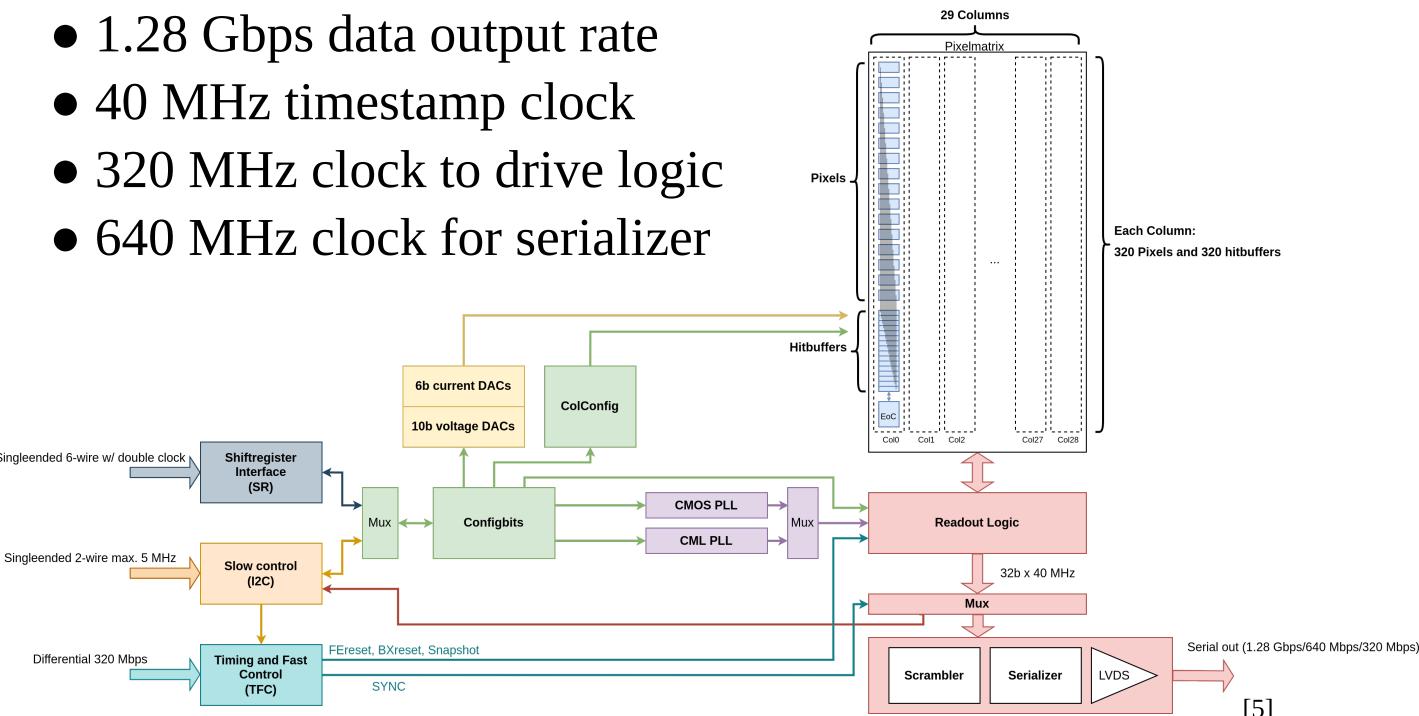

- 29 columns x 320 rows

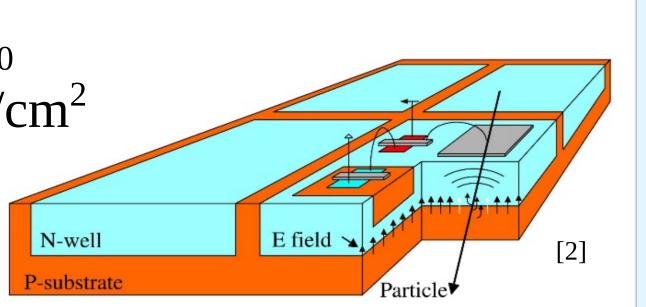

- CMOS amplifier & comparator

- V1 chip size: 5 x 20 mm

## MightyPix Specifications [1][2][3]

- Power consumption < 150 mW/cm<sup>2</sup>

- Low material budget < 1 % of  $X_0$ • Radiation hard: 6·10<sup>14</sup> MeV neq/cm<sup>2</sup>

- Time resolution < 3 ns

- Hit rate: 17 MHz/cm<sup>-2</sup>

- $\rightarrow$  HV-CMOS MAPS

#### MightyPix Design [1][2][3][5]

- Commercial 180 nm production

- Control interfaces: TFC, I2C, SR

## MightyPix Readout - MARS

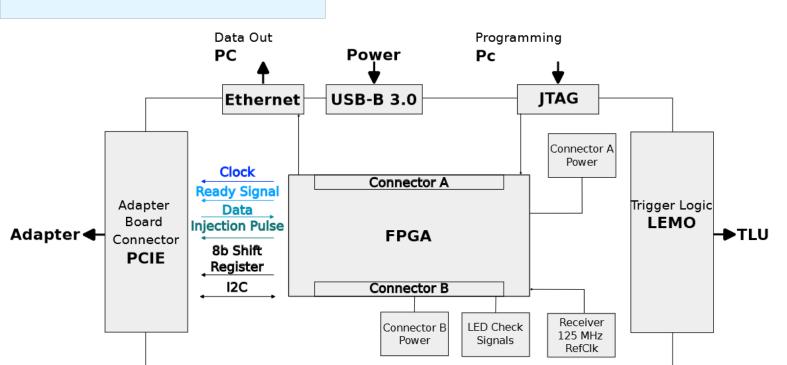

#### FPGA Board

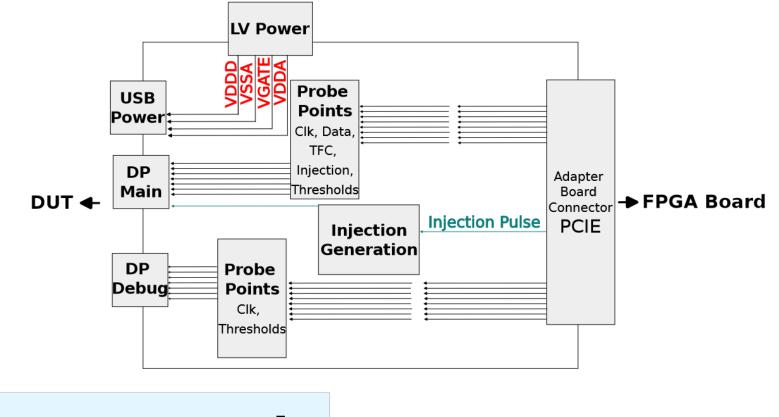

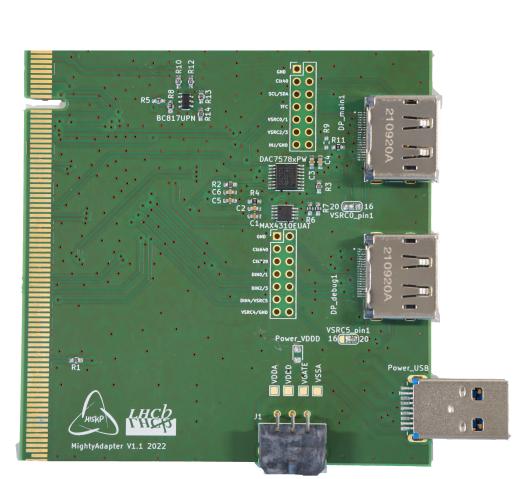

### Adapter Board

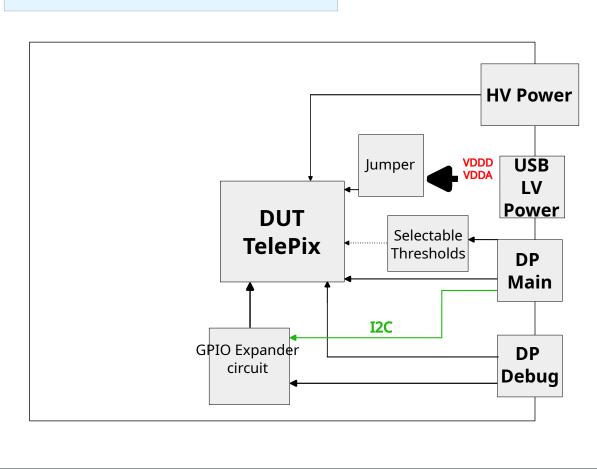

#### **DUT** Board

#### MightyPix - First Performance Studies [7]

- Simulation confirmed hit rate [8]

- Lab tests started 2023 • Functionality tests:

- CMOS PLL

- Slow control

- TFC interface

- SR interface

- Breakdown ~ 200V

- Time resolution studies started

#### Sr90 measurement [7] Counts So 300 250 400 200 300 150 200 100 50 Column [pix]

#### MARS - Specifications

- Modular & flexible hardware design

- Usable at testbeam facilities

- Adapter to use Chip carrier boards from other readout systems

- Multiple DUTBoards: Run2020, Run2021, TelePixV2, MightyPixV1

- High readout speed possible: 1.6 GBps

- Firmware: Modular design with switchable receiver (fast/slow)

- Slow control: Python interface with common functions for all DUTs

- DUT specification defined in configuration file

- Functionality validated for Run202x and TelePix sensors

- Characterization of TelePix ongoing

<sup>[3]</sup> *TSI engineering run HVMAPS*, I. Peric, https://adl.ipe.kit.edu/downloads/TSI engineering run v2.pdf