### **CCPC-ECS** Status

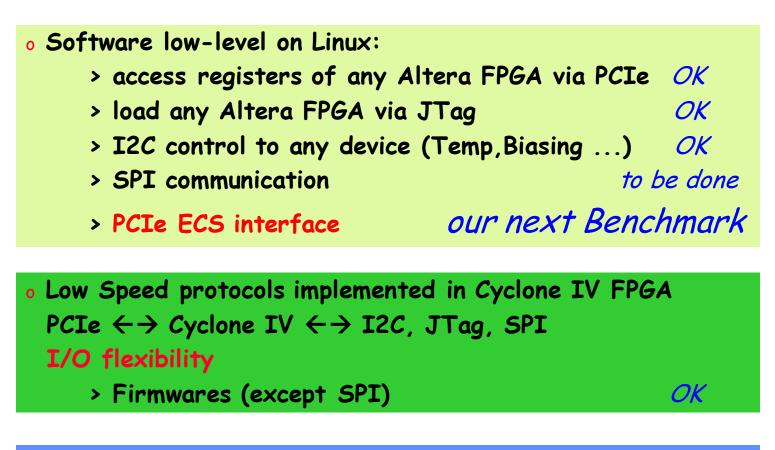

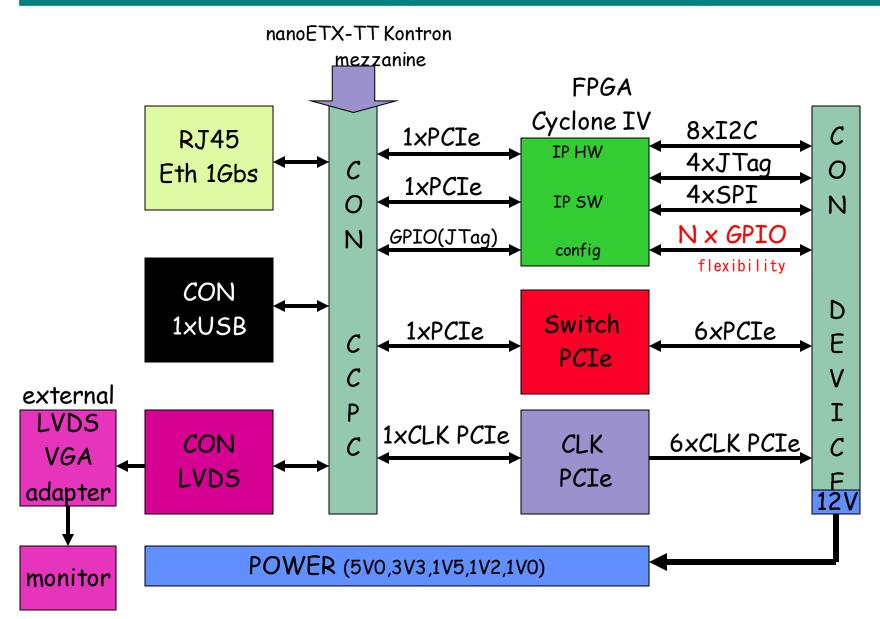

• concept: generic mezzanine to connect any device to control room PCIe, I2C, JTag, SPI  $\rightarrow CCPC \rightarrow 1Gbs$  Eth

• R&D and mass production: CBPF-Rio

o focus on TELL40:

- > OnBoard implementation due vertical limitation (ATCA)

- integration discussed in last october in Marseille

PCIe, JTag (& maybe SPI) very useful

I2C not needed due intrinsical control system in ATCA

• Validation board: Automatic Testing system for HW & SW

o documentation: technical note & specs & Talk

> available for next Electronics meeting

# CCPC-ECS Status (cont'd)

• Prototypes: CCPC-ECS & Validation boards

- > both in production  $\rightarrow$  ready Feb/2012

- > five  $2^{nd}$  versions  $\rightarrow$  mid 2012

(Brasil, CERN, Marseille\*, Lausanne, ...?)

# First Prototype Block Diagram

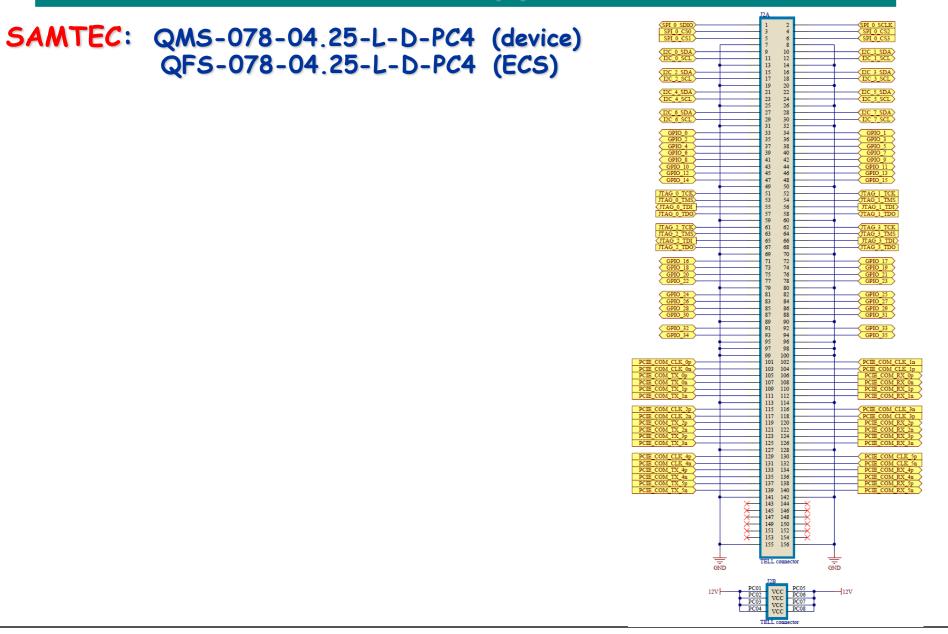

## First Prototype Pinout

# Switching topic

<u>A Test Bench for the</u> <u>upgraded OT FE</u> <u>Electronics mass</u> <u>production</u>

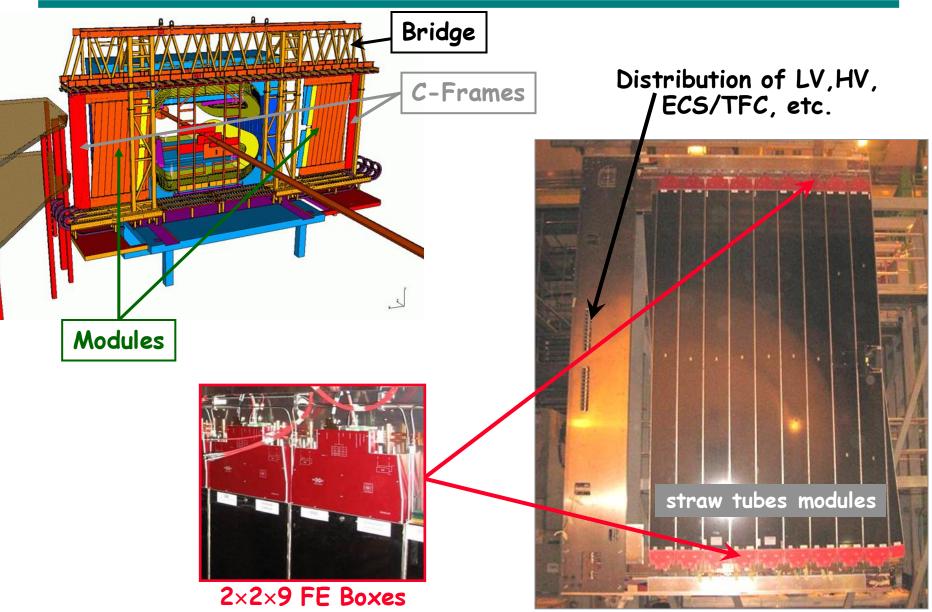

# **OT FEE Overview**

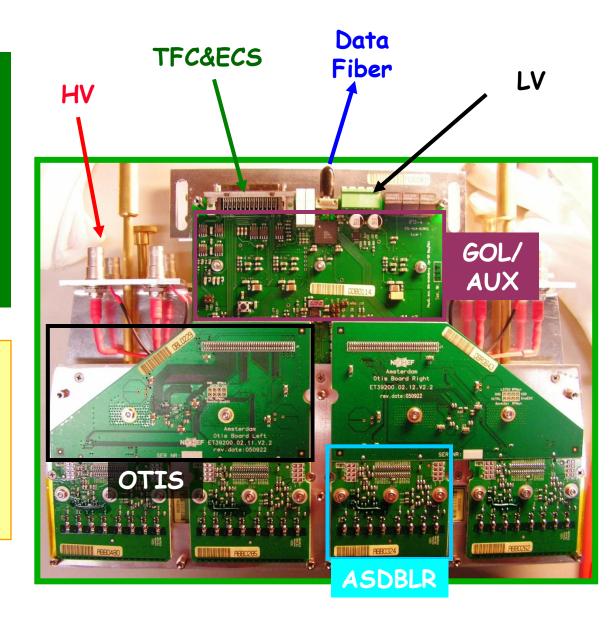

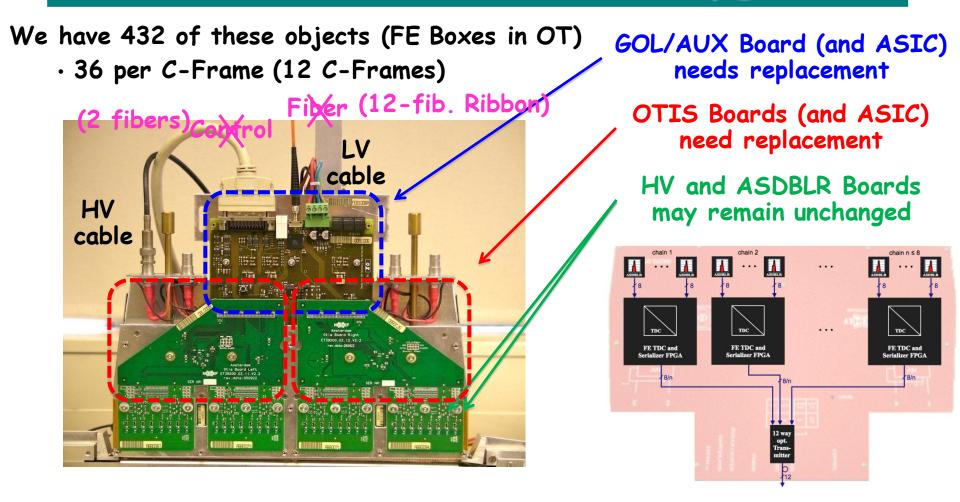

# FE Electronics (the present one)

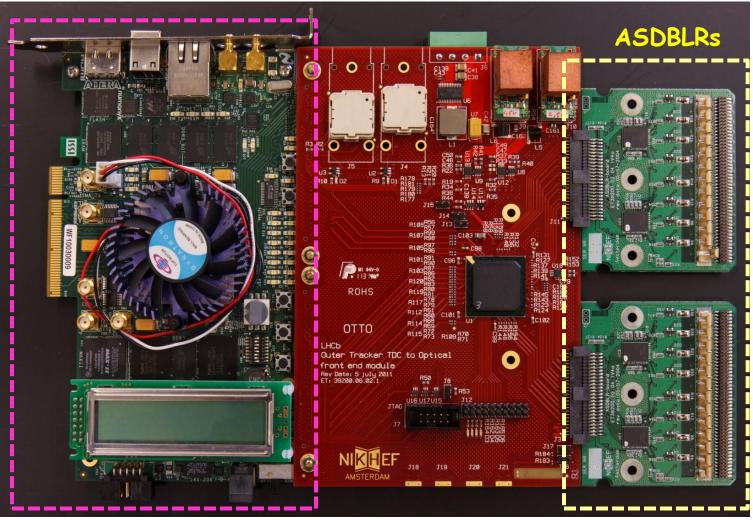

Front end box (full size): 128 channels 4 × (32 ch) HV Boards 16 ASDBLR chips 4 OTIS TDC chips 1 GOL chip: 1.6 Gbit/s

#### MASS PRODUCTION:

500 GOL/AUX Boards2.000 OTIS TDC Boards4.000 ASDBLR Boards2.000 HV Boards

# Why a FE Tester?

A fully automatized FE Tester was mandatory given the large size of the production

MASS PRODUCTION:

500 GOL/AUX Boards 2.000 OTIS TDC Boards 4.000 ASDBLR Boards 2.000 HV Boards

Although we tested individually all boards inside a FE Box, a final global test proved invaluable:

- FE assembly defects  $\Rightarrow$  ~1/3 of FE Box re-assembled

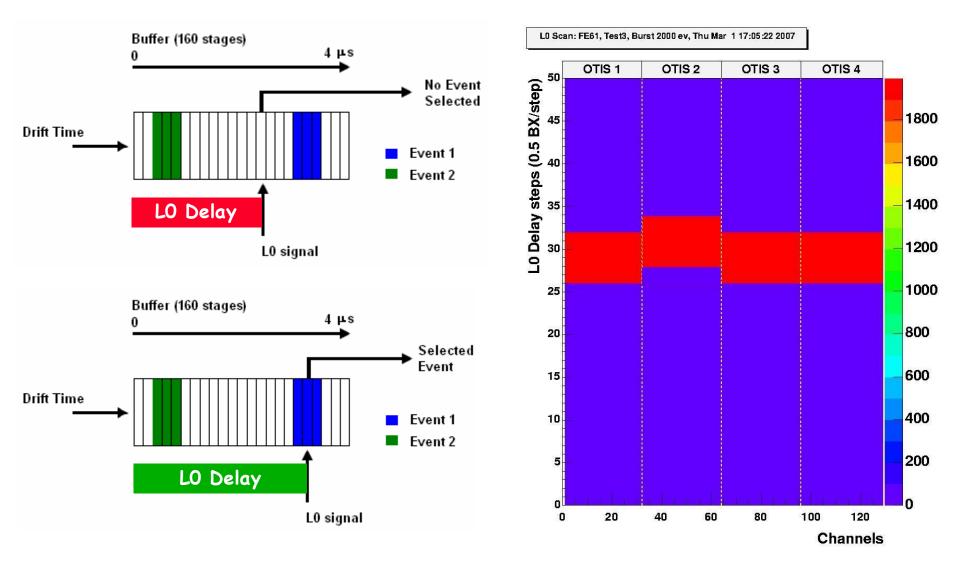

- synchronicity between 4 OTIS in one FE Box could be checked

We <u>did NOT use ODIN and Tell1</u>, but generated TFC internally and read data asynchronously (see next slides):

- simple setup, ready ahead of time (2 extra Nikhef FTE for 1 year)

- but could not check synchronicity (Bxid, LOid, etc.)

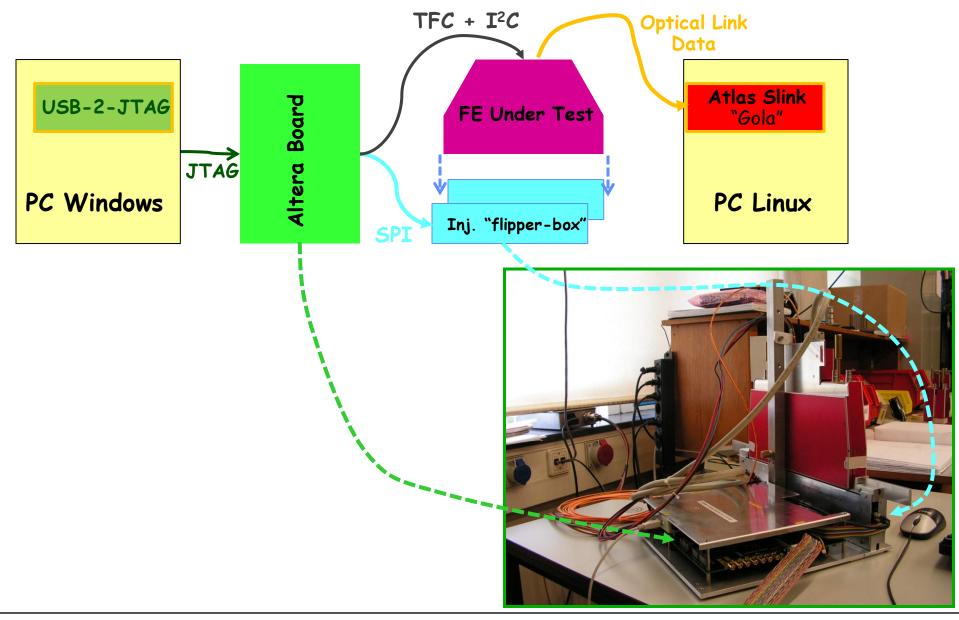

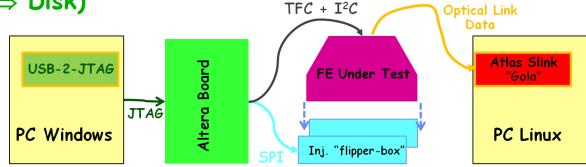

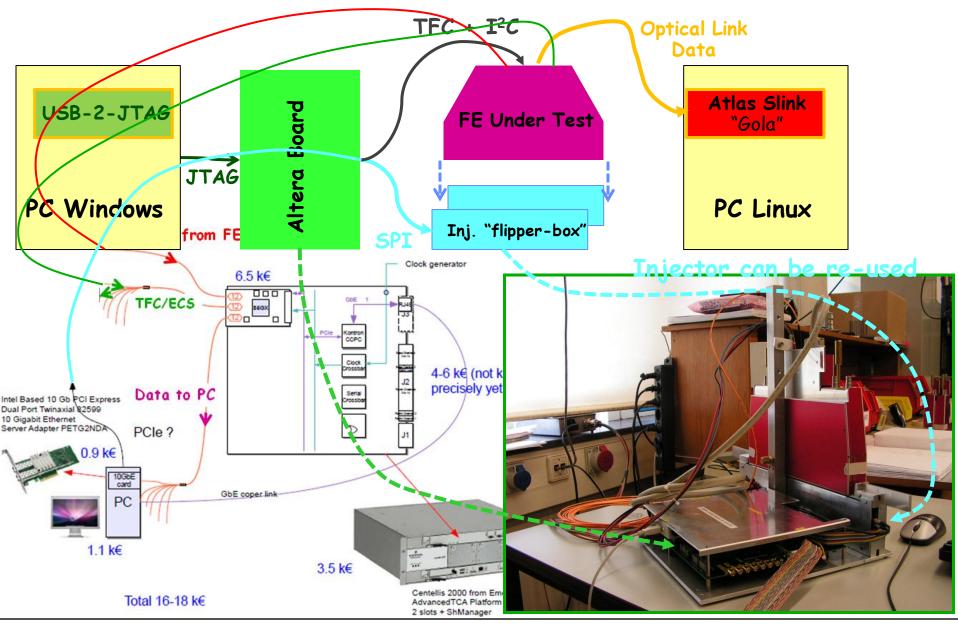

## FE Test Setup

## **FE Tester Functions**

Test of global functionality of fully assembled FE-Boxes:

- Analog input signal injection (mimicking straw-like signal)

- $\cdot$  Internal Generation of ECS & TFC

- Data Acquisition (Fiber  $\Rightarrow$  Disk)

- Threshold Scan

- Input signal amplitude scan

- ASDBLR Testpulse (hi/lo even/odd)

- Input signal delay Scan

- o LO delay scan

0 ...

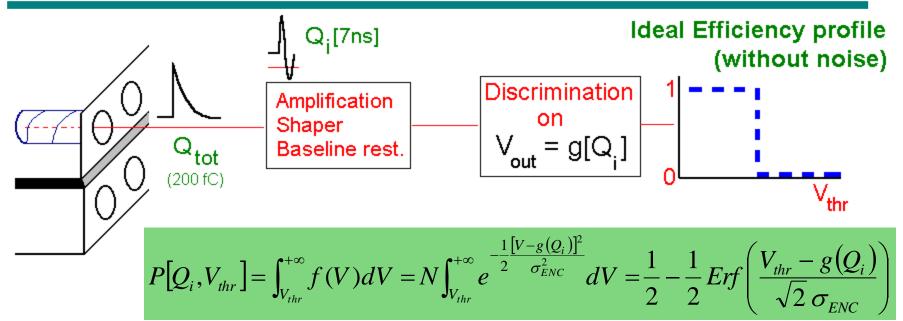

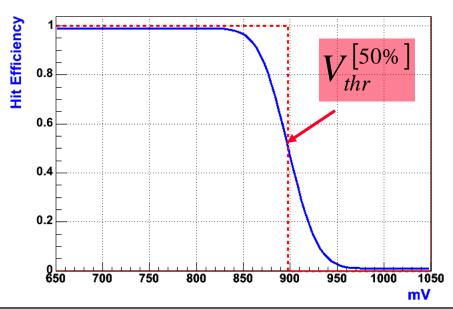

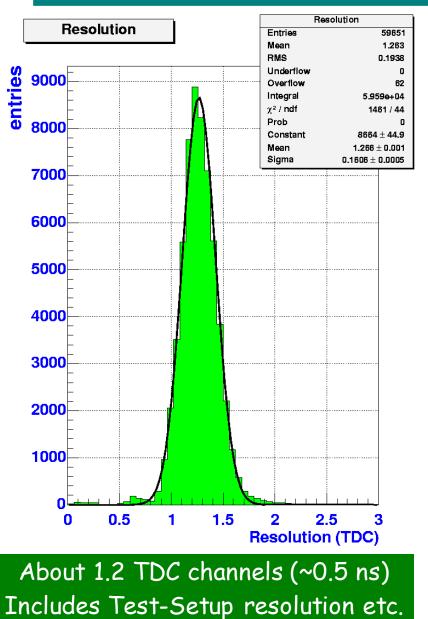

## **Threshold Characteristics**

For a Gaussian Noise, fit efficiency curve with "Erf" and use 50% point as the best estimator

# Threshold Characteristics (cont'd)

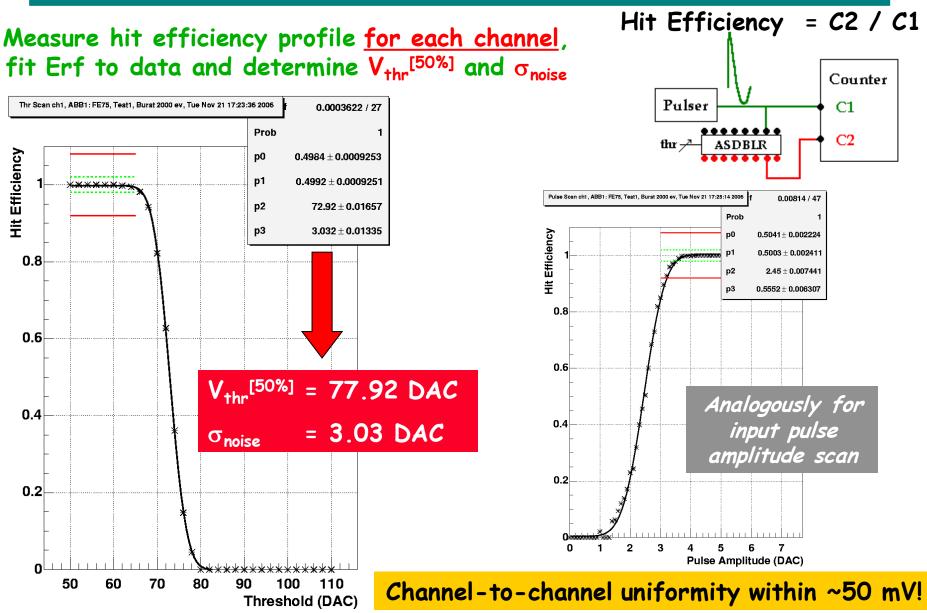

## **Timing Tests**

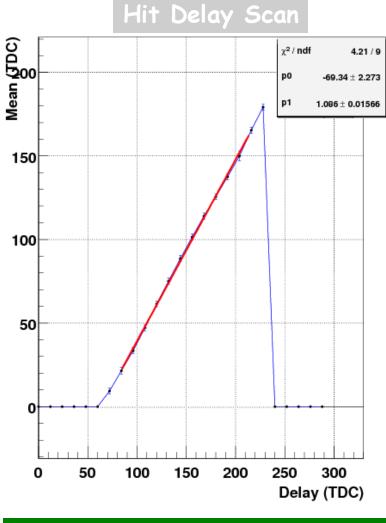

Fit straight line to data and reject if poor linearity (large  $\chi^{2}$ )

December 15, 2011

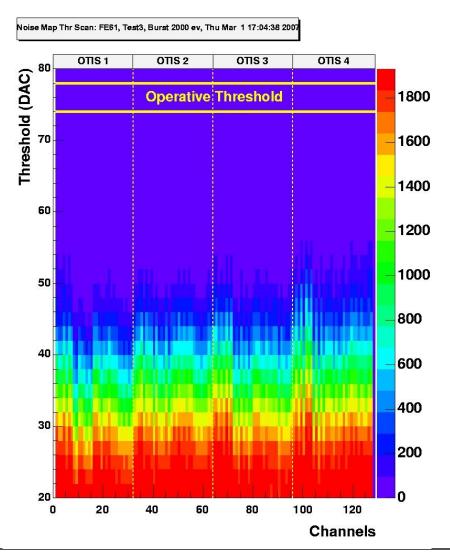

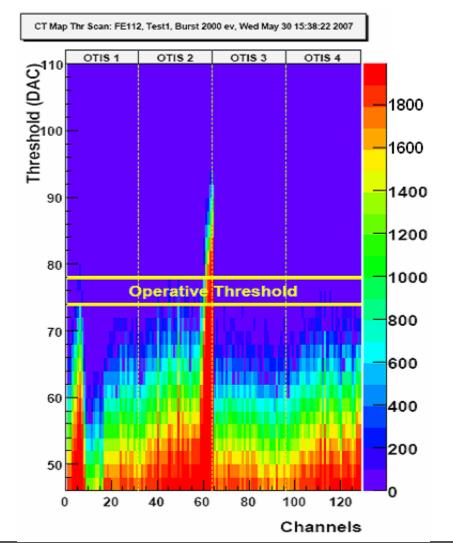

### Noise Tests

Noisy channels

OK

December 15, 2011

Antonio Pellegrino

# LO Delay Checks

### In summary: Test Sequence

Threshold characteristics :

Amplitude Scan with input signal  $\Rightarrow V_{thr}^{50\%}$ , noise, cross-talk, etc.Thr Scan with input signal $\Rightarrow V_{thr}^{50\%}$ , noise, cross-talk, etc.Thr Scan with Testpulse (lo/hi) $\Rightarrow V_{thr}^{50\%}$ , noise, cross-talk, etc.

#### • Noise :

Thr Scan without input signal

#### Timing :

TDC spectra of all channels Input delay scan over the full time range

• LO scan :

LO Delay Scan in steps of  $\frac{1}{2}$  BX

#### Analysis

Control histograms automatically generated for all tests, fitting, etc.

All test results available via the Web

## What we learned

quality of production excellent thanks to systematic and meticulous testing

should have (did not!?) tested also high data-load with random triggers

check synchronicity (mainly Bxid)

we used up >90% of our spares (mainly in commissioning in 2009 and 2010)

buuuut... repaired all defect FE Boxes!!

vithout retaining functional FE Testers, we'd be dead by now!

FE Tester not only important in production, for whole life cycle!

- $_{\circ}$  FE Box transport needs care!?

- Not much use testing, if lousy transport after test!?

- corollary: needs FE Tester also at CERN

# Goal of the project

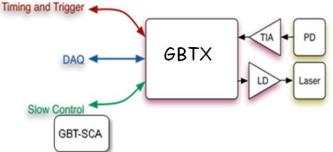

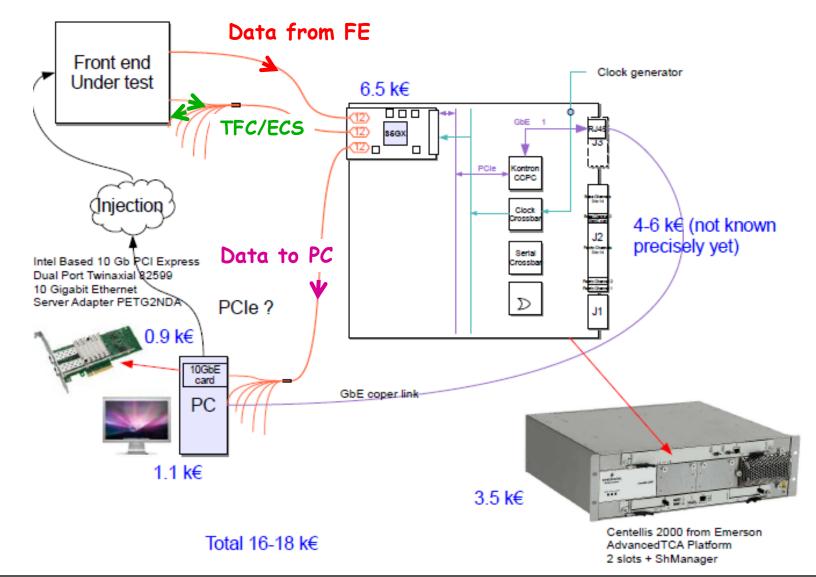

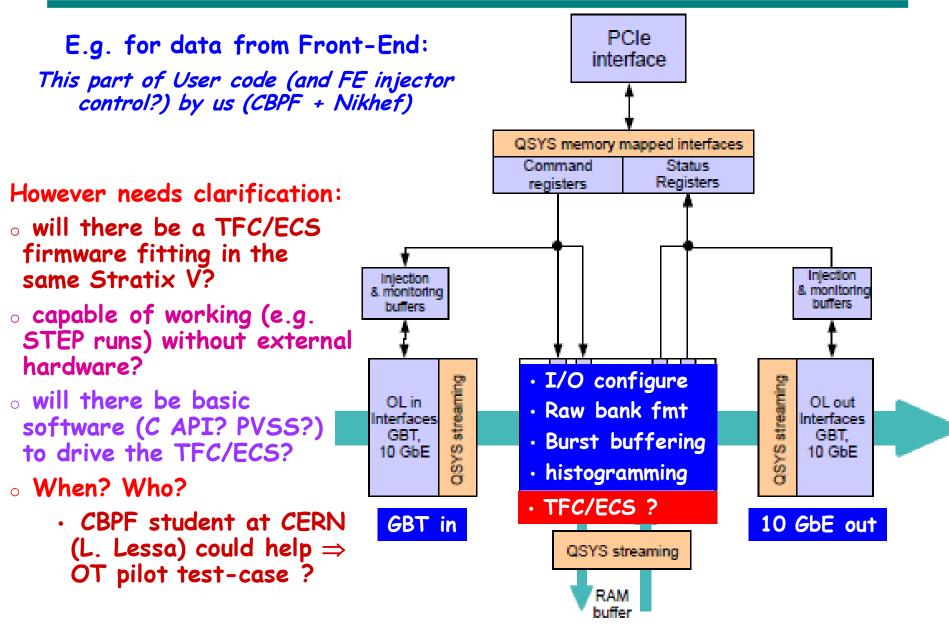

- $_{\circ}$  a tester who can receive the GBTx data

- $_{\circ}$  a tester using GBT/GBT-SCA for TFC/ECS

- $_{\rm o}$  a tester capable of writing "raw" data to disk

- Real time? What bandwidth? Well, let's say at least "bursts" of O(10,000) consecutive events (a "step" in a threshold/delay scan!)

- histogramming in FPGA? Yes, please!

- data analysis in FPGA? No, thanks!

- $_{\circ}$  a tester who can be itself controlled via TCP/IP GbE

- mainly to configure a "step" run (e.g. 33 threshold steps of 10k evts)

extra controls needed (e.g. SPI) ? Probably not...

- When do we need it?

Basic blocks 2<sup>nd</sup> half next year, 1<sup>st</sup> prototype in 2013, 3 instances by 2014 <u>CBPF/Nikhef cooperation (aimed at OT)</u>, support by Marseille & LHCb Online

Question: commonalities with other test benches??

### The Perfect Answer!

Based on proposal by J-P Cachemiche & A. Massafferri

# Overview of OT 40MHz Upgrade

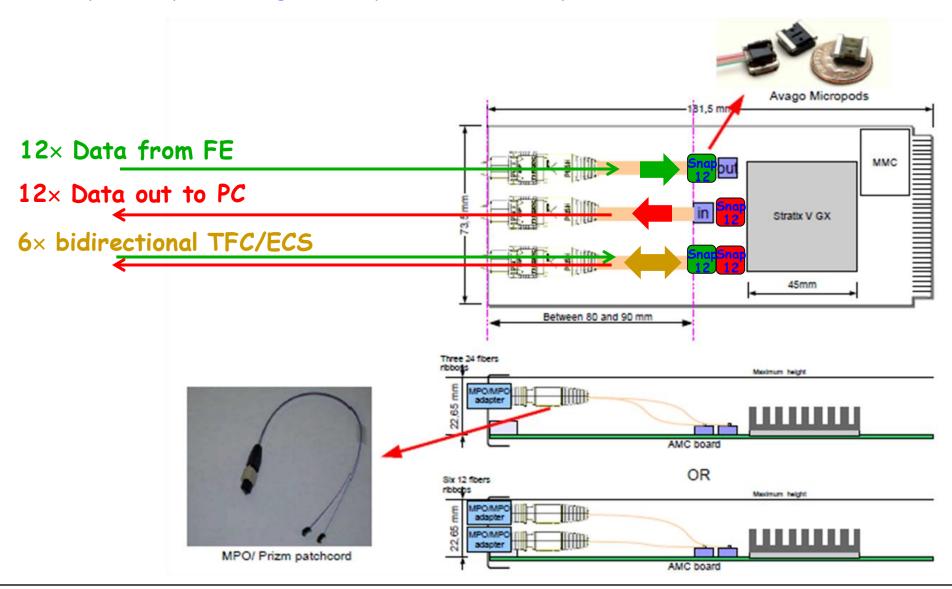

So, Tester <u>physical interfaces</u> to/from FE Box are:

- 12-fibers ribbon (data: 4 or 8 GBTx)

- 2 fibers (bi-directional TFC/ECS)

## Modified FE Test Bench

December 15, 2011

Antonio Pellegrino

## **Optical Interfaces**

Use input/output configurability of the 3×12 optical links to/from Stratix V

# **FPGA Firmware interfaces**

### Where we are now

#### Stratix IV (readout and GBT emulator)

## How do we read & control?

#### At present testing through:

$_{\circ}$  ASDBLR connected to Actel TDC

$_{\odot}$  all data and control lines from/to Actel via HSMC connector to Stratix IV

$_{\odot}$  Actel registers (I2C) controlled by Stratix IV via 1GbE

UDP Nikhef-made + encoding/decoding software on Linux

$_{\odot}$  all data read by Stratix IV via 1GbE (UDP Nikhef-made)

Stratix IV (readout and GBT emulator)

Ok for a while, until 1<sup>st</sup> prototype Actel TDC service board debugged, then FE test bench needed

When do we need it?

Basic blocks 2<sup>nd</sup> half next year, 1<sup>st</sup> prototype in 2013, 3 instances by 2014 <u>CBPF/Nikhef cooperation (aimed at OT)</u>, support by Marseille & LHCb Online

<u>Question: commonalities with other test benches??</u>