## Lessons learnt from the Calorimeter Upgrade I

#### ECAL U-II Workshop

**Frédéric Machefert** IJCLab (Orsay / CNRS)

Many thanks to those whose contributed to this talk

Monday 12<sup>th</sup> December 2022

# INTRODUCTION

- This presentation is very subjective

- I tried to get the input of other people contributing to the upgrade I

- Thanks to them !

- What I found posi/nega-tive may have been nega/posi-tive for others

- I will try to give my feeling

- What was good ? What was bad ?

- What should have we done differently ?

- What could have been improved ? What was well done ?

- What have been the obstacles ?

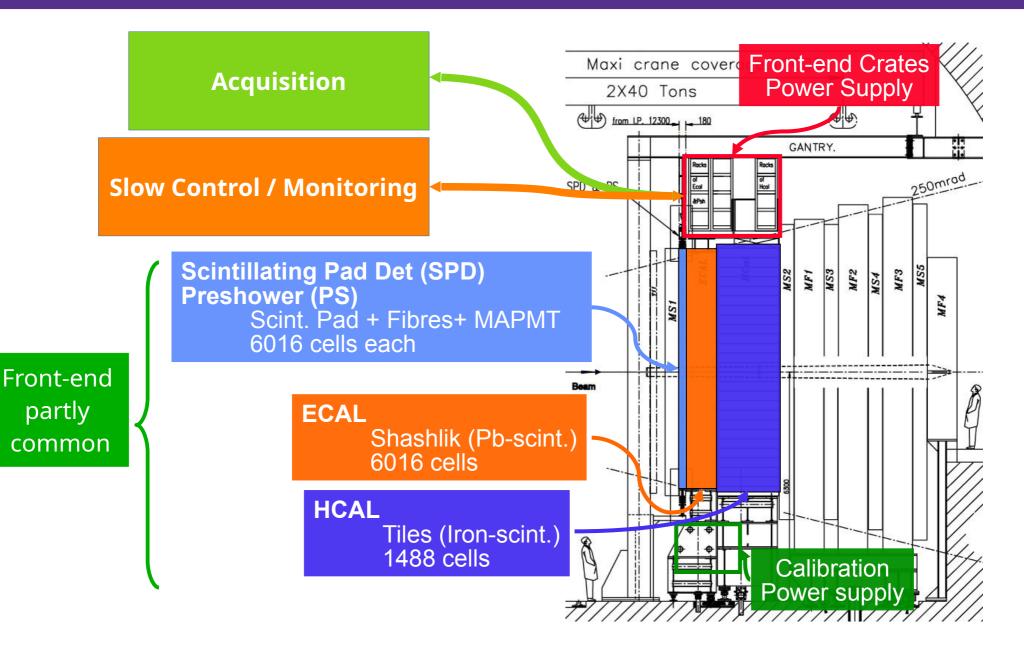

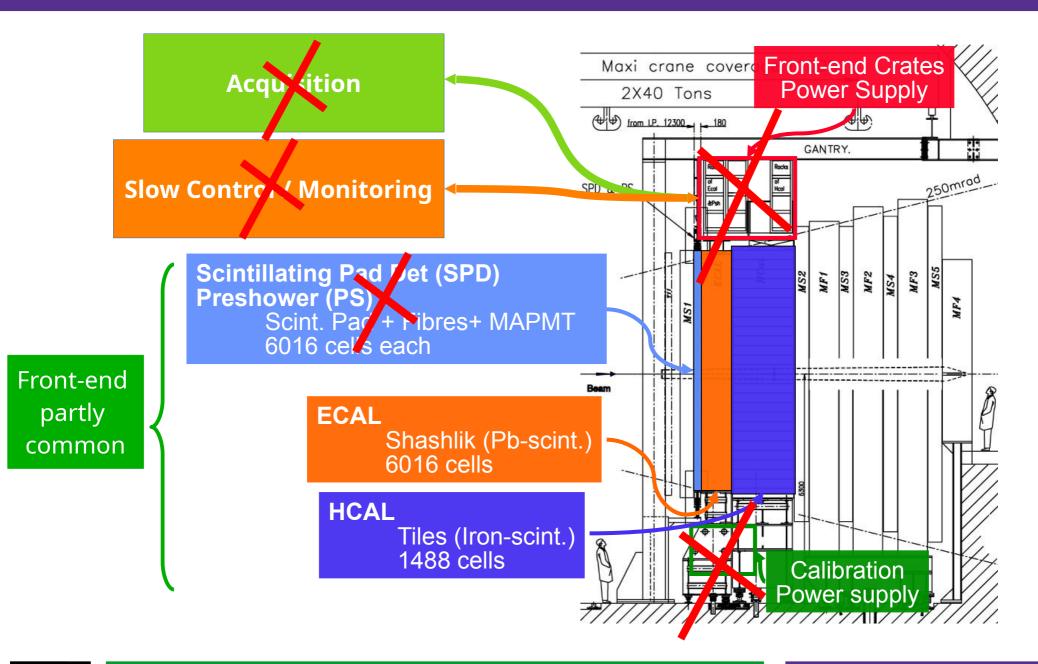

# OVERVIEW OF THE CALORIMETER UPGRADE

- New design of the Front-end electronics, the acquisition and the slow control

- The calorimeter data sent @ 40 MHz to the upgrade-HLT / PC-farm

- The gain of the cells was changed (HV + analog electronics gain) to improve the physics case

- All the communications are based on the GBTx system

- The SPD/PS system is removed

- Not so important after LO disappears

- Particle identification is affected

- But easier calibration of the ECAL/better resolution

## THE CALORIMETER SYSTEM – RUNS I & II

### WHAT WAS CHANGED FOR THE UPGRADE

F. Machefert - ECAL U-II Workshop

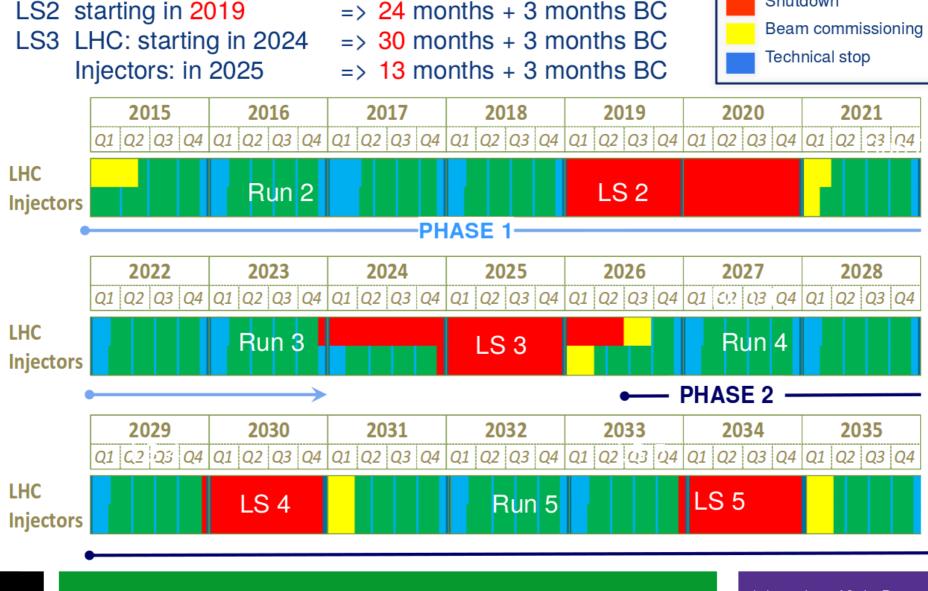

# ORIGIN OF THE PROJECT

- It was important to well define the scope of the project

- Jacques Lefrançois contributed a lot to the preparation of the project

- Thanks also to Marie-Noëlle Minard for her strong support from the beginning

- We tried to think early of the details keeping in mind the time allowed

- Mostly fixed by the schedule of the LHC (which drifted afterwards !)

- Early, we had a clear idea of the possible financial resources we could get

- We could not imagine having the budget to replace the modules

- This clarified early the scope of the project

- And clarified the human resources needed

- We looked for external contributors straight away

- 2 reasons :

- IN2P3 / IJCLab(LAL) would not have been able to make it alone

- We benefited a lot from the experience of the other groups

- We wanted to share the work early and started to discuss with the people we knew to be capable of having a strong impact

- Not always the people who speak loud but those that are competent

- Among the contributors to the Runs I & II Calo  $\rightarrow$  the **Barcelona group** (electronics of the SPD)

- Clermont could not work on the project (SciFi)

- But we benefited a lot from their knowledge of the SPD/PS for the dismantling → their responsibility and they did it perfectly !

- Annecy was involved In the mechanics from the beginning → essential contribution (movement of the detector)

- The russian groups had contributed to the HV / Calibration / Monitoring systems

- Had to be adapted to the new slow control → important contribution from them (ITEP, INR, IHEP) → huge work from Yuri Guz

# THE LHC SCHEDULE IN 2015...

F. Machefert - ECAL U-II Workshop

Monday 12th Dec. 2022

Physics Shutdown

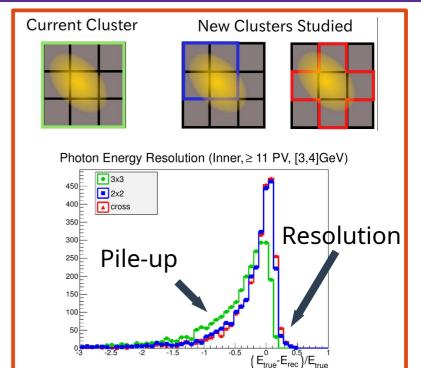

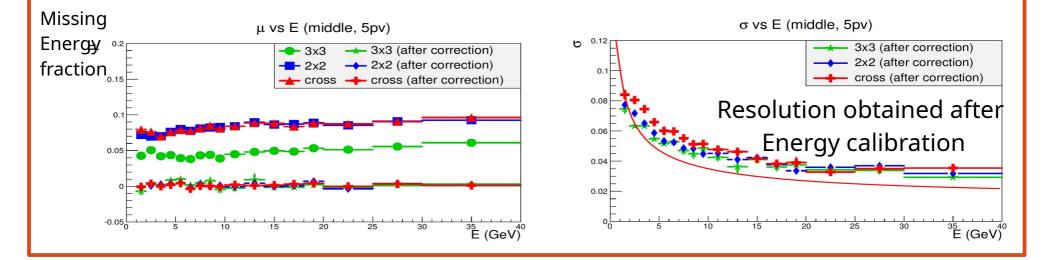

# EARLY PERFORMANCE STUDIES

- We studied the performances of the upgrade I detector (A. Vallier's thesis)

- It was not clear how to cope with the larger occupancy

- We knew that we would not improve the overall performances

- We tried to identify the possibilities to get similar performances as for the "original" calo

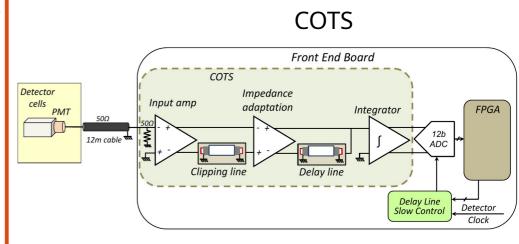

# THE FE ELECTRONICS

- We benefited from two parallel designs of the analog electronics by Barcelona

- The two groups worked together and most people contributed to the two developments

- We benefited from the collaborations of the two "teams" and the sharing of knowledge

- The final choice was based on the performances first, the cost was NOT the priority

- The criteria have been clearly defined early in the development of two designs

- We could decide in 2015 without too much frustration to go for the ASIC

- ICECAL production on a shared waffer

- Important reduction of the cost

# **FE ELECTRONICS**

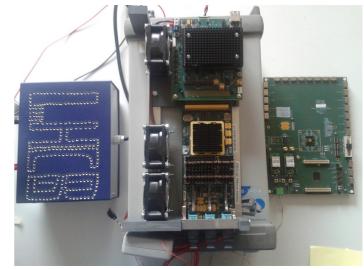

- The first prototype for a FEB was a board that we used essentially to test the analog part, new ideas and components (performances and radiation tolerance) :

- Could host a mezzanine with any type of analog design

- Two FPGAs

- A Socket to host antifuse FPGA

- A flash based FPGA was soldered

used for the data acquisition

- 12 clocks with adjustable phases feeding the Analog/FPGA

- The board could produce its own clock or use an external one

- Synchronisation during test beams

- 10 input/output connectors (LEMO)

- Used as tools to feed or extract user signals

- Communications based on

- A USB port associated to an acquisition / configuration / monitoring software

- A SPECS mezzanine (to be used for irradiation tests)

- Two copies of the same test bench in the two labs involved

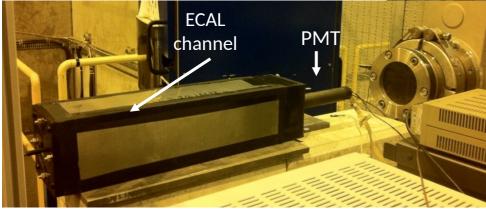

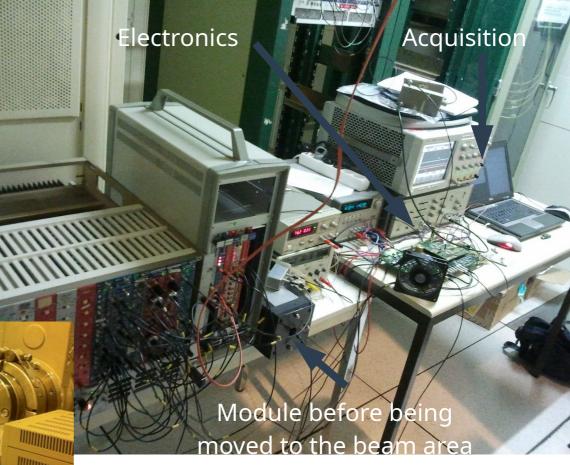

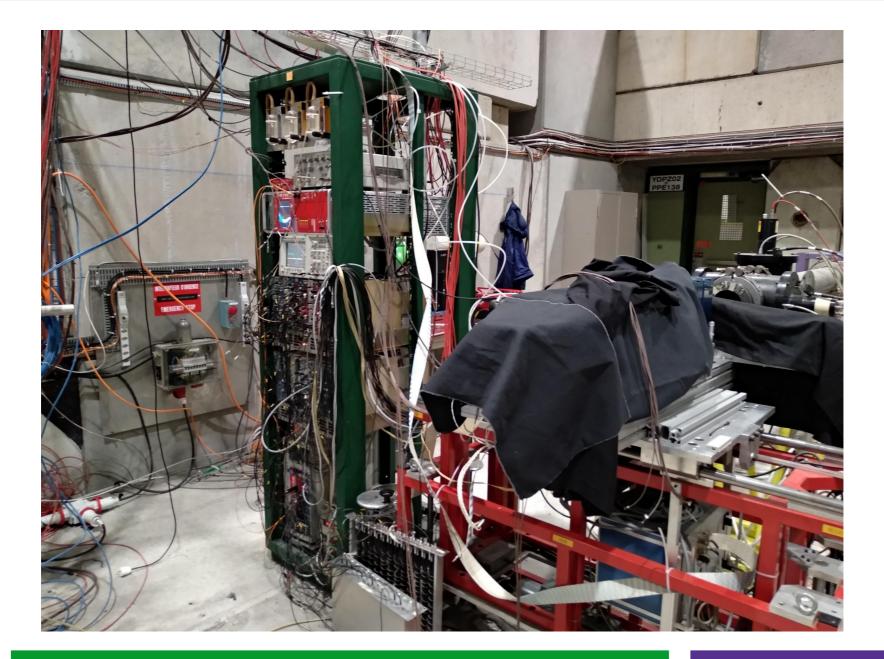

## **TEST BEAMS**

- We did several test beams where we tried to reproduce the most realistic conditions

- We used from the beginning the same cables/modules/PMT/CW bases/... as those used in the cavern

- The pulse shapes were digitised and stored to be generated in the labs in the future

F. Machefert - ECAL U-II Workshop

## **TEST BEAMS**

- We had a "home made" acquisition based on a USB interface and a software designed in our lab

- The test beams have always been the place for discoveries of "features" of our systems

- Having our own acquisition permitted to adapt it "on the fly" sometimes

F. Machefert - ECAL U-II Workshop

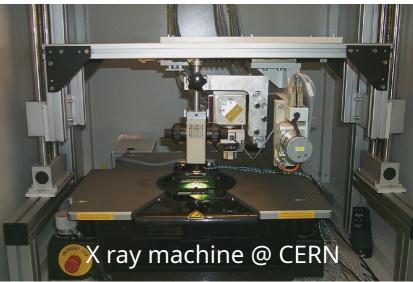

# **IRRADIATION TESTS**

- We had done many tests before the Run I

- GANIL, CERN, Louvain-La-Neuve, PSI, CPO

- We re-used components tested for the Run I design

- But we could not do that for the most critical ones (FPGA, analog chip, ...)

- We organized tests at CERN and Louvain-la-Neuve

- We benefited a lot from the possibility of "last minute" designs of tools by the technicians of the labs

- Being able to adapt quickly was a quality

## EDU AND JOAN IN THE PROTON IRRADIATION BUNKER

- A key ingredient consisted in having a nice and friendly atmosphere in the group

- This depends on the people you work with !

- I don't think that putting pressure on people is the way to go

- But we could afford it as we had quite a lot of margin in the preparation of the Run III

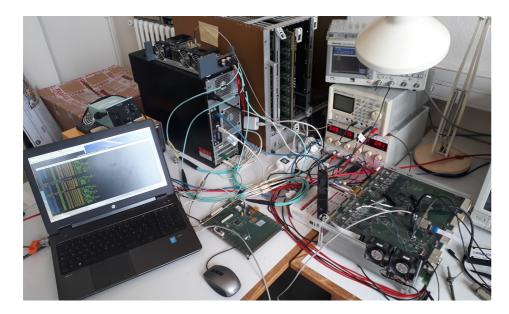

# FIRST FEB PROTOTYPES

- It was important to have nice and efficient tools (not necessarily expensive !) to debug and study the systems under development

- We benefited from old tools designed for the Run I

- Handy backplanes, frames to hold the prototypes

- Don't necessarily dump old things

#### F. Machefert - ECAL U-II Workshop

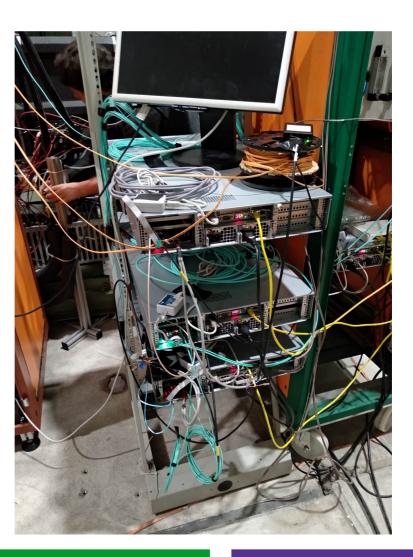

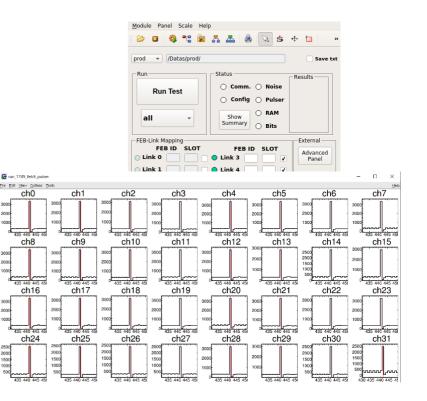

## ACQUISITIONS

- We had our own acquisition based on a USB port and some C++/python programs

- We received a MINIDAQ early

- But not ready yet / in heavy development

- not easy to use

- We needed a "stable" acquisition while the optical link acquisition was still under development → USB

- What do you do when you have a failure of the optical part ?

#### F. Machefert - ECAL U-II Workshop

# SOFTWARE FOR THE DETECTOR

- We had the chance of having from the beginning computing engineers interested in detector design and detector engineers interested by the software

- Could fill the gap between the software and the hardware

- Helped a lot in every day debugging of the hardware

| <b>\$</b>           |            |                                  | MiniDAQ: TOP (System1  | - LAL_MiniDAQ2; #1) |                                | + _ ×                    | <b>@</b> |                                                     | HC1_FEB5:                | OP (System1 - LAL_MiniDAQ2; #1)    | 1                              |                | 0 =        |

|---------------------|------------|----------------------------------|------------------------|---------------------|--------------------------------|--------------------------|----------|-----------------------------------------------------|--------------------------|------------------------------------|--------------------------------|----------------|------------|

| LHCb                | System     | State                            |                        |                     |                                | Mon 03-Feb-2020 16:57:27 | IHCh     | Device                                              | State                    |                                    | Mo                             | on 03-Feb-2020 | 0 16:59:25 |

| <i>LHCD</i><br>THCD | MiniDAQ    | PAUSED                           | A 8 -                  |                     |                                |                          | THCD     | HC1_FEB5                                            | RUNNING                  | ▲ ∨ -                              |                                |                |            |

| Sub-S               | «<br>LHCD  | DAQ: TOP (Systs<br>System<br>DAQ | EHCD                   | LAL0: TOP (Sys      | item1 - LAL_MiniDAQ2;<br>State | Mon 03-Feb-2020 16:57:28 |          | AL System1:HC1 FEB5                                 | Recipe InitGB            | fx <b>v</b> Apply DEFAU            | LT Save Update                 |                |            |

| TF                  | 1          |                                  | гнср                   | LAL0                | RUNNING -                      |                          |          | Derandomizer state                                  |                          | Reset                              |                                |                |            |

| MiniDAQ             | Sub-System | State                            | Sub-System             | State               |                                |                          |          | Front-End Sequencer                                 |                          | Global ALL - ICEC                  | AL ALL Y FE PGA                |                |            |

|                     | TELL40     | RUNNING ~                        | HC1_3CU                | RUNNING -           | 1                              |                          |          |                                                     |                          |                                    |                                | 5              |            |

|                     | LALO       | RUNNING -                        | HC1_FEB0               | NOT_READY -         | ×                              |                          | Г        | FEB Identification                                  | Sequencer Configurat     |                                    | GBTx Clock Phase               |                |            |

|                     |            |                                  | HC1_FEB1               | NOT_READY -         | ×                              |                          |          | Crate                                               | Enable BXID reset        | Output Eport Trig<br>Latency Clock | land la                        |                |            |

|                     |            |                                  | HC1_FEB2               |                     | ×                              |                          |          | Slot                                                | Enable sync              | 0 0                                | Gbt0 ChA 1 23                  |                |            |

|                     |            |                                  | HC1 FEB3               |                     | ×                              |                          |          | Number                                              | OFF • ON                 | Sync pattern CCC                   | Gbt0 ChB 1 23<br>Gbt1 ChA 1 23 |                |            |

|                     |            |                                  | HC1_FEB4               |                     | ×                              |                          |          | Number                                              | GlobalPMEnable           | BXID offset 3320 \$                | Gbt1 ChB 1 23                  | 8              |            |

|                     |            |                                  | HC1_FEB5               | RUNNING -           |                                |                          |          |                                                     | OFF ON                   |                                    | Gbt2 ChA 1 23<br>Gbt2 ChB 1 23 |                |            |

|                     | Messages   |                                  | HC1_FEB6               |                     | ×                              |                          | L        |                                                     | StopSyncLoop<br>NO • YES | GBT Mode Normal 💌                  | Gbt3 ChA 1 23                  | 8              |            |

|                     |            |                                  | HC1_FEB7               |                     | ×                              |                          |          |                                                     | StopInjLoop              | Apply 🔵                            | Gbt3 ChB 1 23                  | Apply          |            |

|                     |            |                                  | HC1_FEB8               |                     | ×                              |                          |          | Front-End Configuration                             | NO • YES                 |                                    |                                |                |            |

|                     |            |                                  | HC1_FEB9               | RUNNING             |                                |                          |          |                                                     |                          | - Subtraction                      | RAM                            |                |            |

|                     |            |                                  | HC1_FEB10              |                     | ×                              |                          |          | 80MhzClkEport                                       |                          | Disable Subtraction                | Clock                          |                |            |

|                     |            |                                  |                        |                     | ×                              |                          |          | <ul> <li>ClockStrength</li> <li>DataPath</li> </ul> |                          | OFF • ON                           | O L0                           |                |            |

|                     |            |                                  | HC1_FEB11<br>HC1 FEB12 |                     | ×                              |                          |          | DIEport                                             |                          |                                    | ChannelB                       |                |            |

|                     |            |                                  |                        | -                   | ×                              |                          |          | 😑 EnableEport                                       |                          | Old Subtraction<br>OFF • ON        |                                |                |            |

|                     |            | - 9                              | HC1_FEB13              |                     | ×                              |                          |          | <ul> <li>TermEport</li> <li>TrackMode</li> </ul>    |                          |                                    | RAM Loop Enabled               |                |            |

|                     |            | G                                | HC1_FEB14              |                     |                                |                          |          | Phase Group 0-3 3-7                                 |                          | 0 🗢                                | Test Length 50                 |                |            |

|                     |            |                                  | HC1_FEB15              | NOT_READY *         | ×                              |                          |          | Phase Group 4                                       |                          |                                    |                                |                |            |

|                     |            | _ S                              | Messages               |                     |                                |                          |          | GbtStatus                                           |                          |                                    |                                |                |            |

|                     |            | 0                                |                        |                     |                                | Close                    |          |                                                     |                          | Apply                              | ] •                            |                |            |

|                     |            |                                  |                        | art step: 1         | Apply                          | FW Versions              |          |                                                     |                          |                                    |                                |                |            |

|                     |            |                                  |                        |                     |                                |                          |          |                                                     |                          |                                    |                                |                |            |

|                     |            |                                  |                        |                     |                                |                          |          |                                                     |                          |                                    |                                |                |            |

# MARKETS

- 2 big markets for the upgrade

- FPGA (CERN)

- The FEBs (CNRS)

- Could avoid market for the 3CU

- FPGA

- No choice in the components

- One company... but several distributors

- SciFi had a (very) bad experience, we (CERN) benefited a lot from their difficulties

- Concerning the FEB

- 5 companies responded to the market survey

- We had worked with one of them  $\rightarrow$  made our first proto, our preference

- One company was very aggressive in term of cost and schedule

- We can imagine that the one we had "choosen" thought CNRS would accept an important overcost

- Tried to reduce to the minimum the impact of the cost on the choice of company, but this was not sufficient

- No possibility to visit or contact any company after the market was launched and until it was closed !

- Our visit of the "winner" increased our worries

## MARKETS

- At the end of the first visit, they called a taxi to take us back to the airport... a Maserati

- First time I seat in such a car

- This was a bad sign : be careful if this happens to you

- A dark cloud appeared when they presented the detailed schedule of the production a couple of months later

- Incompatible with the LHC schedule

- In complete violation with the contract they had just signed !

- We took a bus to go back to the airport

- We had to keep the dialogue without allowing any drift of the schedule

- Conflictual situation and meetings every one/two week(s) until the production ended

- We had to follow the production and watch out carefully for its quality

- We could avoid launching a market for the 3CU...

- Having some market experts nearby is a clear asset

#### Monday 12th Dec. 2022

F. Machefert - ECAL U-II Workshop

## REVIEWS

- The CERN reviews (EDR, PRR, etc...) have been very beneficial to the projet

- We closely followed the advices and comments of the referees

- Not following some remarks would have clearly led to serious difficulties

- We have always been impressed by the competence of the reviewers

- However, we have been asked to participate to other reviews (not @CERN)

- Those reviews did not aim at improving the project

- No experts in the panels  $\rightarrow$  would have been a waste of time

- The aim was to give some activity to the administration  $\rightarrow$  deny if you can !

- We did not document the project enough and regularly

- We had good intentions, but by lack of time and laziness, we did not follow them

- We clearly pay that now and recovering from this situation is painful

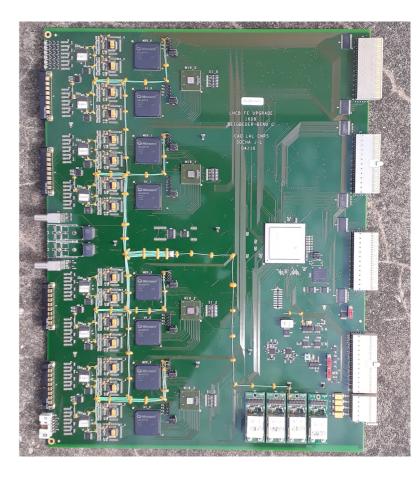

# PRODUCTION

- Should we have produced with the company that made our first prototypes, we would have produced 16 + 280 boards

- We asked for 2 + 16 + 280 boards

- 2 extra boards requested ASAP to check the competence of the new company

- The pre-production 16 boards (a crate) has been crucial

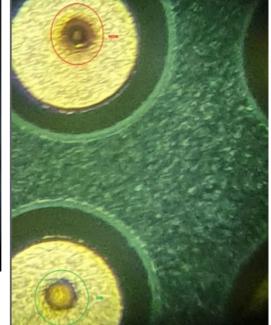

- Discovery of a problem affecting ~13% of our optical light emitters

- Could not be seen with a prototype or 2 boards

- For the Run I & II we had only 16 spares (~5%)

- This was too few. Moreover, some boards could not be debugged after production → we started the Run I with ~ 12 spare FEB

- For the Run III we decided to make 32 spare boards (~10%)

- It was a good idea : we could give a fraction of our boards for Plume

- We missed the *electronics meetings at CERN* that gathered ALL the sub-detectors during the Run I preparation (Jorgen Christianssen)

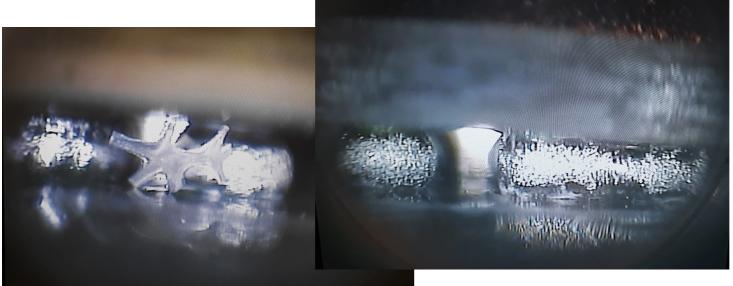

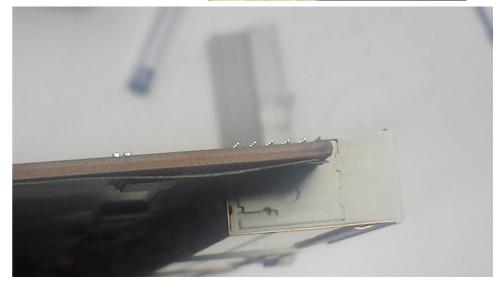

## **PRODUCTION PROBLEMS**

- We had some problems

- Oxydation on the contacts,

- Layers of boards not well glued,

- Bad soldering, ...

- We started with a comfortable margin, we finished just on time !

### TEST BEAM WITH THE FINAL DESIGN

F. Machefert - ECAL U-II Workshop

# TEST BEAM WITH THE FINAL DESIGN

- ... a realistic acquisition (Minidaq3) and the online experts (big thanks !)

- Nothing would have replaced such a test !

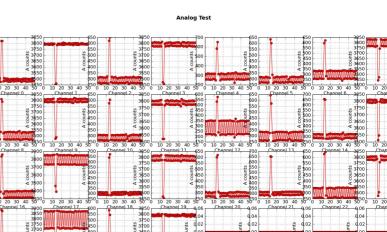

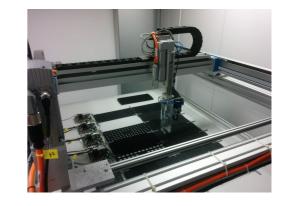

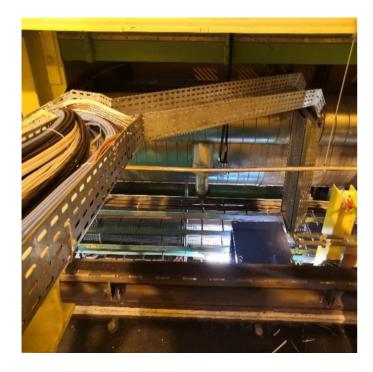

# TEST OF THE PRODUCTION

• Barcelona fully automatized the test procedure of the more than 3000 ICECAL chips

Robot

movement

- The efficiency of the software tools has been important to speed up the validation of the production (~300 complex board to test)

- Contributions of the members of the groups for the test

- The organisation was such that from the early development to the end of the projects, we had physicists and engineers working together in the lab

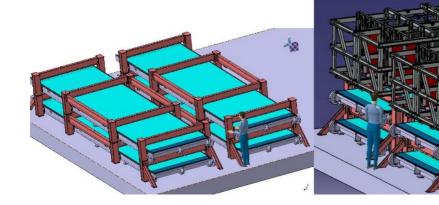

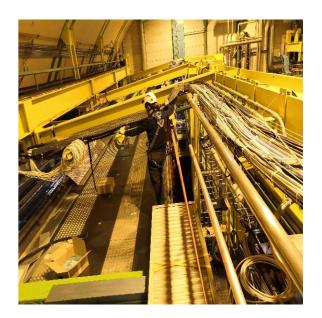

# DISMANTLING OF THE SPD / PS

- The dismantling of the SPD PS has been a heavy task

- Require human resources from several groups

- It was important to have people from CERN / the pit and people knowing perfectly the detectors and how they had been built more than 10 years earlier

- Several tools used for the construction have been re-used / fixed / adapted / copied / developed

- It was a good idea to keep the old tools !

- A precise schedule had been prepared

- A delay may shift the activities of other teams

- Dismantling was followed closely by the installation

#### 26/37

#### F. Machefert - ECAL U-II Workshop

# TESTS OF THE TOOLS

• Tools tested with a 3t load

F. Machefert - ECAL U-II Workshop

### DISMANTLING

28/37

F. Machefert - ECAL U-II Workshop

#### DISMANTLING

29/37

F. Machefert - ECAL U-II Workshop

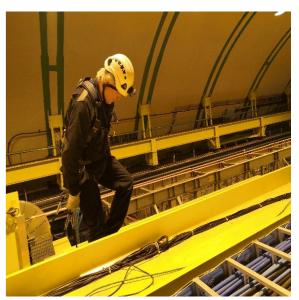

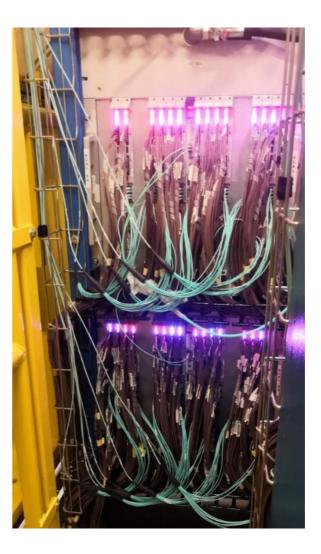

# CABLES AND OPTICAL LINKS

• This is probably the only field were the activity was properly documented... thanks to the CERN teams that were in charge of the installation

#### 30/37

#### F. Machefert - ECAL U-II Workshop

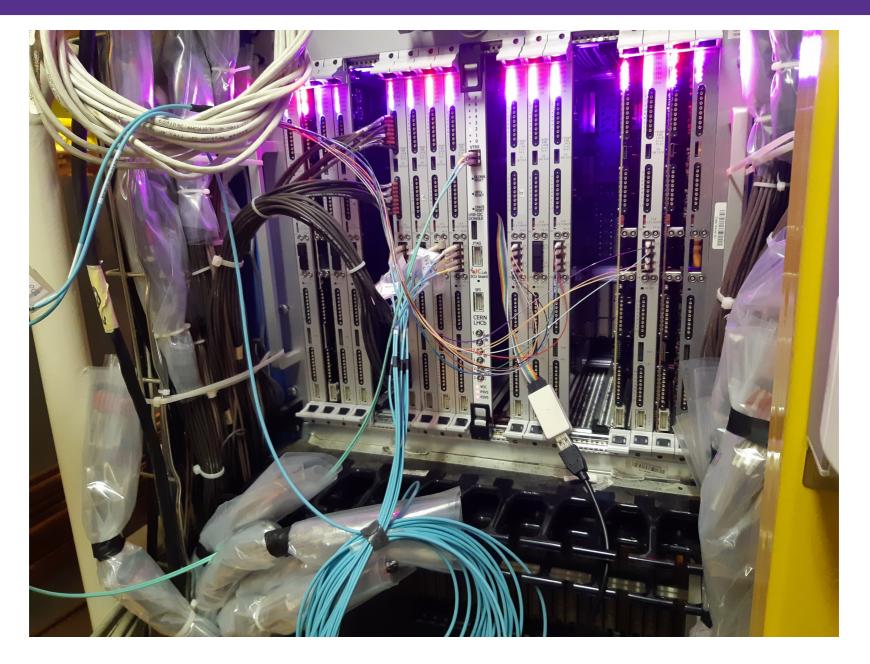

# INSTALLATION OF THE ELECTRONICS

- It was important to put labels on the hardware

- And it is even nicer to have labels that stay glued on the device and that you don't find on the floor after a while !

#### 31/37

F. Machefert - ECAL U-II Workshop

## INSTALLATION OF THE ELECTRONICS

32/37

F. Machefert - ECAL U-II Workshop

# INSTALLATION OF THE ELECTRONICS

#### ... Cabling could start

F. Machefert - ECAL U-II Workshop

#### **EVERYTHING READY IN 2021**

F. Machefert - ECAL U-II Workshop

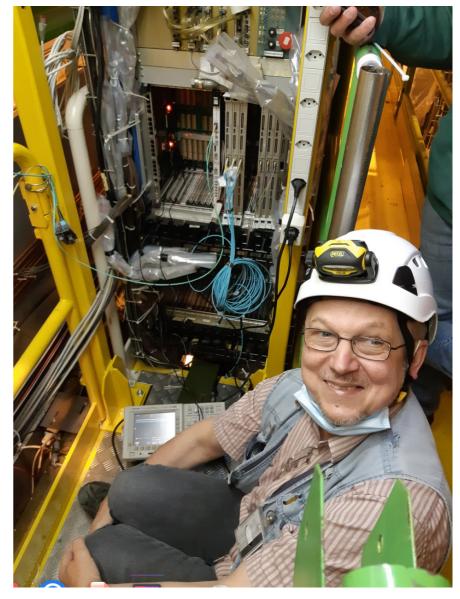

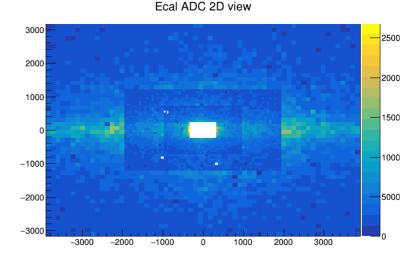

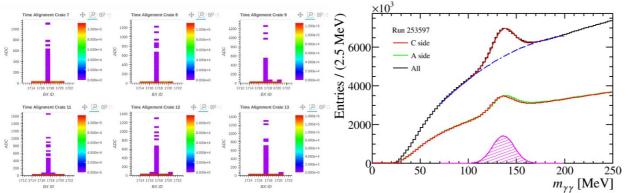

### AND COMMISSIONING STARTS

F. Machefert - ECAL U-II Workshop

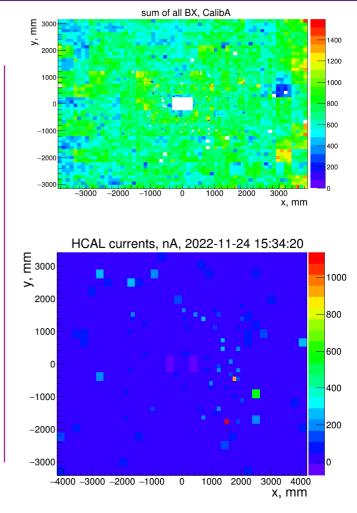

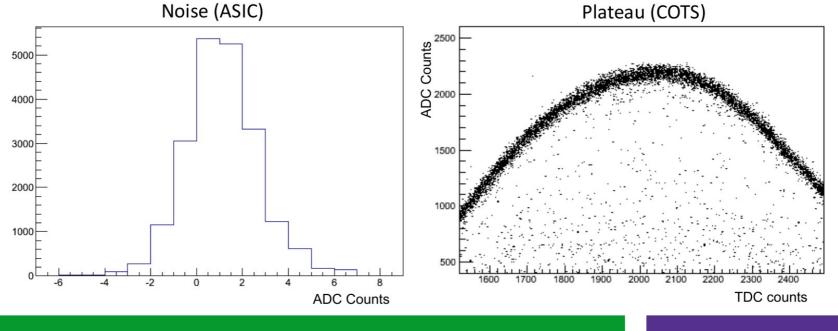

# COMMISSIONING

- With the commissioning the need for software experts (~young people) became more important

- It is important to involve young people early in the project

- We benefit from the methods developped for the Runs I & II

- Still a huge work to adapt to the new systems

- new acquisition, new framework, new constraints, ...

- rewriting everything from scratch could have been more efficient

- It is important to start the software development early

- The reconstruction, simulation (DD4HEP) developments started late

- Thank to some extra-contribution we could catch up

- Automatic test of the code is crucial

#### • The project relies on a VERY SMALL number of people

- Not many exchanges between the upgrade I and upgrade II communities

- LHCb Upgrade II will depend on the success of the Upgrade I

# COMMISSIONING

- We rely on a small group of "old" experts for the maintenance

- PMT / CW replacement, fixing the FEBs

- Younger people are essentially involved in detector tuning, analyzing the data

- There are doing the most important work now

- This dichotomy reflects probably our unability to involve new / young people early in the design of the detector and in the "hardware" activities

- The control room/pit are the best places to learn how the detector works

- We suffer from a distance between the people who made the detectors and the people who look at the data produced

- We do not benefit enough from the experience of those who were analyzing data a couple of years ago !

- My feeling is that this is not true ONLY for the Calorimeter system of LHCb

- I don't think this was so true for the preparation of the Run I