### OBELIX for the Belle II Experiment

### Maximilian Babeluk

on behalf of the Belle II VTX collaboration

AIDAinnova 2nd Annual meeting

Apr 25<sup>th</sup> 2023

Apr 25<sup>th</sup> 2023 1/23

10

8

4

2

2019

<sup>peak</sup> Luminosity [x10<sup>35</sup>cm<sub>2</sub>s<sup>-1</sup>]

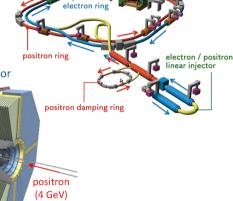

Belle II detector

- Located at the SuperKEKB collider in Tsukuba/Japan

- Asymmetric  $e^+ e^-$  collisions at  $\sqrt{s} = M_{\Upsilon(4S)} = 10.58\,{

m GeV}$

electron (7 GeV)

30 ଢ

20

10 0

2034

- Luminosity-frontier experiment, exploring new physics

- Target:  $\mathcal{L}_{int} = 50 \text{ ab}^{-1}$ , currently at 0.43 ab<sup>-1</sup>

- Right now: long shutdown, restart early 2024

- $\mathcal{L}_{inst}$  will be increased stepwise

- Challenging hitrates expected

l neak(Taros

Interaction

Region

2024

2029

OBELIX for the Belle II Experiment

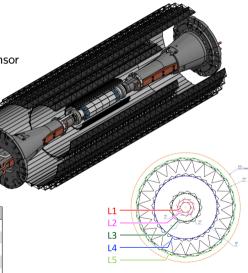

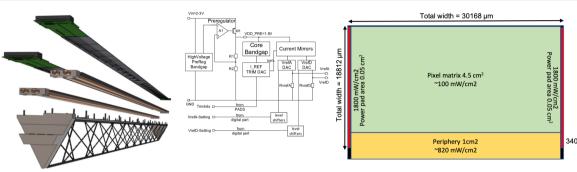

# The VTX Upgrade Concept

- Scheduled for 2027/2028

- 5 straight layers with DMAPS in ladder/stave design

- Identical chips on all layers: Optimized BELIe II pIXel sensor

- Different features enabled on different ladders

- L1 & L2 (iVTX):

- All silicon ladders

- Air cooling (constrains power)

- L3 to L5 (oVTX):

- Carbon fiber support frame

- Cold plate with water cooling

|                  |      |      |      | 0    |       |                  |

|------------------|------|------|------|------|-------|------------------|

|                  | L1   | L2   | L3   | L4   | L5    | Unit             |

| Radius           | 14.1 | 22.1 | 39.1 | 89.5 | 140.0 | mm               |

| # Ladders        | 6    | 10   | 8    | 18   | 26    |                  |

| # Sensors        | 4    | 4    | 8    | 16   | 24    | per ladder       |

| Expected hitrate | 18.0 | 6.7  | 1.7  | 0.45 | 0.22  | $MHz/cm^2$       |

| Material budget  | 0.1  | 0.1  | 0.3  | 0.5  | 0.8   | % X <sub>0</sub> |

# **OBELIX Key Requirements**

- High hit efficiency at demanding hitrates and radiation levels

- 2. Handling trigger latency of the Belle II experiment

- 3. Power dissipation allowing air cooling of inner layers and water cooling of outer layers

- 4. Low space for cables inside detector

5. Fast but coarse hit information as input for Belle II trigger

- Evaluation still ongoing

- New implementation of digital periphery

- Simulation to validate performance

- Optimized digital logic

- 1 or 2 LVDS link(s) per chip (Tx)

- 2 LVDS links for groups of chips (Clk, CMD)

- On chip voltage regulators

- Independent data path

- Low granularity/low latency transmission

**OBELIX** for the Belle II Experiment

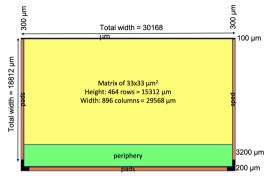

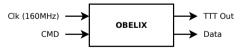

# The OBELIX chip

- Fast clock of TJ-Monopix2 is 160 MHz

- OBELIX clock 1/3 Belle II RF (509 MHz)

- Often round numbers stated

- Matrix from TJ-Monopix2, only size adjusted

- 464 rows and 896 columns

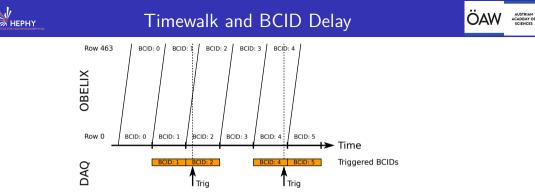

- Timestamp resolution:  $\sim 50\,\text{ns}$

- Up to 10 µs trigger latency

- Power: < 1.5 W per chip

- TID tolerance: 100 kGy/year

- $\bullet~$  NIEL tolerance:  $5\times10^{13}\,n_{eq}/cm^2/year$

- Hitrates up to 120 MHz/cm<sup>2</sup> (continuous):

- Safety factor of 5

- Hitrate spikes due to injection expected

| Clock signal | Rounded | Real value | Period  |

|--------------|---------|------------|---------|

| Fast clock   | 160 MHz | 169.7 MHz  | 5.89 ns |

| Slow clock   | 20 MHz  | 21.2 MHz   | 47.1 ns |

| TXU clock    | 32 MHz  | 33.9 MHz   | 29.5 ns |

USTRIAL

ADEMY O

### **OBELIX** Power Management

- Long linear ladders: voltage drop across ladder

- Narrow LDOs on both sides of the chip

- Input voltage 2 to 3 V

- LDOs cause some dead area, but TJ-Monopix2 matrix requires power from the sides

- Aspect ratio of regulators as high as possible to keep dead area small

AUSTRIAN

CADEMY OF

CIENCES

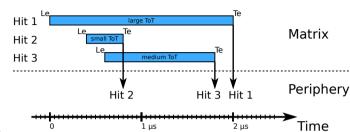

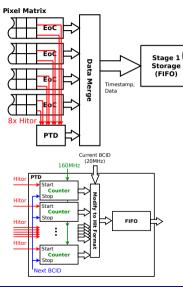

## Matrix Readout

#### TJ-Monopix2 Readout Scheme:

- Also used in OBELIX

- Charge information over ToT measurement (up to 2 µs, tunable)

- Hit is released to periphery after trailing edge

- Leads to time disorder of received hits

• Max ToT defines how late data may come in datastream

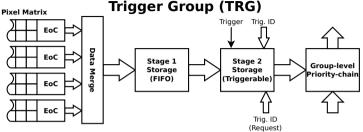

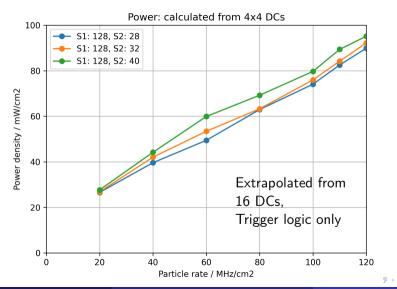

# **OBELIX** Trigger Group

ÖAW

#### Sophisticated 2-Stage trigger logic:

- Trigger memory organized in 112 Tigger Groups (TRGs), each connected to 4 DCs

- Stage 1 (128 hits): Pre-trigger buffer SRAM, low power dissipation

- Stage 2 (32 hits): Associative memory to match trigger with hitdata, power hungy

- Time-disorder (2  $\mu s)$  less than latency (10  $\mu s):$  S2 can be smaller than S1

- Buffer sizing driven by power dissipation and hitrate, evaluated with extensive simulations

120 -

100

80

60

40

20

0.0

TRU Power / mW

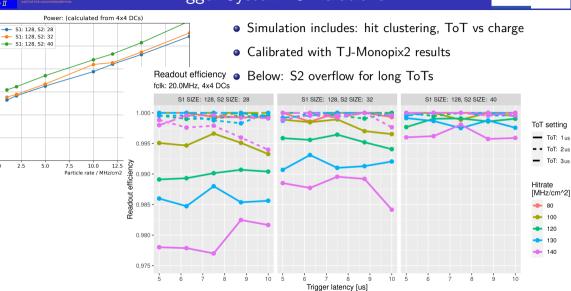

# Trigger System: Simulations

Maximilian Babeluk

Apr 25<sup>th</sup> 2023 9 / 23

AUSTRIAN

ACADEMY OF

SCIENCES

- HitOR: all comparator outputs of one column in an OR-chain (asynchronous)

- PTD: precision timing better than BCID (20 MHz)

- 160 MHz clock frequency

- Power hungry feature: disabled in iVTX

- PTD data stored in (fake-)hit data with nonexistent row addresses

- No extra storage needed for PTD, re-use of large trigger memory needed for higher hitrates

- Little overhead in terms of area/space when disbaled

- Resolution limited by timewalk and PVT of HitOR delay

AUSTRIAN

ADEMY O

AUSTRIAN

ADEMY O

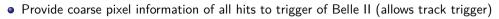

- Allows a Belle II trigger based on track information (track trigger)

- Low transmission latency is wanted (leaves more time for trigger algorithm)

#### Solution: Track Trigger Transmission (TTT)

- Separate transmission logic independent from normal OBELIX readout system (extra LVDS link))

- Power constrains this to the oVTX (outer 3 water cooled layers)

- 2 to 8 logical macropixels per whole chip (configurable)

- 160 MHz DDR transmission (320 Mb/s, 8b/10b encoded)

- No framing, no sync necessary, bit is set when HitOR of macropixel rises

- The OBELIX chip is based on the analog part of TJ-Monopix2

- The digital periphery will have several additional features

- Versatile chip for large dynamic range of hitrates

- Still under development, but significent progress recently

- Feature completeness planned for July 2023

- Verification ongoing

### **Backup slides**

Maximilian Babeluk

OBELIX for the Belle II Experiment

Apr 25<sup>th</sup> 2023 13 / 23

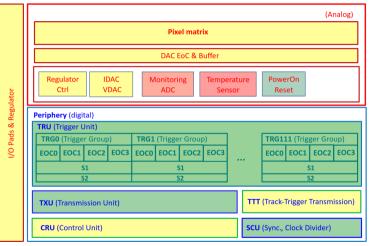

### **OBELIX Block Diagram**

- On chip LDOs (1.8V)

- On chip trigger logic (TRU)

- Fast triggerless output for Belle II Track Trigger (TTT)

AUSTRIAN

ACADEMY OF

$\Box \Delta$

- Precision timing counter improve timing for outer layers

- On chip ADC for temperature measurement and calibration

НЕРНҮ

Relle 1

OBELIX for the Belle II Experiment

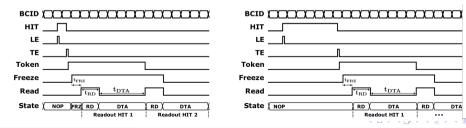

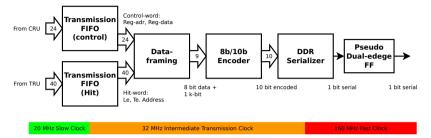

# Transmission Unit (TXU)

- Most TXU components run at 32 MHz (160 MHz/5) intermediate clock

- Serializer needs one byte (10 bit encoded, DDR) per 32 MHz clock cycle

- This allows simple state machines

- Clock boundary to 20 MHz clock is done via FIFO

- Hits are sent in frames sharing the same leading edge BCID

#### Goal:

- Provide coarse pixel information of all hits to trigger of Belle II

- Allows a Belle II trigger based on track information (track trigger)

- Power constrains this to the oVTX (outer 3 water cooled layers)

- Low transmission latency is wanted (leaves more time for trigger algorithm)

#### Solution: Track Trigger Transmission (TTT)

- Independent from normal OBELIX readout system

- Separate transmission logic (and extra LVDS link)

- 2, 4 or 8 logical macropixels per whole chip (configurable)

- Whole columns grouped via HitOR (56 to 224 DCs create one macropixel)

#### **OBELIX LVDS Connections**

AUSTRIAN

CADEMY O

- $\bullet\,$  Continous data stream is sent out, 8b/10b encoded

- Bit corresponding to macropixel is set once when rising edge on HitOR

- No data frames, each byte sent stands for its own and defines timing

- No sync needed

- 160 MHz DDR transmission (320 Mb/s)

- Resolution from clock: 29.6 ns (boxlike,  $\sigma = 8.5$  ns)

- Uncertainty from HitOR: 35 ns (boxlike,  $\sigma = 10.1$  ns)

- Total time resolution:  $\sigma \sim 13\,\mathrm{ns}$

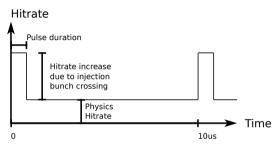

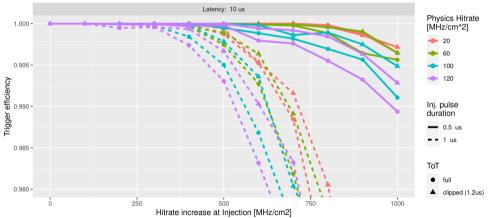

- Hitrate is time modulated

- To the physics hitrate, an increased pulse is added

- Trigger is NOT vetoed some triggers will happen during injection bunch

- Two different pulse durations tested:  $0.5 \,\mu s$  (expected) and  $1 \,\mu s$  (much more demanding)

AUSTRIAN

CADEMY O

SCIENCES

Trigger efficiency fclk: 20.0MHz, 32x4 DCs

НЕРНҮ

Relle T

イロト イヨト イヨト イヨ

- Short pulses of high hitrate do not degrade performance

- Longer spikes create performance degradation

- For 0.5  $\mu s,$  up to 800 MHz/cm² of BG have low impact (20 MHz/cm² physics)

- An additional veto mechanism is probably not necessary

- Trigger probability was constant over time (no veto)

- We might have triggers inside the veto in the future

ADEMY O

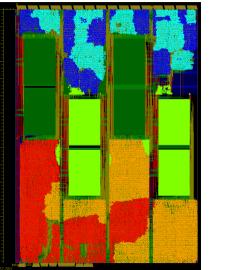

# Floorplan (4x4 Version)

Apr 25<sup>th</sup> 2023 21 / 23

◆□ → ◆問 → ◆ □ → ◆ □ → □ □

ÖAV

AUSTRIAN ACADEMY OF SCIENCES

### Power simulation

Maximilian Babeluk

OBELIX for the Belle II Experiment

AUSTRIAN

SCIENCES

OΔ

- The plan is: no further precautions for the chipdesign

- OBELIX can handle triggers on multiple subsequent BCIDs

- The DAQ system automaically can create e.g two triggers for BCID, BCID+1 for the same event

- Easily reconfigurable if e.g. three BCID frames are necessary

- At 30 kHz trigger rate, link speed is not limiting