## WP5: Activities on TPSCo 65 nm process

#### Report by Jerome Baudot for a large community

- → Interest for sensors in a 65 nm process

- → 1<sup>st</sup> submission MLR1 findings

- → Contents of ER1

- → Plan for ER2

# 65 nm & requirements from WP 5

#### Sensor spatial resolution

- Key requirement for Higgs factories:  $\sigma_{sp} \lesssim 3 \ \mu m$

- ALICE-ITS3 ~5  $\mu m$ , Belle II <15  $\mu m$ , trackers >10  $\mu m$

- Detection layer with material budget: 0.05 to 0.15 % X<sub>0</sub>

- Achieved through large stitched & curved sensors

- Key requirement for ALICE-ITS3, strong interest for Higgs factories

- Low power <<100 mW/cm<sup>2</sup>, compatible with air-cooling

- Important for Higgs factories & ALICE-ITS3

- Hit rate and time resolution (highly dependent on experiment)

- Few 10 MHz/cm<sup>2</sup>/s for Higgs-factories

- > 100 MHz/cm<sup>2</sup>/s for Belle II and some trackers

- Time resolution ~ns for CLIC and some trackers

- Specific for PID or 4D tracking: time resolution in ~10 or ~100ps range

- Radiation tolerance to NIEL fluence

- Up to  $10^{12} n_{eq(1MeV)}/cm^2$  for task 5.2

- Mimimum  $10^{15}\,n_{eq(1MeV)}/cm^2\,$  and beyond for task 5.3

- ⇐ critical benefit of small feature size in 65nm for task 5.2

- ⇐ possible with other techno BUT attractive in 65nm due to 12" wafer size

- ⇐ benefit of low supply voltage in 65nm, critical for task 5.2

#### 1

Slightly modified introductory slide from kick-off meeting (April 2021)

- ← requires new readout architectures, critical for both tasks 5.2+5.3

- ← benefit of thin sensitive layer in 65nm, critical for task 5.3

- ⇐ 65nm tolerance to be checked, critical for task 5.3

# A large effort, including AlDAinnova partners 🦓

### Many contributors

University and INFN Torino: F. Benotto, S. Beole, C. Ferrero, V. Sarritzu, U. Savino, S. Perciballi, F. Prino, A. Turcato University and INFN Bari: G. De Robertis, F. Loddo University and INFN Catania: P. La Rocca, A. Triffiro University and INFN Cagliari: D. Marras, G. Usai, S. Siddhanta University of Salerno: R. Ricci University and INFN Trieste: M. Buckland, G. Contin IPHC: J. Baudot, G. Bertolone, A. Besson, R. Bugiel, S. Bugiel, C. Colledani, A. Dorokhov, Z. El Bitar, X. Fang, M. Goffe, C. Hu, K. Jaaskelainen, F. Morel, H. Pham, S. Senyukov, J. Soudier, I. Valin, Y. Wu (also with USTC) CPPM: P. Barrillon, M. Barbero, D. Fougeron, A. Habib, P. Pangaud NIKHEF: R. Russo, V. Gromov, D. Gajanana, A. Yelkenci, A. Grelli, R. Kluit, J Sonneveld, A. Vitkovskiv Heidelberg University: H.K. Soltveit, P. Becht, A. Yuncu **Prague University**: A. Isakov, F. Krizek **Technical University Munich**: L. Lautner, I. Sanna (also with CERN) DESY: A. Chauhan, D.-V. Berlea, M. Del Rio Viera, D. Eckstein, F. Feindt, I. Gregor, K. Hansen, L. Huth, B. Mulyanto, C. Reckleben, S. Ruiz Daza, P. Schütze, A. Simancas, S. Spannagel, M. Stanitzki, A. Velyka, G. Vignola, H. Wennlöf **Technical University Vienna**: J. Hasenbichler (also with CERN) **STFC (RAL)**: A. Hodges, S. Matthew, I. Sedgwick

**Oxford University**: D. Bortoletto, F.Windischofer (also with CERN)

Birmingham University: L. Gonella, P. Allport Bolu University: K. Oyulmaz Talinn University: K. Rebane (also with CERN) Zagreb University: T. Suligoj, D. Dobrijevic (also with CERN) Yonsei University: Y. Kwon, G.H. Hong CCNU: Wenjing Deng (also with CERN) EPFL: E. Charbon, F.Piro (also with CERN)

**CERN:** G. Aglieri Rinella, I. Asensi Tortajada, W. Bialas, G. Borghello, R. Ballabriga, J. Braach, E. Buschmann, M. Campbell, F. Carnesecchi, L. Cecconi, F. Dachs, D. Dannheim, V. Dao, K. Dort, Joao de Melo, W. Deng (also with CCNU), A. Di Mauro, D. Dobrijevic, A. Dorda Martin, P Dorosz, L. Flores Sanz de Acedo, A. Gabrielli, G. Gustavino, J. Hasenbichler (also with TU Vienna), H. Hillemans, .I. Kremastiotis, A. Kluge, T. Kugathasan, M. LeBlanc, P. Leitao, M. Mager, P. Martinengo, M. Munker (now with U. Geneva), L. Musa, H. Pernegger, F. Piro, K. Rebane (also with Talinn University), F. Reidt, P. Riedler, I. Sanna (also with TU Munich), A. Sharma, W. Snoeys, C. Solans, M. Suljic, G. Termo M. Vicente (now with U. Geneva), J. Van Rijnbach (also with Oslo U.)

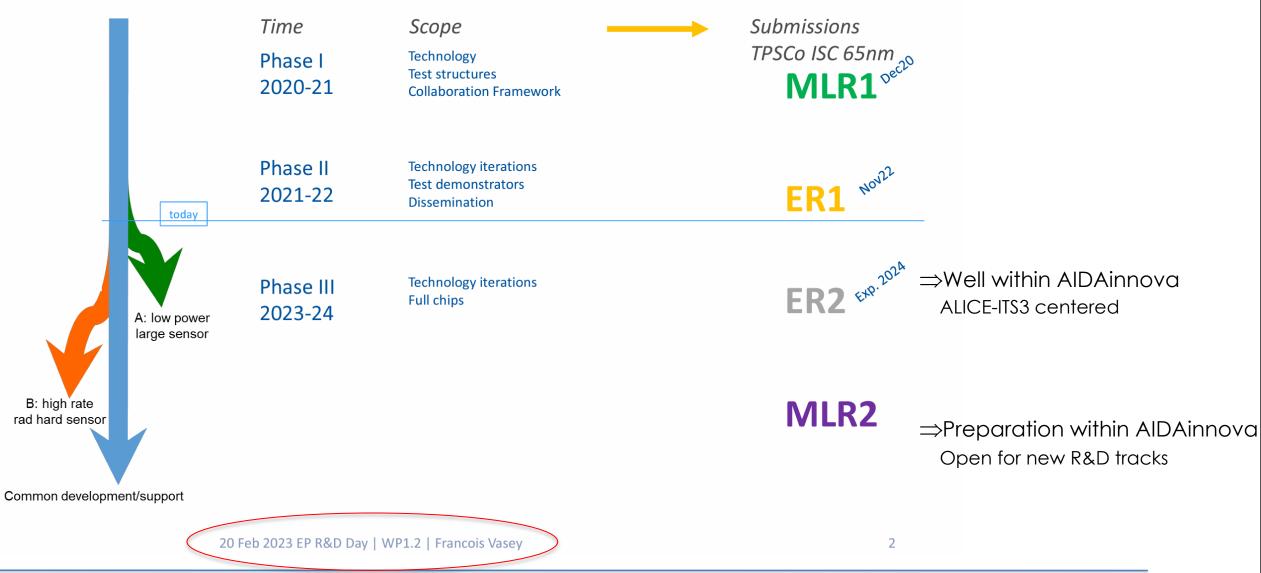

### Timeline

# Reminder on 1st submission

- Multi-Layer Reticule (MLR1)

- 5 metal layers, HR thin (~10µm) epi layer

|              |                                                                         | EP   | R&D  |

|--------------|-------------------------------------------------------------------------|------|------|

| IPHC<br>CE65 | APTS<br>25 µm SF st pw 20 µm AMP Nikher                                 |      |      |

| DEST RAL     | 20 µm PAD 20 µm srac 10 µm AMP Opamp<br>SF chip SF srac 10 µm AMP Opamp | GDS2 | GDS1 |

|              | 15 µm SF SF SF 20 µm AMP Ac                                             | GDS3 | GDS1 |

| CPPM EI      | 10 µm SF SFAC >10 µm AMP                                                |      |      |

- IPHC: rolling shutter larger matrices, DESY: pixel test structure (using charge amplifier with Krummenacher feedback, RAL: . LVDS/CML receiver/driver, NIKHEF: bandgap, T-sensor, VCO, CPPM: ring-oscillators, Yonsei: amplifier structures

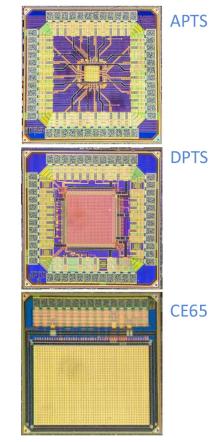

- Transistor test structures, analog pixel (4x4 matrix) test matrices in several versions (in collaboration with IPHC with special amplifier), digital pixel test matrix (DPTS) (32x32), pad structure for assembly testing. CERN

- After final GDS placement, GDS1 is instantiated twice.

- Converged with 4 splits of 3 wafers

• APTS = analogue outputs with OpAmp

$\Rightarrow$  Sensors

• 10-25 µm pitch

- DPTS = digital outputs

- CE65 = analogueoutputs with DC/AC and no-Amp/Amp

- Test & Building blocs

Transistors: no show stoppers (still some measurements to be done)

Ring oscillators: ready for irradiation study

DAC, Bandgap, Temp-sensors, VCO: functional, TID/NIEL irradiations & SEE under-study

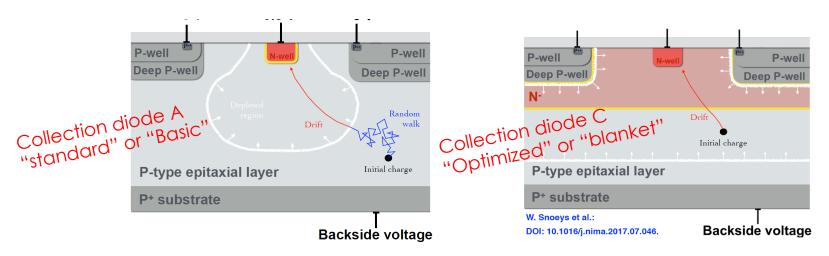

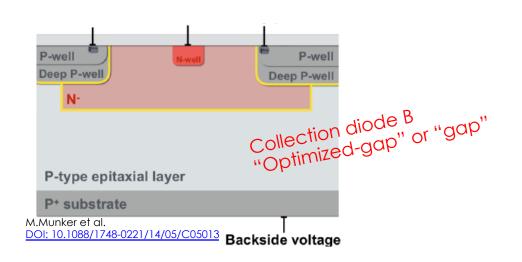

## **TPSCo 65nm process modification**

#### <u>4 process splits</u>

- Doping modifications:

- 1. Default process

- 2. First intermediate process

- 3. Second intermediate process

- 4. Optimized process

- <u>3 collection diode structures</u>

- Following successful modifications in Tower 180 nm

- Standard => Optimized(gap) structures

⇒ Both modifications based on TCAD studies Stll on-going for subsequent submissions

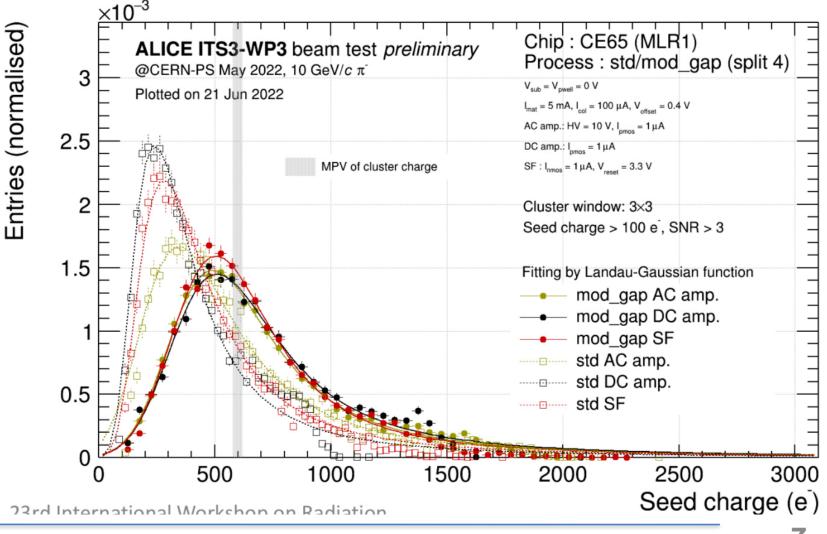

MLR1 findings so far 1/3

#### Process modifications successfull / basic detection

S.Senyukov @ IWoRiD2022

- CE-65 (analog) with 15 µm pitch

- Beam test at DESY

# MLR1 findings so far 1/3

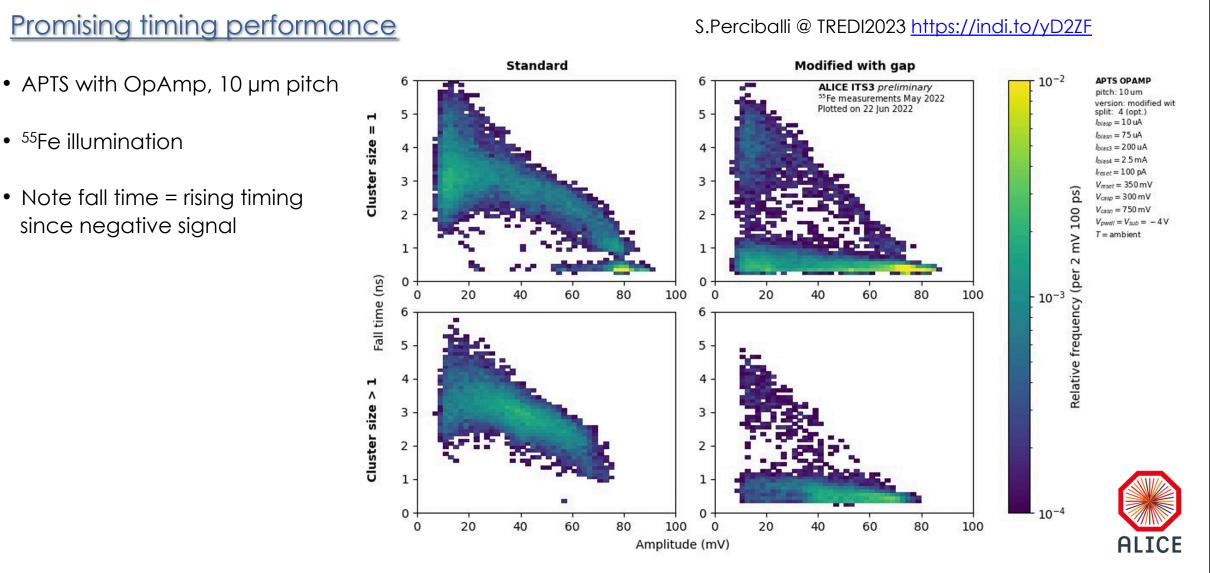

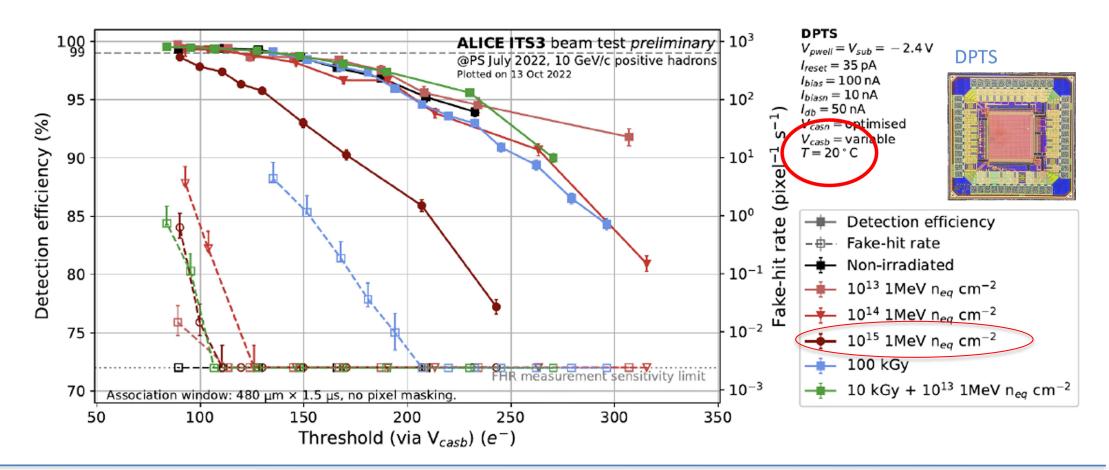

# MLR1 findings so far 3/3

Promising radiation tolerance

S.Perciballi @ TREDI2023 https://indi.to/yD2ZF

- DPTS (digital) with 15 µm pitch

- Beam test results

# 2<sup>nd</sup> submission: Engineer Run 1 (ER1)

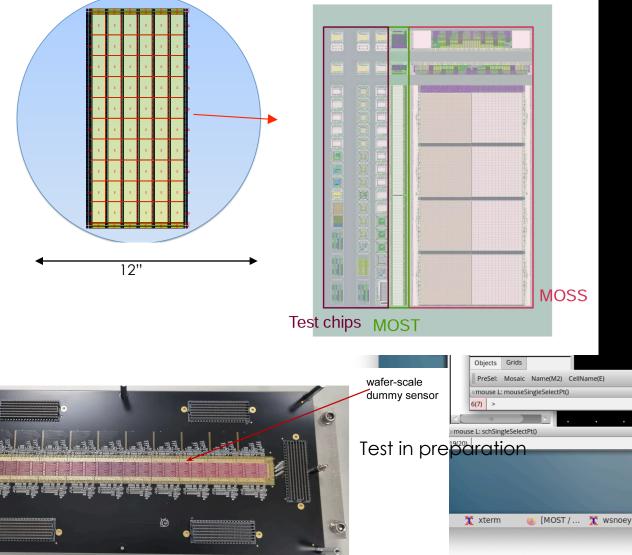

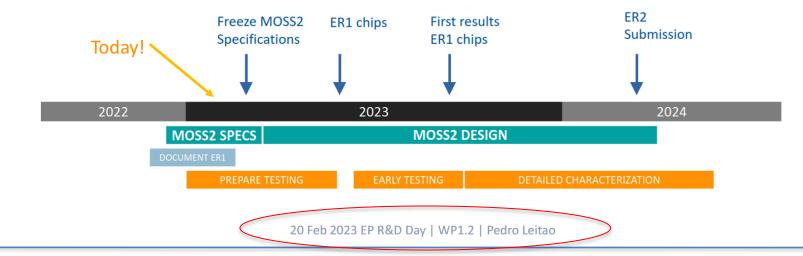

- Main goal = exercise stitching (in 1D) to assess yield

- Submission November 2022

- Back from fab April 2023

- 2 long (~26 cm) sensors

- MOSS: priority-encoder readout (ALPIDE-like)

- 1.4 cm wide

- 18 & 22.5 µm pitch

- MOST: low power asynchronous readout

- 0.25 cm wide

- Many (51) chiplets

- Pixel prototypes

- SEU test chips

- Functional blocks (PLL, serial links)

- New metal staks

- New methodology for submission

- Digital-on-top

## 3rd submission: ER2

### **Towards ER2 submission**

EP R&D

13

- ER2 submission will focus on a large area stitch sensor that targets the ALICE ITS3 requirements

- Build on ER1 learned lessons

- Increased dimensions (1.8 x 26 cm)

- Decreased dead area (between 6.7% 9.5%)

- Increased readout speed (between 25.6 Gbps 51.2 Gbps)

- On chip power regulation for power segmentation and IRdrop compensation (~0.6% active area granularity)

- Design specifications are ongoing

Report by J.Baudot - WP 5: Activities on TPSCo 65nm techno. - 2<sup>nd</sup> AIDAinnova annual meeting, April 2023

## Conclusion

- 1<sup>st</sup> submission: MLR1 Pre-AIDAinnova

- Test structures + Functional blocs

- Various pixel structures

- Design work

- Preparation for **ER2**

- ALICE-ITS3 stitched sensors

- Still some chiplets

- 3<sup>nd</sup> submission: ER2

- Preparation for 4<sup>th</sup> submission

- MLR2 with new R&D tracks

2025

2024

2023

4<sup>th</sup> submission ?

Activities in 2021-23 mostly driven by CERN EP R&D-roadmap & ALICE-ITS3 .

Testing work

- Finalise tests on MLR1

- Start ER1 tests

- 1st test on stitched sensors

- Tests on chiplets

- Continued tests on ER1

- Preparartion of **ER2** tests

- Tests of **ER2**

Still targeting GENERAL GOALS in excellent synergy with WP5

- <u>Question addressed</u>

⇒ Techno validation

- Yield with stitching

- Handling/bending of thin & large (<100cm<sup>2</sup>) area

- Performance optimisation

(space & time resolution

⇒ Techno exploration

• Readiness for ALICE-ITS3

Report by J.Baudot - WP 5: Activities on TPSCo 65nm techno. - 2nd AIDAinnova annual meeting, April 2023

### Supplementary slides

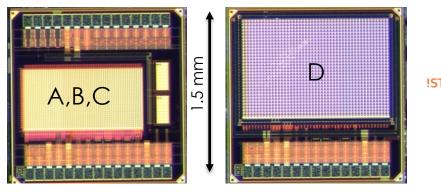

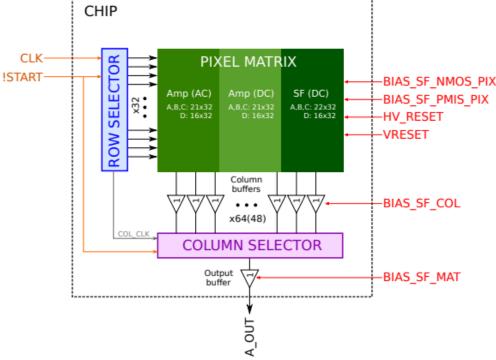

## CE-65 sensors

- Contribution from IPHC

- <u>4 different flavours</u>

- Square pixels

- Analogue output

- Rolling-shutter readout 10 to 40 MHz

| Variant | pitch | Matrix size | Front-ends                  | Collection diode<br>structure | Split |

|---------|-------|-------------|-----------------------------|-------------------------------|-------|

| А       | 15 μm | 64x32       | DC-SF,<br>DC-Amp,<br>AC-Amp | Basic                         | 1-4   |

| В       |       |             |                             | Blanket w gaps                |       |

| С       |       |             |                             | Blanket                       |       |

| D       | 25 µm | 48x32       |                             | basic                         |       |

#### Note:

• AC-coupled front-end allows sensitive volume biasing without backside voltage