# TPSCo 65nm CIS Ring Oscillators Temperature, Irradiation and Annealing tests

Pierre Barrillon, Marlon Barbero, Denis Fougeron, Alexandre Habib & Patrick Pangaud

April 25<sup>th</sup> 2023

AIDA – Innova meeting

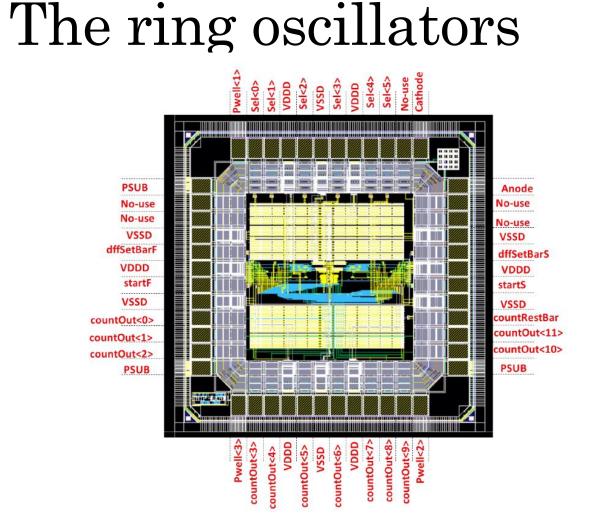

## The ring oscillators

| ${\bf Low} \ {\bf V}_{\rm T}$ |             | Super Low V <sub>T</sub> |              |

|-------------------------------|-------------|--------------------------|--------------|

| Size Min                      | Size+       | Size Min                 | Size+        |

| INV0_LVT                      | INV4_LVT    | INV4_SLVT                | INV8_SLVT    |

| NOR1_LVT_A                    | NOR4_LVT_A  | NOR4_SLVT_A              | NOR8_SLVT_A  |

| NOR1_LVT_B                    | NOR4_LVT_B  | NOR4_SLVT_B              | NOR8_SLVT_B  |

| NAND0_LVT_A                   | NAND4_LVT_A | NAND4_SLVT_A             | NAND4_SLVT_A |

| NAND0_LVT_B                   | NAND4_LVT_B | NAND4_SLVT_B             | NAND4_SLVT_B |

| DFF1_LVT                      | DFF4_LVT    | DFF1_SLVT                | DFF4_SLVT    |

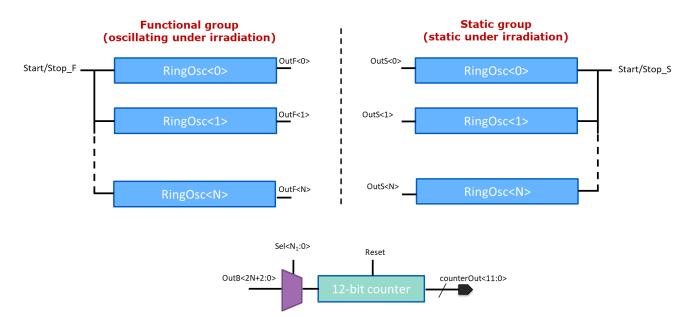

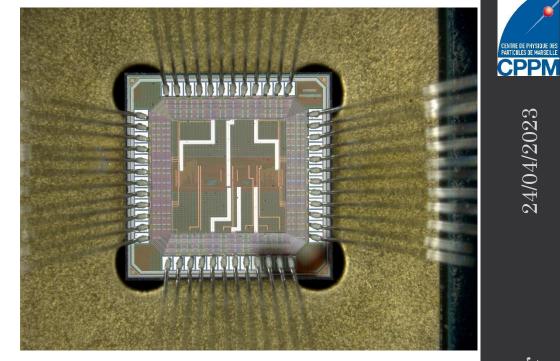

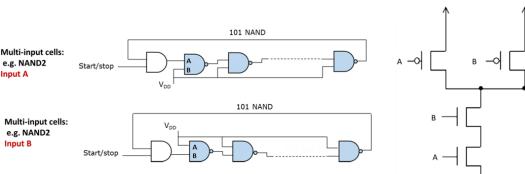

- In 2020, participation to the MLR1 run in TowerJazz 65 nm through CERN's EP-R&D WP1.2, by designing a **Ring Oscillator test chip** to characterize the standard cells of this technology.

- The chip contains 48 ring oscillators made of a chain of 101 standard cells.

- 2 banks of 24 Rows each with the purpose of testing two approaches while irradiating:

- Functional: the oscillation is enabled •

- Static: the oscillation is disabled .

2

24/04/2023

The 24 ring oscillators, of each bank, differ from each other by the **type of cells** they were made of (Inverter, NAND, NOR and DFF), with variations in the transistor width (e.g. Inv0, Inv4 and Inv8, the width being larger with increased number) and threshold (Low VT and Super Low VT). A and B correspond to 2 flavors to observe the effect of the proximity of the power supply rail.

Table 3: Typical oscillation frequencies Schematic

[MHz]

298,9

392,9

304,1

392,9

147,7

184,7

185,1

229,5

152,1

182,6

190,1

226,1

174,3

217,2

200,2

246,6

180,9

213,9

206,6

242,1

344,1

372,5

352,3

383,1

Cell Name

Inv0\_LVT

Inv4\_SLVT

Inv4\_LVT

Inv8\_SLVT

NOR1\_A\_LVT

NOR4\_A\_SLVT

NOR1 B LVT

NOR4\_A\_LVT

NOR8\_A\_SLVT

NOR4\_B\_LVT

NOR8 B SLVT

NANDO A LVT

NAND4\_A\_SLVT

NANDO B LVT

NAND4\_B\_SLVT

NAND4\_A\_LVT

NAND8\_A\_SLVT

NAND4\_B\_LVT

DFF1\_LVT

DFF1\_SLVT

DFF4\_LVT

DFF4 SLVT

NAND8\_B\_SLVT

NOR\_4\_B\_SLVT

Channel

number

ch<0>, ch<24>

ch<1>, ch<25>

ch<2>, ch<26>

ch<3>, ch<27>

ch<4>, ch<28>

ch<5>, ch<29>

ch<6>, ch<30>

ch<7>, ch<31>

ch<8>, ch<32>

ch<9>, ch<33>

ch<10>, ch<34>

ch<11>, ch<35>

ch<12>, ch<36>

ch<13>, ch<37>

ch<14>, ch<38>

ch<15>, ch<39>

ch<16>, ch<40>

ch<17>, ch<41>

ch<18>, ch<42>

ch<19>, ch<43>

ch<20>, ch<44>

ch<21>, ch<45>

ch<22>, ch<46>

ch<23>, ch<47>

e.g. NAND2 Input A

e.g. NAND2

Input B

Post-layout (F)

[MHz]

195,5

286,6

241,6

292

128

148

139

183,1

122,3

149,2

152,6

169,5

136,2

174,2

134,2

198,7

146,3

173,8

167,7

182,4

168,1

182,6

187,4

200,8

SIMULATION

196,8

288,8

244,4

294,5

129,1

148,8

140,7

185,9

123,6

150,3

153,9

170,7

137,2

176,2

135,1

200,5

145,6

169,4

183,8

170,1

184,2

188,8

194,9

175

Post-layout (S)

[MHz]

| 23                     |

|------------------------|

| 20,                    |

| 4/                     |

| F/0                    |

| $\mathbf{Z}_{\vec{L}}$ |

TJ65nm Ring Oscillator

## Temperature tests

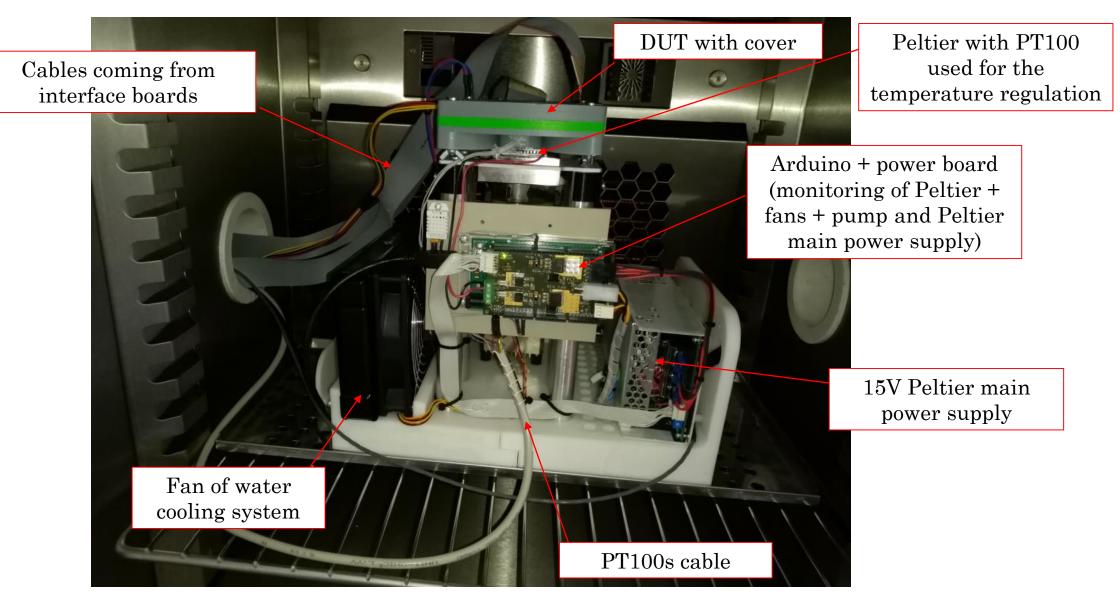

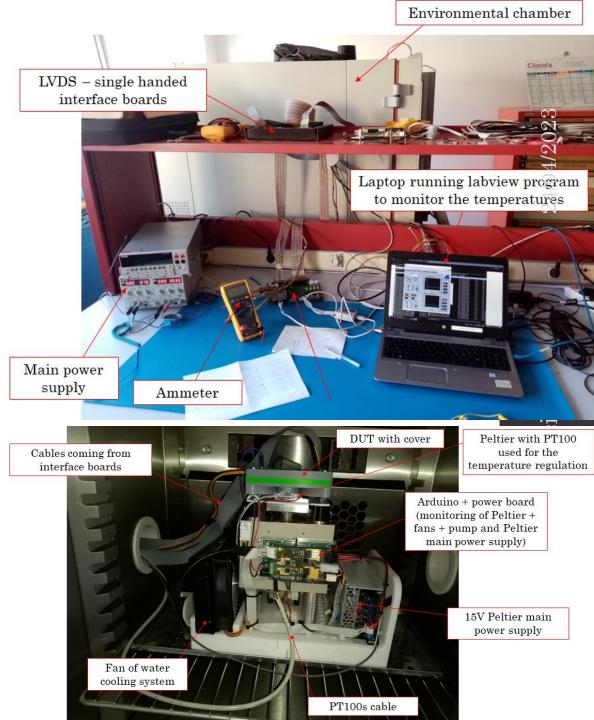

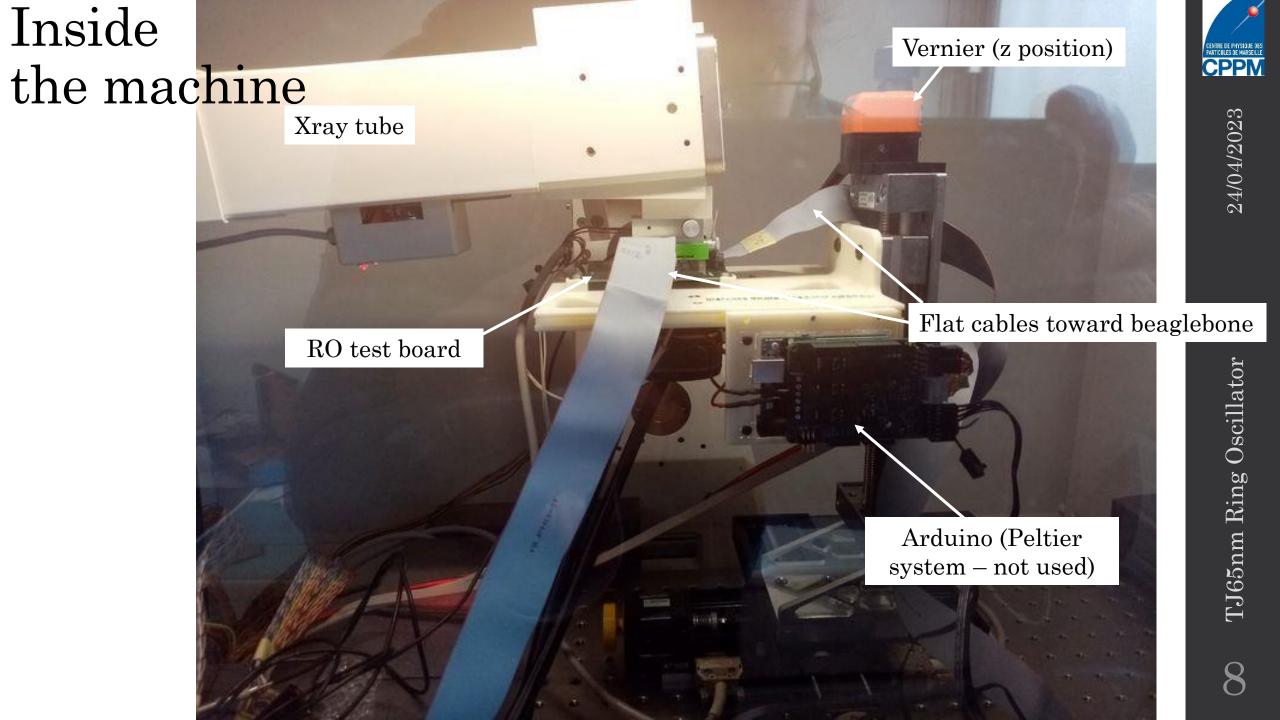

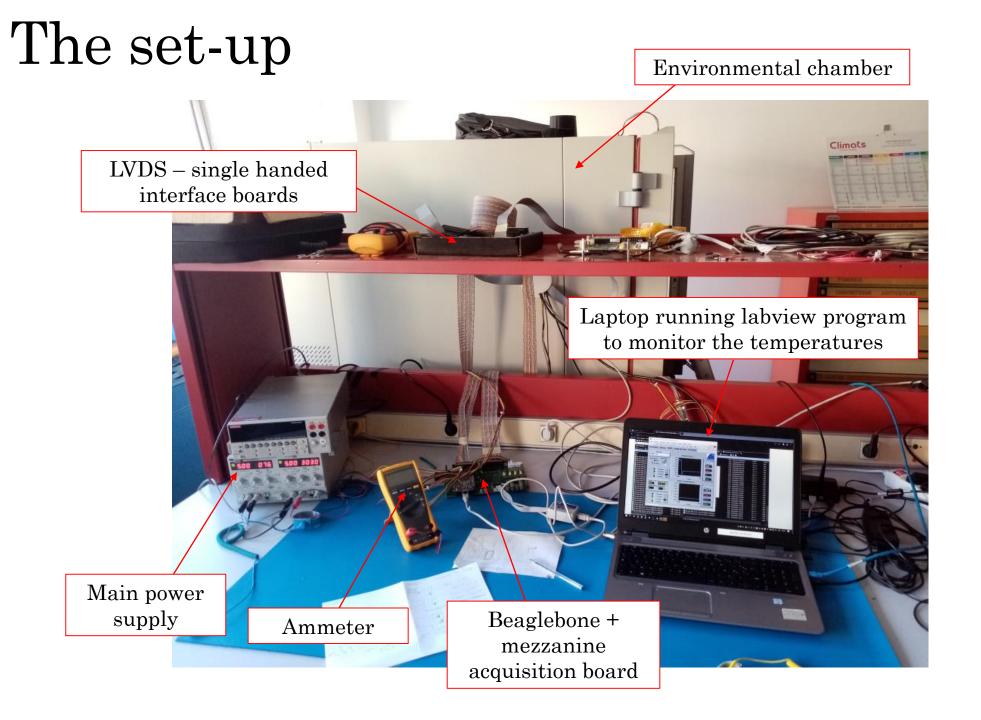

- The temperature tests were carried out with the characterization set-up (DUT board, beaglebone + mezzanine, interface boards) and an environmental chamber to regulate the temperature.

- In addition, inside the chamber a **Peltier system** was used to accurately set the temperature at the level of the circuit.

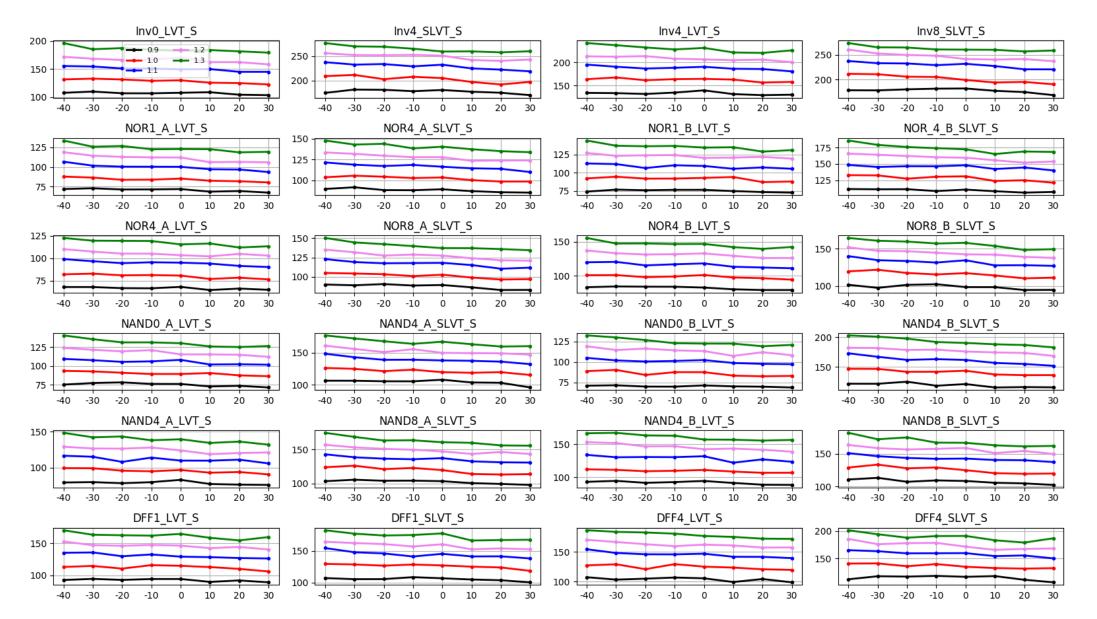

- Temperature regulated at 8 values: -40, -30, -20, -10, 0, 10, 20 and 30  $^{\circ}\mathrm{C}$

- At each temperature: 5 different values of the Vddd: 0.9, 1.0, 1.1, 1.2 (nominal) and 1.3V

- For each couple (Temperature, Vddd), 20 measurements were taken for each ring oscillator.

- Offline, the data were analyzed by computing the mean count for each RO and then calculating the mean frequency.

- Each RO exhibits a decrease of the frequency while the temperature increases (5-10 % over 70°C) whatever the Vddd or the bank.

# Separating RO: temperature effect BANKS

# Tests: irradiation & annealing

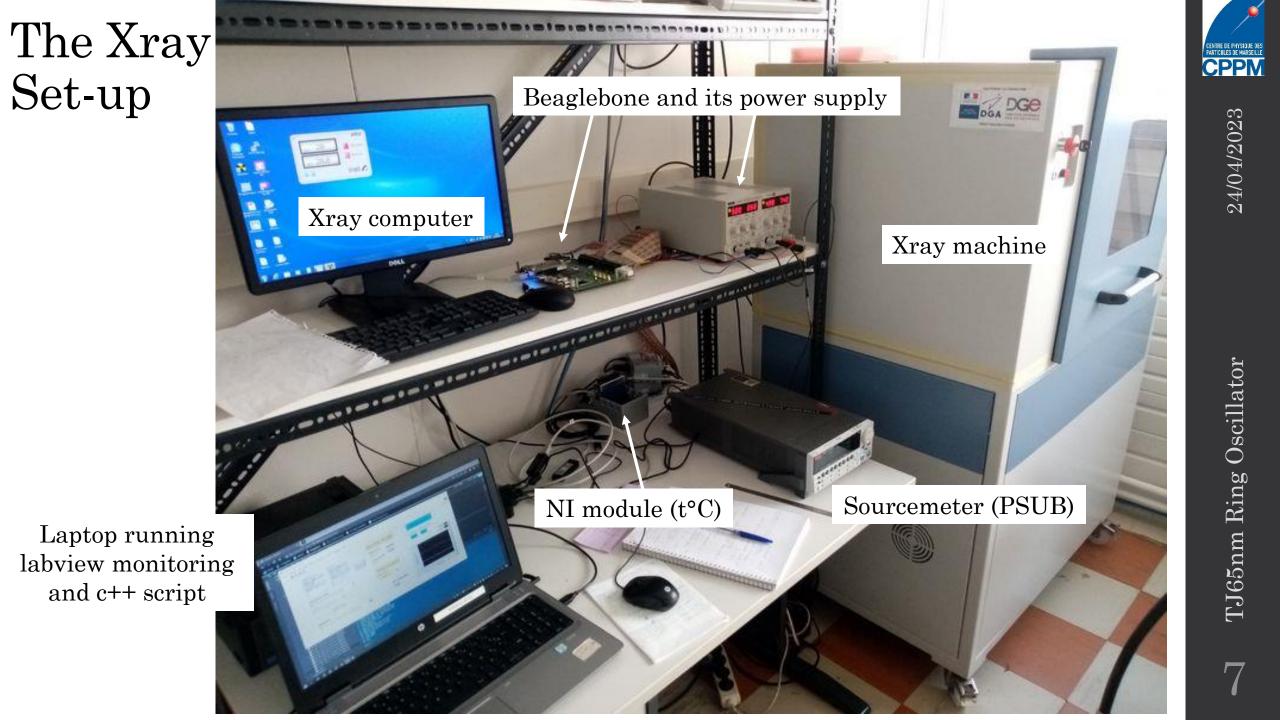

- Irradiation performed at ambient temperature with no regulation.

- Xray tube at 1 cm above the DUT (<u>dose rate: ~20 krad/mn</u>). Temperatures (pcb and ambient) monitored every minute.

- $\bullet$  During irradiation bank F oscillating and bank S no oscillating.

- Paused at specific TID

both banks oscillating and measurement of the 24 RO of each bank.

- 2 chips tested:

- <u>Chip1</u>: 4 weeks irradiation (830MRad) followed by annealing at -18°C (21 days), 25°C (25 days) and 80°C (9 days). It is important to that the functional bank of the chip1 was incorrectly configured during the irradiation and therefore was also kept static.

- <u>Chip2</u>: started irradiation 13/06/22. Chaotic because of Xray tube cooling system. Several technical stops correlated to the outside temperature.

20/06/22 : a mobile clim is installed and running (25°C regulation) in the room. Still we had interruptions (for some > 1 day). We stopped at 521 Mrad.

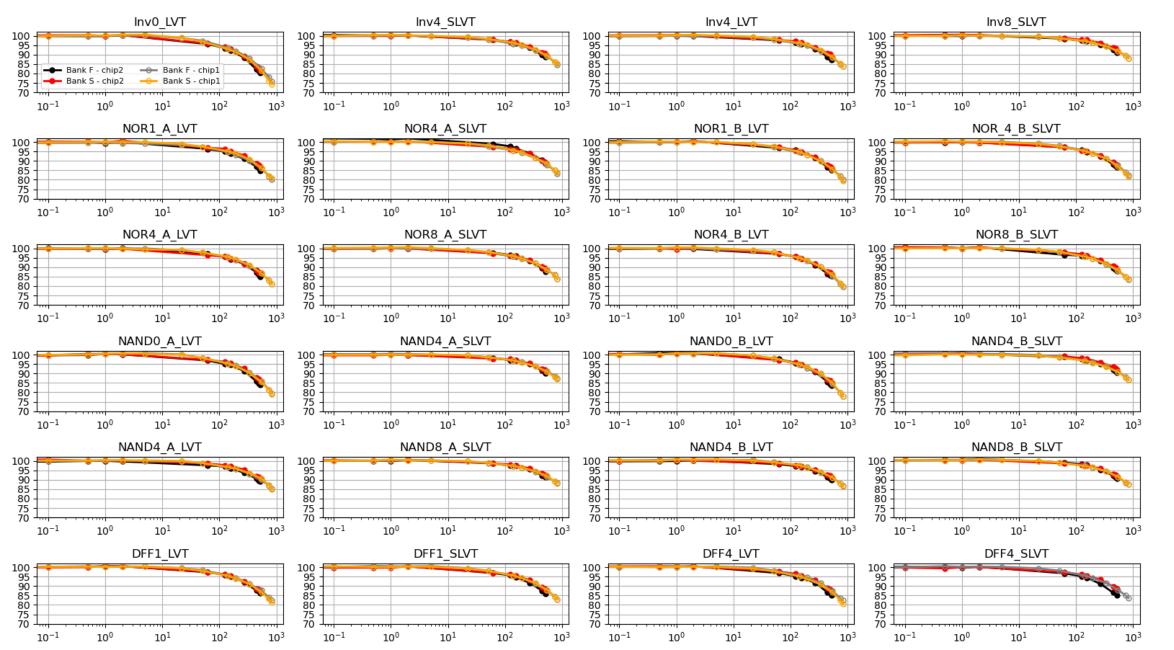

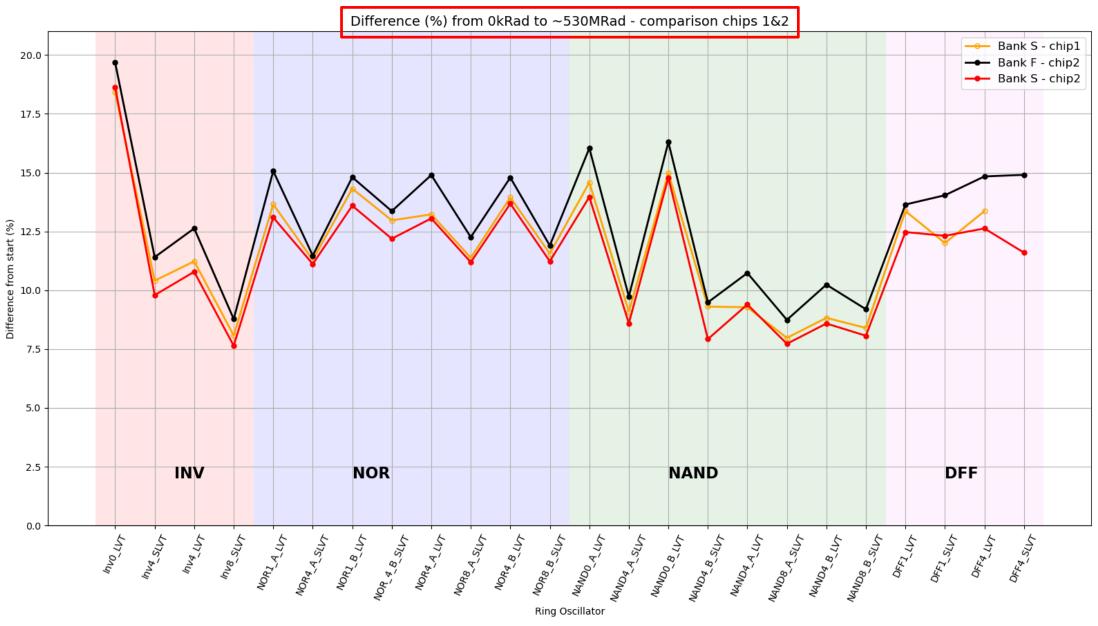

- Both chips responded similarly to the irradiation and exhibited a decrease (up to 25%) of the frequencies. We observed differences between ring oscillators, depending on the type, length, and threshold of the transistors of the base cells.

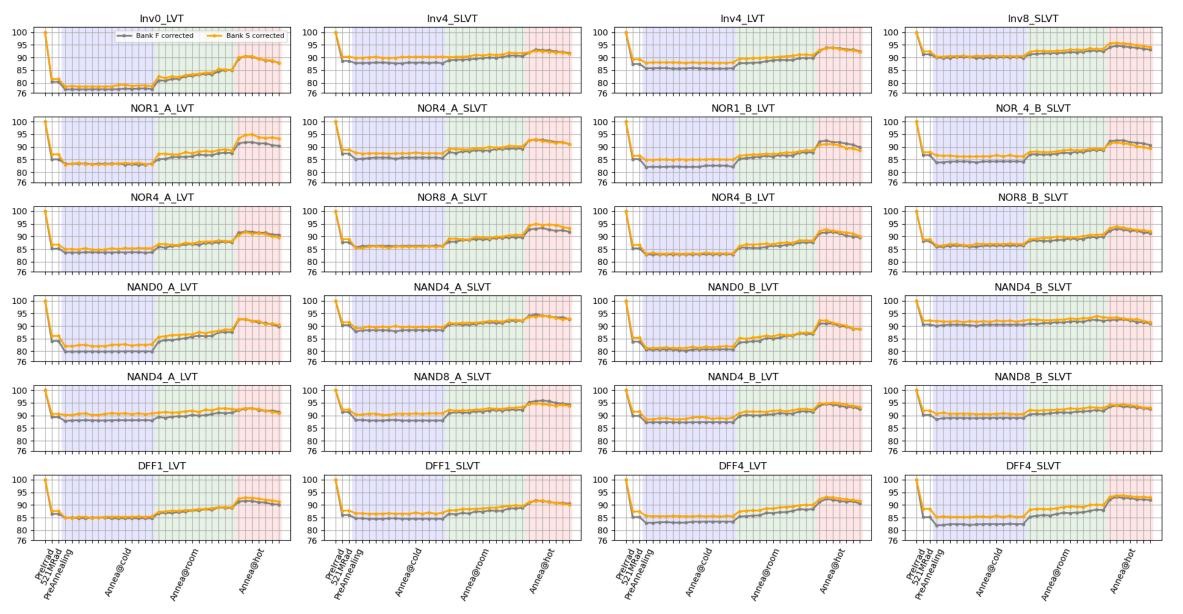

- <u>Annealing</u>: For all the ring oscillators, we observed no recovery at cold temperature (-20°C), a small recovery at room (25°C) and what looks to be a reverse annealing at warm temperature ( $80^{\circ}C$ ).

#### <u>Chip1 and chip2 relative frequency vs dose</u>

24/04/2023

CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE CPPM

#### **Chip1 and chip2 relative difference**

#### **Chip2 annealing with temperature correction**

CENTRE DE PHYSIQUE DES Particules de Marseille

24/04/2023

# Conclusions

- The temperature has an impact (decrease of the frequencies with increasing temperature) that can be quantified.

- Irradiation shows a decrease of the frequencies for all types of RO with a level different depending on the cell (from 12 to 25% at 830 Mrad).

- The size of the cells is an important parameter, the smaller cells (e.g Inv0) being more affected than the bigger ones (e.g Inv8).

- The difference between the two banks is not clearly visible while similar results were obtained for both chips tested.

- Annealing seemed dependent of the temperature with a better impact (recovery) at ambient (25°C).

- A poster has been presented at TWEPP 2022 and associated proceedings accepted early 2023.

- This limited degradation opens perspective for the usage of digital cells of this technology in high radiation environments.

- Resubmission with new ER  $\rightarrow$  to be tested summer 23.

Digital cells radiation hardness study of TPSCo

This project has received funding from the European Union's Horizon 2020 Research and Innovation programme under GA no 101004761.

### End

13

## The set-up inside the chamber

15