# Production of a demonstrator for the Silicon Electron Multiplier concept

Victor Coco (CERN), Marius Mahlum Halvorsen (CERN, UiO), Ivan Lopez Paz (IMB-CNM), Giulio Pellegrini (IMB-CNM), Gemma Rius (IMB-CNM)

2<sup>nd</sup> AIDAinnova conference, 25<sup>th</sup> April 2023

www.imb-cnm.csic.es

# **Motivation**

- New HEP accelerator applications require increasing radiation hardness

(cumulative dose per year)

- From  $5 \times 10^{15} n_{eq}$ /cm<sup>2</sup> in ATLAS IBL lifetime to  $10^{17} n_{eq}$ /cm<sup>2</sup> in FCC-hh **per year**

- Inner trackers start requiring excellent time resolution

- High pile-up requires finer granularity

from the CERN Strategic R&D Programme on Technologies for Future Experiments [CERN-OPEN-2018-006]

| [fineprint in CERN-OPEN-2018-006]                | HL-LHC             | SPS   | FCC-ee           | FCC-hh |

|--------------------------------------------------|--------------------|-------|------------------|--------|

| Fluence [n <sub>eq</sub> /cm²/y]                 | 5x10 <sup>16</sup> | 1017  | 10 <sup>10</sup> | 1017   |

| Max Hit rate [cm <sup>-2</sup> s <sup>-1</sup> ] | 2-4G               | 8G    | 20M              | 20G    |

| Material budget per layer [X <sub>0</sub> ]      | 0.1-2%             | 2%    | 0.3%             | 1%     |

| Pixel size [µm²]<br>inner trackers               | 50x50              | 50x50 | 25x25            | 25x25  |

| Temporal hit resolution [ps]                     | ~50                | ~40   | -                | ~10    |

Challenge: pixelated detector with resolutions of down to 10 ps, able to survive high fluences

# **Motivation**

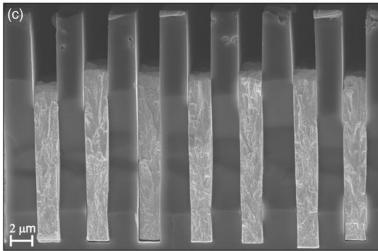

- Monolithic sensors:

- **PRO:** resolution (spatial & temporal), material budget

- **CONS:** radiation hardness, data rate (but could be bonded to CMOS), temporal resolution

- 3D sensors :

- PRO: radiation hardness, temporal resolution, spatial resolution

- **CONS:** spatial resolution, fill factor, capacitance

- LGAD familly:

- **PRO:** temporal resolution

- **CONS:** radiation hardness, spatial resolution (could be solved by AC-LGAD, Ti-LGAD or iLGAD

- Internal gain without radiation damage sensitivity?

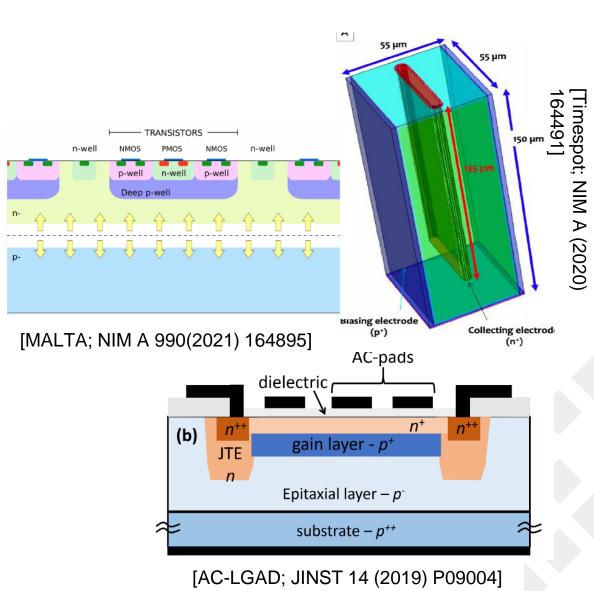

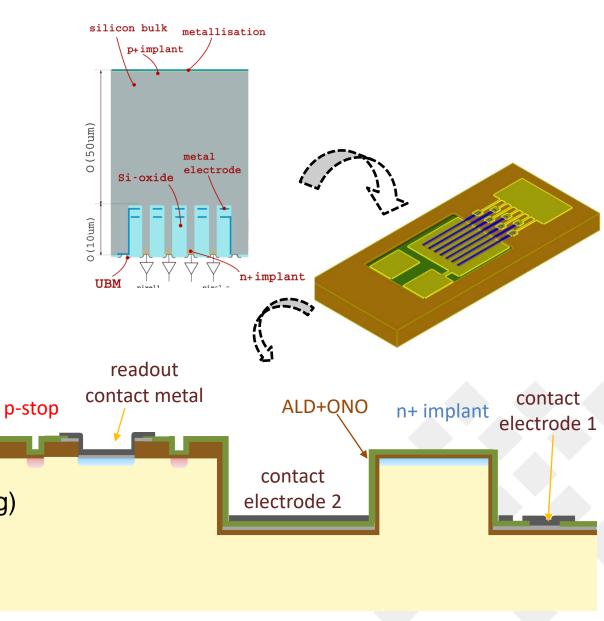

### **The Silicon Electron Multiplier concept**

- Instead of relying on high doping concentration for charge multiplication (LGAD), adapt the geometry of the device for high fields

- Multiplication mechanism not compromised by acceptor removal  $\frac{1}{O}$

- Electrons generated by ionisation in the bulk, multiplied in amplification region (high field from electrodes 1&2)

- After charge multiplication, charge carriers induce signal on the readout electrodes

- Individual readout pillar width: ~2-4 um

- Possibility of small pitch/pixel size

Potential for small pixel size, multiplication not affected by radiation and 100% fill factor

$\rightarrow$  Promising for future colliders

oxide in between pillar

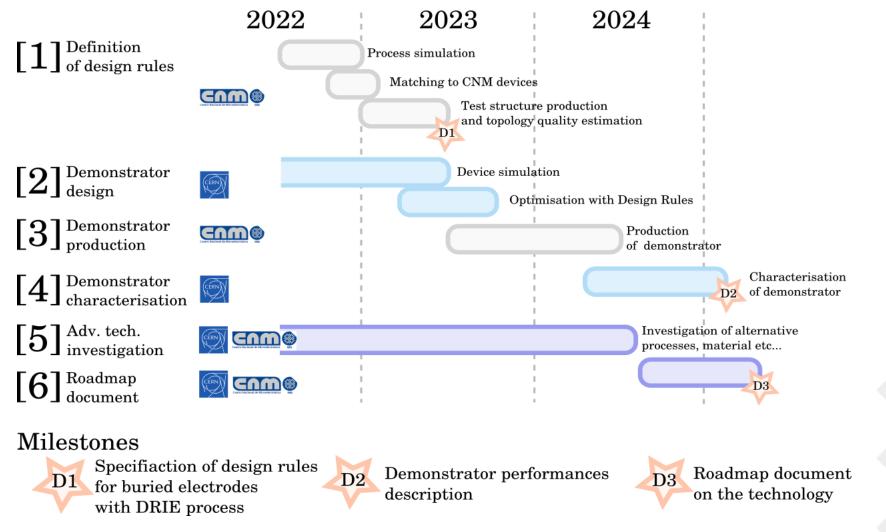

#### **Planning towards demonstrator**

#### Team

#### • CERN

- Victor Coco [coordination]

- Marius M. Halvorsen [PhD] until Oct 2023

- Federico De Benedetti [PhD] to start ~Feb 2023 [25% AIDAinnova]

- Vagelis Gkougkousis until Feb 2023 Edgar Cid Lemos fellow to joined in 2023 [support]

#### • CNM

- Giulio Pellegrini [coordination]

- Ivan Lopez Paz [postdoc] started in July for 2 years 100% AIDAinnova

- Gemma Rius [researcher]

- + technical and executive support from the Clean Room staff (DRIE expert etc...)

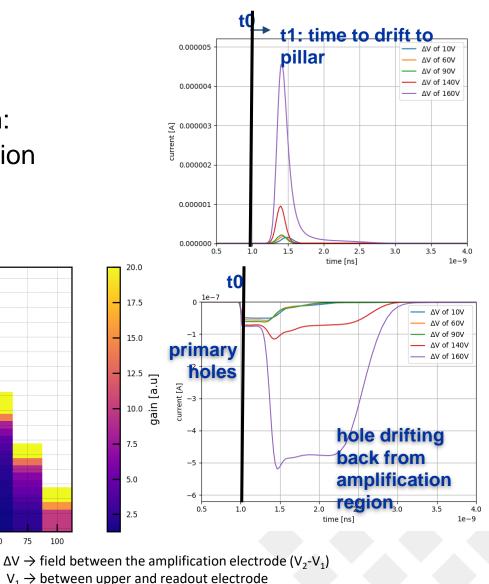

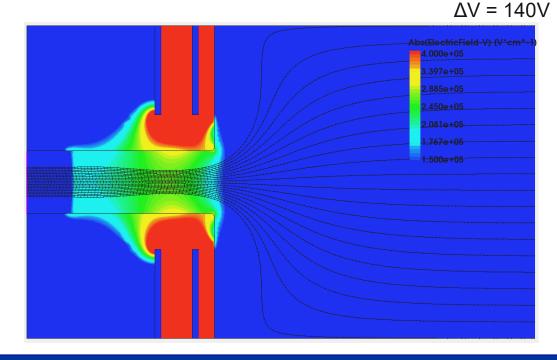

# Simulation

#### NIM A 1041 [2022] 167325

∑ 130 ∑ 120 ∑ 110

V1 [V]

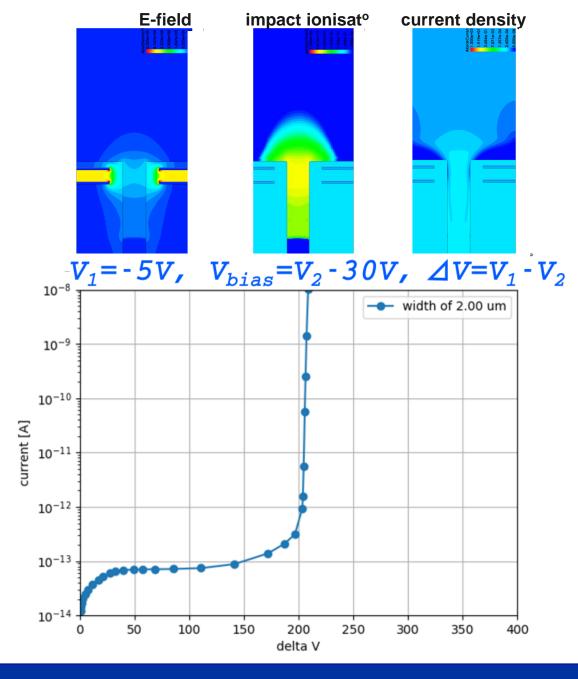

- Simulation demonstrates charge multiplication mechanism:

- Carriers multiplication when electrons reach amplification region

- Gains of up to x20 observed in simulation study (depending on geometry and applied bias)

Carrier multiplication to be verified in hardware

V<sub>bias</sub> = -30 V (depleted bulk) → Physical realisation: Production of demonstrator device

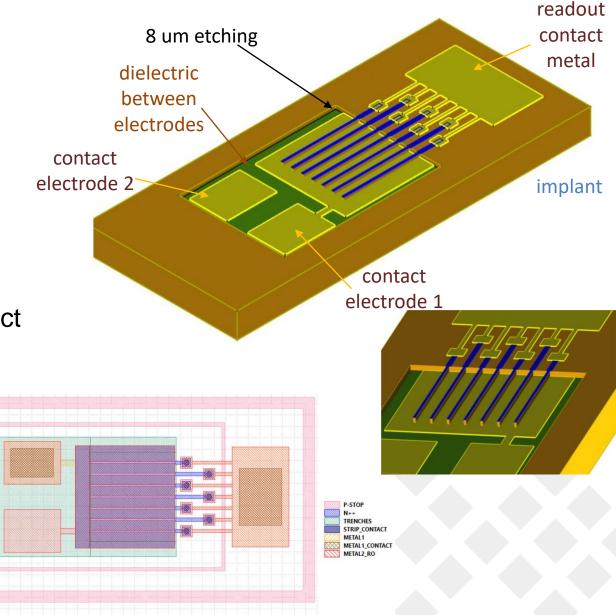

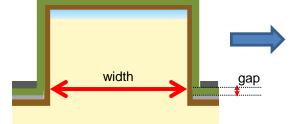

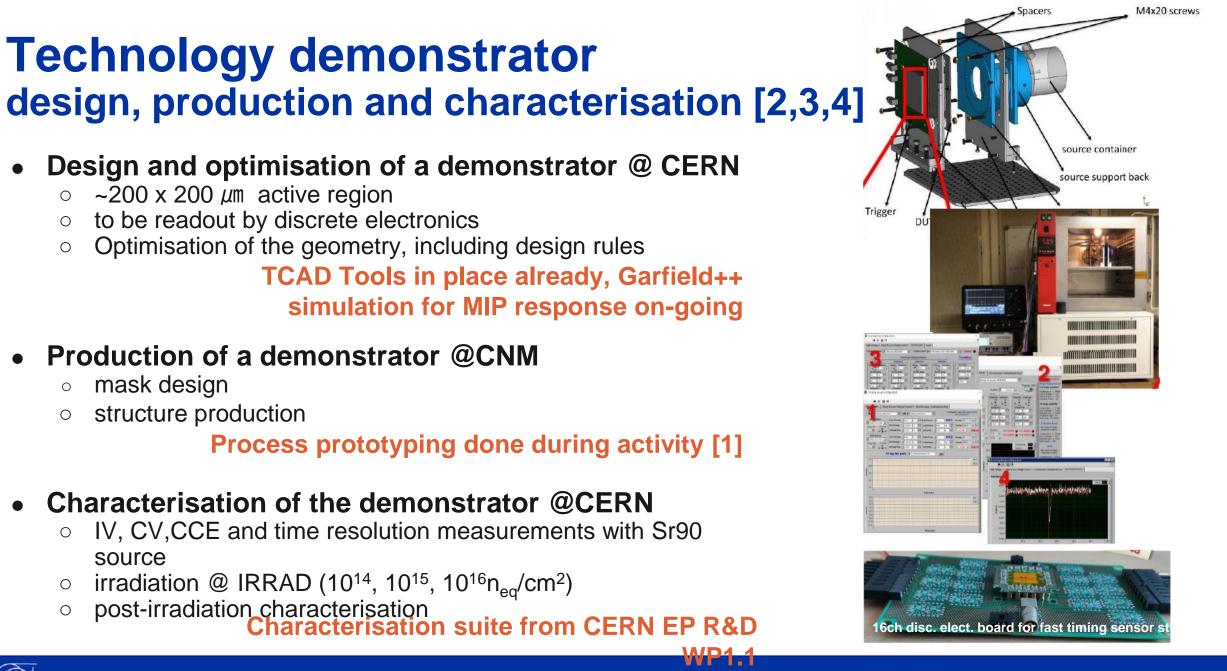

#### **Demonstrator layout design**

Matching simulation dimensions

- Pillar widths: 2, 3 and 4 um

- Inter-electrode dielectric thickness: 1 um

Strip design for proof-of-concept: demonstrate amplification mechanism

- Interconnected strips, shorted to readout contact

- Allow for wirebonding for testing

- 2 amplification electrodes

Opening on back side for TCT tests

# **Design and processing definition**

- Trenches

- laser photolithography → trenches

- Si etching depth ~8um

- Electrode 1 deposition

- surface treatment

- ALD 50nm oxide, metal deposition, ALD 50nm oxide

- Oxide deposition O(um)

- Electrode 2 deposition

Challenges:

- Oxide layer can induce stress ⇒ limit the gap between electrodes 1 and 2

- Etching limited in width depending on patterning process used:

- laser photolithography down to 2um (design/layout fliexibility, good for prototyping)

- electron beam lithography (adjustment needed)

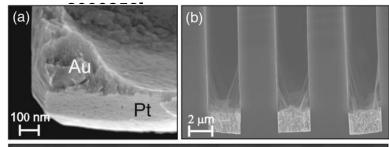

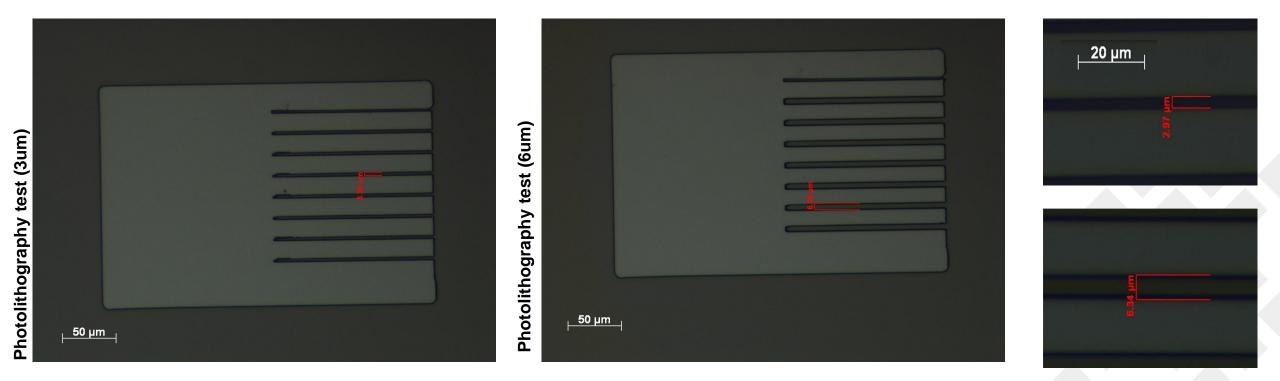

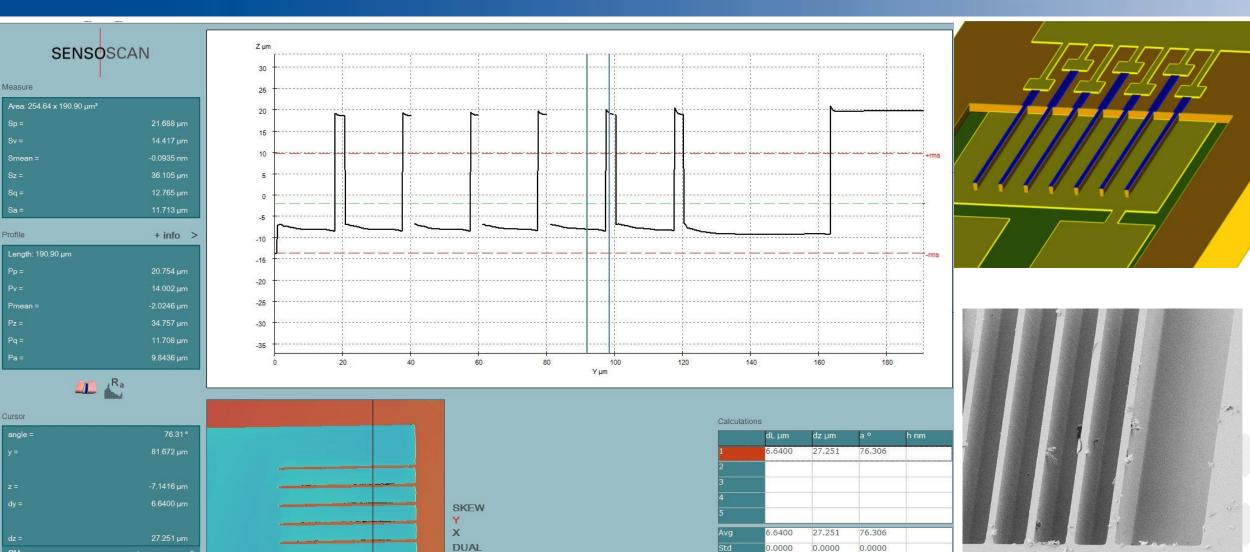

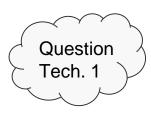

# **Photolithography tests**

#### • Pillar diameter / width test

- test with 3 and 6um wide trenches OK

- optimisation of exposition and development parameters

- $\circ~$  probably possible to go to 2um

- $\Rightarrow$  limited by the laser resolution

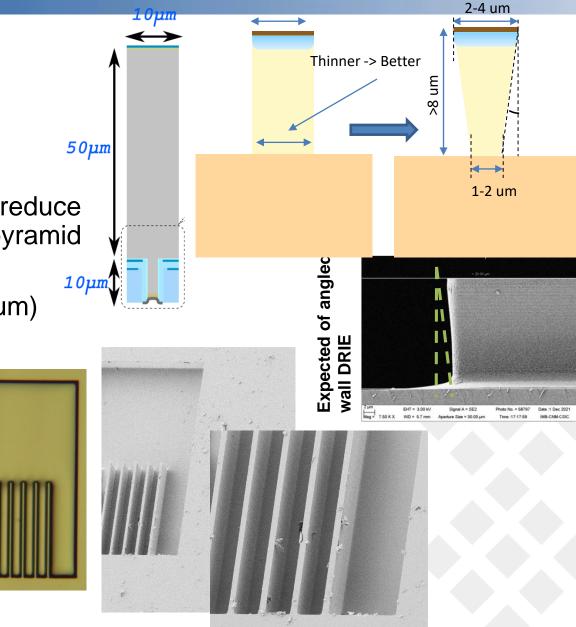

# **Etching tests**

- Thinner pillar width -> More charge multiplication

- Currently limited by lithography

- Trying to reduce distance across pillar base to reduce distance between electrode sides -> Inverted pyramid profile

- Over-etching in the first batch (25 um instead of 8 um)

- Adjust recipe

# **Next steps**

- Metallisation and oxide deposition tests (~1-2 months)

- Production (~end-of-year)

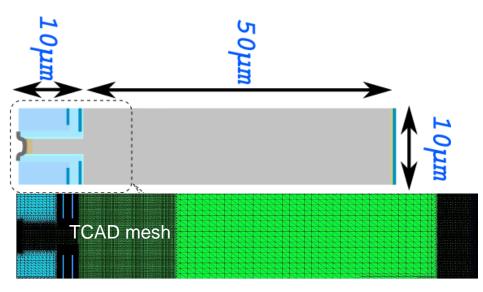

# **Device simulation**

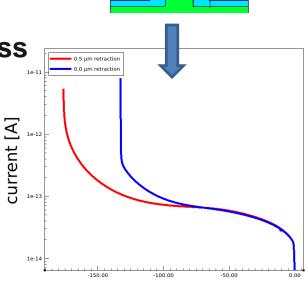

• Geometry adapted to the real production process

#### • Specific geometrical constraints

- width of the amplification pillar

- gap between amplification electrodes

- distance between pillar and electrodes

- Study with TCAD simulation of geometry compatible with process

s with different

Ž

Simulated

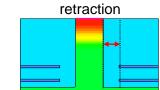

electrode retraction

- IV used to check if amplification happens before breakdown (checked with transient sim.)

- best for low width and high gap

- width limited by lithography and gap limited by oxide deposition

- retraction of the electrode from the pillar still allow amplification

backside potential [V]

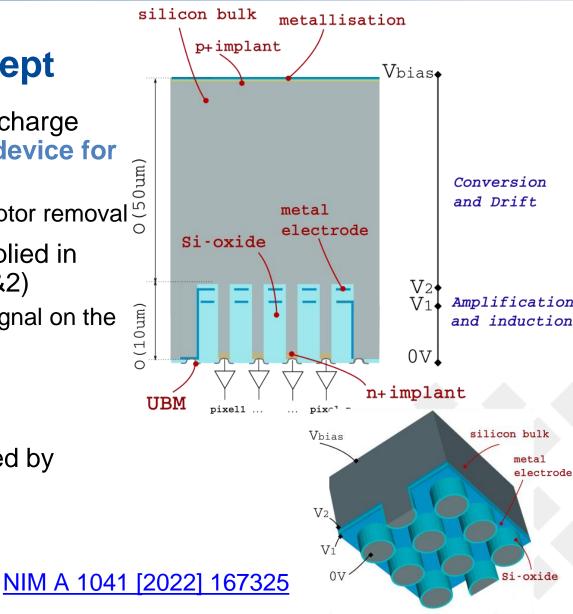

# **Alternative approach to SiEM**

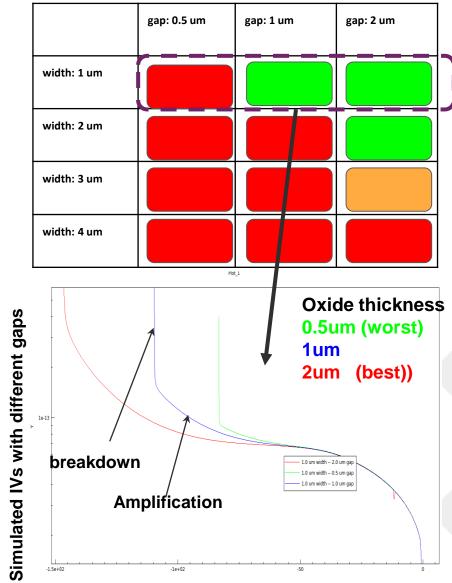

#### • Study possible use of Metal assisted etching

- parallel project between CERN and PSI, based on AdEM 22 (2020) 2000258

- very different process constraints (cheap, high aspect ratio, first electrode deposited while etching), but never used in active device

bias voltage [V]

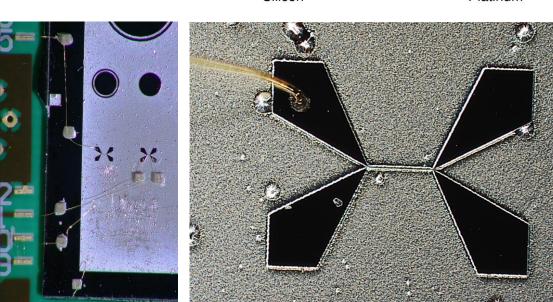

#### • Testing the structures

IV measured under SEM after prod.

Single pillar

Strip

- $\circ$  IV just after production with probe-station  $\Rightarrow$  pn junction conserved

- bonding of test structures for IV in the lab

- preparing setup for laser/ source test.

#### see M. Halvorsen @ RD50 41st workshop

Strip structure bonded for testing

bilicon Platinum

#### **Summary and outlook**

- Electron Multiplier concept on Silicon Radiation allows charge multiplication not relying on high doping implantation

- Mechanism depends on geometry only -> not sensitive of acceptor removal

- First processing tests being performed for the fabrication of demonstrator

- RIE, laser lithography, oxide and metallisation

- Exploring inverse pyramid profile to reduce pillar width (to overcome the limit on pillar width, limiting charge multiplication according to simulation)

- Simulation being updated to match CNM processes

- Inter-electrode gap and pillar width, different dielectrics, etc

- Alternatives approaches to the SiEM geometry being studied by means of metal-assisted etching

# Back-up

CLEAR

EXPORT

System Ready

#### Electric Field and leakage current

- The bulk can be depleted

- low leakage current

- High field region can be achieved

- between 200 and 300kV/cm

- field in dielectric < 3MV/cm</li>

# CERN

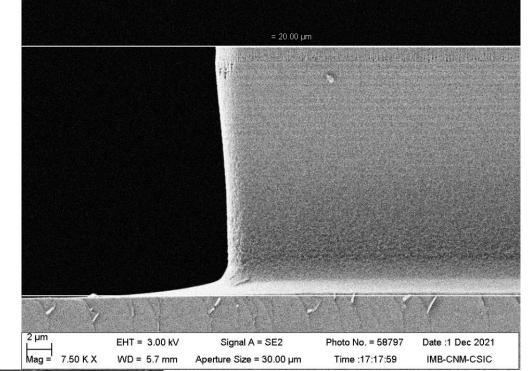

# **Design rule determination** Activity [1] @ CNM

#### • Structures with various:

- $\circ$  pillar width (1-5µm)

- o inter-pillar distances (2 to 5x pillar width)

- o depth (6-10µm)

- $\circ$  guard between elect. and pillar (0.25 to 1µm)

- inter-electrode distances

- various DRIE parameters

- Process simulation

- Tuning to CNM device parameters

- Production of the structures

- Characterisation of the topologies

1µm pillar OK but large structure of 1µm pillar will require dedicated dev. (beyond this project)

Ο

Ο

Ο

Ο

Ο

Ο

$\cap$

# **Technology investigation** and roadmap document [5,6]

- Different sensor geometry

- single electrode

- stack of electrodes

#### • Different bulk material (SiC, Diamond,...)

higher radiation hardness, lower charges fr Question Tech. 6

Question

Tech. 3

$\circ$  could be compensated by achieving gain  $\diagdown$

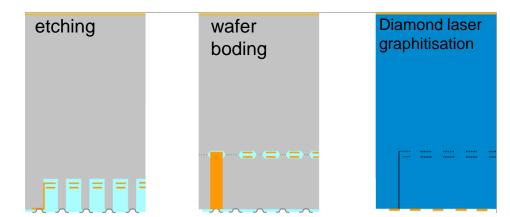

#### • Different process

- MacEtch: less production ready but simple and different contraints (parallel project with PSI)

- Wafer bonding: more complex but different constraints

- Hardware implementation are beyond the R&D steps scope of this project and other applications

#### [L. Romano et al; AdEM 22 (2020)