Advancement and Innovation for Detectors at Accelerators

## Subtask 8.4.2:

# Development of highly granular dual-readout fibre-sampling calorimeter

Romualdo Santoro

Università dell'Insubria and INFN-MI

On behalf of the IDEA Dual-Readout calorimeter collaboration

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 101004761.

### 8.4.2 – Objectives

- Development of highly-granular dual-readout fibre-sampling calorimeters

- The beneficiaries: INFN Italy (PV, MI, PI, BO, CT and RM1), Sussex Univ. (UK) and CAEN

- **Collaborators external to the program**: Kyungpook National University (Korea), Korea University (Korea) and Iowa State University (US)

The dual-readout fibre-sampling technique offers a way to overcome one of the limiting factors in hadron calorimetry, by cancelling, event by event, the effects of the electromagnetic fraction fluctuations in hadronic showers, and, with SiPM read-out, provides high granularity and excellent angular resolution. The production and mechanical assembly of the detector elements, the readout of  $O(10^8)$  channels with an optimised scalable system, and the possibility to discriminate photon and electron showers from hadrons by time measurements will be investigated. The readout system will be developed in collaboration with CAEN in order to equip several  $10 \times 10$  cm<sup>2</sup>, 2 m long, prototypes to be qualified with test beams.

| Milestone<br>number <sup>18</sup>        | Milestone title                                                                                          | Lead beneficiary |                                                                                       | 1      | Due<br>Date (in<br>months) Means of verification |                   | Report available here:    |              |                                           |                    |                                      |                                          |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------|--------|--------------------------------------------------|-------------------|---------------------------|--------------|-------------------------------------------|--------------------|--------------------------------------|------------------------------------------|

| MS35                                     | Definition of the assembly<br>method and of the ASIC<br>specifications for a dual<br>readout calorimeter | 22 - INFN        | - INFN                                                                                |        | 23                                               | Report (Task 8.4) |                           |              | https://aidainnova.web.cern.ch/milestones |                    |                                      |                                          |

|                                          |                                                                                                          |                  | Deliverable<br>Number <sup>14</sup>                                                   | Delive | erable Ti                                        | tle               | WP<br>number <sup>9</sup> | Lead be      | neficiary                                 | Type <sup>15</sup> | Dissemination<br>level <sup>16</sup> | Due<br>Date (in<br>months) <sup>17</sup> |

| Now, fully committed to the demonstrator |                                                                                                          | D8.4             | Construction and<br>qualification with beam<br>of 10×10 cm^2, 2 m<br>long, prototypes |        | WP8                                              | 22 - INF          | N                         | Demonstrator | Public                                    | 46                 |                                      |                                          |

- Summary of the results reported in the Milestone M35

- Progress report on the activities on going to build the hadronic size demonstrator

## Summary from the 2021 Test beam

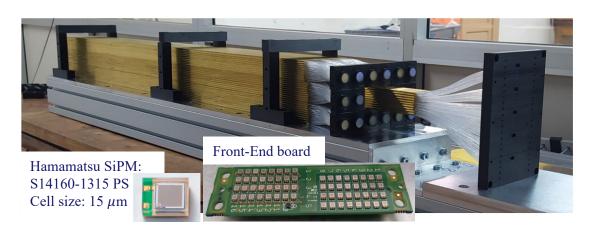

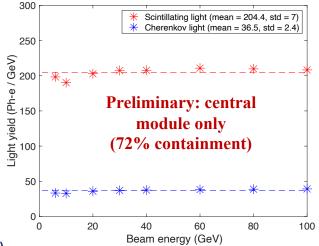

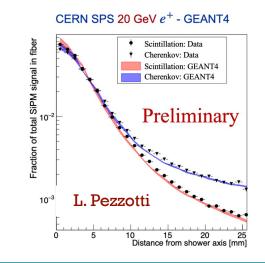

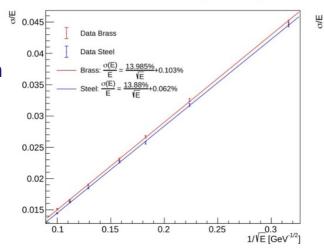

- A EM-size prototype has been tested on beam in 2021 (@DESY and @CERN) with electrons from 1 to 100 GeV

- The prototype was made of brass capillary tubes (2 mm outer diameter) each hosting a fibre of 1 mm diameter: (10x10x100 cm<sup>3</sup>)

- There are 9 towers containing 16x20 capillaries with alternating scintillating and clear fibres

- The central tower is equipped with SiPMs while the surrounding towers are connected to PMTs (cost-saving reason)

<u>Calor2022 – DOI: 10.3390/instruments6040059</u>

A performance paper is almost ready for the submission

## Design of a scalable solution

Challenging task requiring:

- Precise assembly procedure

- Compact components: almost no space in the rear part of the calorimeter

- Sensors

- Mechanical support

- Services

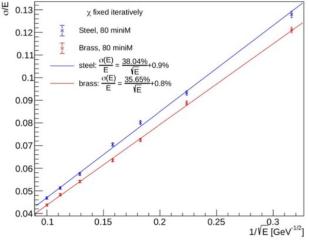

### Pion resolution in [10, 100] GeV Range

- The scalable design is a compromise between integration constrains, costs and performance tuned with a Geant4 simulation

- Baseline: steel tubes, 2mm diameter, 2.5 m long

Electron resolution in [10, 100] GeV Range

### SiPM - requirements

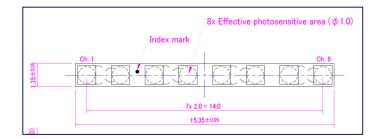

- Compact package (almost no dead area)

- Large dynamic range: •

- Cherenkov (scintillating) light is expected to produce  $\approx$  5 p.e./GeV ( $\approx$  28 p.e./GeV) in the SiPMs closest to the • shower axis

- Different options considered for Cherenkov and scintillating light to operate SiPMs in linear regime (occupancy less than 25 – 30 %)

### Compact package

**Options considered for the**

|                                     | 2021 prototype | hadronic-size  | e prototype    |

|-------------------------------------|----------------|----------------|----------------|

| Parameter                           | S14160-1315PS  | S16676-15(ES1) | S16676-10(ES1) |

| Effective photosensitive area (mm2) | 1.3 x 1.3      | 1 x 1          | 1 x 1          |

| Pixel pitch (mu)                    | 15             | 15             | 10             |

| Number of pixels                    | 7284           | 3443           | 7772           |

| Recommended operating voltage (Vop) | +4 V           | +4 V           | +5 V           |

| PDE at the Vop (%)                  | 32             | 32             | 18             |

| Direct cross talk at the Vop (%)    | <1             | <1             | <1             |

| Dark count rate (kHz)               | 120 (360 max)  | 60 (200 max)   | 60 (200 max)   |

| Gain (10 <sup>5</sup> )             | 3.6            | 3.6            | 1.8            |

Used for the

### ASIC – requirements

| Main specifications                                                         |                                                              |  |  |  |

|-----------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| Readout strategy                                                            | Charge integration                                           |  |  |  |

| Number of channels                                                          | 32 / 64                                                      |  |  |  |

| Sensitivity                                                                 | 0.5 p.e. (@ 2 * 10 <sup>5</sup> SiPM gain)                   |  |  |  |

| Dynamic Range                                                               | 0 – 320 pC (i.e. 10000 p.e. @ 2 * 10 <sup>5</sup> SiPM Gain) |  |  |  |

| Timing resolution                                                           | < 50 ps rms (single p.e.)                                    |  |  |  |

| Power consumption                                                           | < 500 mW                                                     |  |  |  |

| Full frame readout                                                          | Internal / external trigger (one of the two or both)         |  |  |  |

| Additional features                                                         |                                                              |  |  |  |

| Single channel HV adjustment                                                |                                                              |  |  |  |

| Single channel gain tuning                                                  |                                                              |  |  |  |

| Single channel threshold setting (required for timing and internal trigger) |                                                              |  |  |  |

| Trigger mask (required for internal trigger)                                |                                                              |  |  |  |

| Signal latency (≈100 ns)                                                    |                                                              |  |  |  |

| Internal TDC (optional)                                                     |                                                              |  |  |  |

|                                                                             |                                                              |  |  |  |

## Charge integration plus timing information

### ASIC – requirements

| Main specifications                                                         |                                                              |  |  |  |

|-----------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| Readout strategy                                                            | Charge integration                                           |  |  |  |

| Number of channels                                                          | 32 / 64                                                      |  |  |  |

| Sensitivity                                                                 | 0.5 p.e. (@ 2 * 10 <sup>5</sup> SiPM gain)                   |  |  |  |

| Dynamic Range                                                               | 0 – 320 pC (i.e. 10000 p.e. @ 2 * 10 <sup>5</sup> SiPM Gain) |  |  |  |

| Timing resolution                                                           | < 50 ps rms (single p.e.)                                    |  |  |  |

| Power consumption                                                           | < 500 mW                                                     |  |  |  |

| Full frame readout                                                          | Internal / external trigger (one of the two or both)         |  |  |  |

| Additional features                                                         |                                                              |  |  |  |

| Single channel HV adjustment                                                |                                                              |  |  |  |

| Single channel gain tuning                                                  |                                                              |  |  |  |

| Single channel threshold setting (required for timing and internal trigger) |                                                              |  |  |  |

| Trigger mask (required for internal trigger)                                |                                                              |  |  |  |

| Signal latency (≈100 ns)                                                    |                                                              |  |  |  |

| Internal TDC (optional)                                                     |                                                              |  |  |  |

## Charge integration plus timing information

| Main specifications      |                                                      |  |  |

|--------------------------|------------------------------------------------------|--|--|

| Readout strategy         | Waveform sampling                                    |  |  |

| Number of channels       | 32 / 64                                              |  |  |

| Sampling frequency (GHz) | 5 - 10                                               |  |  |

| Input Bandwidth (GHz)    | >1                                                   |  |  |

| Buffer length (samples)  | > 4k                                                 |  |  |

| Feature extraction       | i.e. total charge, ToA, ToT, current-peak time       |  |  |

| Full frame readout       | Internal / external trigger (one of the two or both) |  |  |

Waveform sampling plus feature extraction

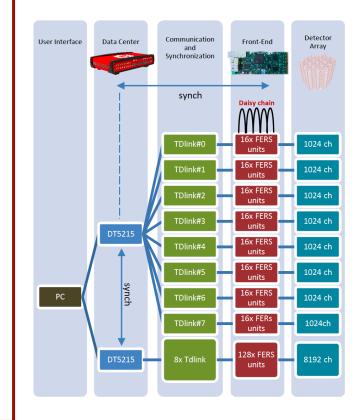

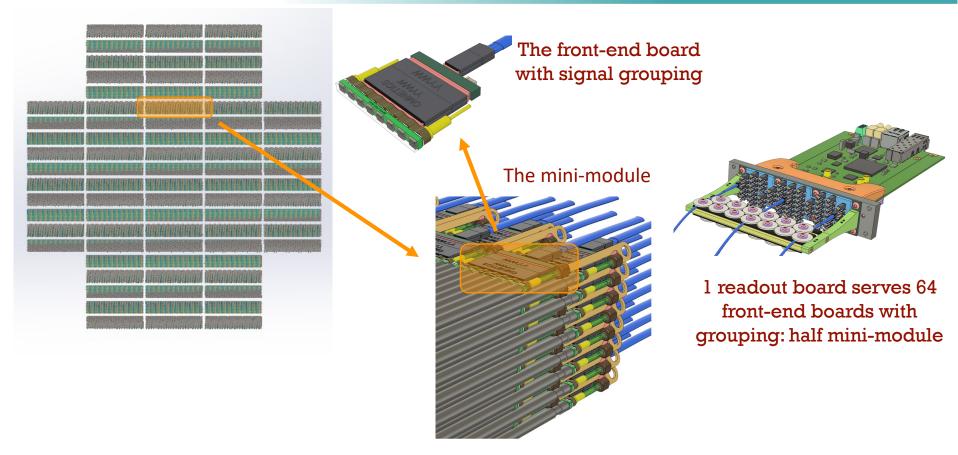

## Scalable readout system

• The Caen FERS system (5200) is our baseline, compliant with the Citiroc1A and the Radioroc (hopefully soon). Alternatives will be also considered

- Two Citiroc1A for reading out up to 64 SiPMs

- One (20 85V) HV power supply with temperature compensation

- Two 12-bit ADCs to measure the charge in all channels

- Timing measured with 64 TDCs implemented on FPGA (LSB = 500 ps)

- 2 High resolution TDCs (LSB = 50 ps)

- Optical link interface for readout (6.25 Gbit/s)

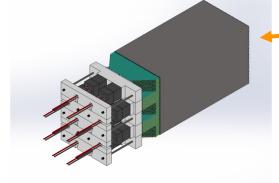

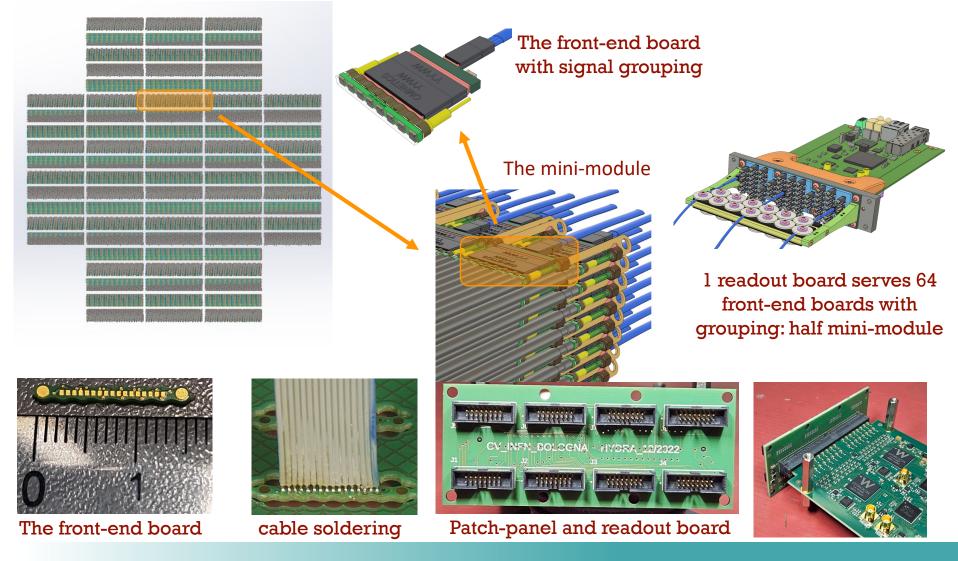

The Mini-Module

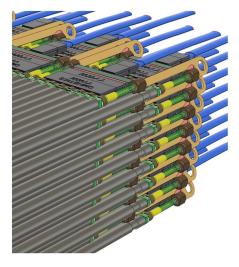

## Prototype with hadronic containment: HiDRa

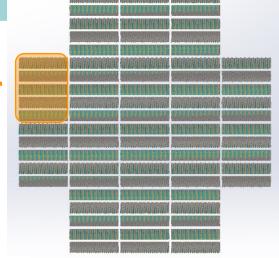

HiDRa INFN-funded R&D project HiDRa INFN-funded R&D project The Module 5 Mini-modules \* 13 x 13 x 250 cm<sup>3</sup> HiDRa INFN-funded R&D project • The highly granular modules • 16 modules in total • 2 central modules • quipped with SiPMs • 14 modules equipped with PMTs • ~ 65 x 65 x 250 cm<sup>3</sup>

### The hadronic prototype

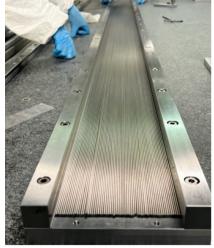

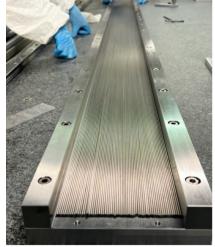

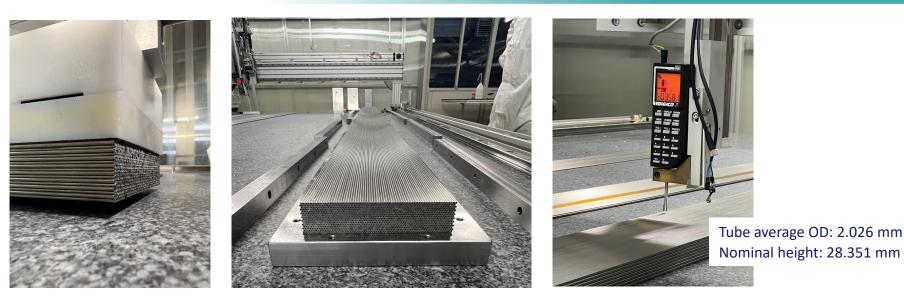

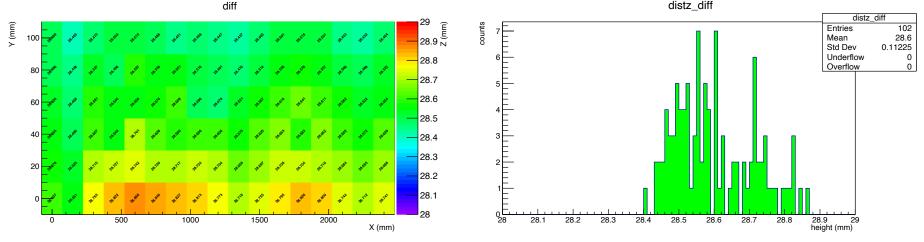

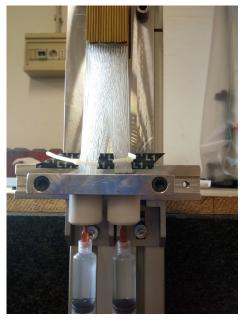

### Construction technique for the mini-module

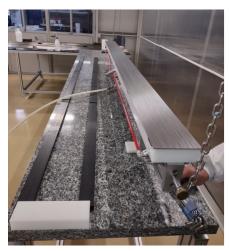

Assembly reference structure anchored to the granite table with the 1<sup>st</sup> layer of tubes in place

Vacuum + double-sided tape for tube handling

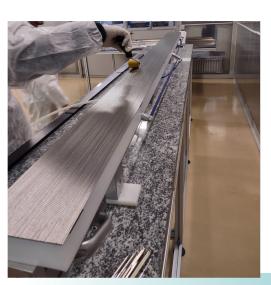

## Construction technique for the mini-module

Assembly reference structure anchored to the granite table with the 1<sup>st</sup> layer of tubes in place

Vacuum + double-sided tape for tube handling

Glue dispensing and tube alignment and positioning

R. Santoro

### **Construction technique for** the mini-module

## Photodetector integration: PMTs

### The Module = 5 mini-modules

Each minimodule is readout with 2 PMTs (one for Cherenkov and one for scintillation)

Fibre and PMT holder built with 3D-printing technique

### Fibre grouping and PMT coupling

Left: R11265U series, Right: H11934 series

Hamamatsu PMT:

- R8900 (out of stock)

- R11265U-200

- R11265-203 (extended UV photodetection efficiency Cherenkov light)

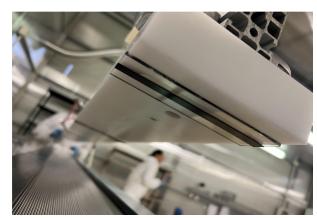

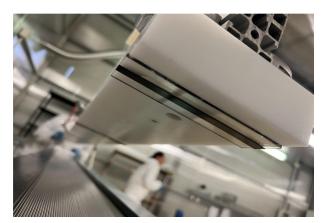

## Preparation for fibre loading

### Fibre gluing technique

## Photodetector integration: highly granular module

## Photodetector integration: highly granular module

### What next?

- The Milestone 35 has been submitted (<u>https://aidainnova.web.cern.ch/milestones</u>)

- Definition of assembly method and ASIC specifications

- A performance paper summarising the 2021 TB data is almost ready. It covers:

- Calibration, Linearity, EM energy resolution and Data-Geant4 comparison

- A test beam is planned at CERN this year with the EM-size prototype. We will focus on

- Increased statistic at high energy

- Additional studies on the energy resolution dependence on the angle of the impinging particles

- The first mini-module has been assembled and the mechanical precision is within specification. The material procurement to build the Had-size prototype is started (i.e. tubes, fibres, PMTs)

- The photodetector integration with the highly granular module still needs to be finalised

- The first batch of SiPMs with front-end board will be qualified soon

- Integration test with dummy components is needed to freeze out the design

- Simulation studies are progressing to further constrain the specifications or to add new requirements (i.e. new features to better exploit ML techniques and PFA)