**Overview of the ATLAS High-Granularity Timing Detector:** project status and results Yassine El Ghazali<sup>1</sup> On behalf of the ATLAS HGTD Group

**FLEX tail**

<sup>1</sup>Faculté des Sciences, Université Ibn-Tofail, Kénitra

### **High-Luminosity LHC**

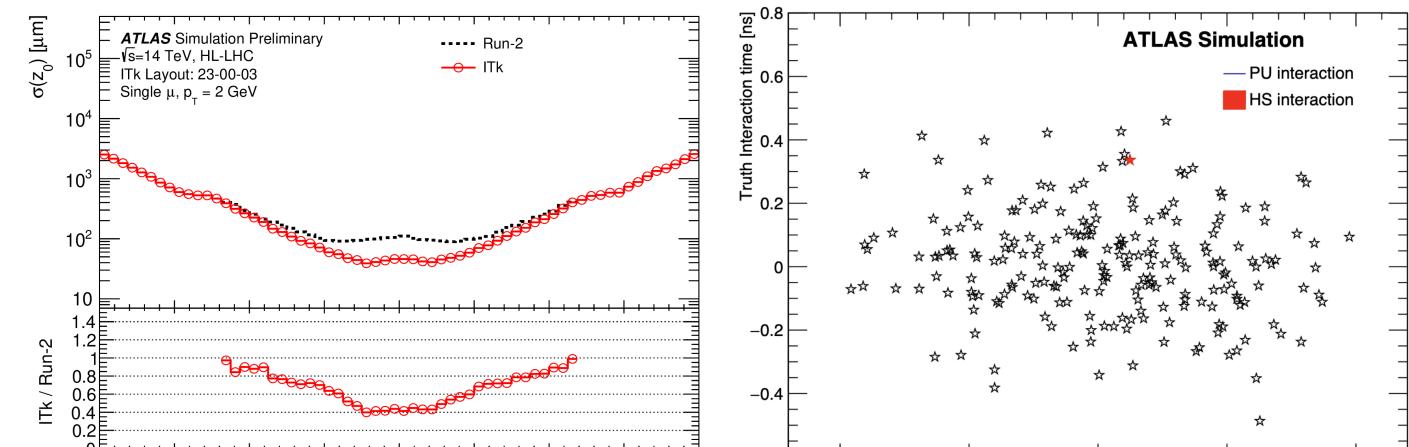

• High-Luminosity LHC will deliver an instantaneous luminosity of up to  $L \approx 7.5 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1}$ • Very harsh environment with **200** pile-up events (*p*-*p* interactions on same bunch crossing) • ATLAS will install a full-silicon Inner Tracker (ITk) to maintain its physics performance

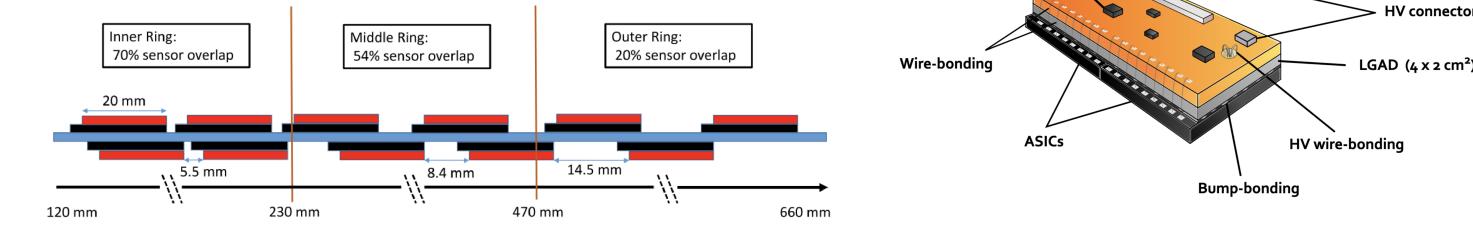

#### **Detector module**

Module FLE

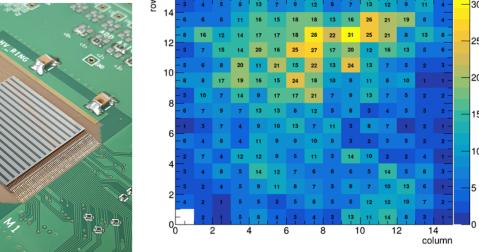

- **HGTD module** consists of 2 LGAD sensors + 2 ALTIROC ASICs bump-bonded and glued to a module flex

- HGTD will have 8032 modules  $\implies$  3.6 M channels

- Modules mounted on cooling plate, connected to the surrounding Peripheral Electronics Boards via FLEX cables

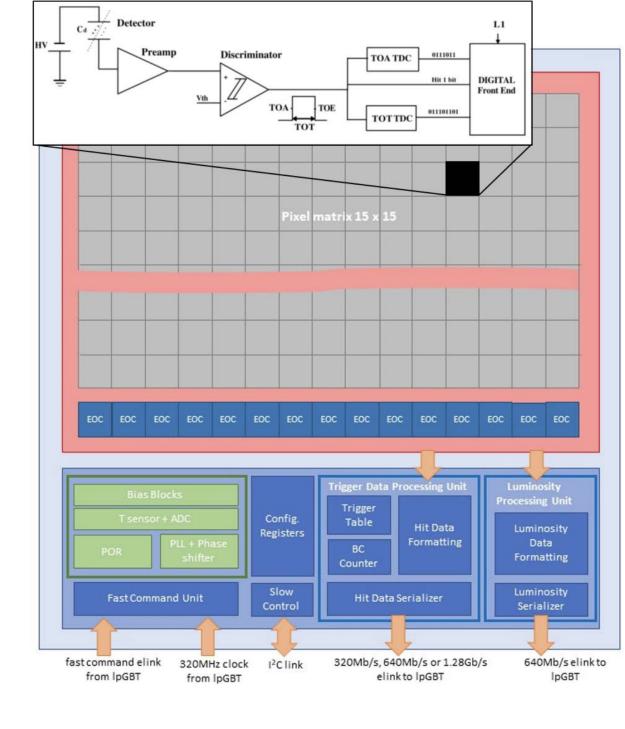

### **ATLAS LGAD Timing Integrated Readout Chip (ALTIROC)**

Provides time-of-arrival (TOA) + time-over-threshold

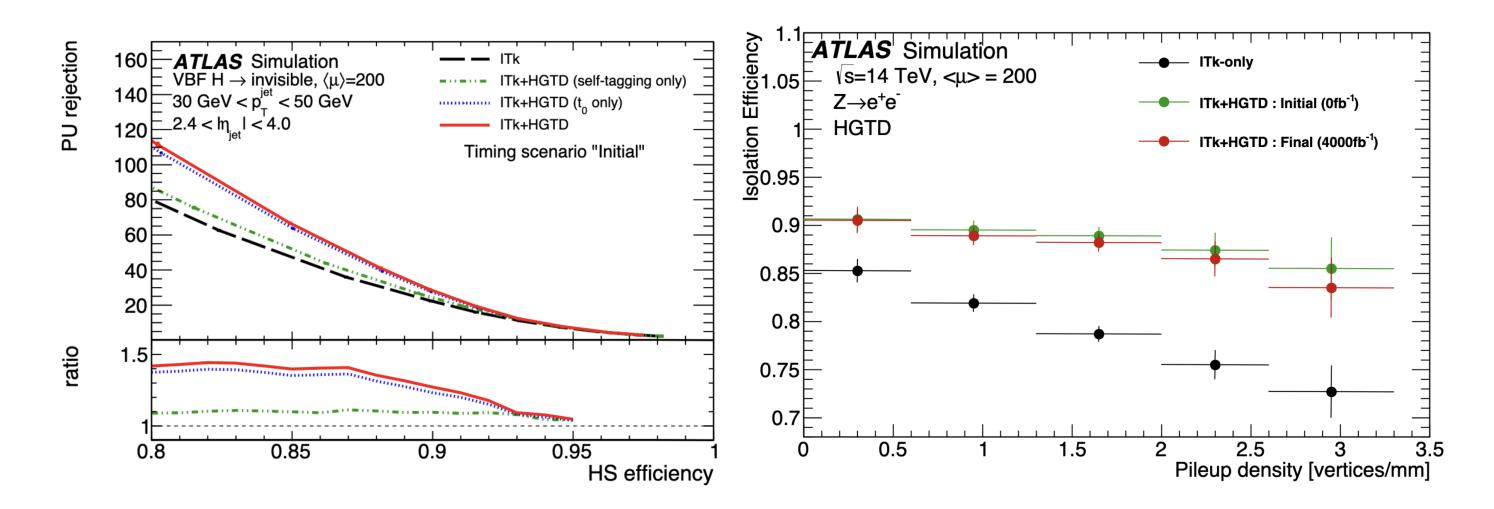

• ITk does great job, but in the forward region  $z_0$  resolution worsens and becomes larger than distance between two vertices  $\implies$  Timing information allows to separate these vertices

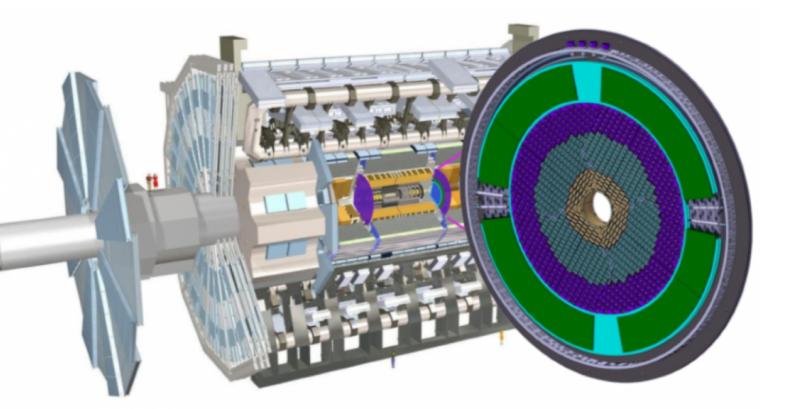

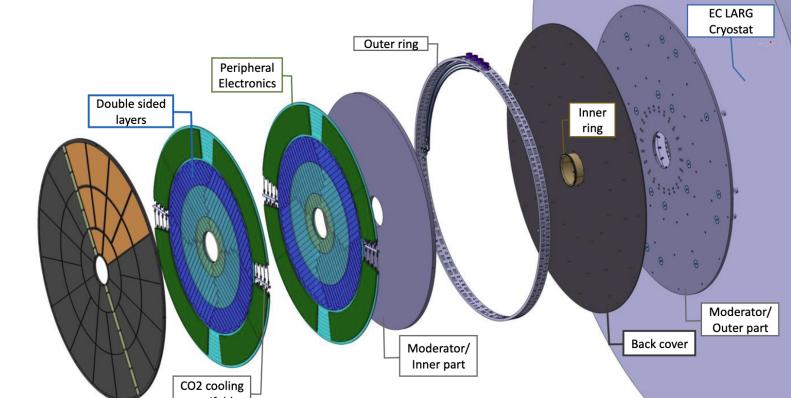

### High Granularity Timing Detector (HGTD)

- HGTD will be installed in the forward region of ATLAS

- $2.4 < |\eta| < 4$  Resolution per track 30-50 ps

- $\pm 3.5$  m from IP Resolution per hit 35-70 ps

- 12 < R < 64 cm Radiation hard:  $2.5 \times 10^{15}$  n<sub>eq</sub>/cm<sup>2</sup>

- 3 ring layout

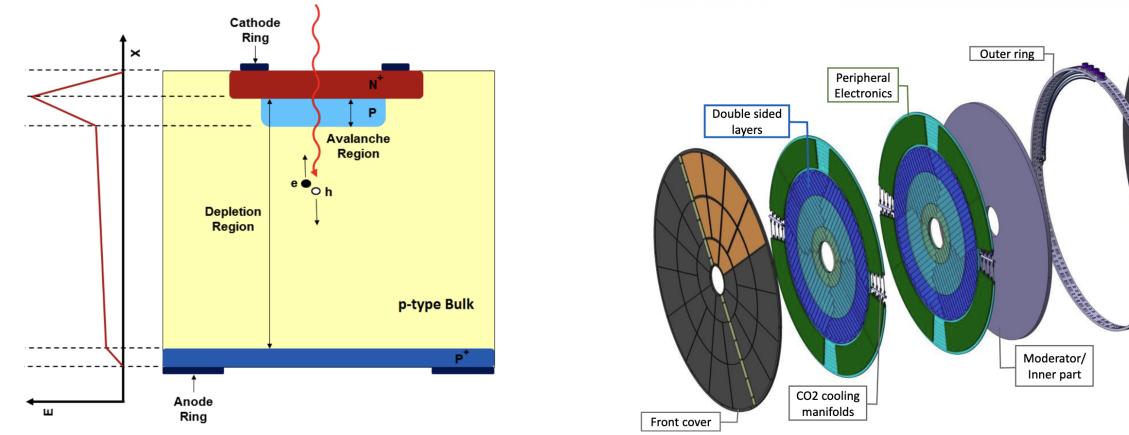

- Sensor technology: Low Gain Avalanche Detectors (LGADs)

- n-p planar silicon diodes with additional p-type doped layer

- Moderate gain **10-20** compared to APD and SiPM

- Thin ( 50  $\mu$ m): radiation hardness and faster rise time

- LGAD pad size  $1.3 \times 1.3 \text{ mm}^2$  (low occupancy)

- (TOT) data per channel

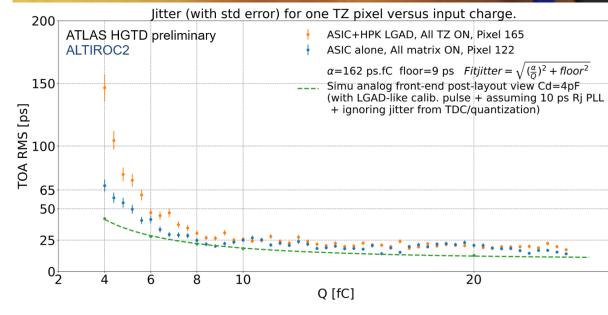

- Radiation hard + Jitter < 25 ps @ 10 fC/ < 65 ps @ 4 fC

- Integrated temperature measurement + calibration between LHC fills to maintain resolution @ system level

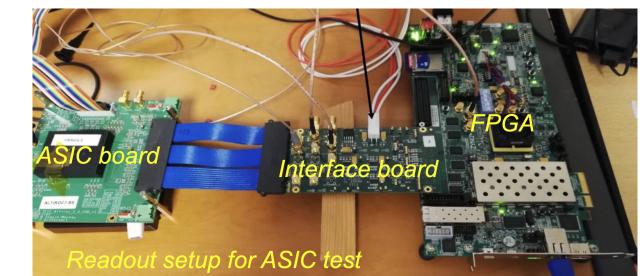

- Assess the performance of ALTIROC2 using dedicated PCB and interface board

**Physics prospects**

- Pile-up rejection and maintained as the ring will be replaced every 1000 fb $^{-1}$

- Improvements on lepton isolation  $\implies W$  mass precision measurements

- b-tagging performance enhancement by rejecting pileup tracks

HGTD will act as a luminometer  $\implies$  luminosity uncertainties reduction which would benefit most of the precision measurement analyses

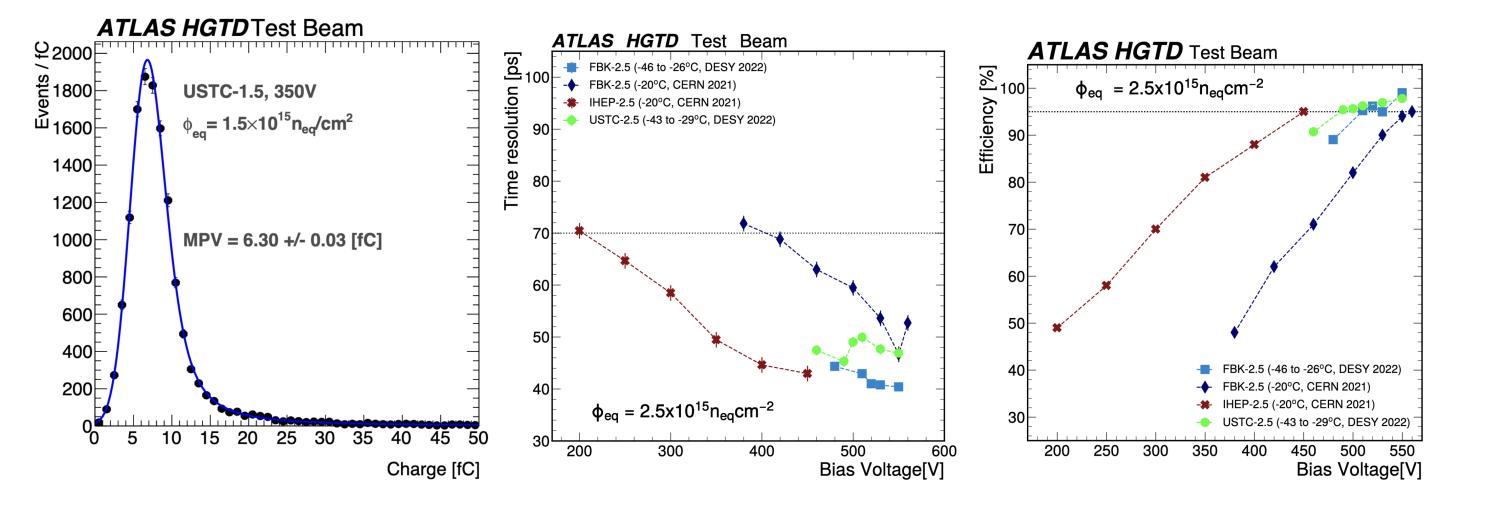

## **Sensor performances**

Several beam tests performed at DESY and CERN to assess the performance of sensors focusing on carbon-enriched LGADs

• **Time resolution**: measured with a time

DUTs

D3 D2 D1

downstream triplet

M1

upstream triplet

Beam

- Test a hybrid prototype (Sensor + ALTIROC)

- Use test pulses to ensure the functionality

- Tests with Sr90 source to validate bump-bonding connectivity

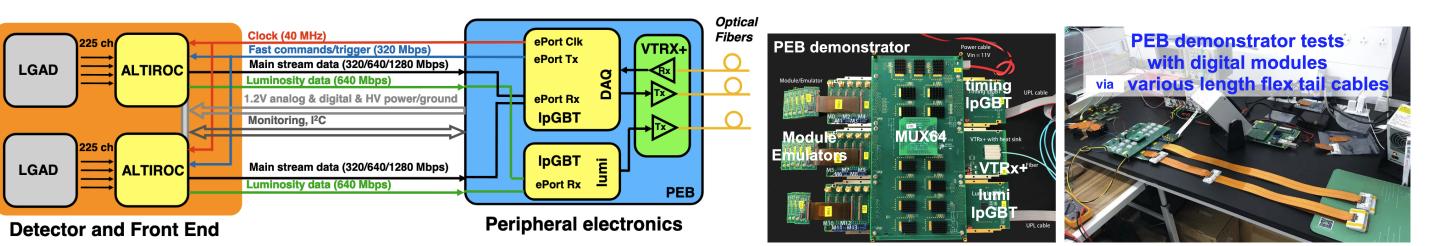

# Peripheral Electronic Board (PEB)

- 48 PEBs located outside the active area (frontand back-side of the disks), connected via pigtails to outer-ring

- Radiation hard components: IpGBTs, DC-DC converters, VTRX+

- DC-DC converter bPOL12V in depth investigated regarding space constraints, power efficiency

- Communication through IpGBTs with FELIX card

- Successfully dumped digital module data through FELIX

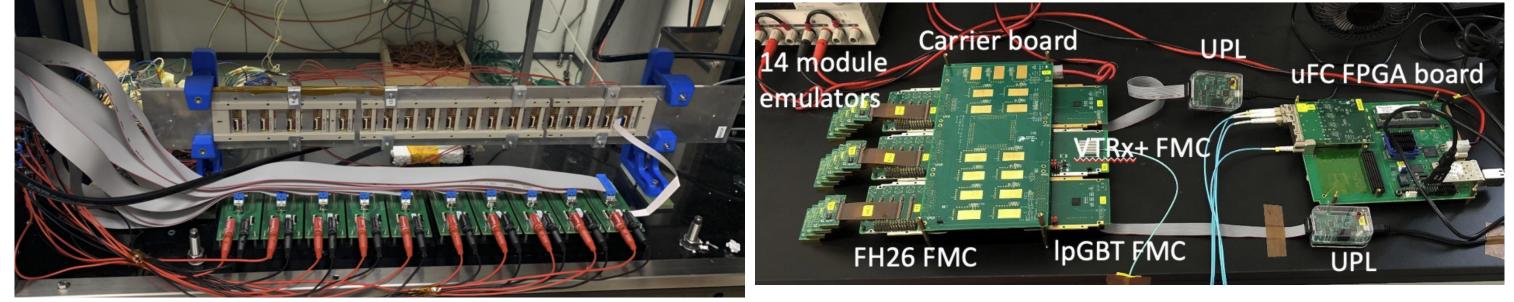

## **Demonstrator**

Several demonstrator prototypes are being built to test different components of the system

#### Heater demonstrator

- Stave with 19 silicon heaters

- Mounted on a cooling plate to verify CO<sub>2</sub> cooling capabilities as well as identify best thermal media between modules and cooling plate

#### DAQ Modular PEB demonstrator

• Up to 14 modules with two lpGBTs and one VTRx+

yassine.el.ghazali@cern.ch

- Timing and luminosity data reach the required benchmark bandwidth

- Digital module

- reference device  $\sigma_{i,j} = \sigma_i \oplus \sigma_j < 50$  ps (well below requirement < 70 ps)

- **Collected charge**: Maintain a minimum of 4 fC needed by ASIC

- Efficiency: > 95% for track with charge > 2 fC

Ongoing preparation for full demonstrator with 55 full HGTD modules connected to prototype PEBs

### Conclusion

- HGTD will significantly improve the physics performance in the forward region of ATLAS

- Significant progress has been made on LGAD sensors, readout chips and modules

- Exciting time ahead in the near future as HGTD is moving towards construction

### References

[2] 2023 JINST 18 P05005 [1] CERN-LHCC-2020-007, ATLAS-TDR-031

#### Yassine El Ghazali

The 11th annual Large Hadron Collider Physics conference, Belgrade, 22–26 May 2023