**CERN**

# Future Monolithic Pixel Detectors in ALICE and beyond

Francesca Carnesecchi

On behalf of the ALICE collaboration

25<sup>th</sup> May 2023, Belgrade The 11th annual Large Hadron Collider Physics conference

**LHCP 2023**

### ALICE **CMOS MAPS – a short introduction**

**Qualitative timeline...**

Early 2001 1969 Today **1990s** Digital imaging  $\rightarrow$  with the invention of the Charge-Coupled Device (CCD). → Start of the the digital imaging revolution HARGED PARTICLE Emergence of **C**omplementary machine vision, human recognition and

- most widespread implementation of image sensors, advantage  $\rightarrow$  price

- CMOS Imaging Sensor (CIS) capacity is extending to 28-22nm

#### Big steps for charge particles detection

Nobel Prize in Physics in 2009 Willard S. Boyle and George E. Smith "for the invention of an imaging semiconductor circuit - the CCD sensor"

Metal-Oxide Silicon (CMOS) Image Sensor technology

Since 15 years  $\rightarrow$  leading imaging technology

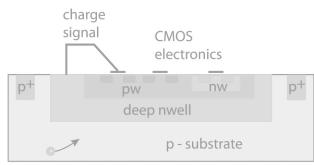

#### MIMOSA-1 Early versions with thin and low resistivity epi-layer

https://doi.org/10.1016/S0168-9002(00)00893-7

MOS TRANSISTORS IN PWE

DISTANCE

- Shallow depletion region  $\rightarrow$  low charge collection efficiency

- Detector element covers only a small fraction of the pixel area

CMOS used in **camera phones**, vehicles, security systems

Future MAPS in ALICE LHOP. 2023,

25th May

F.Carnesecchi,

2

and beyond

### ALICE **CMOS MAPS – evolution for charged particles**

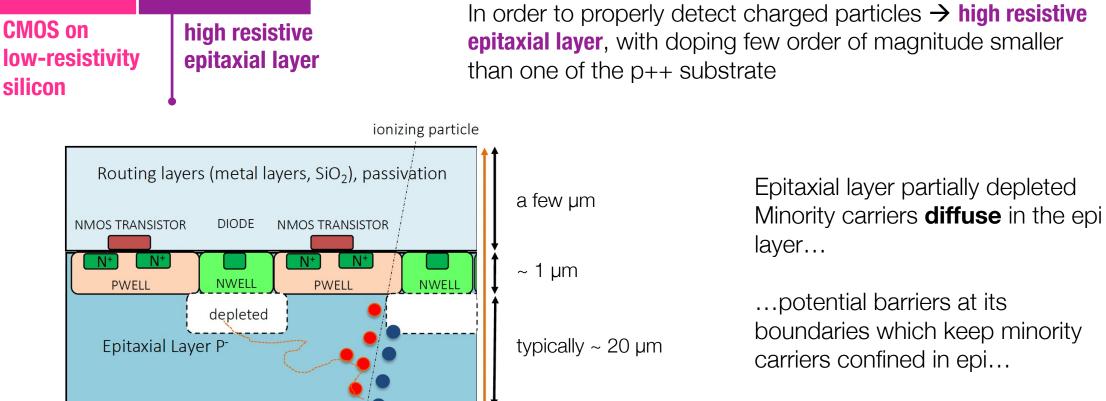

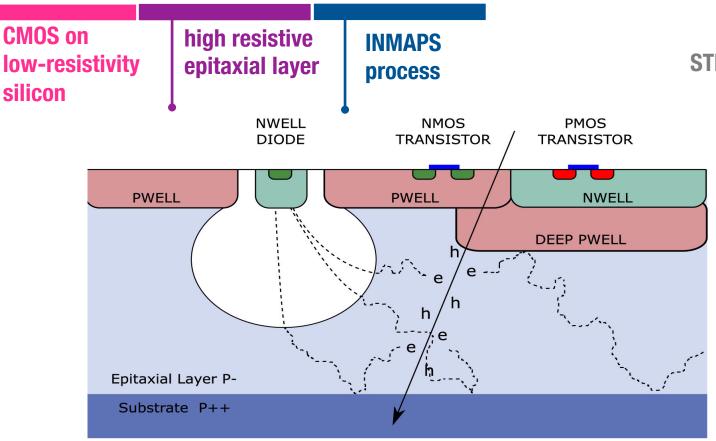

Recipe's evolution for CMOS MAPS for charged particles...

Substrate P<sup>++</sup>

total typically ~ 50 µm

... till they reach the depleted region → drift

N.B. **NMOS transistors in a pwell**  $\rightarrow$  to shield the source and drain junctions from the epitaxial layer

$\rightarrow$  essential, otherwise these sources and drains would act as collection electrodes

would prevent the nwell from collecting all the signal charge.

silicon

# **STAR – first application in HEP**

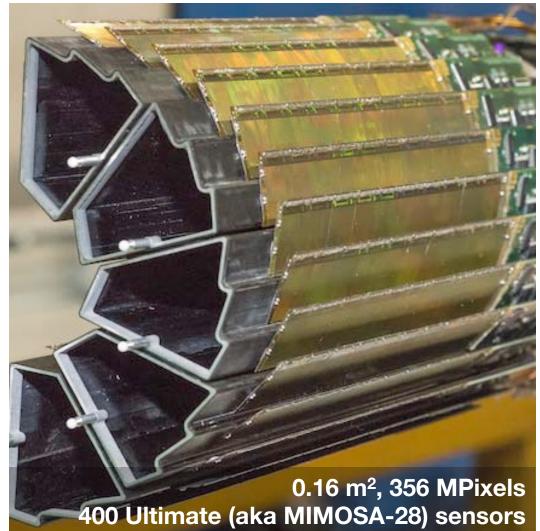

### Full detector in 2014

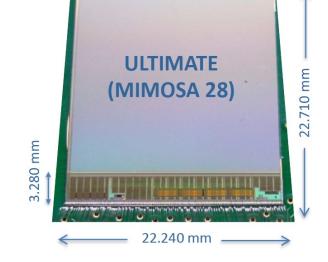

#### MIMOSA-28

high-resistivity p-epi layer The STAR building block

- x/X<sub>0</sub> = **0.39%** (first layer at 28 mm)

- technology node 0.35 μm CMOS

- power ~ 150 mW/cm<sup>2</sup>

- 18.4 µm pitch

- 20 µm not fully depleted and no reverse bias

- Charge collected (mostly) by diffusion

- **NIEL** up to ~ $10^{12}$  1MeV n<sub>eq</sub>/cm<sup>2</sup>

- in-pixel simple circuit: 3T structure

### Physics Runs in 2015-2016

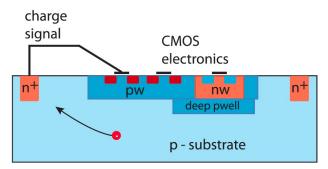

### **CMOS MAPS – INMAPS process**

Recipe's evolution for CMOS MAPS for charged particles...

### 2008, https://doi.org/10.3390/s8095336 STFC development, in collaboration with TowerJazz

Additional deep P-well :

- no charge collection competition between diode and N-well

- CMOS electronics in pixel

faster

#### Before

limitation of in-pixel circuitry (only NMOS)

### Now

new generation of CMOS APS for scientific applications with **complex CMOS circuitry inside the pixel**

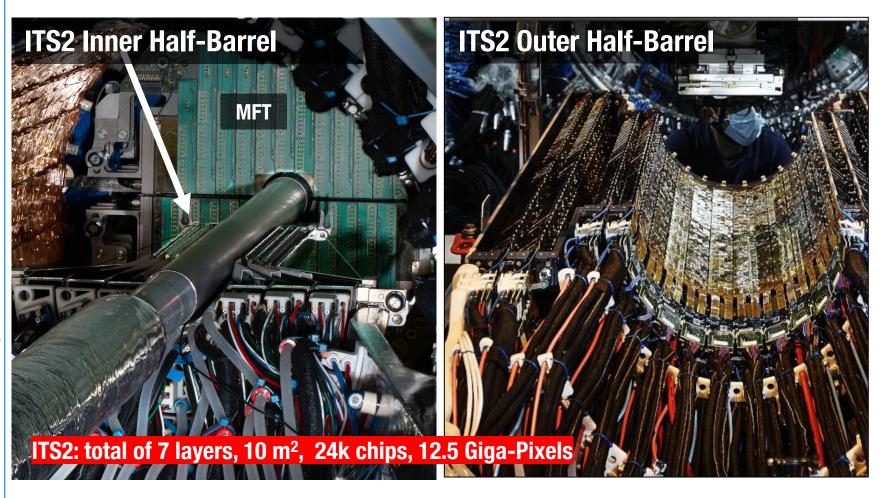

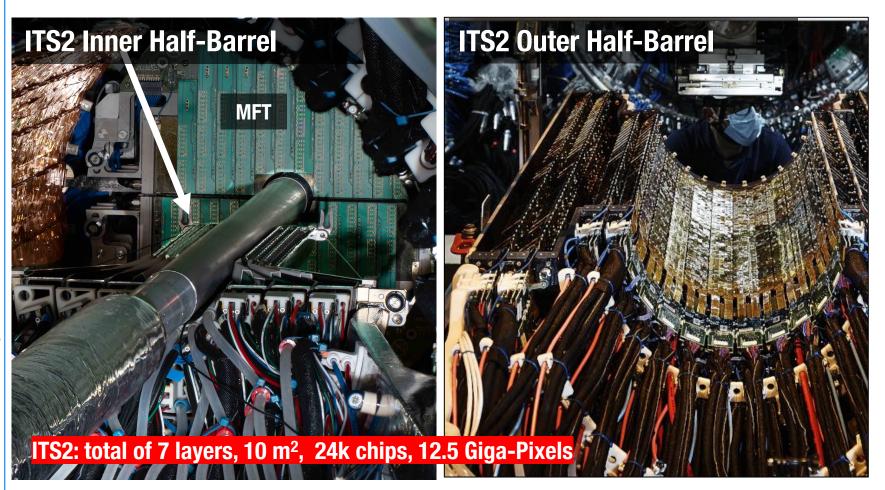

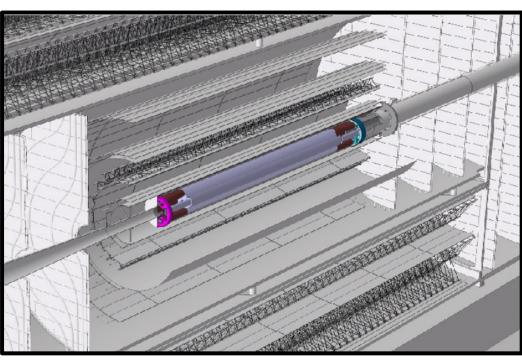

# ALPIDE in ALICE – ITS2

First MAPS in HEP with complex sparse readout similar to hybrid sensors Inner Tracking System 2 (ITS2) upgrade – installation during 2021 (LS2)

# ALPIDE in ALICE – ITS2

First MAPS in HEP with complex sparse readout similar to hybrid sensors Inner Tracking System 2 (ITS2) upgrade – installation during 2021 (LS2)

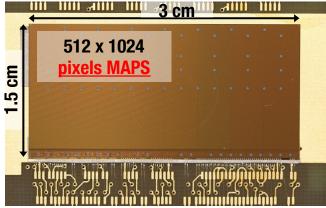

**ALPIDE**, the ITS2 building block

- TJ CMOS 180 nm, high-res. p-type epi layer (25µm)

- Small n-well diode (2µm)  $\rightarrow$  low capacitance (~fF)

- **INMAPS**

- Reverse bias voltage

- pixel size ~ 27x29 µm<sup>2</sup>

- **NIEL**~ $2.7 \ 10^{13} \ 1 \ MeV \ n_{eq}/cm^2$

- 30 nW /pixel (<50 mW/cm<sup>2</sup>)

- 23 mm from IP

- 0.36% x/X<sub>0</sub>/layer, IB

ALPIDEs used also by Muon Forward Tracker in ALICE and in **sPHENIX** with a clone of the Inner **B**arrel

**Currently taking data in ALICE (since 2 years):**

- with stable operation of all the 24k ALPIDEs

- >99% functional pixels

- very low FHR < 10<sup>-7</sup> hits/(events pixel)

State of art for CMOS MAPS application in HEP

More about ITS2 performances in **"Run 3 Performance of new hardware in ALICE", J. Liu, 23/05 11:30**

# What next? What do we need further in HEP?

#### Improve:

- radiation hardness

- position resolution

- material budget

- power consumption

- scalability (larger and larger areas)

#### How:

- pixel pitch ~10-20 µm

- also linked to deeper sub micron tech. node  $\rightarrow$  65 nm node

- ► larger wafers: 200 mm (8") → to 300 mm (12")

- stitching

. . .

### CMOS MAPS – Fully depleted, small electrode

Recipe's evolution for CMOS MAPS for charged particles...

| CMOS on<br>low-resistivity<br>silicon | high resistive<br>epitaxial layer | INMAPS<br>process | Depleted MAPS<br>and new<br>processes |

|---------------------------------------|-----------------------------------|-------------------|---------------------------------------|

A common path in order to improve the radiation hardness and the time resolution → fully depleted CMOS MAPS

Electronics inside charge collection well

### large collection electrode

- → C~300 fF → higher noise O(100 e-) and speed/power penalty

- high and homogeneus electric field

- Large depletion depth

- less trapping -> radiation hard

- possible cross-talk (digital to sensor)

### Electronics outside charge collection well

### small collection electrode

- → C~3fF → reduced noise O(10 e-) and lower analogue power budget (noise, speed)

- potentially low field regions

- smaller depletion depth, needs process modification

- radiation hardness needs process modification

- less prone to cross-talk

### **CMOS MAPS – Fully deplet<u>ed, small electrode</u>**

PMOS

NWELL

LOW DOSE N-TYPE IMPLANT

DEEP PWELL

P<sup>=</sup> EPITAXIAL LAYER

P<sup>+</sup> SUBSTRATE

NMOS

**PWELL**

process modification

NWELL

DEEP PWELL

DEPLETION BOUNDARY

PWELL

https://dx.doi.org/10.1016/j.nima.2017.07.046 https://doi.org/10.22323/1.420.0083

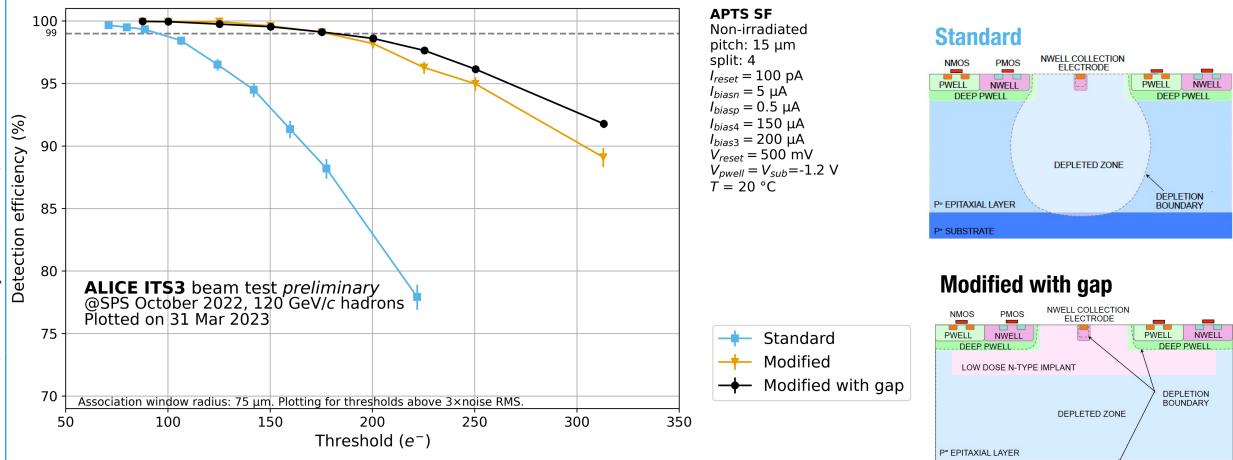

Standard ALICE ITS2 type

- partially depleted epi layer

- Partially collected by diffusion → collection time ~30 ns

- Operation up to 2 10<sup>13</sup> n<sub>eq</sub>/cm<sup>2</sup>

**Modified with gap** planar junction (N-implant) separate from the collection electrode with gap in the low dose n-type implant

NWELL COLLECTION

ELECTRODE

DEPLETED ZONE

#### more volume can be depleted

- Fully operational up to 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup>

- better charge collection in lateral direction

ightarrow Excellent co-operation with foundry

R&D started already by ALICE and followed by MALTA, CLICpix, FastPix

Charge

Charge sharing

**Charge Collection efficiency and speed**

10

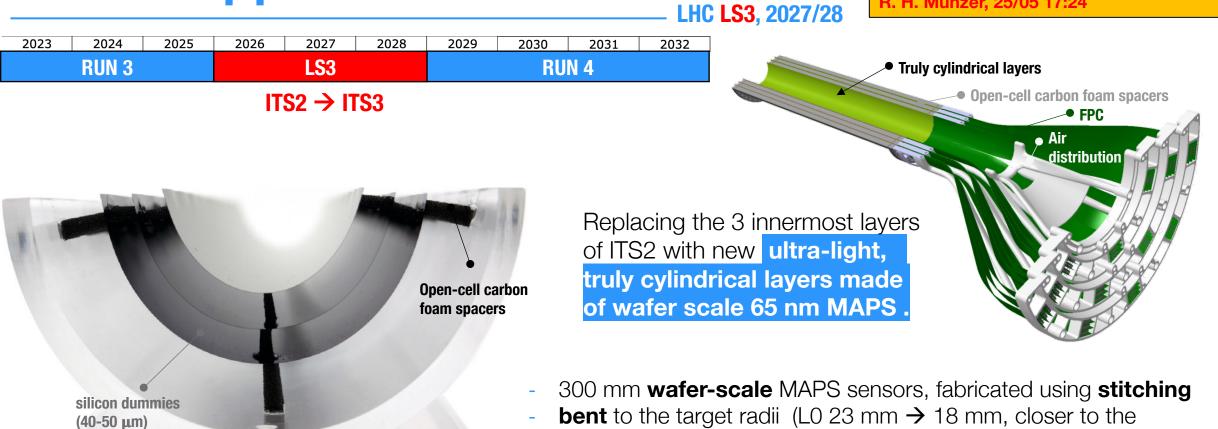

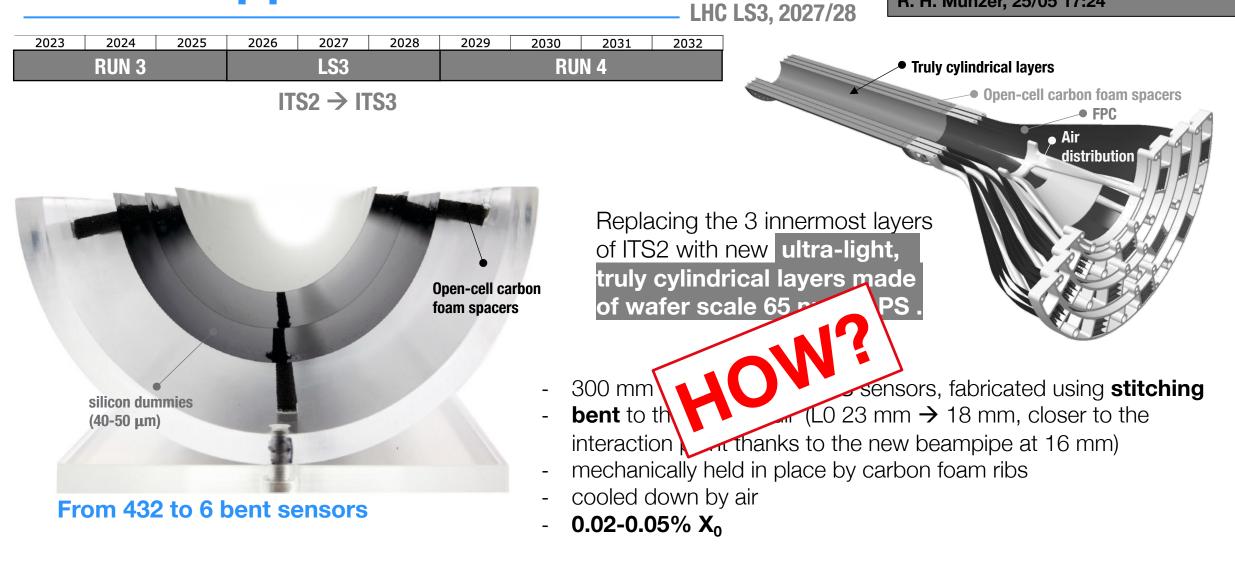

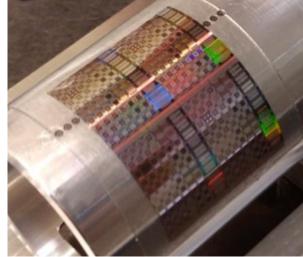

### ALICE Applications – ITS3

From 432 to 6 bent sensors

More about ITS3 performances and physics motivations in **"ALICE upgrades"**, **R. H. Munzer, 25/05 17:24**

- bent to the target radii (L0 23 mm → 18 mm, closer to the interaction point thanks to the new beampipe at 16 mm)

- mechanically held in place by carbon foam ribs

- cooled down by air

- 0.02-0.05% X<sub>0</sub>

N.B. Other experiments even beyond LHC already shown interest in this development

→ ITS3 R&D will pave the way for an ultimate vertex detector concept

## ALICE Applications – ITS3

More about ITS3 performances and physics motivations in **"ALICE upgrades", R. H. Munzer, 25/05 17:24**

N.B. Other experiments even beyond LHC already shown interest in this development → ITS3 R&D will pave the way for an ultimate vertex detector concept

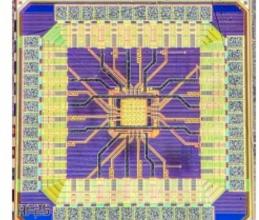

### CMOS MAPS – 65 nm

Recipe's evolution for CMOS MAPS for charged particles...

| CMOS on<br>low-resist<br>silicon | ivity | high resistive<br>epitaxial layer | INMAPS<br>process | Depleted MAPS<br>and new | to 65 nm   | First submission in the Towe<br>Partners Semiconductor<br>(TPSCo) 65 nm technology |

|----------------------------------|-------|-----------------------------------|-------------------|--------------------------|------------|------------------------------------------------------------------------------------|

| silicon                          |       |                                   |                   | processes                | technology |                                                                                    |

Verification of the technology for charge collection efficiency, detection efficiency, radiation hardness:

- larger wafers: 300 mm (instead of 200 mm), single "chip" is enough to equip an ITS3 half-layer

- smaller feature sizes to: lower power consumption, increase spatial resolutions, increase in-pixel circuitry

- **matrix**: 6x6 pixels

- readout: direct analogue readout of central 4x4

- **pitch**: 10, 15, 20, 25 μm

- **process**: 3 variants

### DPTS

- ▶ matrix: 32x32 pixels

- readout: async. digital with ToT

- pitch: 15 µm

- **process**: 1 variant

E

S

12

### CMOS MAPS – 65 nm

Excellent detection efficiency over large threshold range for modified processes

\* SUBSTRATE

### **Beam test results**

### CMOS MAPS – 65 nm

**Process: modified with gap**

-https://arxiv.org/abs/2212.08621

14

#### At ALICE-ITS3 requirements irradiation level slightly larger fake rates, but still largely operational At 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> → ~99% efficiency reached at 20°C **Beam test results** $10^{3}$ 100 ALICE ITS3 doi.org/10.48550/arxiv.2212.08621 <u>At 20°C</u> DPTS, $V_{sub} = -2.4 V$ 10<sup>2</sup> 95 Detection efficiency (%) г Fake-hit rate S Non-irradiated efficiency 90 10<sup>1</sup> (pixel<sup>-</sup> $10^{13}$ 1MeV n<sub>eq</sub> cm<sup>-2</sup> $10^{14} \, 1 \text{MeV} \, n_{eq} \, \text{cm}^{-2}$ 10<sup>0</sup> 85 rate 10<sup>15</sup> 1MeV n<sub>eq</sub> cm<sup>-2</sup> Detection ke-hit 10 kGy $10^{-1}$ 80 - 100 kGy 🛏 10 kGy + 10<sup>13</sup> 1MeV n<sub>ea</sub> cm<sup>-2</sup> FHR ITS3 requirement 10-2 75 **ITS3 requirement** FHR measurement sensitivity limit 10-3 70 125 200 225 250 75 100 150 175 275 300 325 350 Threshold (via $V_{casb}$ ) ( $e^-$ )

25th May 2023, LHCP, Future MAPS in ALICE and beyond

F.Carnesecchi,

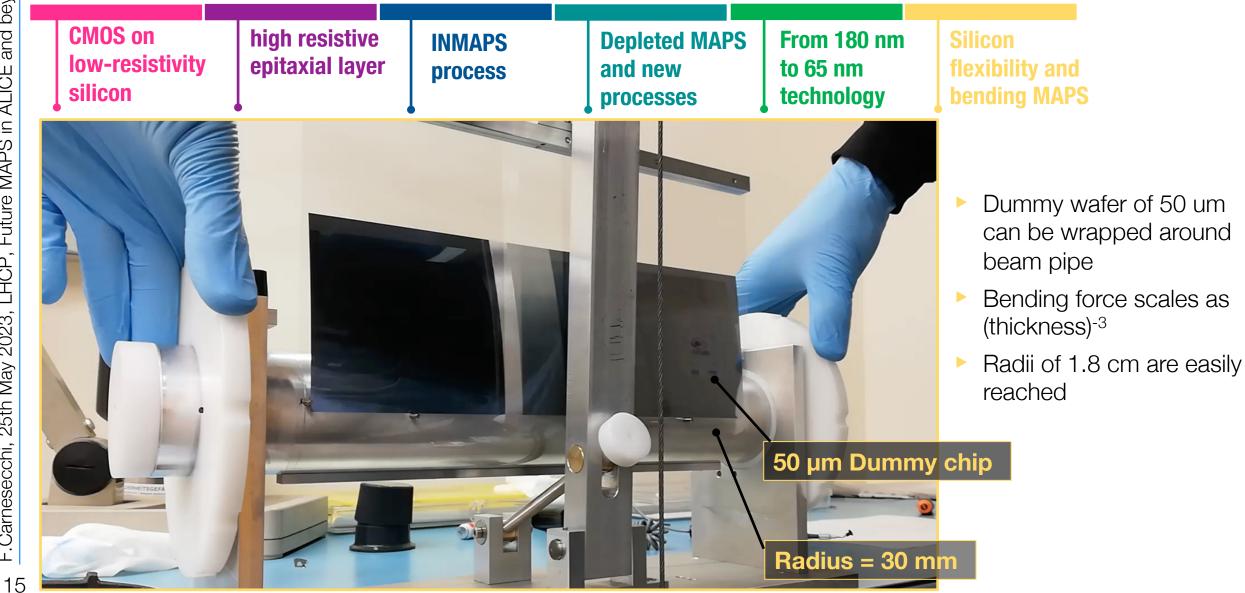

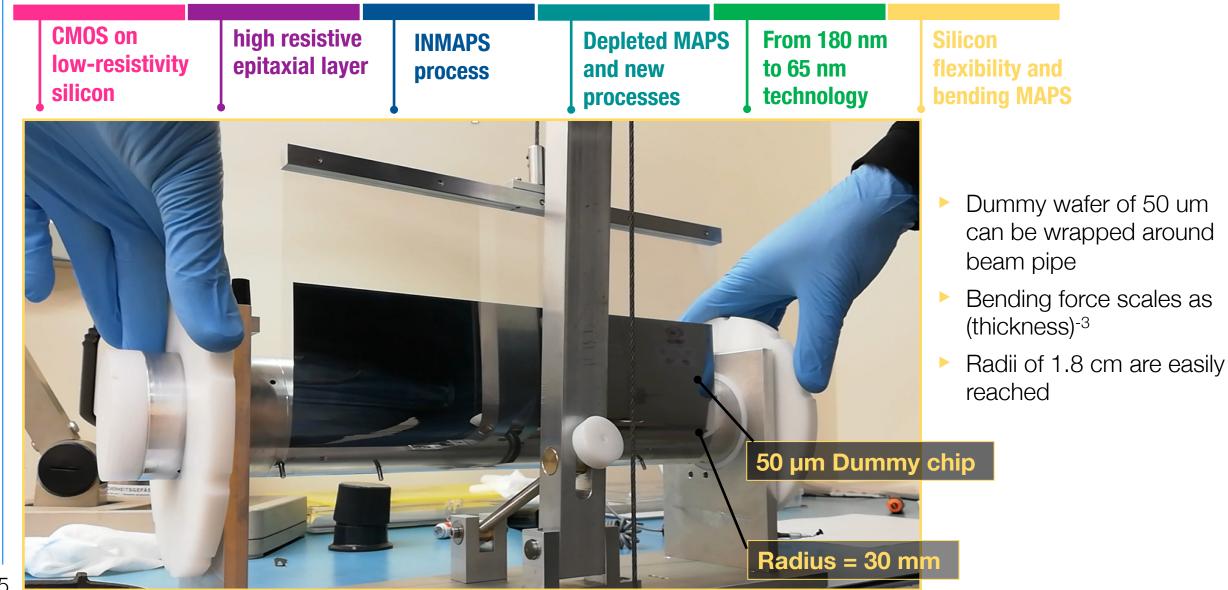

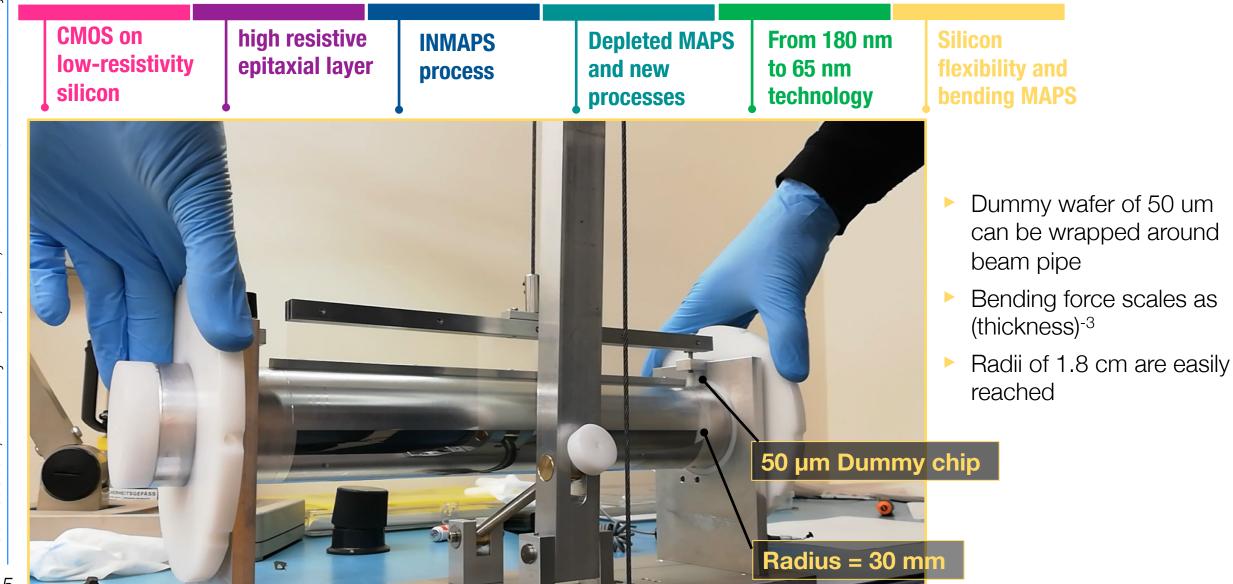

### **CMOS MAPS – Silicon flexibility and bending**

### **CMOS MAPS – Silicon flexibility and bending**

### **CMOS MAPS – Silicon flexibility and bending**

### ALICE **CMOS MAPS – Silicon flexibility and bending**

500

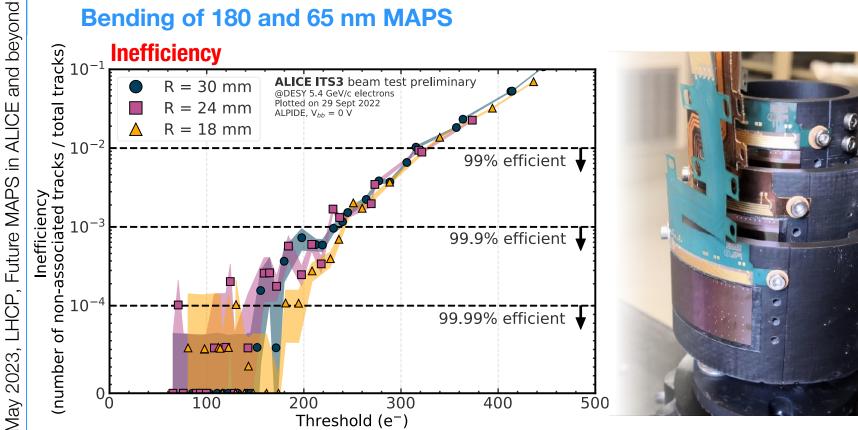

### Bending of 180 and 65 nm MAPS

100

200

total tracks) Inefficiency ALICE ITS3 beam test preliminary = 30 mm 24 mm ALPIDE,  $V_{hh} = 0$ R = 18 mmacks 99% efficient Inefficiency issociated tra .0 99.9% efficient non 99.99% efficient of (number

Functional chips **ALPIDEs (180 nm)** have been bent routinely

Threshold (e<sup>-</sup>)

300

**Several ways** were explored (bending before/after bonding, different jigs)

400

- The chips continue to work (doi:10.1016/j.nima.2021.166280)

- Full mock-up called "µITS3": 6 ALPIDE chips, bent to ITS3 target radii

- Beam test on µITS3: uniform among different radii

### ALICE **CMOS MAPS – Silicon flexibility and bending**

Functional chips **ALPIDEs (180 nm)** have been bent routinely

The chips continue to work (doi:10.1016/j.nima.2021.166280)

Several ways were explored (bending before/after bonding, different jigs)

**TPSCo 65nm chips bending** of both APTS and DPTS

- special boards developed to bond on the bent structure

- tests ongoing

- so far all test structures are working

- more measurements and sample preparation ongoing

F.Carnesecchi, 25th May 2023, LHCP 16

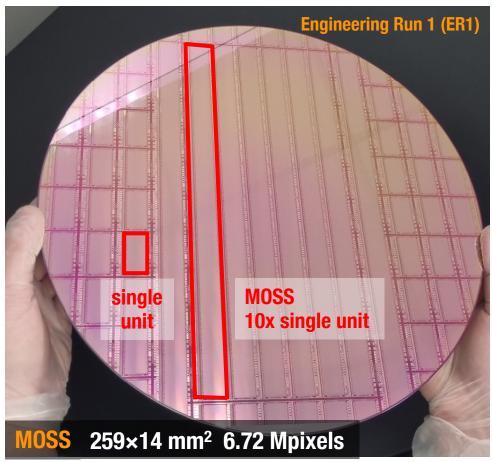

### CMOS MAPS – Wafer scale sensors : stitching

|   | CMOS on<br>low-resistivity | , | high resistive<br>epitaxial laye |   | INMAPS  | Depleted MAP         | S |                        |   | Silicon                         |   | Wafer scale           |

|---|----------------------------|---|----------------------------------|---|---------|----------------------|---|------------------------|---|---------------------------------|---|-----------------------|

|   | silicon                    |   |                                  | ' | process | and new<br>processes |   | to 65 nm<br>technology |   | flexibility and<br>bending MAPS | s | sensors:<br>stitching |

| ( |                            |   |                                  | • |         | processes            | • |                        | • | boliding in A                   |   | outoning              |

- For large area (ALICE-ITS3 280 x 94 mm)  $\rightarrow$  stitching needed:

- aim at a realization of a true single wafer scale sensor

- Eliminates the need of tiling chips on circuit boards

- First wafers just received (ALICE-ITS3)  $\rightarrow$  MOSS (asses the yield of wafer-scale stitched sensors, testability, not yet as sensor for ITS3)

- First CMOS MAPS for HEP using stitching

- to be thinned, diced...and tested

### CMOS MAPS – Wafer scale sensors : stitching

Recipe's evolution for CMOS MAPS for charged particles...

| CMOS on<br>low-resistivity<br>silicon | l ŭ | resistive<br>axial layer | INMAPS<br>process | Depleted MAPS<br>and new<br>processes | S | From 180 nm<br>to 65 nm<br>technology | Silicon<br>flexibility and<br>bending MAP | Wafer scale<br>sensors:<br>stitching |

|---------------------------------------|-----|--------------------------|-------------------|---------------------------------------|---|---------------------------------------|-------------------------------------------|--------------------------------------|

- For large area (ALICE-ITS3 280 x 94 mm)  $\rightarrow$  stitching needed:

- aim at a realization of a true single wafer scale sensor

- Eliminates the need of tiling chips on circuit boards

- First wafers just received (ALICE-ITS3)  $\rightarrow$  MOSS (asses the yield of wafer-scale stitched sensors, testability, not yet as sensor for ITS3)

- First CMOS MAPS for HEP using stitching

- to be thinned, diced...and tested

Very first single unit (single-stitching) tested (two weeks ago!) in a probe station  $\rightarrow$  is alive! can be powered and responds correctly to slow control commands

F.Carnesecchi, 25th May 2023, LHCP, Future MAPS in ALICE and beyond

### ALICE ALICE applications – ALICE 3 LHC LS4, 2033/34

More about ALICE3 performances and physics motivations in **"ALICE upgrades"**, **R. H. Munzer, 25/05 17:24**

2030 2031 2032 2035 2033 2034 2036 **RUN4 RUN 5** LS4 **ALICE 3 :** a next-generation LHC heavy-ion (soft QCD) experiment 800cm 160cm

### Outer tracker with around 60 m<sup>2</sup> MAPS tracker

- order of magnitude larger than ITS2

- large coverage:  $\pm 4\eta$

- high-spatial resolution:  $\approx 5 \,\mu m$

- very low material budget:  $X/X_0$  (total)  $\leq 10\%$

- low power consumption  $\approx 20 \text{ mW/cm}^2$

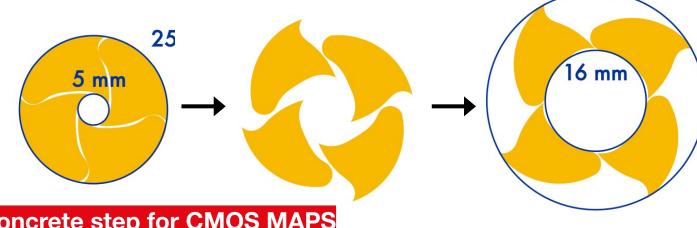

### ALICE ALICE Applications – ALICE 3 LHC LS4, 2033/34

More about ALICE3 performances and physics motivations in **"ALICE upgrades"**, **R. H. Munzer, 25/05 17:24**

Innermost layers (vertex detector)

- will be based on wafer-scale, ultra-thin, curved MAPS "iris tracker" → ITS3 like BUT in vacuum

- → 3 layers inside beampipe, retractable configuration

### clear extension of ITS3 developments

pushes the **technology** on a number of fronts

- distance from interaction point: 5 mm

- radiation hardness ~  $10^{16}$  1MeV  $n_{eq}/cm^2$

- spatial resolution:  $\approx 2.5 \ \mu m$

- material budget:  $\approx 0.1\%X_0$ /layer

#### **CMOS MAPS** are ideal devices for vertexing

Low material budget (thin + low power), high resolution (small pixels), large surfaces (commercial process), non-planar geometries (thin silicon is flexible)

#### Impressive progress over the last decade

Already several applications, e.g. STAR 2015 and ALICE ITS2 2021, and improvements on radiation hardness, low noise, and speed

#### ALICE ongoing R&D on bending, deeper sub micron tech. node (65 nm) and stitching (wafer scale)

Big push from ITS3 (2026): new inner-most 3 layers, wafer-scale, bent, stitched sensors  $\rightarrow$  paves the way for future experiments like ALICE 3 (2033): 60 m<sup>2</sup> silicon-only

#### Lot of interest on ALICE ITS3 developments from other experiments

Similarly to what happened with ITS2