# **FASER Experiment: Ongoing and Proposed Upgrades**

Large Hadron Collider Physics Conference 2023 Belgrade, 25-5-2023

### Stefano Zambito, on behalf of the FASER collaboration

## Introduction & Outline

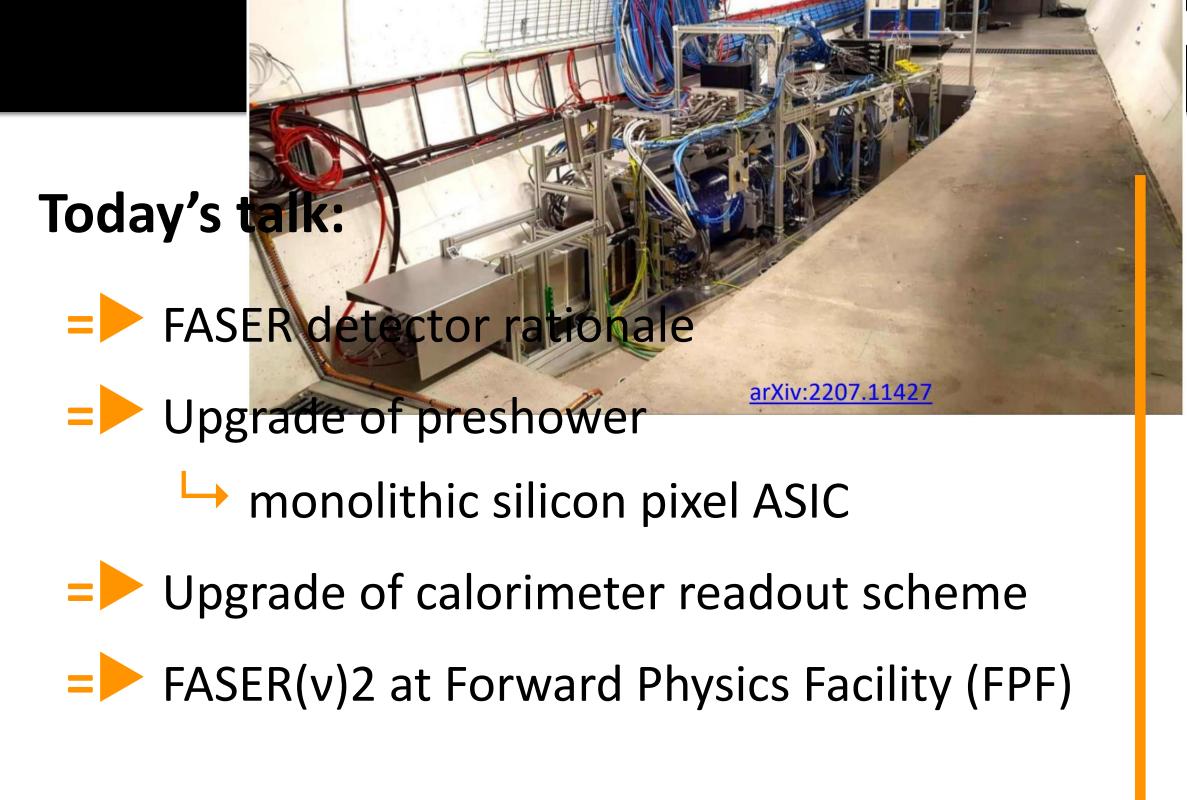

## Today's talk:

- **FASER detector rationale**

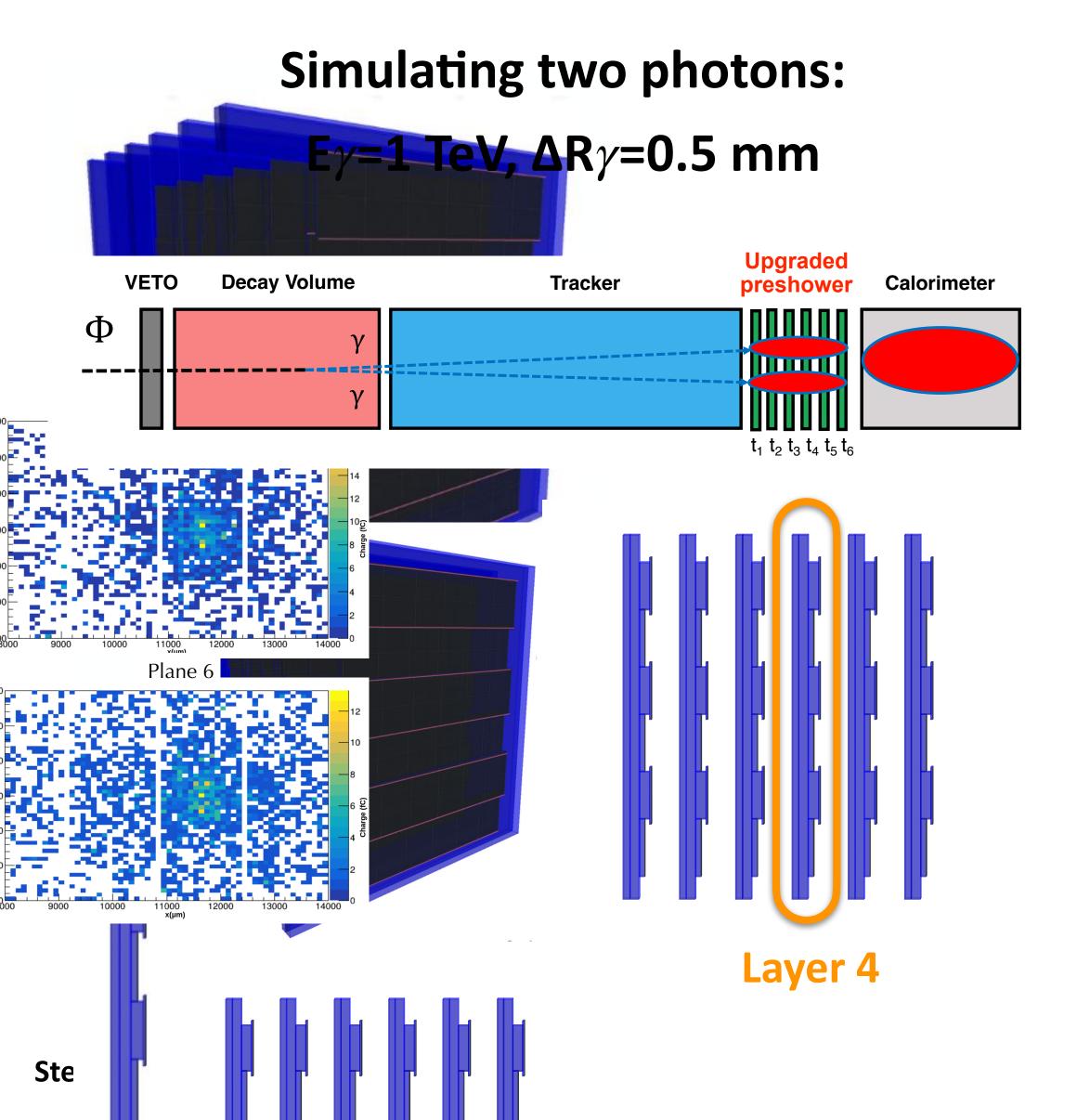

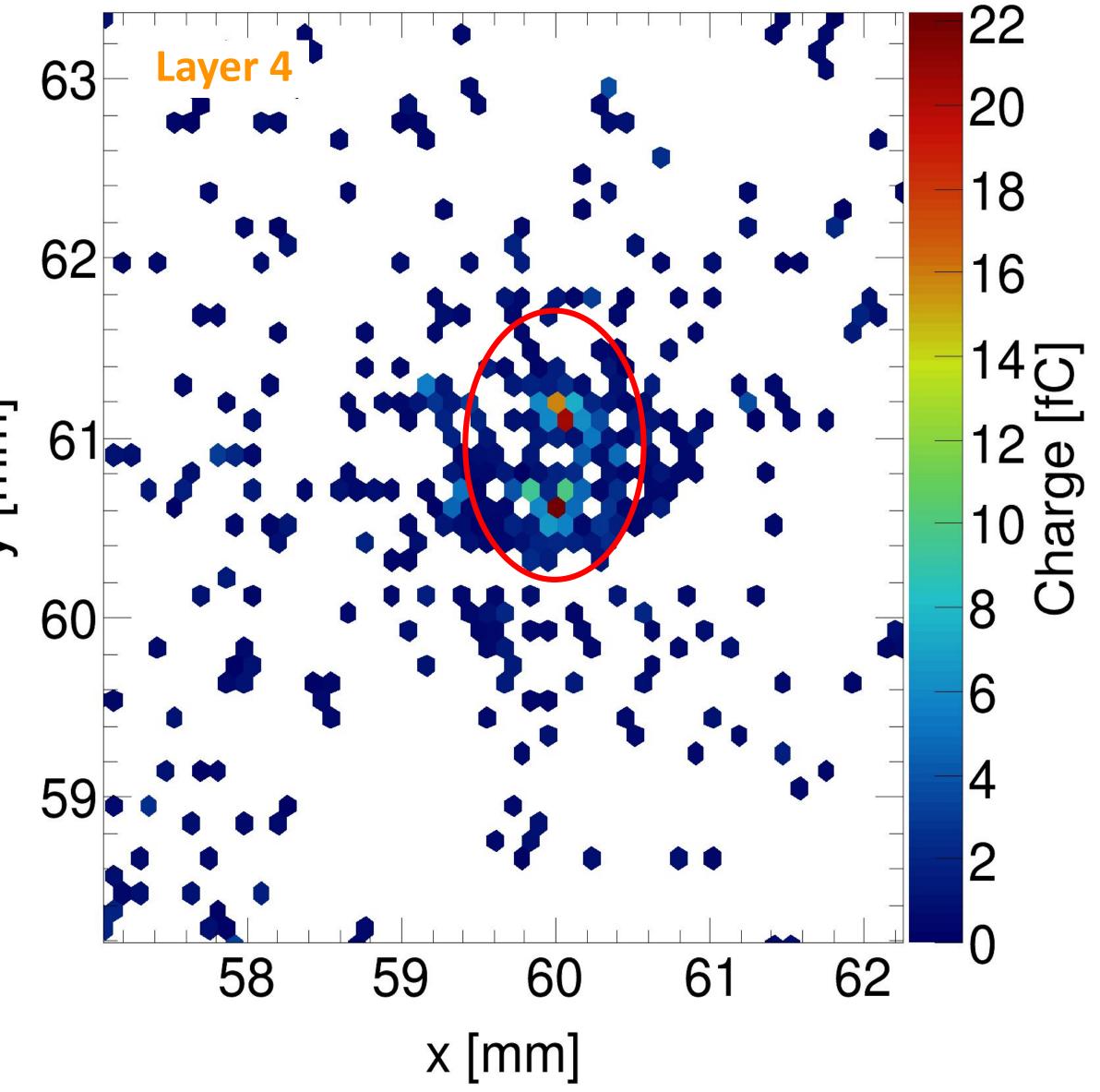

- Upgrade of preshower

- → monolithic silicon pixel ASIC

- Upgrade of calorimeter readout scheme

- = FASER(v)2 at Forward Physics Facility (FPF)

### Check these out too!

- **Noshin:** *first dark photon search results*

- **—** <u>Tobias:</u> *neutrinos in the forward region*

- Rosham: new physics searches at FPF

### **Check these out too!** UNIVERSITE

Noshin: first dark photon search results

<u>Tobias:</u> *neutrinos in the forward region*

<u>Rosham:</u> *new physics searches at FPF*

**Stefano Zambito** | *Université de Genève*

## on & Outline

## **ATLAS**

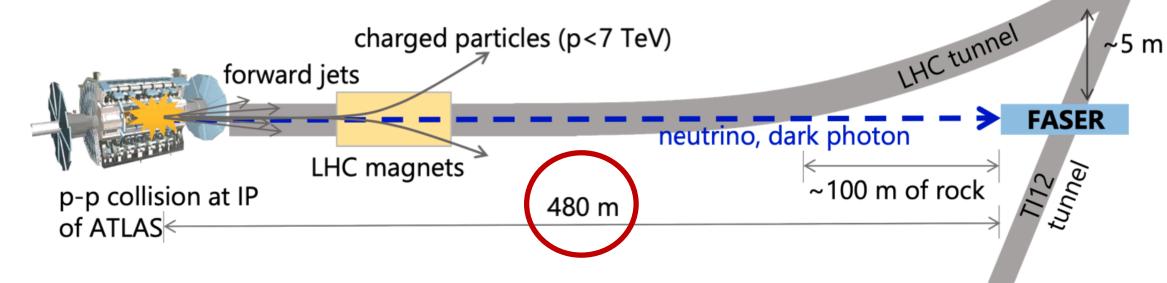

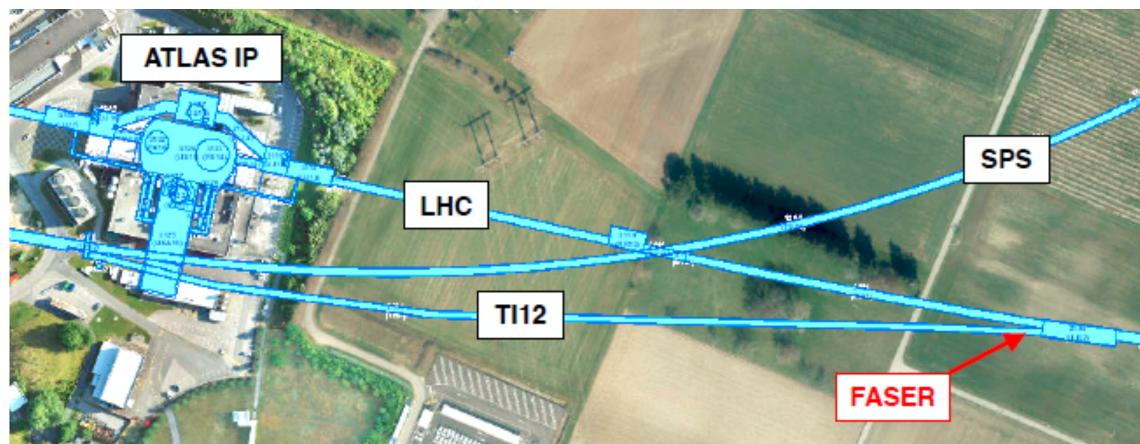

## The ForwArd Search ExpeRiment at the LHC

### Search for light, weakly interacting (LLP) new particles

stemming from rare meson decays ( $\pi$ ,  $\eta$ , K, D ...) in very forward ATLAS region ( $\theta \sim$  mrad)

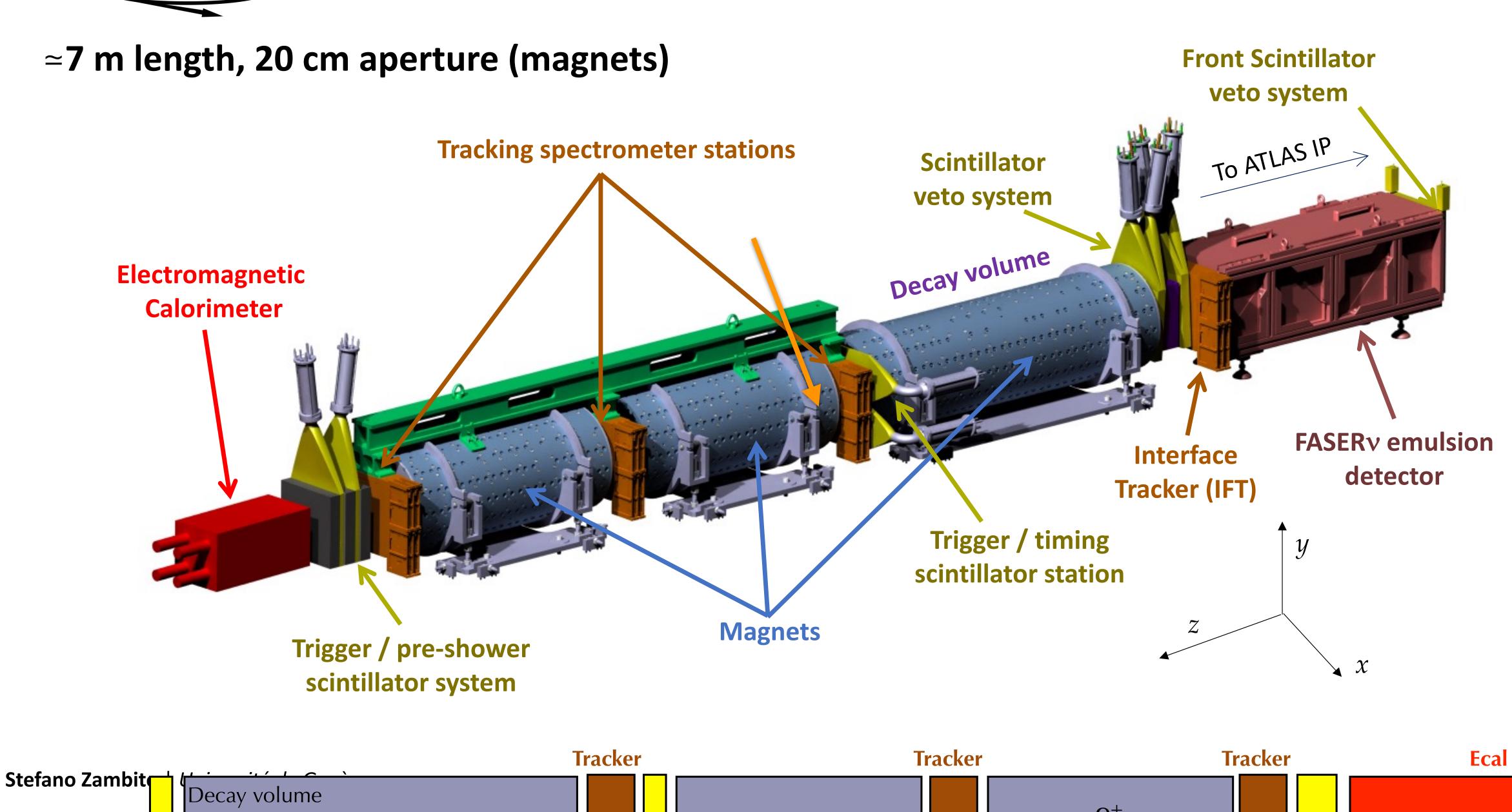

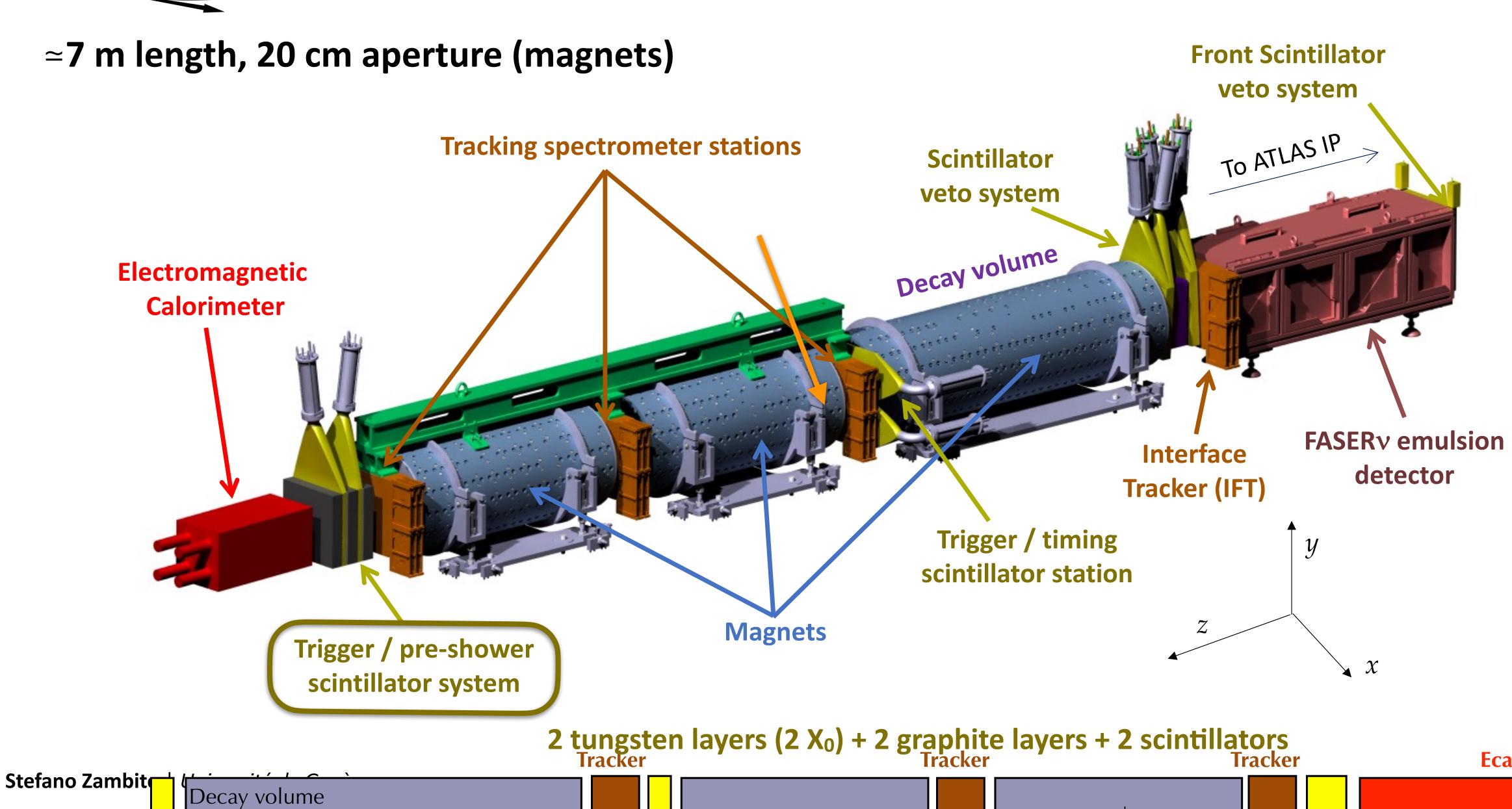

## $\simeq$ 7 m length, 20 cm aperture (magnets)

### $\simeq$ 7 m length, 20 cm aperture (magnets)

Ecal

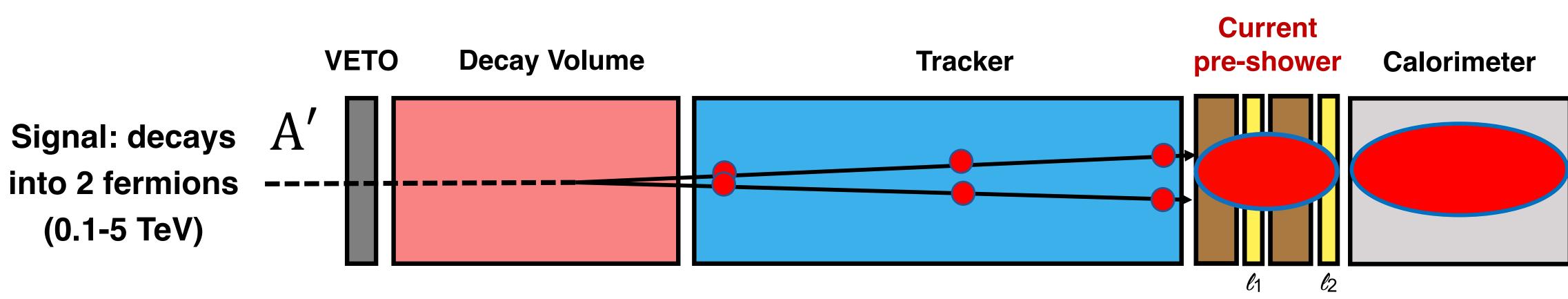

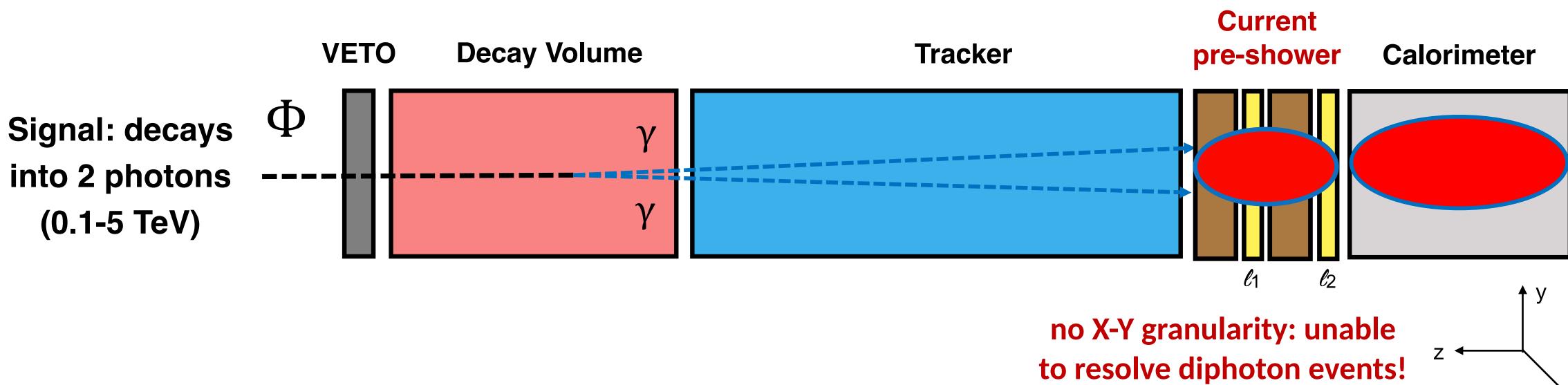

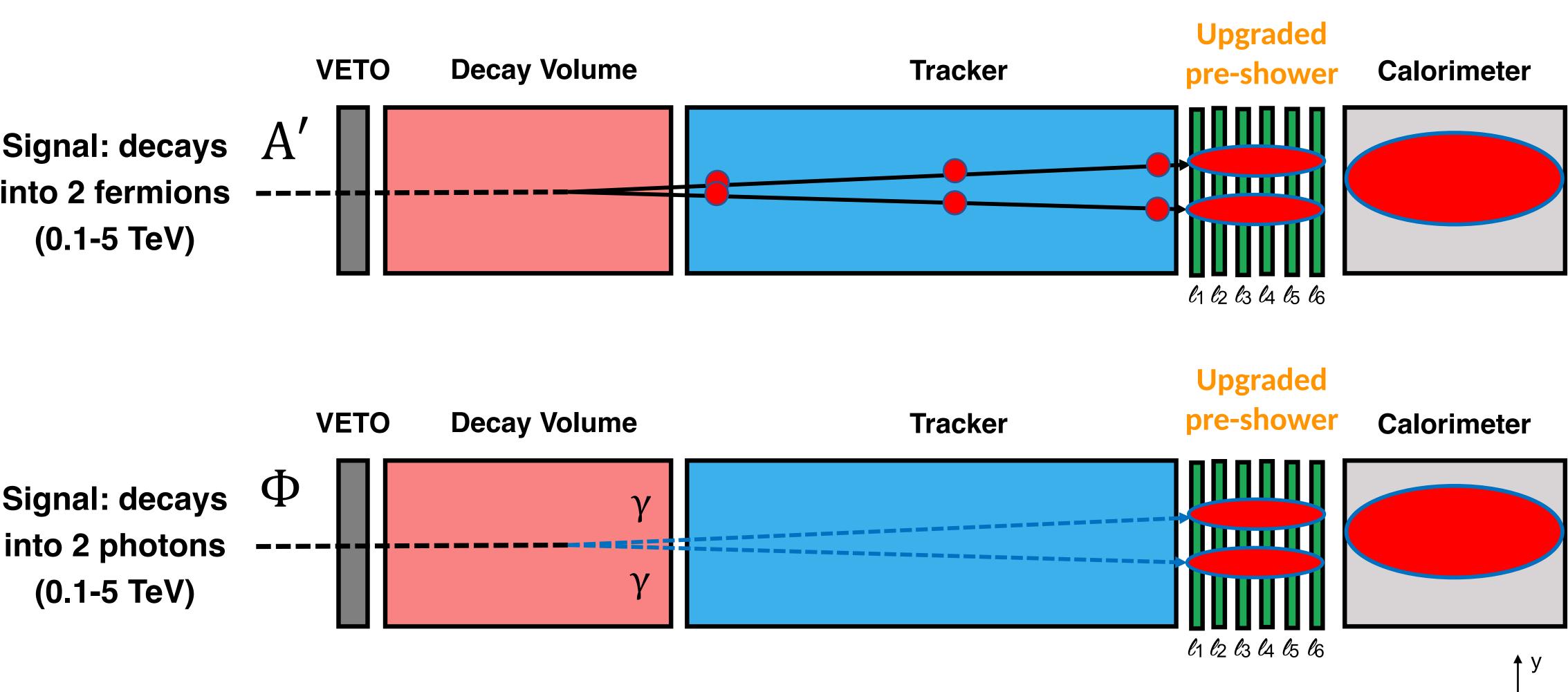

## **Current** Detection Capabilities: Two Fermions

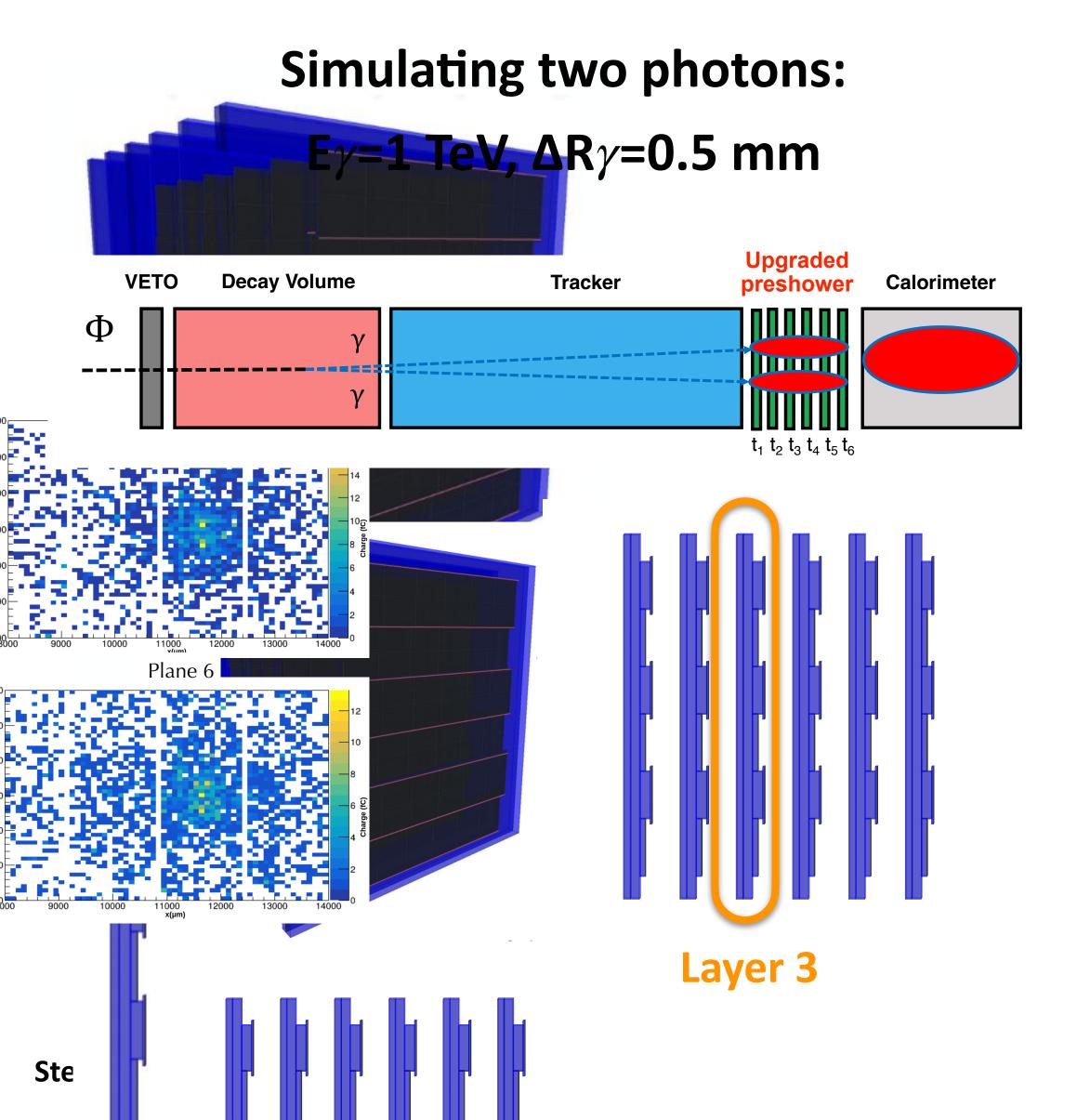

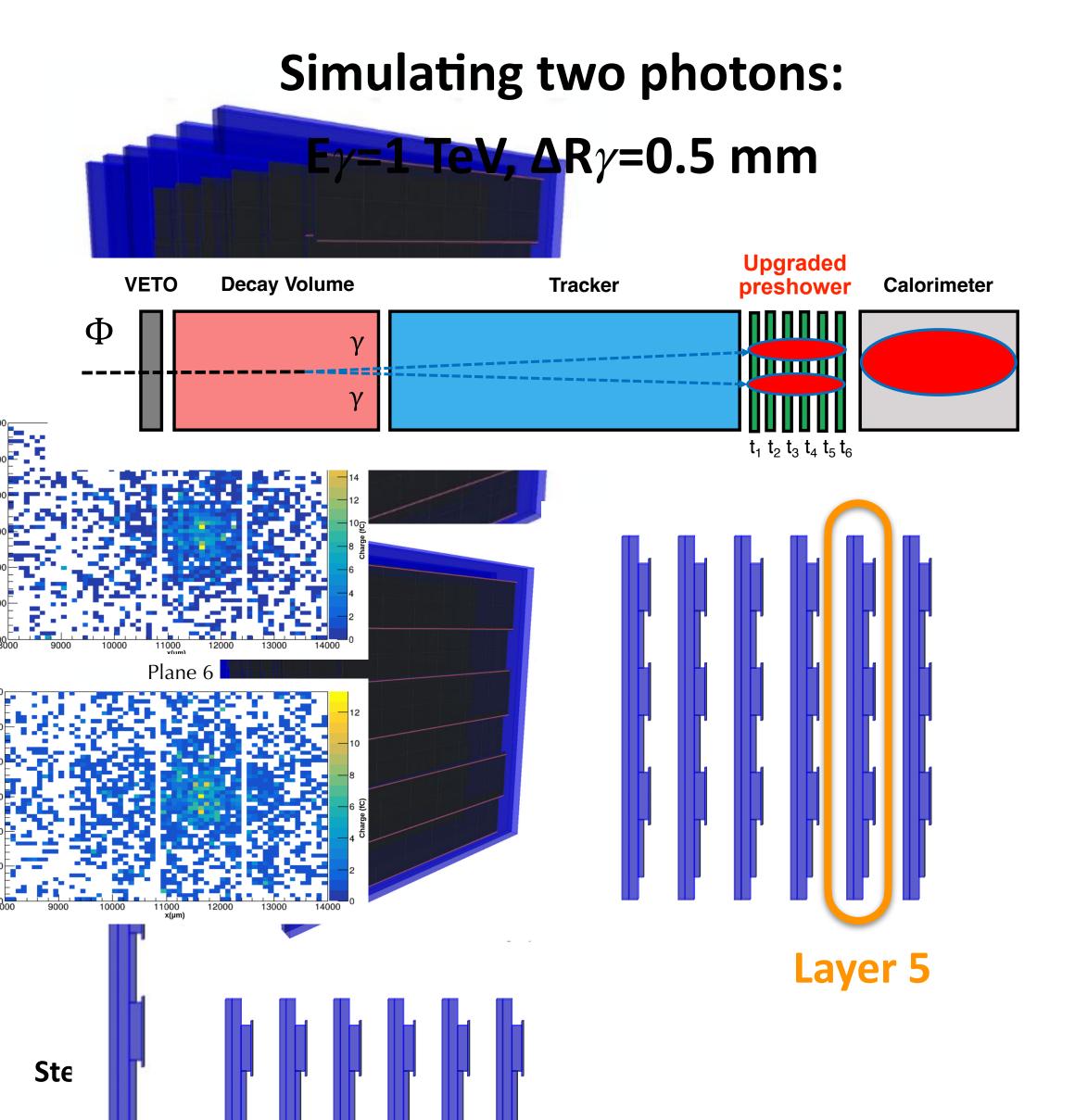

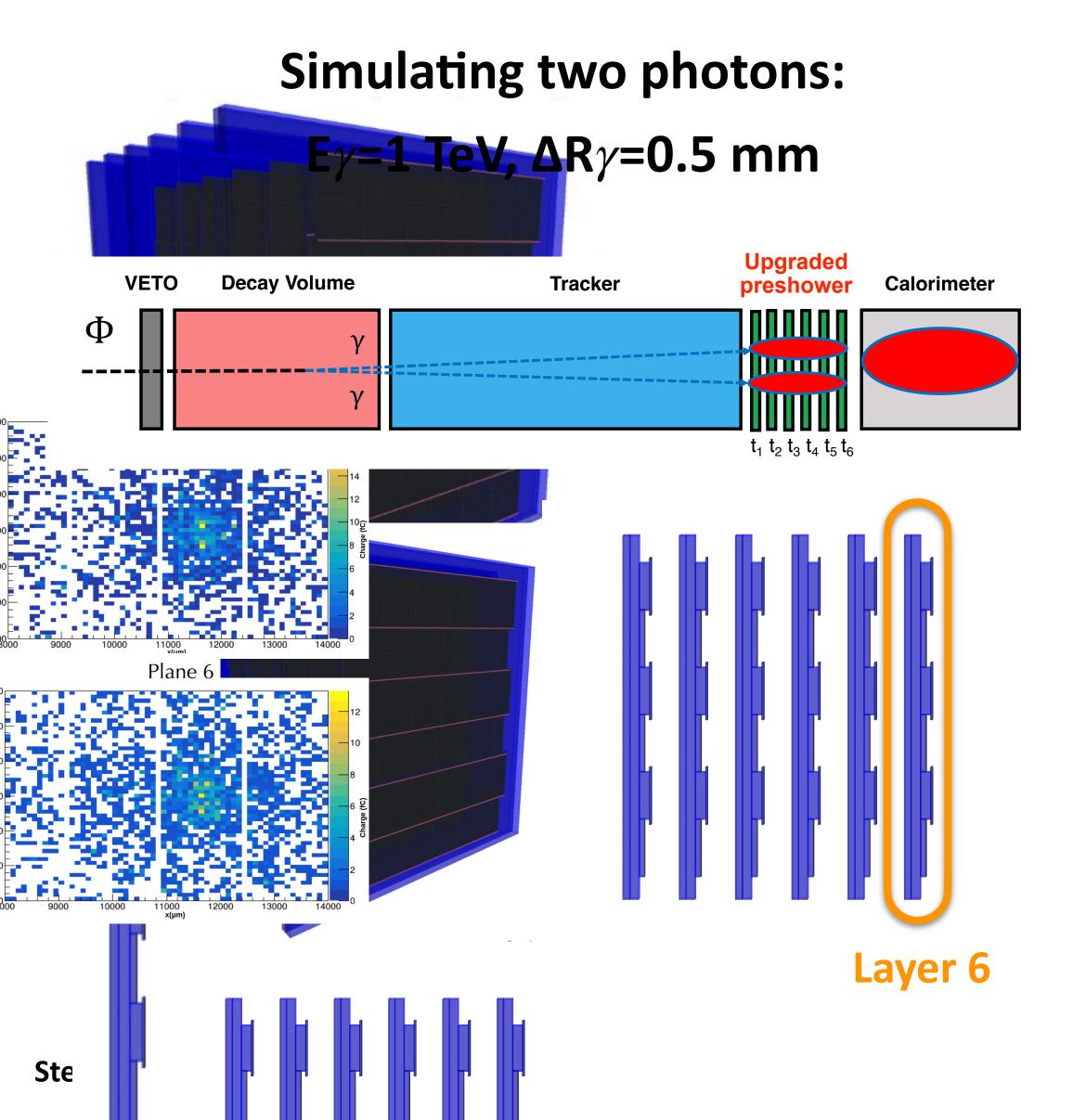

## **Desired** Detection Capabilities: Two Fermions / Photons

**Stefano Zambito** | *Université de Genève*

### fine X-Y granularity, high dynamic range

## New Preshower Detector []

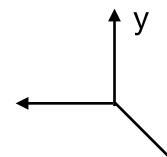

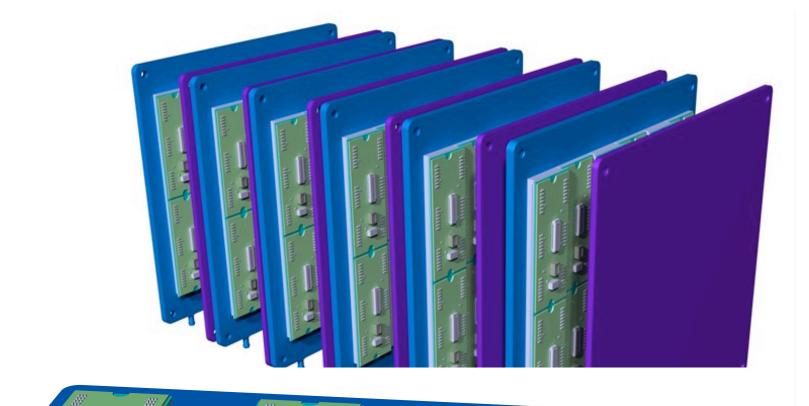

The readout module will consist of an assembly of six ASICs mounted in an array of two by three. Given the expected dimensions of an ASIC the module size will be  $315 \times 67 \text{ mm}^2$ . The gap between Upgraded preshower detector  $(\lesssim 300)$

### 6 detector p $\mapsto$ each plan

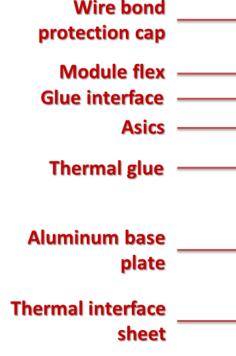

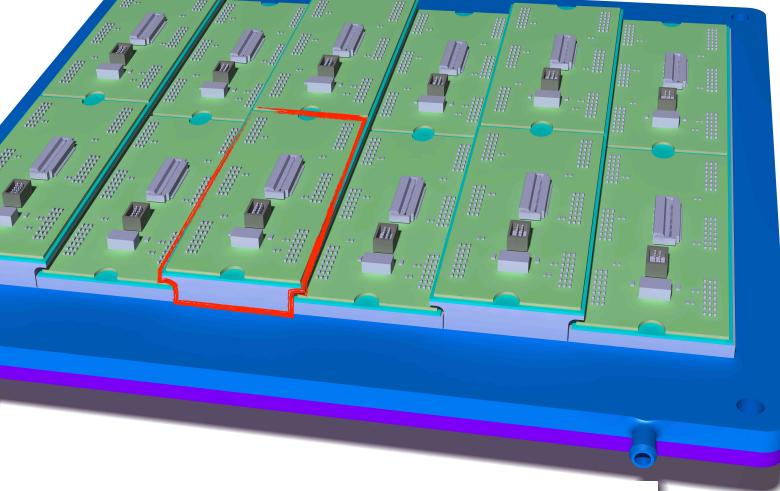

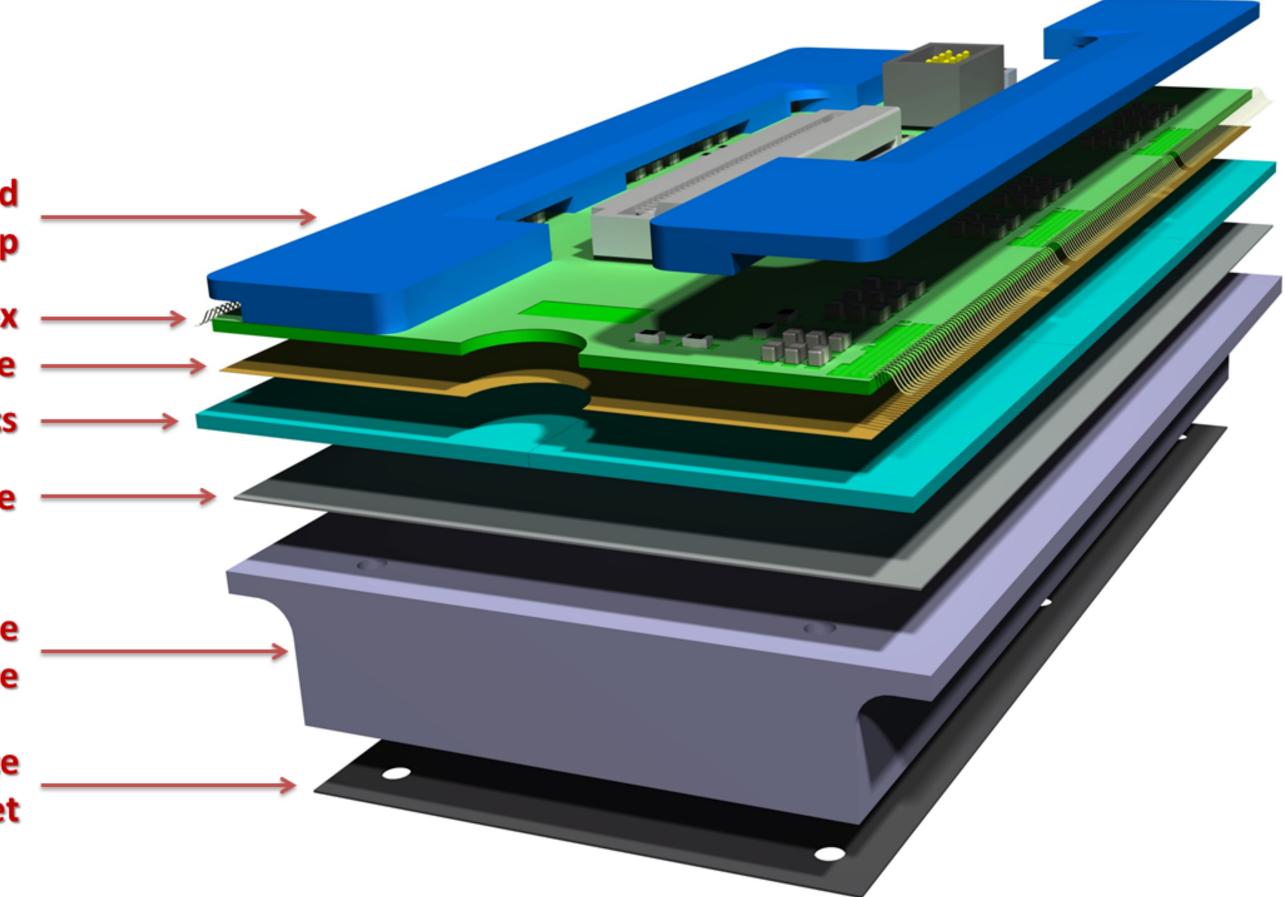

Figure 13: Exploded CAD view of a module assembly. A module is composed by six ASICs glued to an usions and mass. The module consists of fuminum base-plate. The module flex with the electrical interconnection and the SMD components is glued Traon the top of the ASICs. The bottom layer is the thermal interface sheet that

ded when integra

a module to the cooling plate. The size is  $\sim 31 \times 67 \text{ mm}^2$ .

Each module will be supported by a base-plate with thermo-mechanic plate will be made of aluminum wit features (See Figu a reference mounting hole and slot. It be machined six threaded hole a nard anodising for surface insulation receive an electrolytic I breakdown. This procedure was already used to tion of the sense prototy (Figure 14).

interface to the six ASICs for the I/O and powering will be made through a material flexible printed circuit board (PCB). Each ASIC has  $\sim 100$  wire bonding pads to be interconnected teor grease the flex PCB. The module flex will be interconnected to an external patch panel with zeroand dismountinesertion force connector for the digital signal, clock and command and with a separate pigtail for the module powering.

The module will drive four types of power lines, three LV supply and one HV for the six ASICs. 420 While the sensors will have low current consumption (below 100  $\mu A$ ), the analog, the digital and the driver supply lines will consume  $\sim 1$  A each. The system is designed to handle a module power

sors

## New Preshower Detector [II]

Jo

Wire bond protection cap Module flex Glue interface

Asics

Thermal glue

Aluminum base plate

Thermal interface sheet

### m fithela 12 modules per plange at on cooling plate

dules. The cooling plate size is  $\sim 20 \text{ x } 20 \text{ cm}^2$  and 5 mm thick. Of One

rts i**StefanouZambito**anel with ensites ides Gethèves. The module consists of bed on Figure 13 except the base plate and the thermal interface sheet.

## 6 ASICs per module, 208x128 pixels each

y [mm]

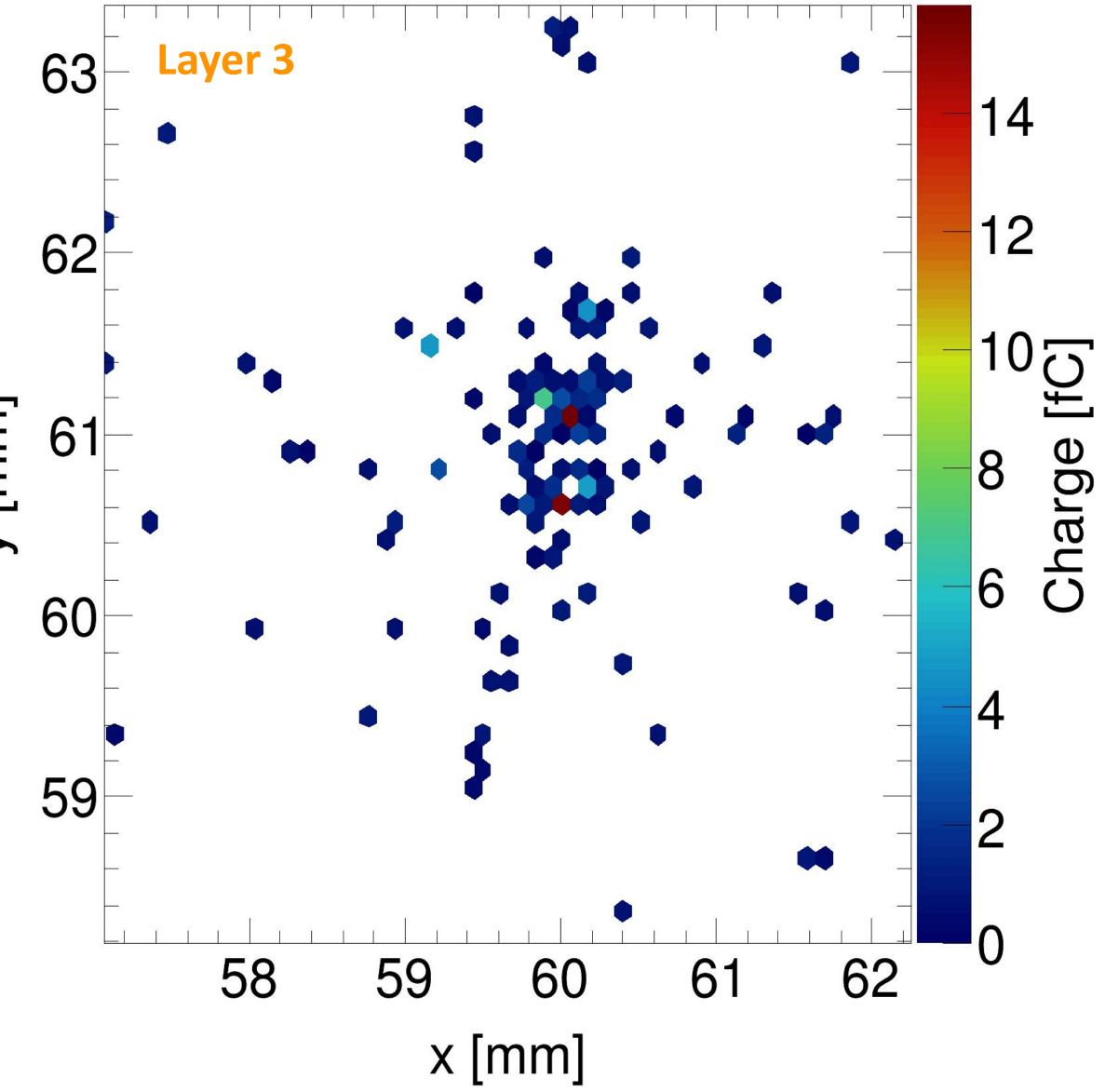

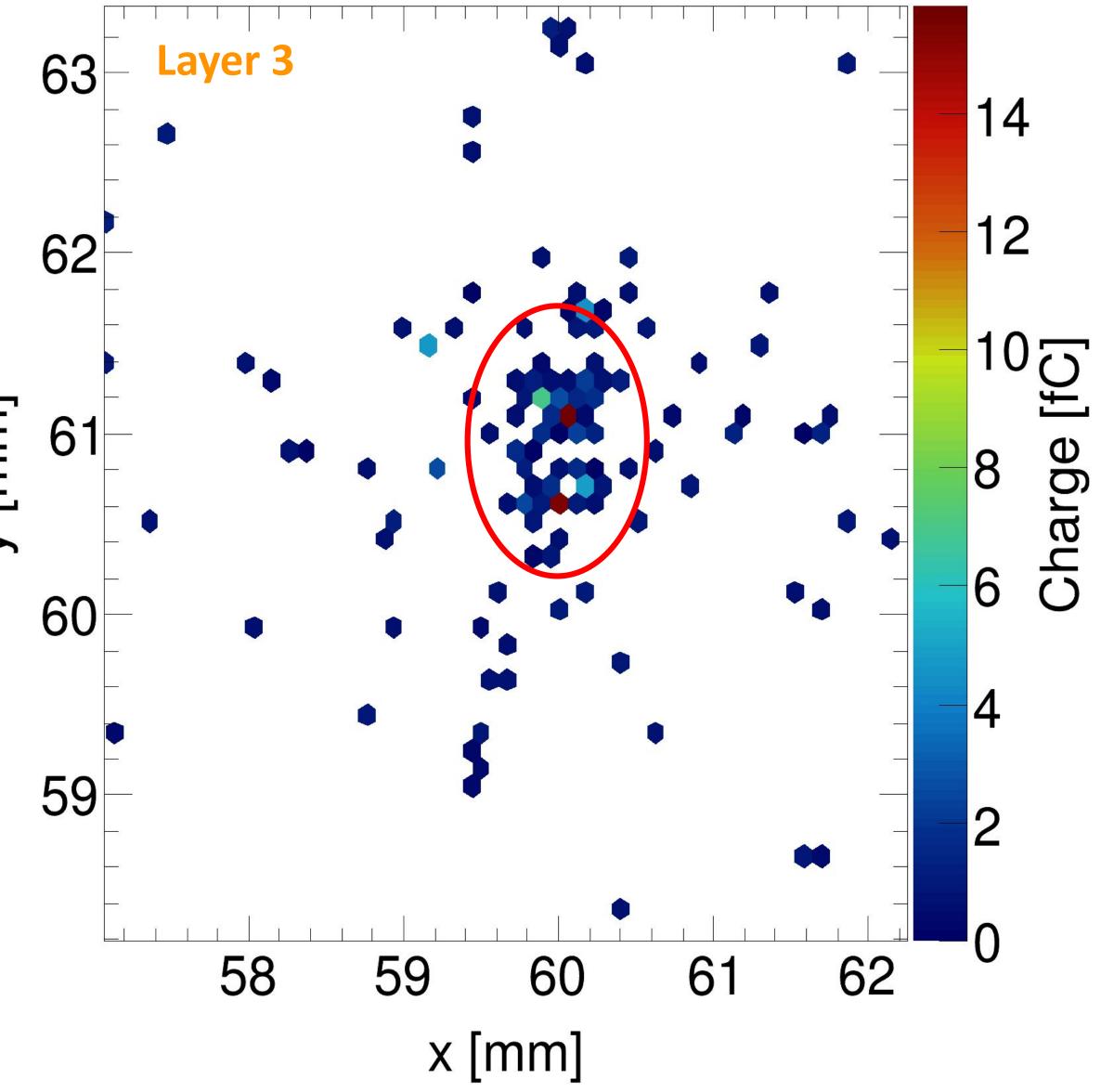

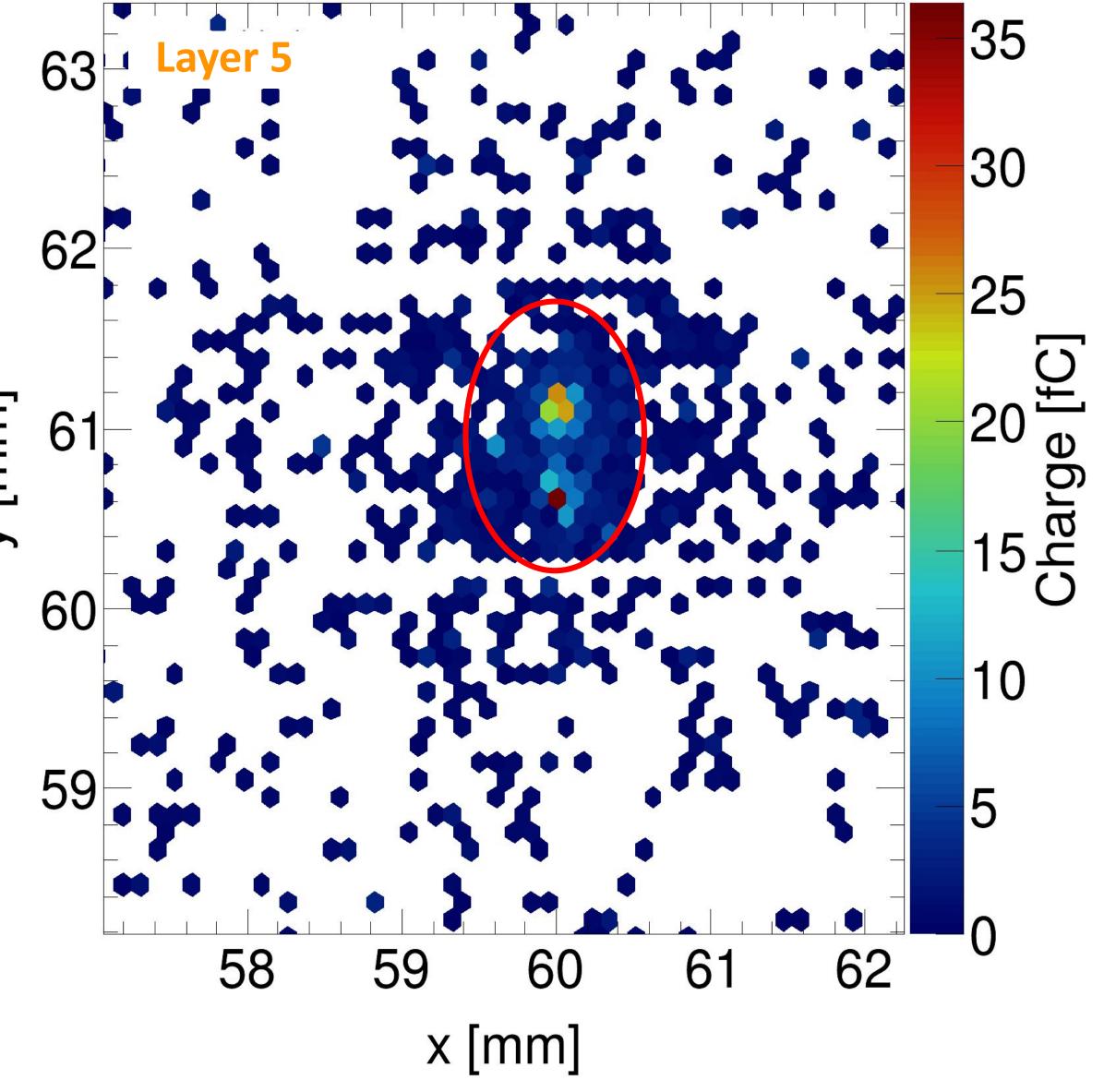

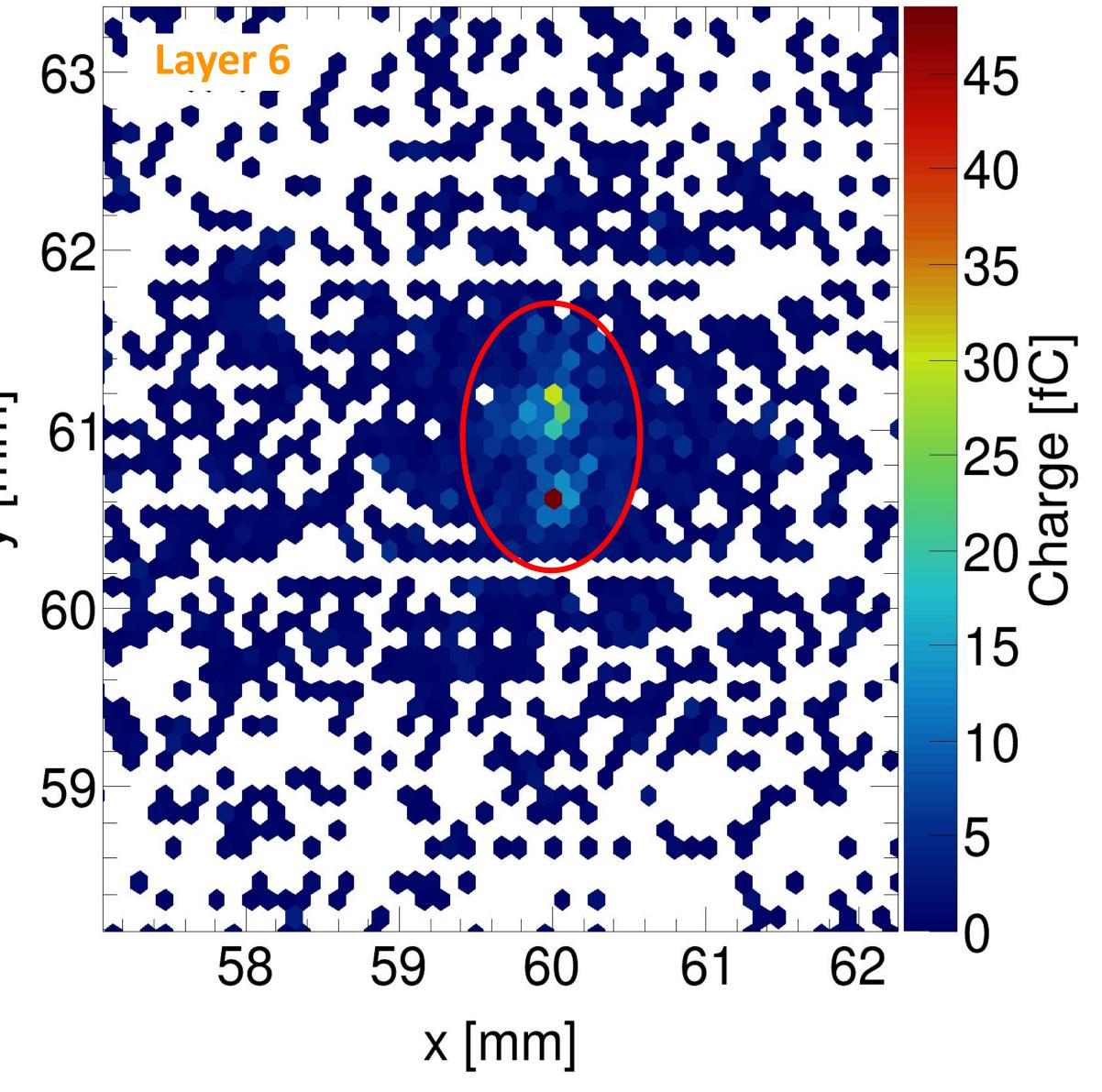

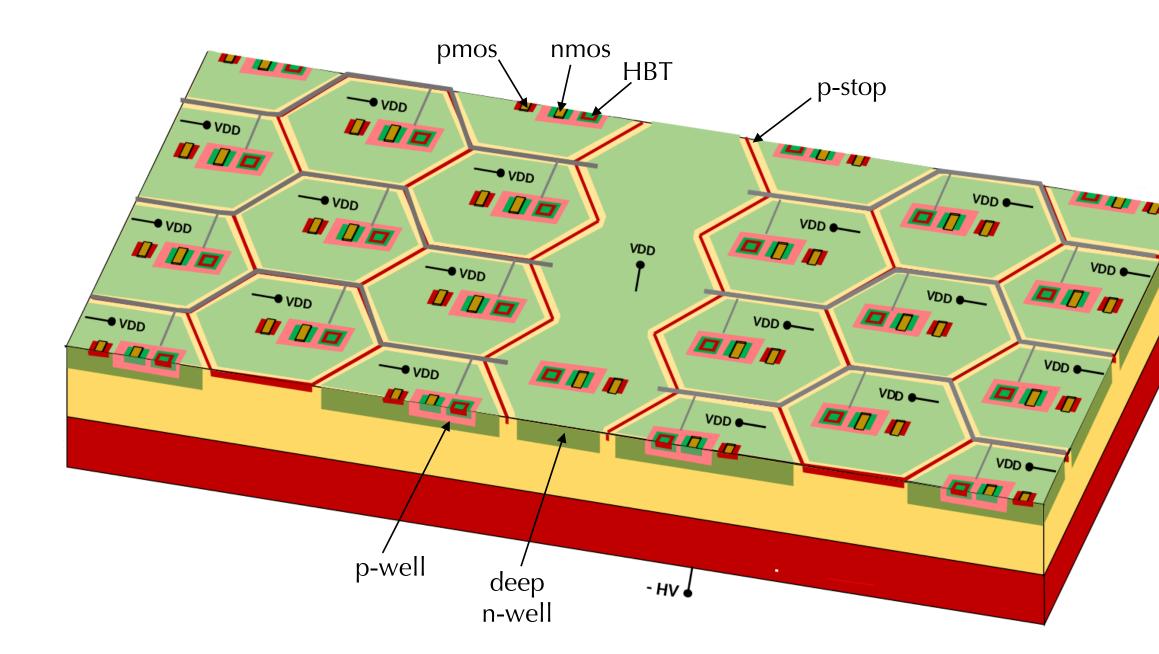

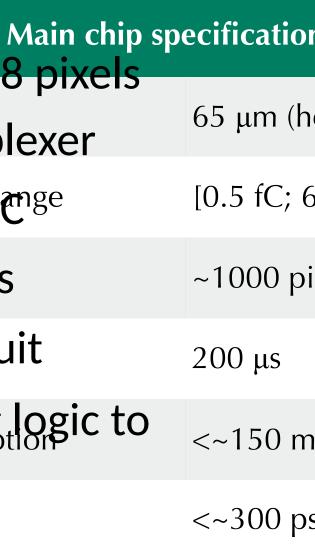

## Monolithic Pixel ASIC: Sensor

## Monolithic active pixel sensor 130 nm SiGe BiCMOS technology (IHP SG13G2)

- High-resistivity (220  $\Omega \cdot cm$ ) substrate, about 130  $\mu m$  thickness =

- Hexagonal pixels integrated as triple wells; 80 fF pixel capacitance =

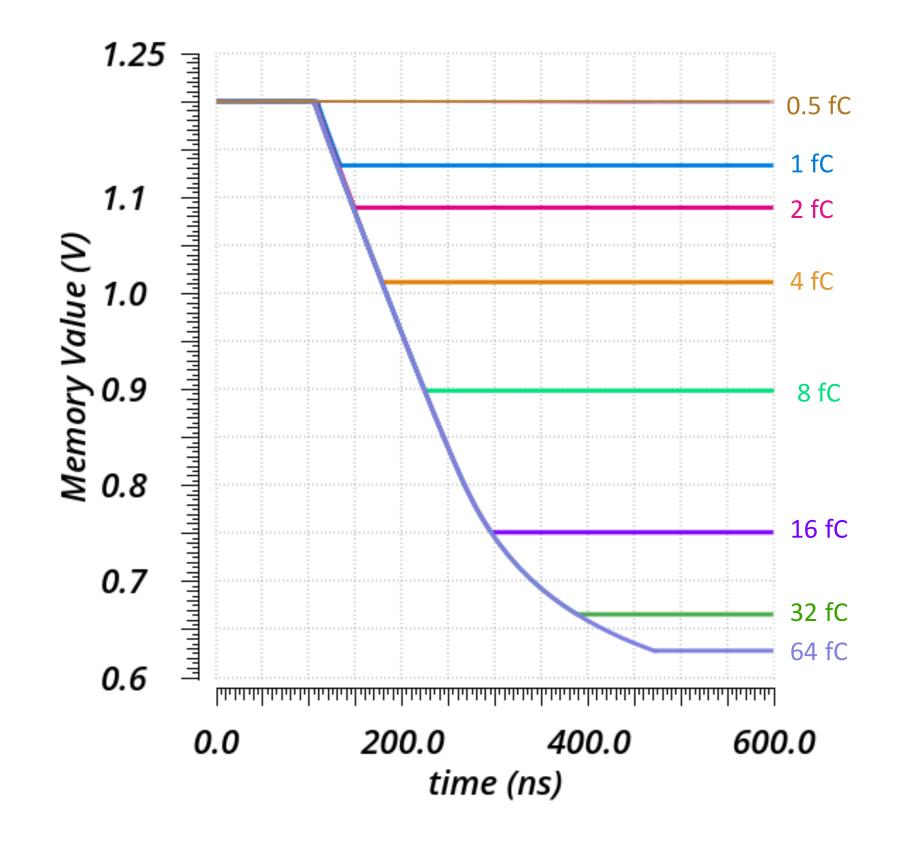

- High dynamic range for charge measurement (0.5÷65 fC); fast readout of many channels =

| Main specifications |                          |  |  |

|---------------------|--------------------------|--|--|

| Pixel Size          | 65 μm side (hexagonal)   |  |  |

| Pixel dynamic range | 0.5 ÷ 65 fC              |  |  |

| Cluster size        | O(1000) pixels           |  |  |

| Readout time        | < 200 µs                 |  |  |

| Power consuption    | < 150 mW/cm <sup>2</sup> |  |  |

| Time resolution     | < 300 ps                 |  |  |

**Stefano Zambito** | *Université de Genève*

19

**Stefano Zambito** | *Université de Genève*

20

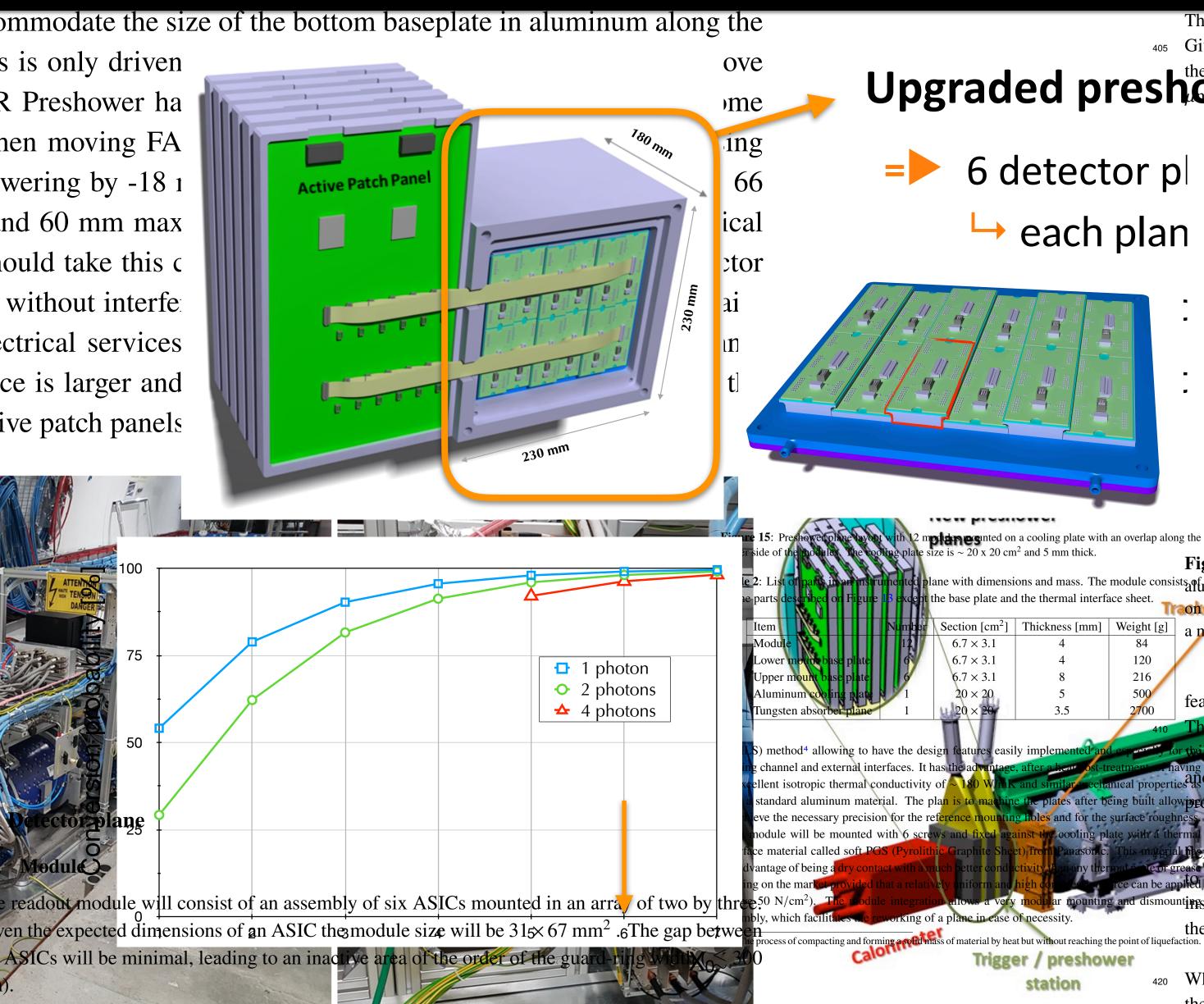

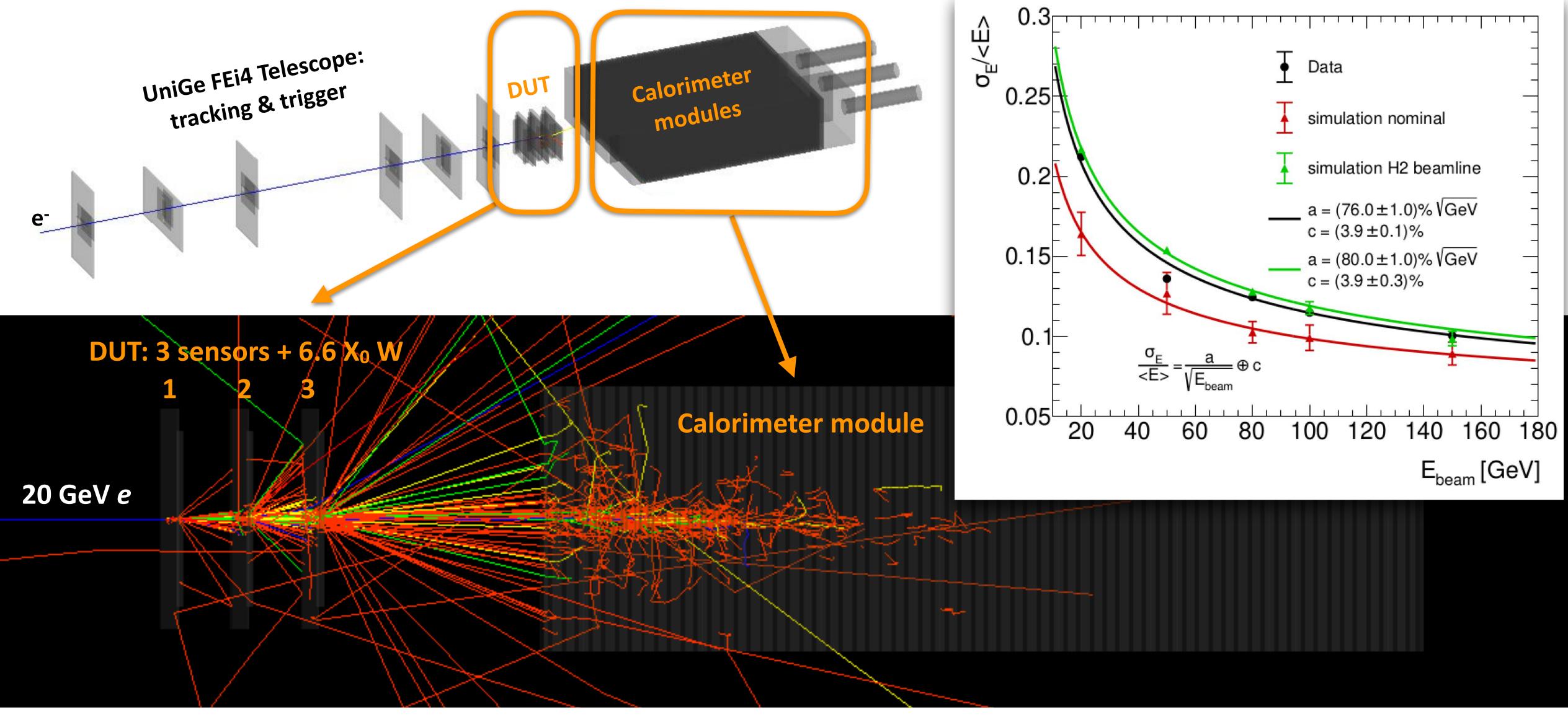

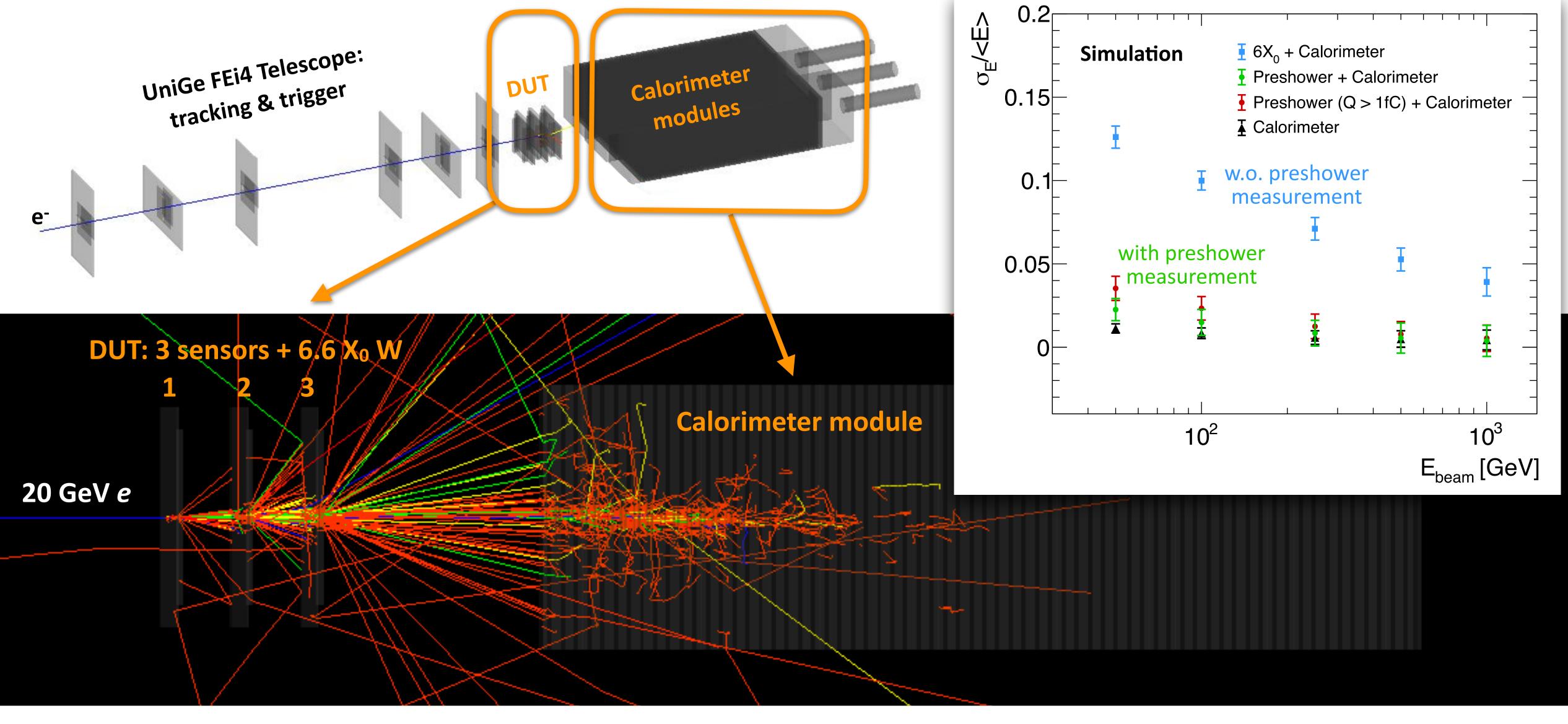

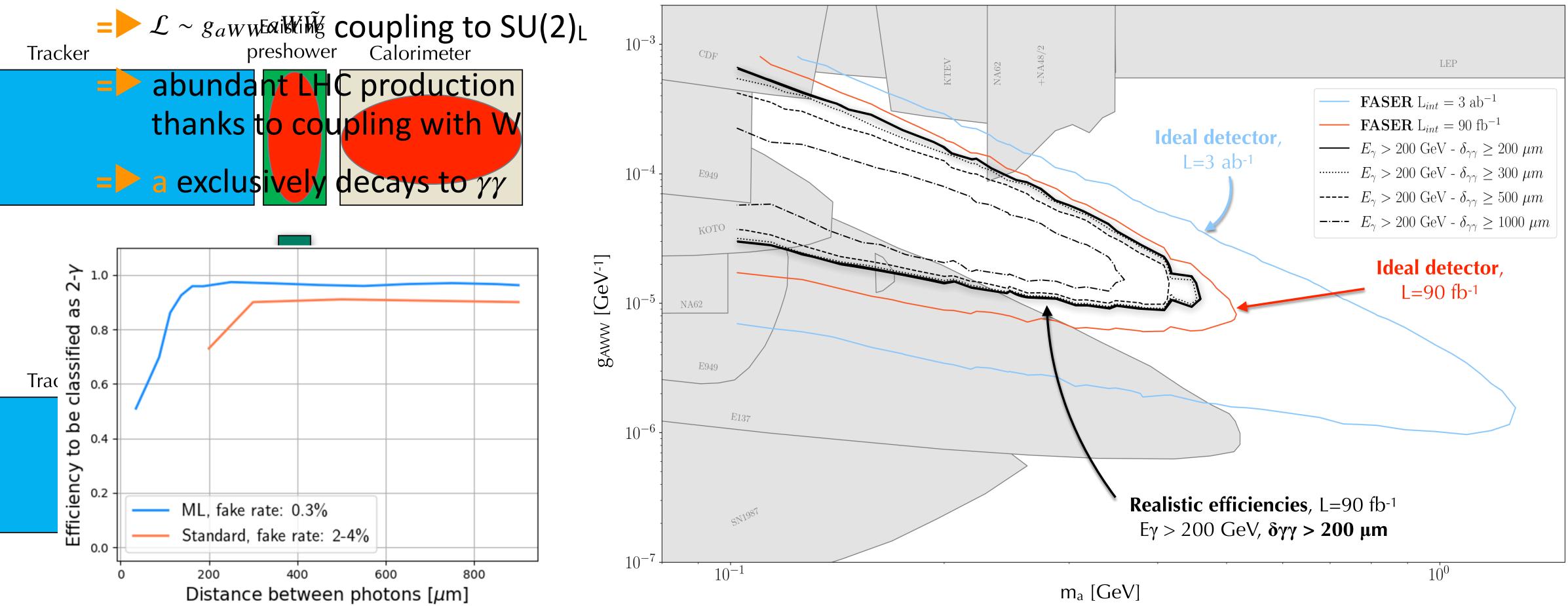

## Diphoton Signature: Sensitivity

### Impact of upgrader preshower evaluated for benchmark dark photon (a) model

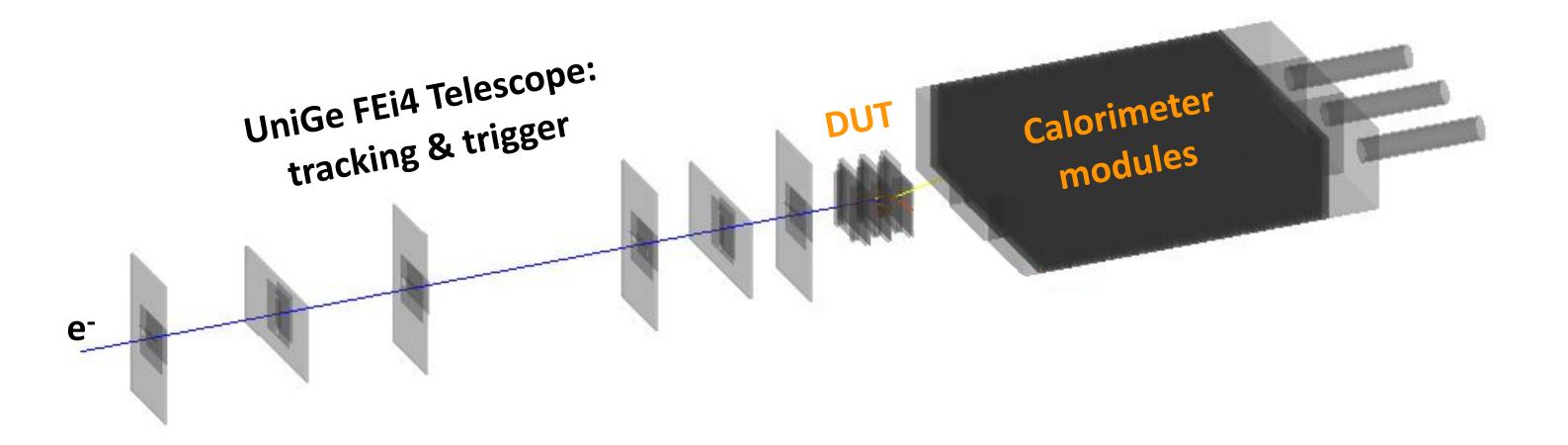

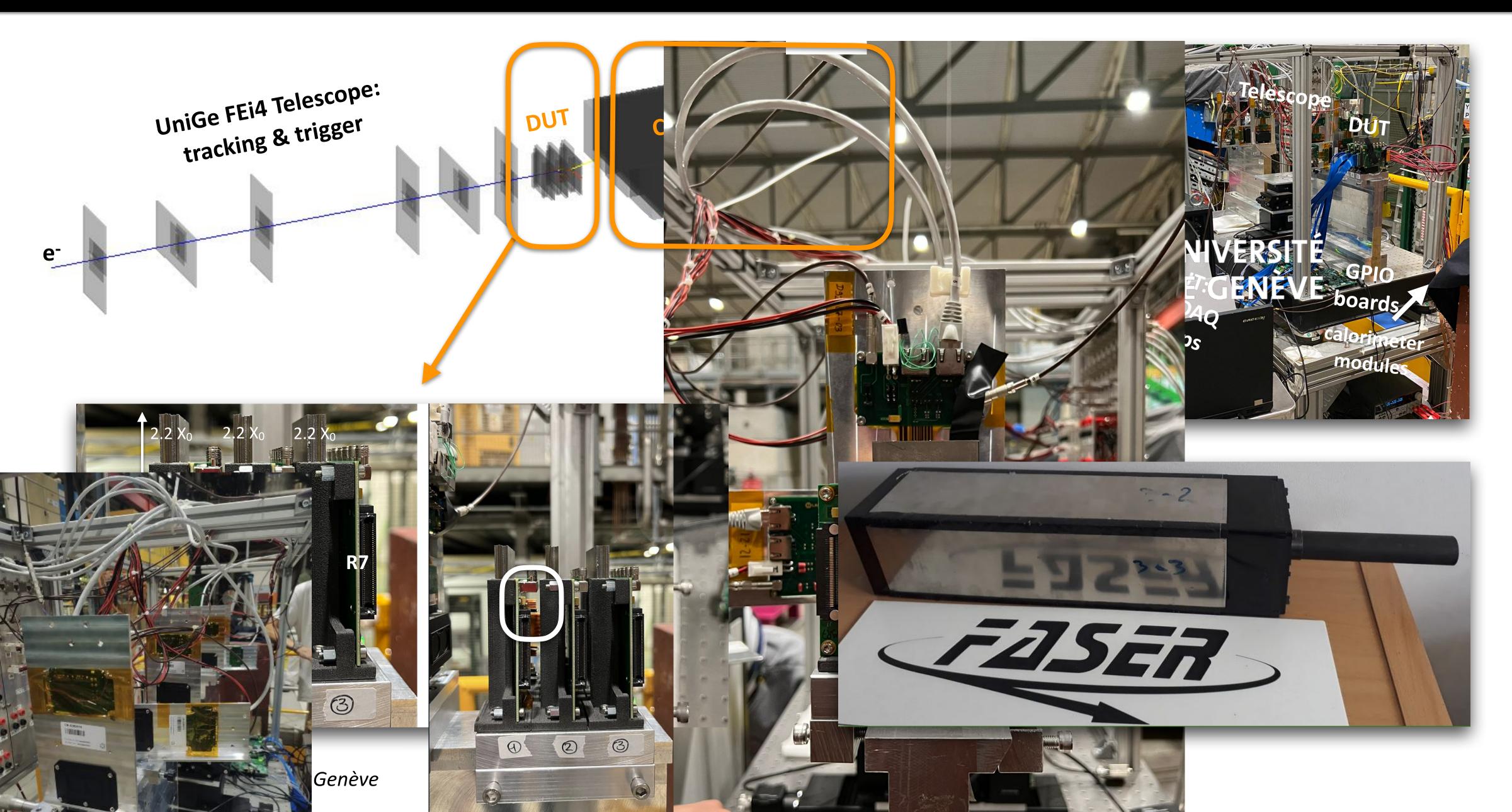

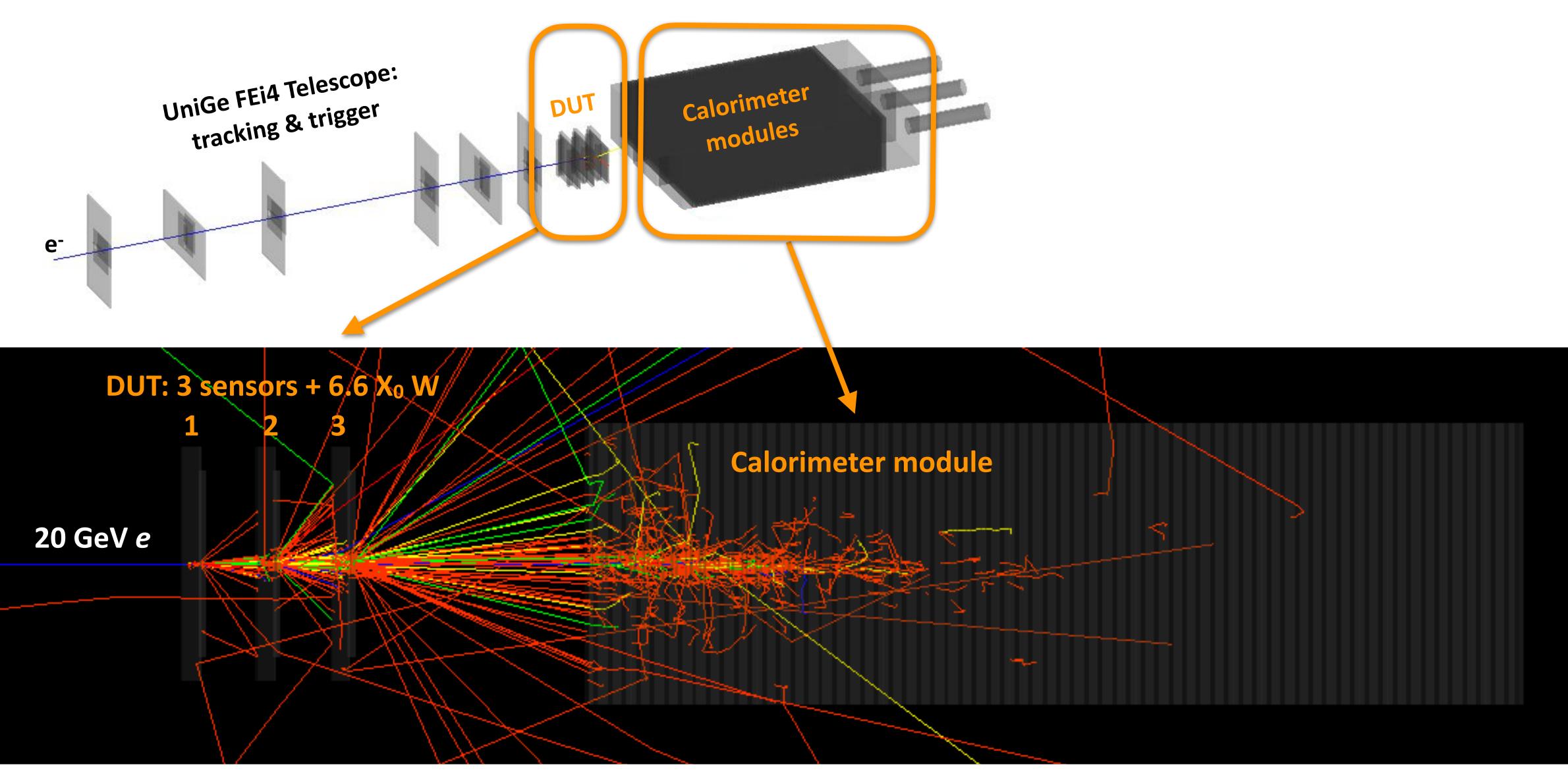

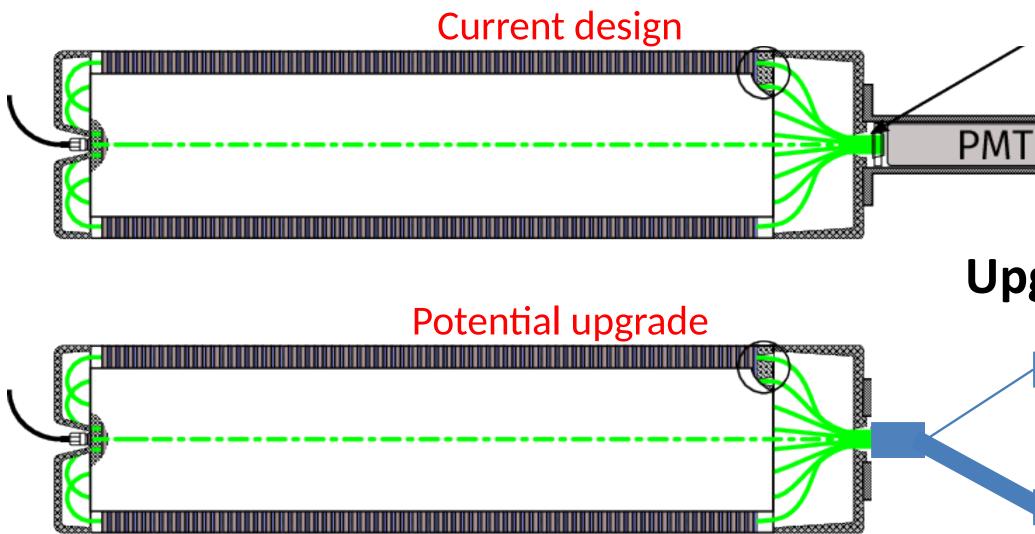

## Upgraded Calorimeter Readout Scheme

### Plan to upgrade the calorimeter readout scheme to improve range and energy scale

- Currently relying on single PMT, and optical filter to reduce light output by factor 10

- → Calibrations: MIP data (high PMT gain) extrapolated to low gain with LED-determined gain ratio

- => Upgrade: use two separate PMTs to cover low E (high gain) and high E (low gain) at same time

**Stefano Zambito** | *Université de Genève*

Light output reduced by *optical filter,* otherwise too large signal at TeV scale

### Upgrade: same PMT type, but operated at medium gain

PMT1

High energy range PMT: 3-3000 GeV

### PMT 2 Low energy range PMT: 0.1-300 GeV

$\Rightarrow$  3-300 GeV overlap region for cross-calibrations

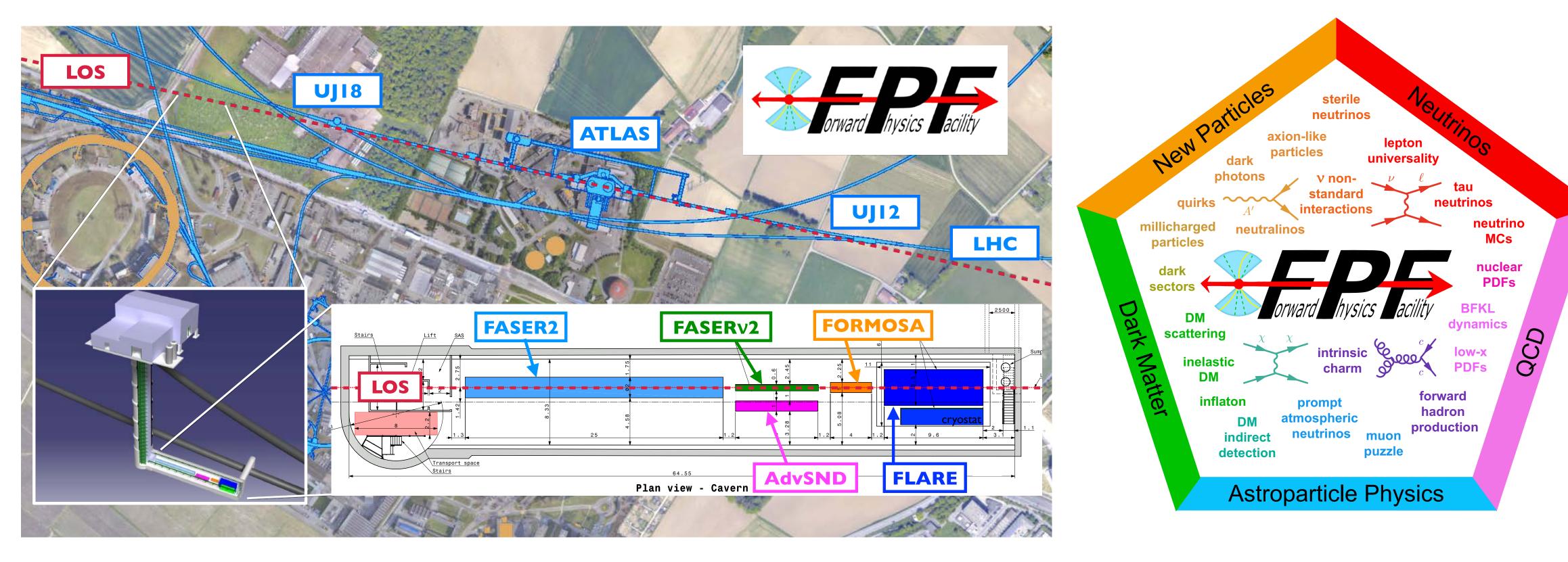

## Proposal [Link]: Forward Physics Facility at the LHC

## FASER 2 upgrade proposed in the context of a broader Forward Physics Facility (FPF)

65 m long and 9 m wide cavern, 617-682 m west of ATLAS IP, on beam collision axis = =

**Stefano Zambito** | *Université de Genève*

Besides FASER2 and FASERv2, may host several other experiments: FORMOSA, AdvSND, FLArE, ...

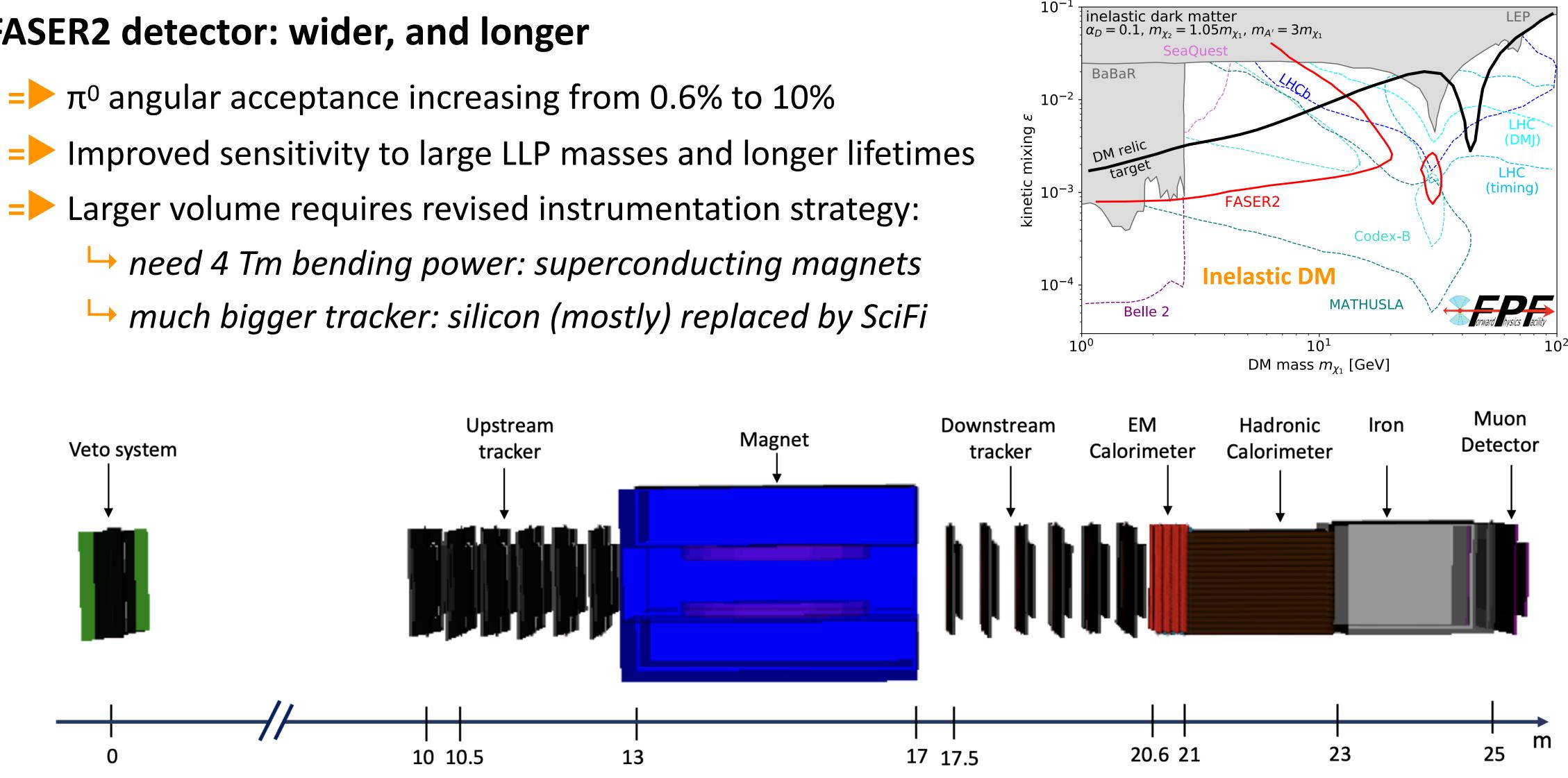

## FASER2 And FASERv2

### **FASER2** detector: wider, and longer

**Stefano Zambito** | *Université de Genève*

## FASER2 And FASERv2

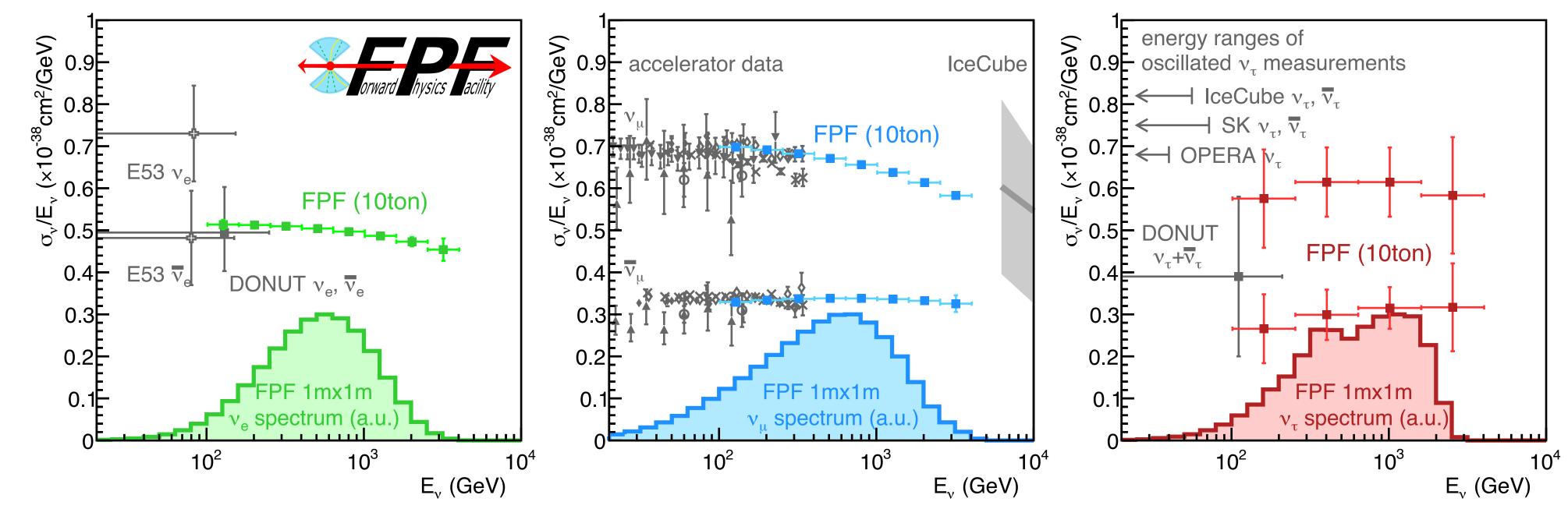

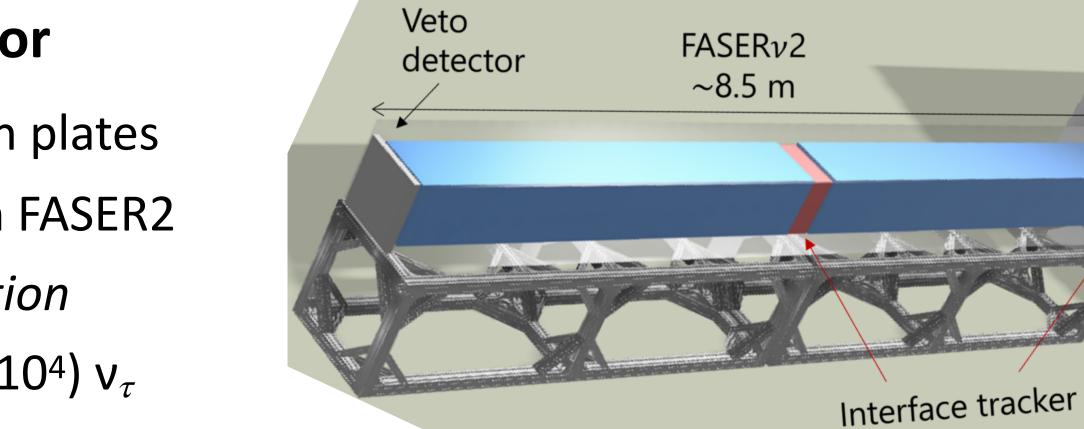

### FASERv2: 20-ton emulsion-based v detector

> 3300 AgBr layers interleaved with tungsten plates

> veto + two tracker planes to interface with FASER2

→ μ charge, and global event reconstruction

= for HL-LHC, expect: O(10<sup>6</sup>) v<sub>µ</sub>, O(10<sup>5</sup>) v<sub>e</sub>, O(10<sup>4</sup>) v<sub>τ</sub>

## Summary & Outlook

### **Empowering FASER's capabilities with several upgrades...**

New preshower will enable multi- $\gamma$  tagging and greatly increase dark photon searches' reach Detector layout and mechanics design converged; pre-production ASIC extensively tested Final chip design just submitted to foundry: targeting preshower installation in 2024 Calorimeter readout scheme upgrade: extended range and improved energy scale Further upgrades proposed in the context of a broader Forward Physics Facility → Wider and longer FASER2 detector to tackle larger LLP masses and longer lifetimes Bigger and more complex FASERv2 system to expand neutrino physics program

## Summary & Outlook

### **Empowering FASER's capabilities with several upgrades...**

New preshower will enable multi- $\gamma$  tagging and greatly increase dark photon searches' reach Detector layout and mechanics design converged; pre-production ASIC extensively tested Final chip design just submitted to foundry: targeting preshower installation in 2024 **Calorimeter readout scheme upgrade: extended range and improved energy scale** Further upgrades proposed in the context of a broader Forward Physics Facility → Wider and longer FASER2 detector to tackle larger LLP masses and longer lifetimes Bigger and more complex FASERv2 system to expand neutrino physics program

## ... Many years of exciting physics ahead of us!

## Spares

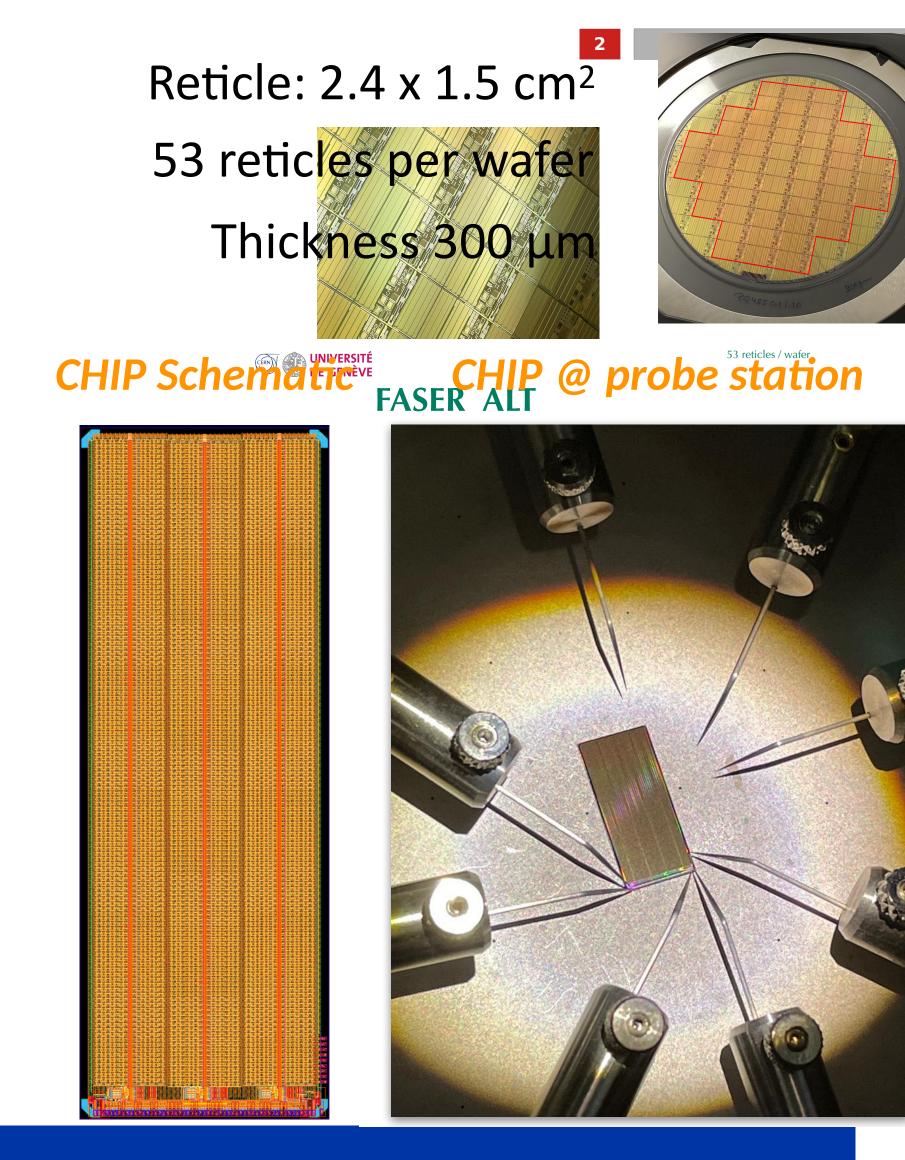

## Pre-production AS

\_MAIN

[nA]

## Wafers received in Jun 2022, tested in laboratory

I-V characteristics measured at probe station

Charge response scrutinised with <sup>109</sup>Cd and IR laser

Stress-tests for digital electronics and readout

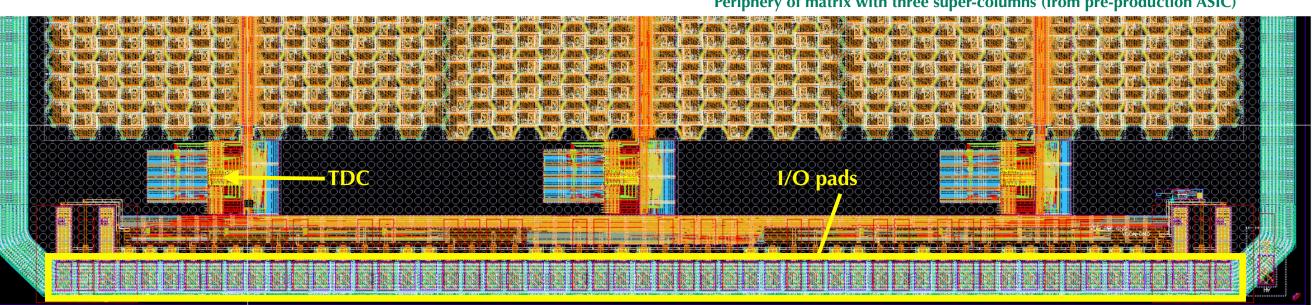

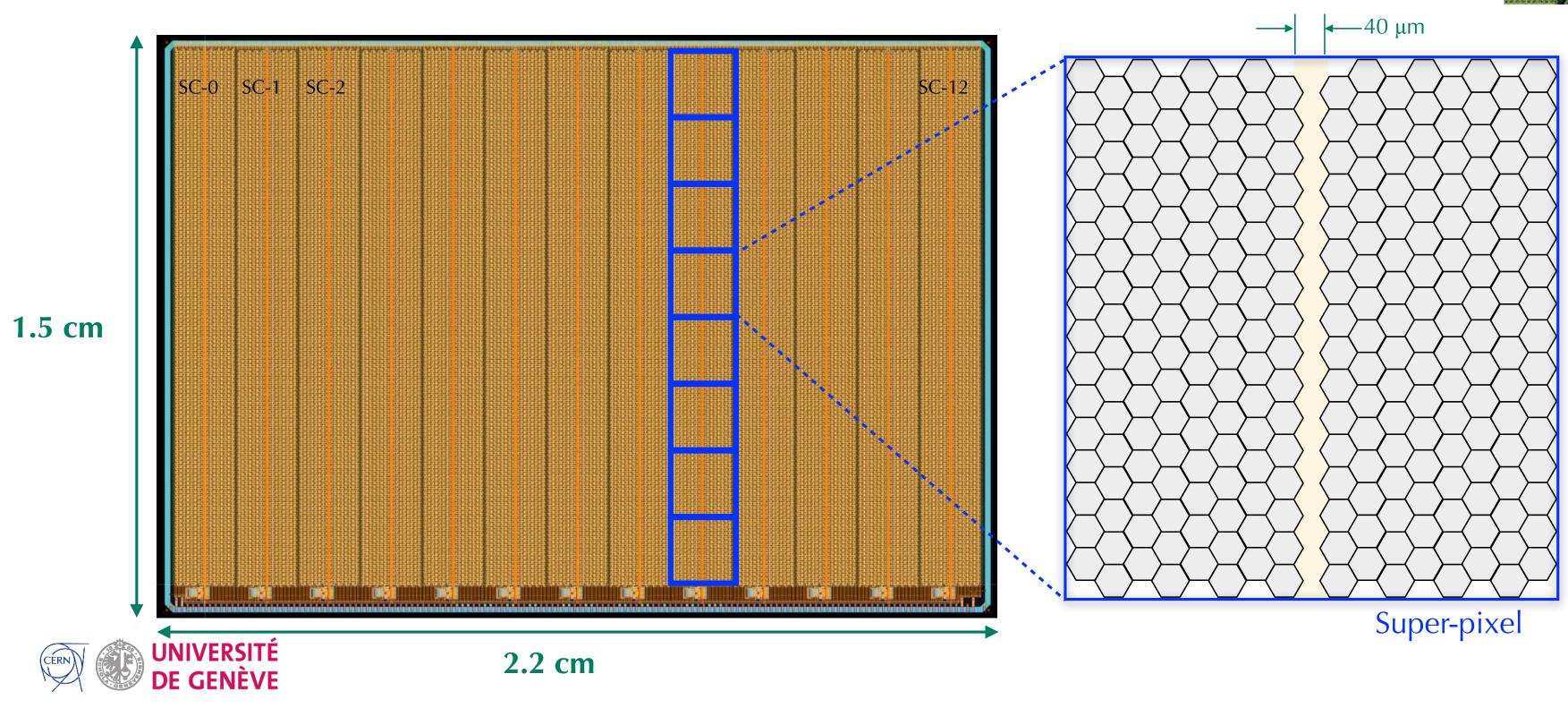

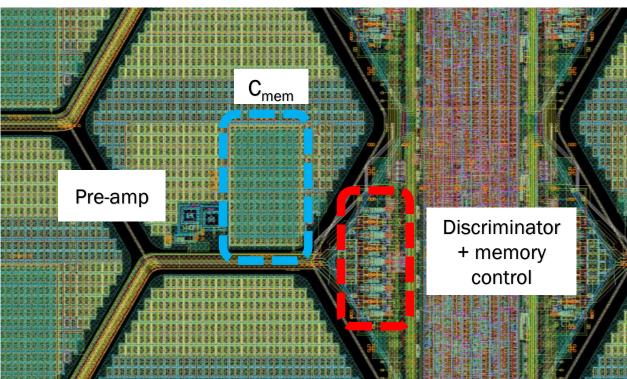

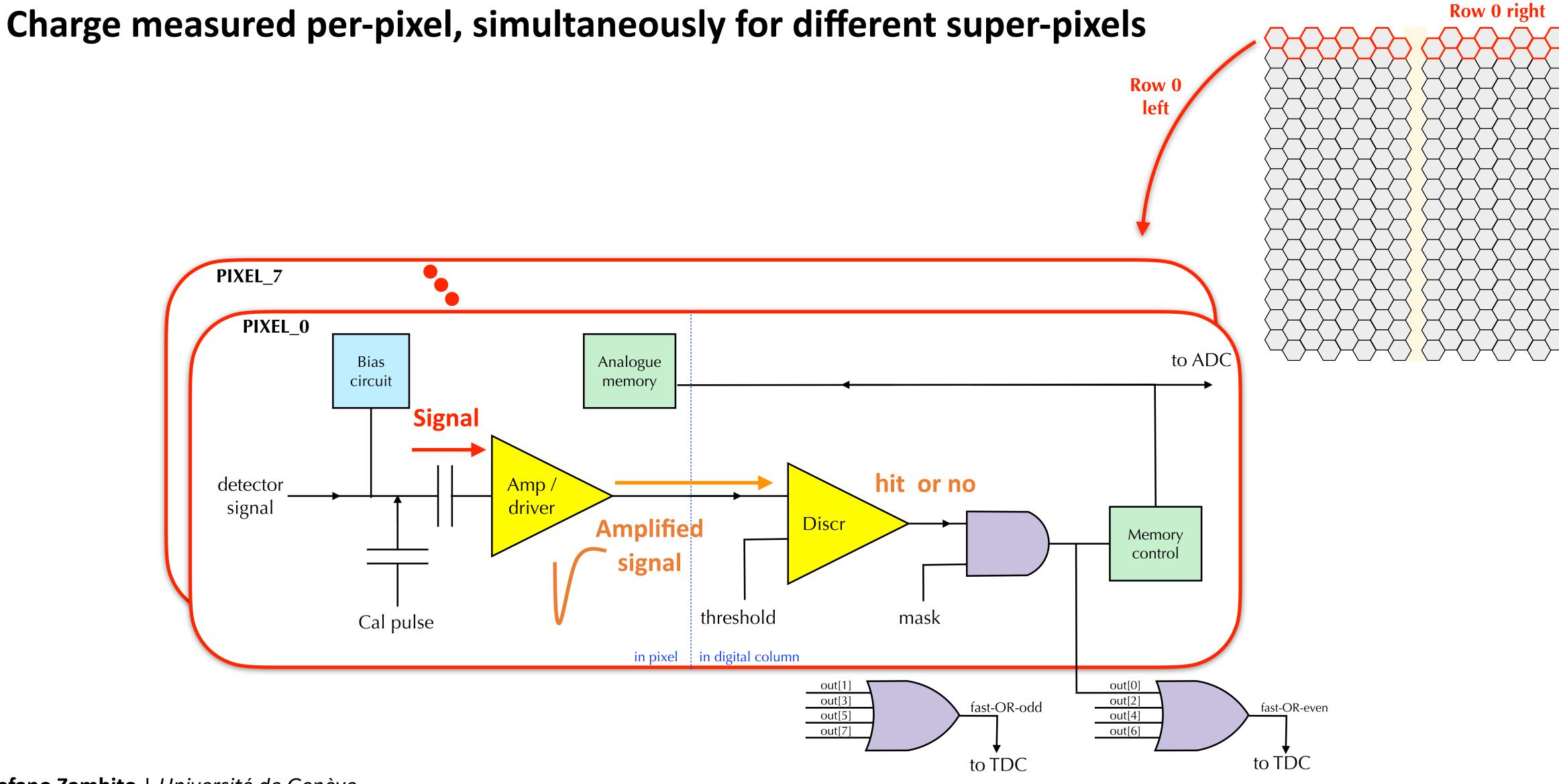

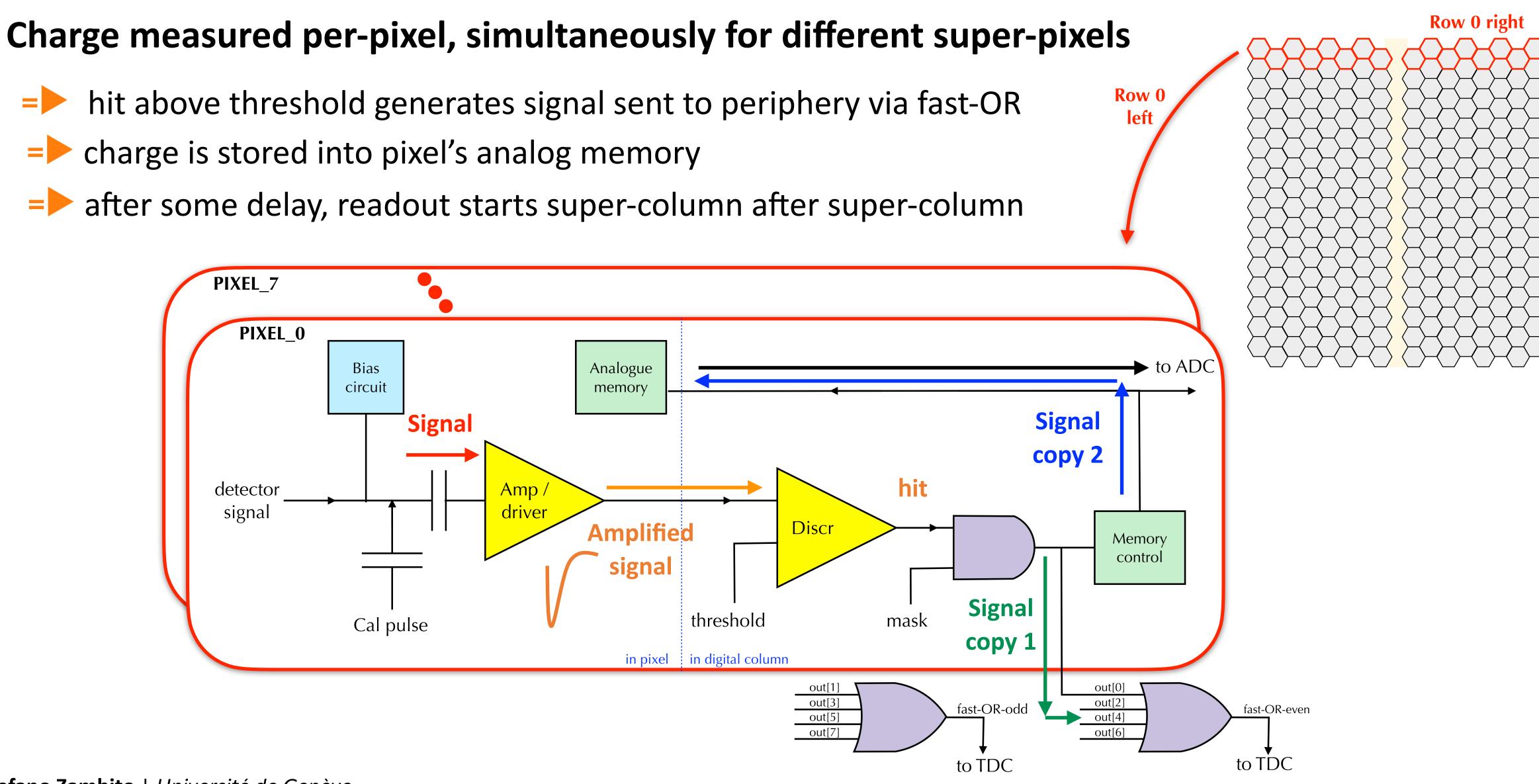

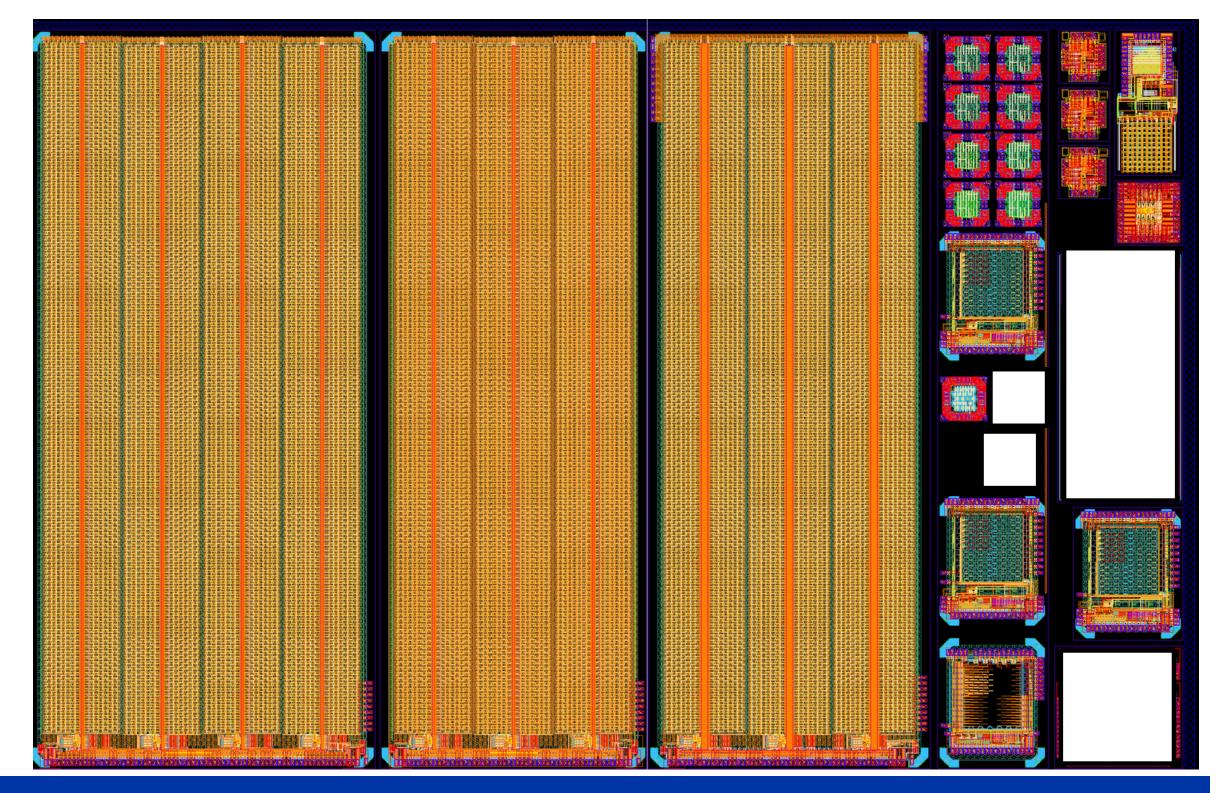

## Monolithic Pixel ASIC: Chip Structure

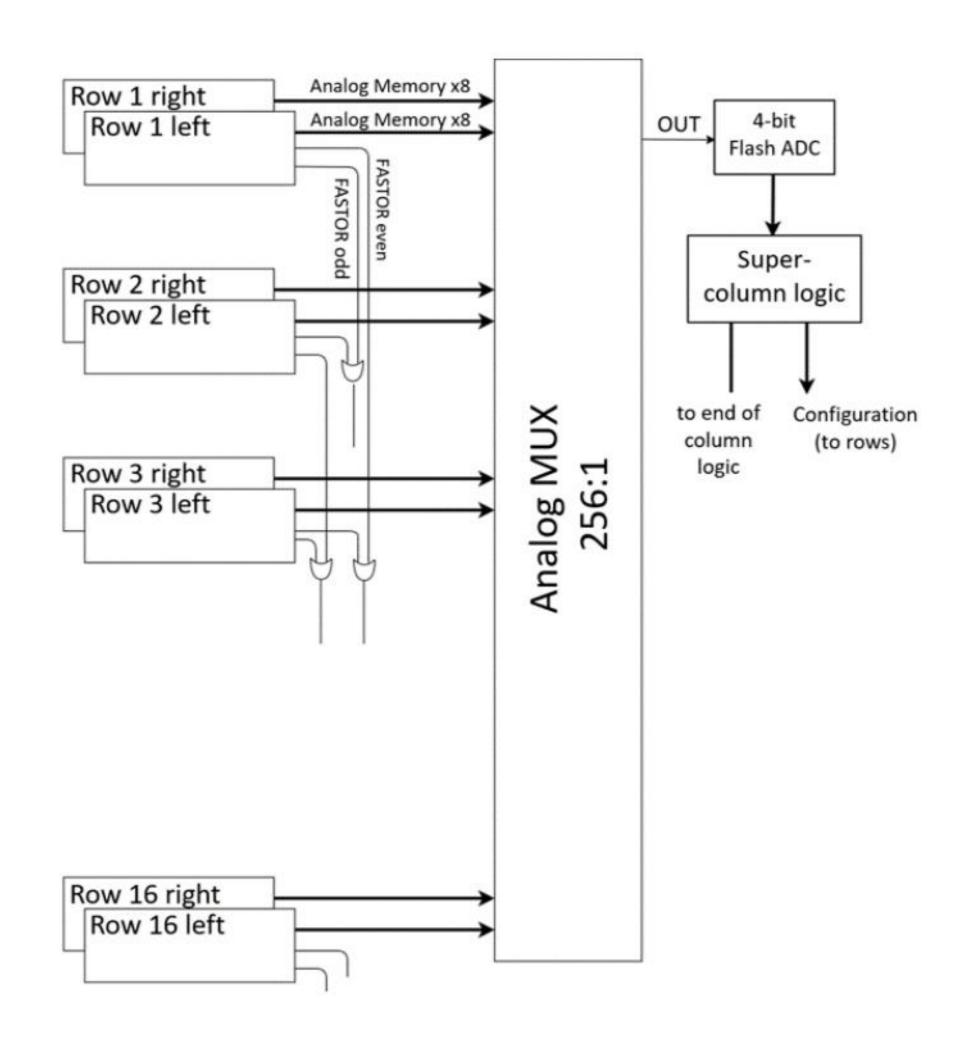

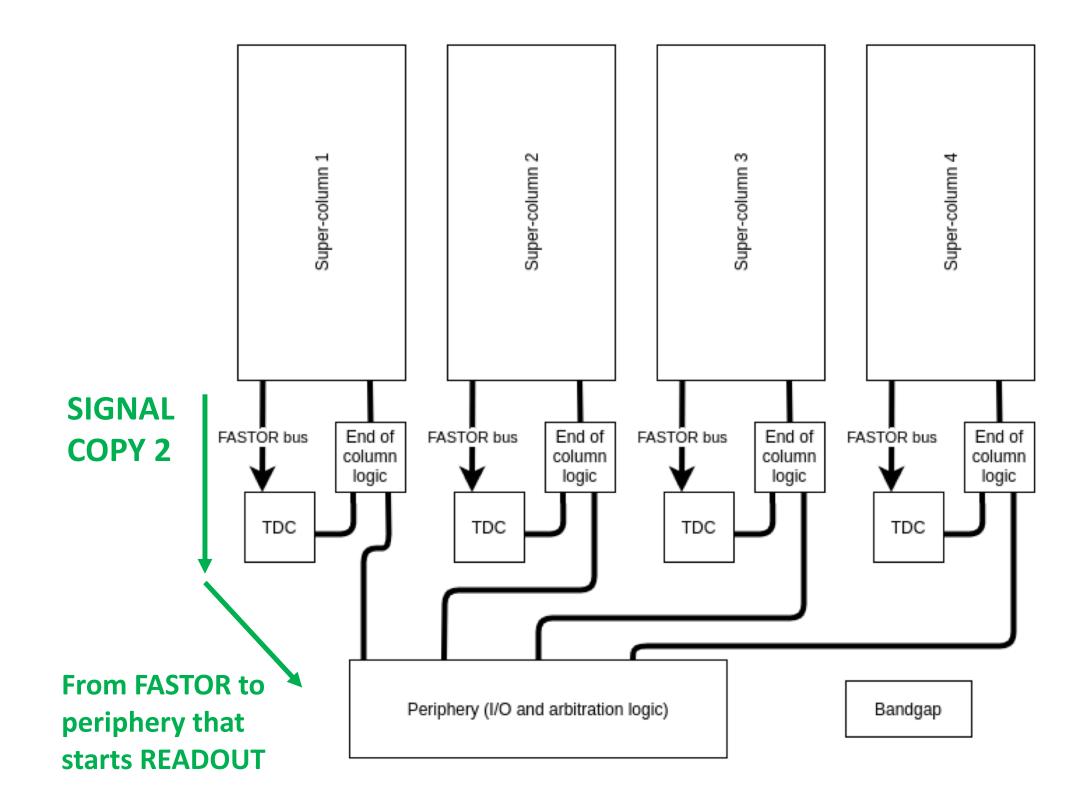

## Chip organized in 13 "super-columns", each with:

- active region, subdivided into 8 "super-pixels" of 16x16 pixel each

### Digital periphery on the bottom, and multiple guard-ring structure

**Stefano Zambito** | *Université de Genève*

digital column (40 μm) in the middle: sharing of digital electronics

### Super pix

- $\rightarrow$  16 rows of 8+8 pixels

- → analog multiplexer

- → 4-Biteflash ADC ge

- → 3 fastet @Rzlines

- → localabiatsificuit

- programming logic to mask pixels Time resolution

Dead area <5%

=

= =

- =

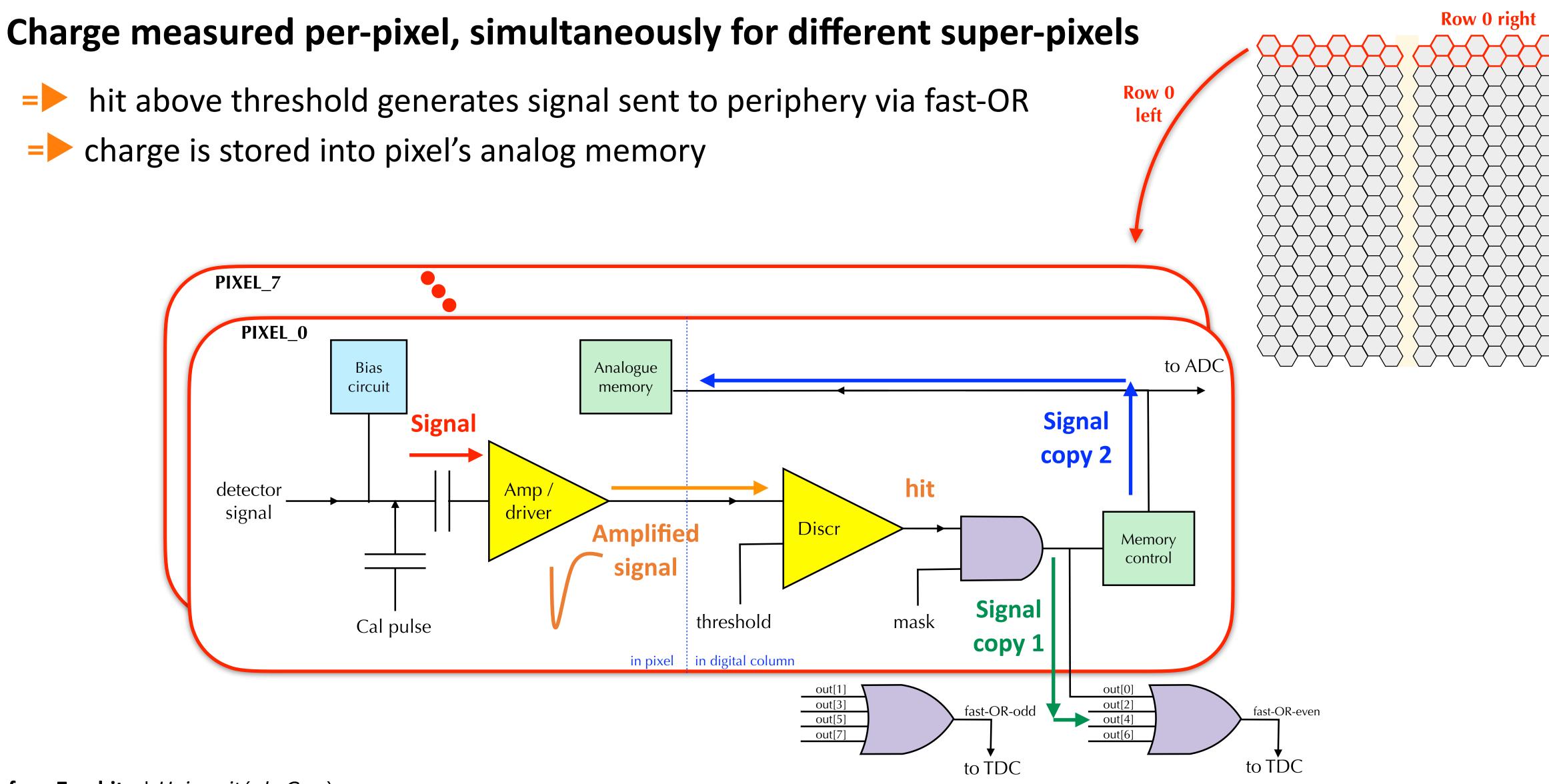

- charge is stored into pixel's analog memory

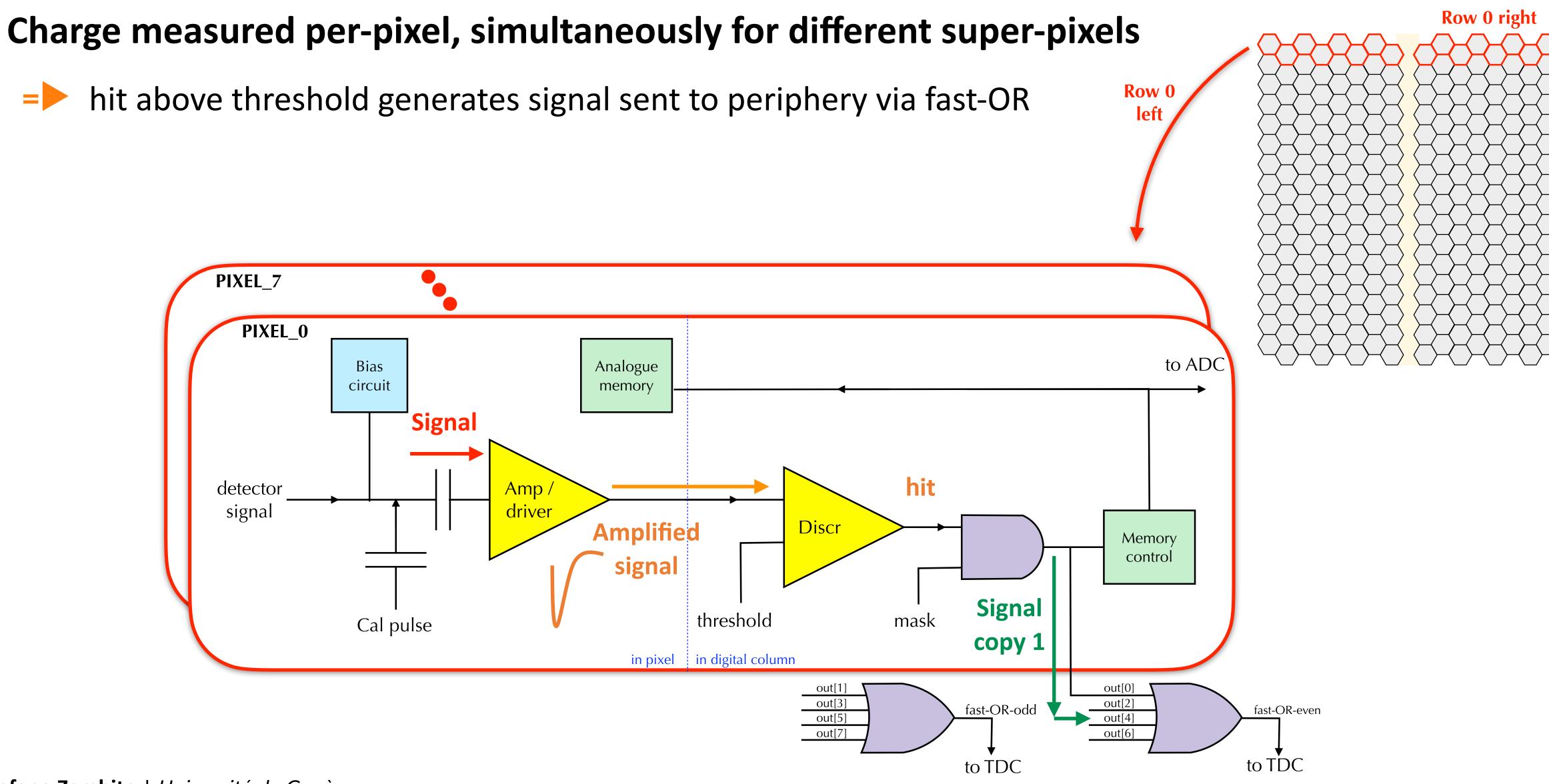

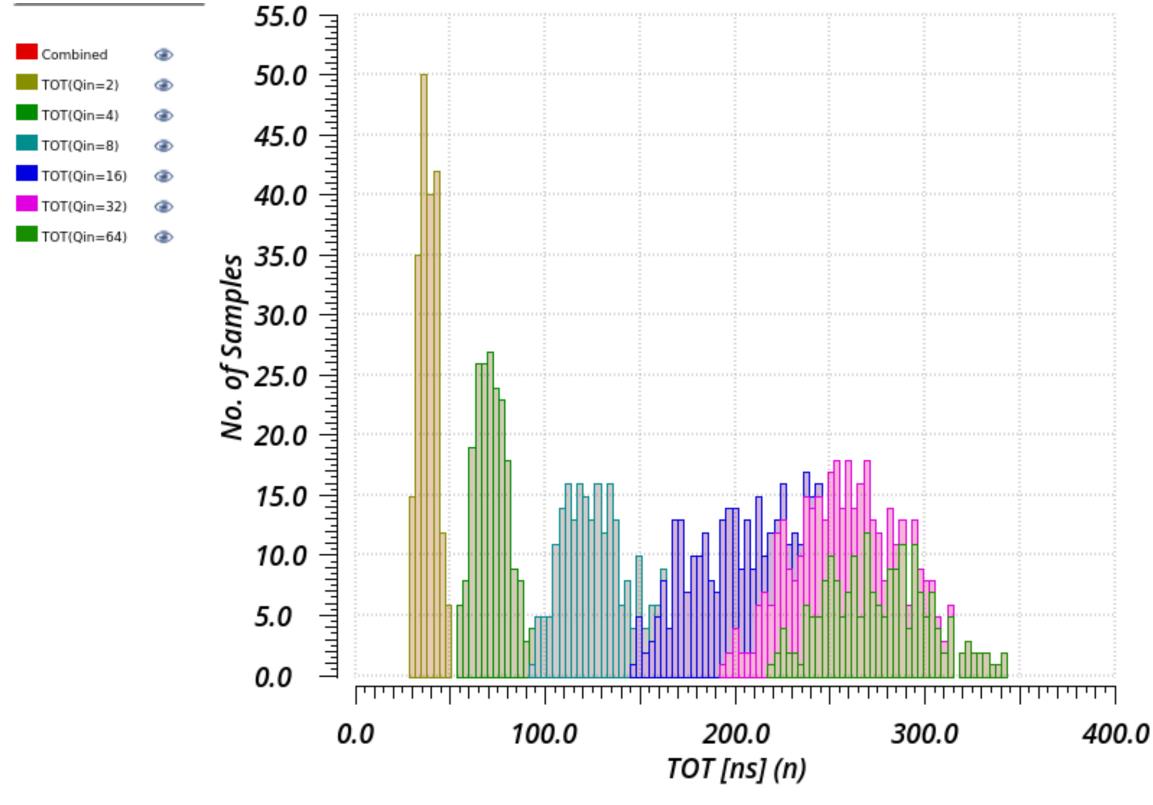

## Monolithic Pixel ASIC: Charge Measurement

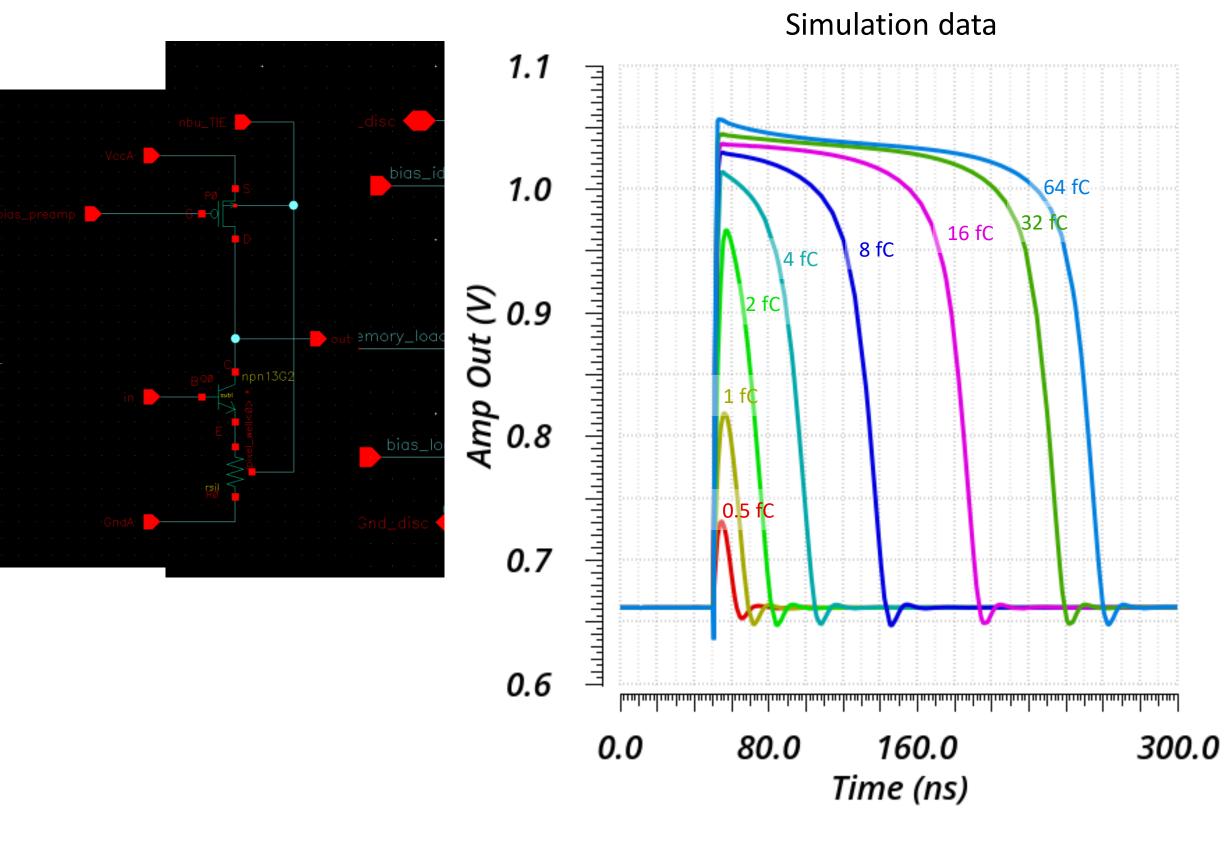

## Analog memories: capacitors inside each pixel charged with const current during ToT

when signal returns below threshold, memory is disconnected and left floating until read by flash ADC = preamplifier designed to produce a signal proportional to the *log* of input charge

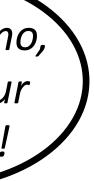

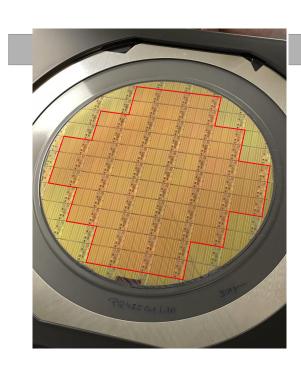

# Pre-production Chip (2022)

## **Engineering run (IHP Microelectronics)**

In each reticle, three pixel matrices

FASER\_v1 (baseline)

- → 128 x 64 pixels, 4 super-columns

- → in-pixel pre-amp and driver

- └→ discriminator outside

### FASER\_v2

- → 128 x 48 pixels, 3 super-columns

- → in-pixel pre-amp, driver, and discriminator

### FASER\_ALT

- → 128 x 48 pixels, 3 super-columns

- → no analog memories

- → counter for charge measurement

- Several test structures (TDC, etc...)

### Reticle: 2.4 x 1.5 cm<sup>2</sup>

53 reticles per wafer

Thickness 300 µm

### FASER\_v2

### FASER DE GENÈVE FASER ALT

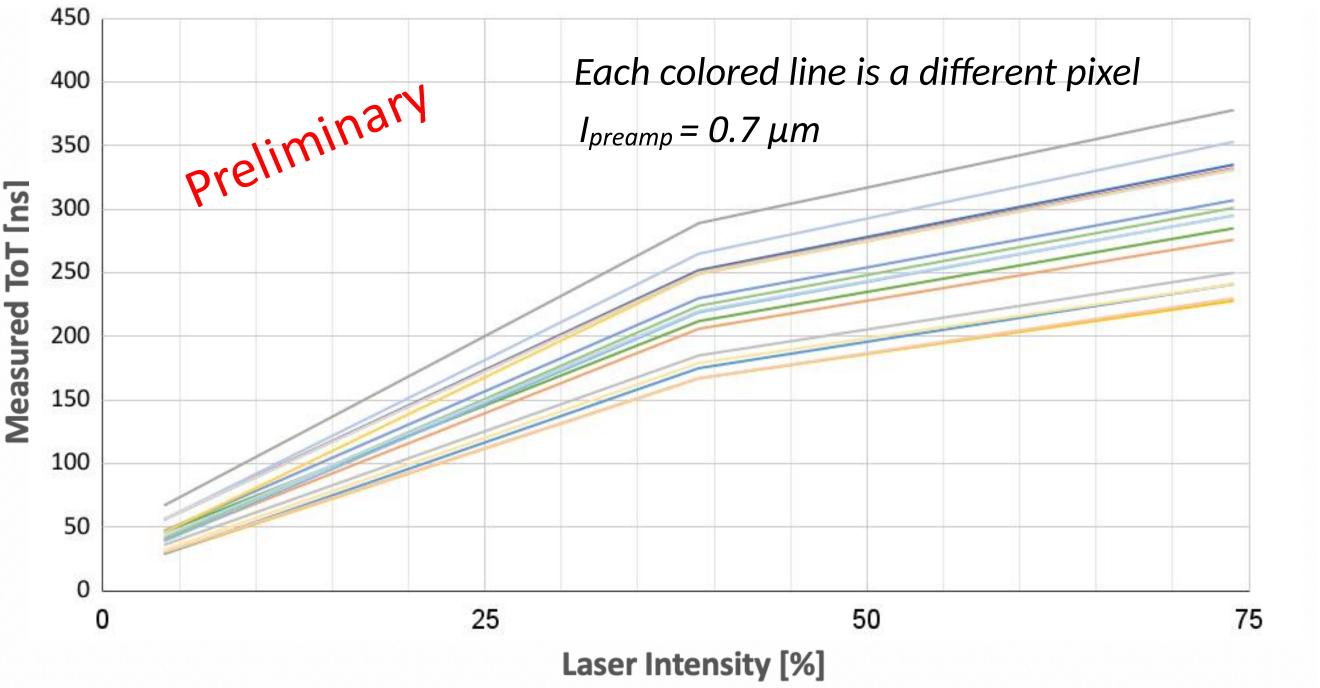

# Pre-production Chip: TOT (Charge) Mismatch [I]

### **Stefano Zambito** | *Université de Genève*

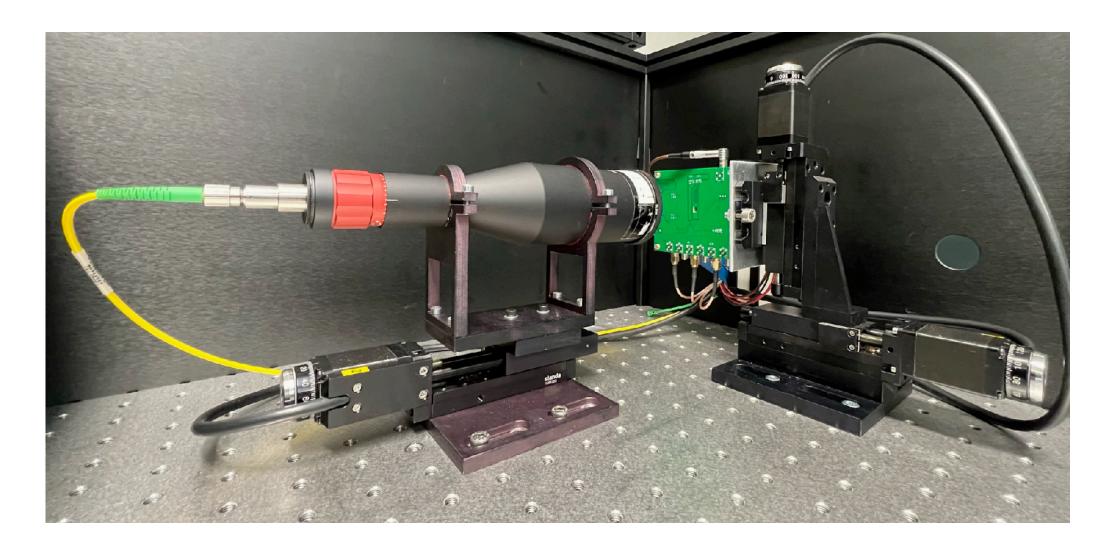

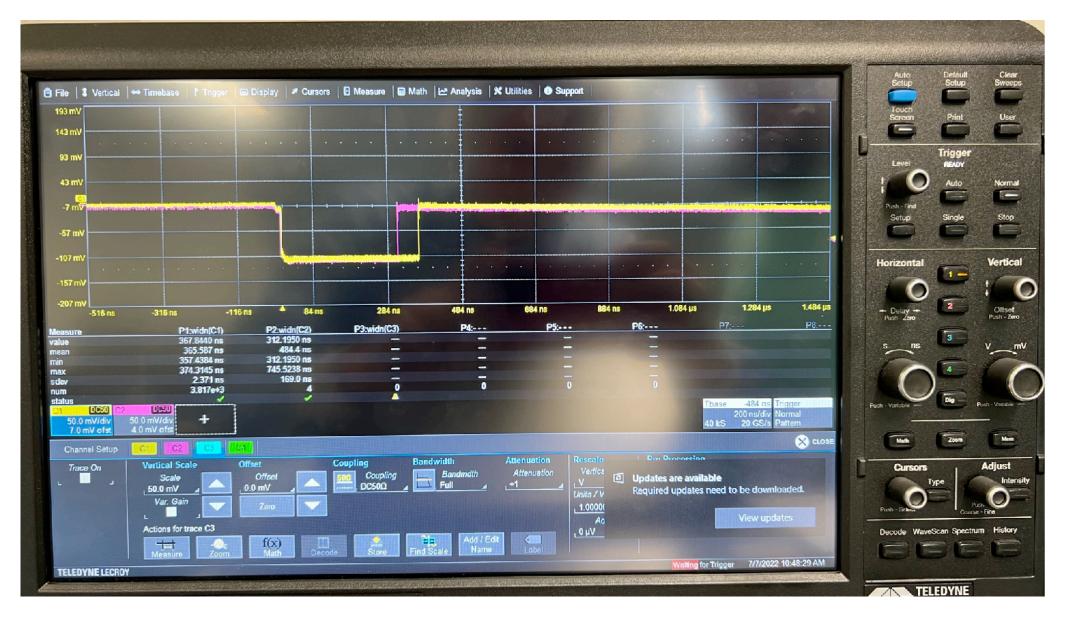

## **Evaluating charge response with infrared laser**

- measuring ToT via fast-OR signal on the scope =

- varying per-pixel injected charge via laser attenuator

- measurement repeated at different *I*<sub>preamp</sub> =

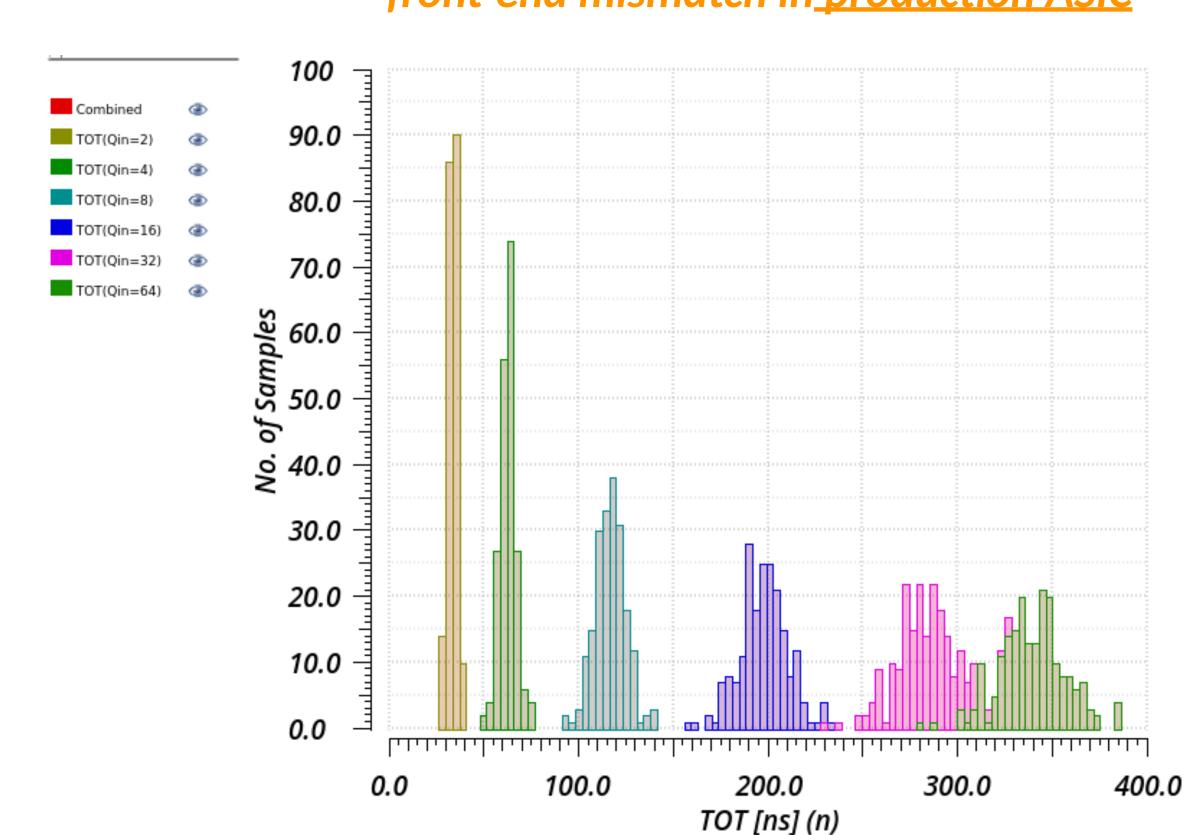

## Pre-production Chip: TOT (Charge) Mismatch [II]

## Expect improvement of front-end uniformity in production ASIC thanks to bigger transistors

**Cadence Spectre Simulation:**

front-end mismatch in <u>pre-reduction prototype</u>

**Stefano Zambito** | *Université de Genève*

### **Cadence Spectre Simulation:**

### front-end mismatch in production ASIC

**Stefano Zambito** | *Université de*

All front-end system in Pixel Driver in Pixel, discriminator outside

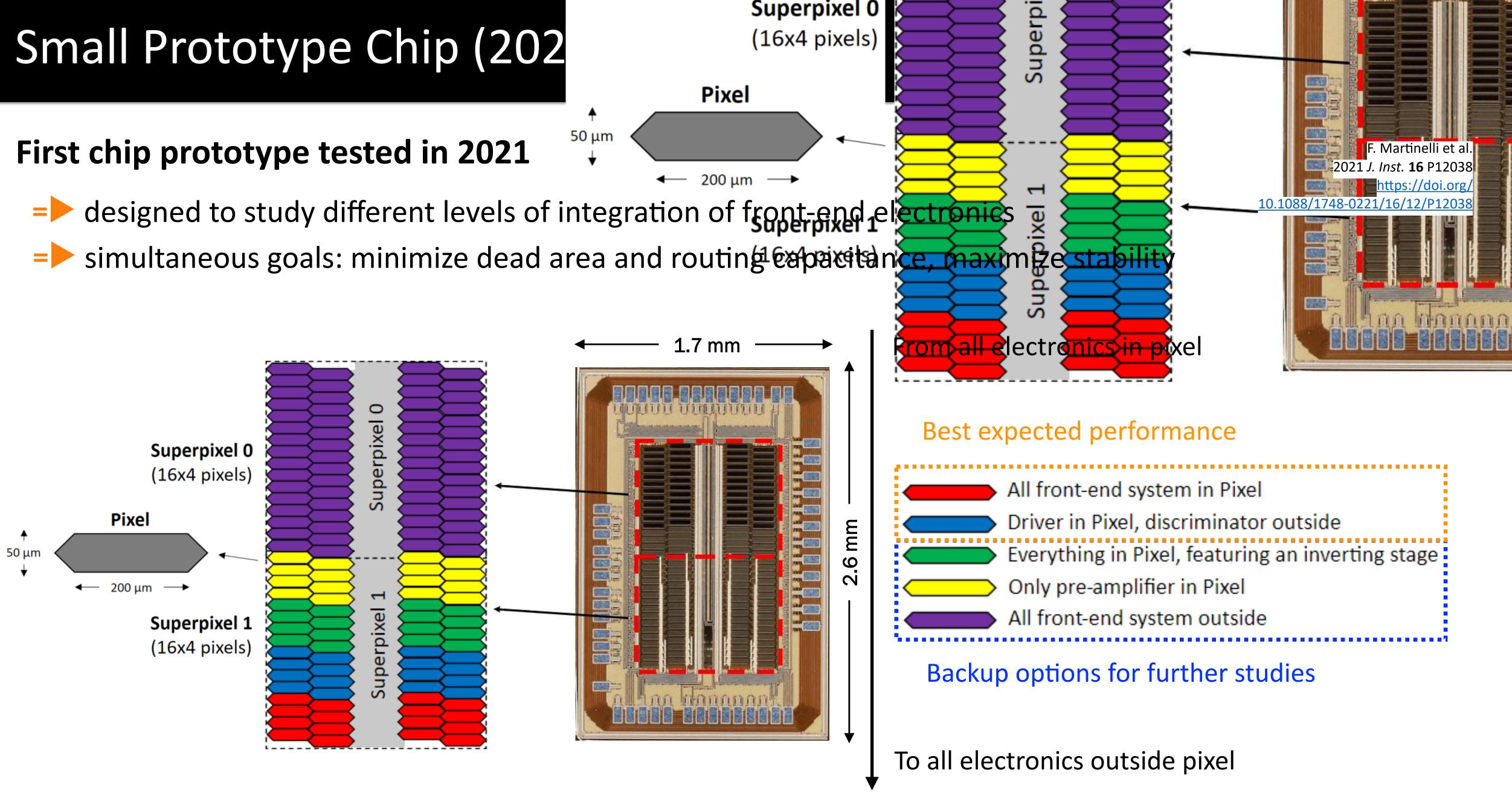

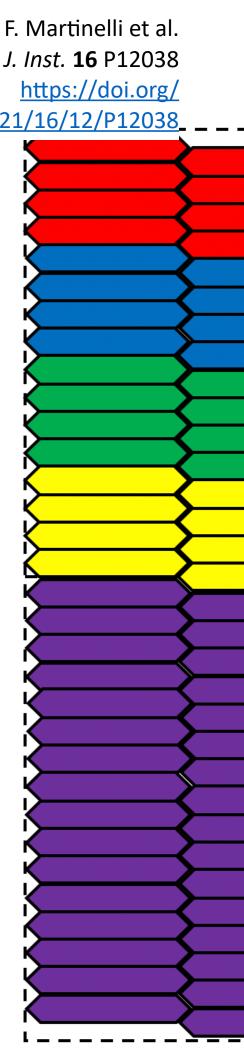

# Small Prototype Chip (2021)

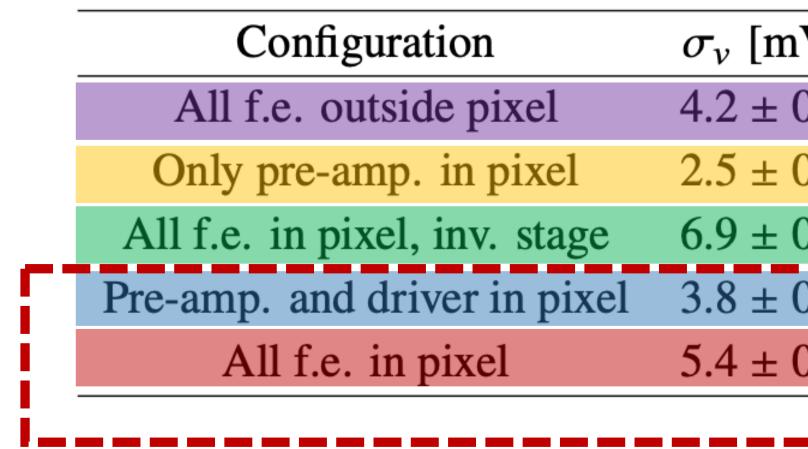

### First chip prototype tested in 2021

designed to study different levels of integration of front-end electronics = simultaneous goals: minimize dead area and routing capacitance, maximize stability =

Last two configurations are good compromise between *compactness* and *performance*: adopted for pre-production prototype

**Stefano Zambito** | *Université de Genève*

2021 J. Inst. 16 P12038 10.1088/1748-0221/16/12/P12038

|     |                 |                              |                        | _ |

|-----|-----------------|------------------------------|------------------------|---|

| V]  | $G_c$ [mV/fC]   | <i>ENC</i> [e <sup>-</sup> ] | $\sigma_{V_{th}}$ [mV] | _ |

| 0.2 | $159 \pm 1.0$   | $165 \pm 9$                  | 32.3                   | - |

| 0.1 | $96.8 \pm 0.5$  | 161 ± 9                      | 26.9                   |   |

| 0.5 | $179 \pm 1.0$   | $241 \pm 19$                 | 30.8                   |   |

| 0.2 | $133.7 \pm 0.6$ | 178 ± 9                      | 23.4                   |   |

| 0.4 | $148 \pm 1.0$   | $228 \pm 20$                 | 27.1                   |   |

|     |                 |                              |                        | - |

### GENE Monolithic Pixel ASIC: Charge Digitization & Readout

**Stefano Zambito** | *Université de Genève*

### Periphery of matrix with three super-columns (from pre-production ASIC)