### **GOLD** status

B.Bauss, V.Büscher, R.Degele, A.Ebling, W.Ji, C.Meyer, S.Moritz, U.Schäfer, C.Schröder, <u>E.Simioni</u>, S.Tapprogge

### OUTLINE

- L1 CALO Upgrade

- Generic Opto Link Demonstrator "GOLD" status

- Trigger Topological cuts (simulation)

- Data Format

- Summary

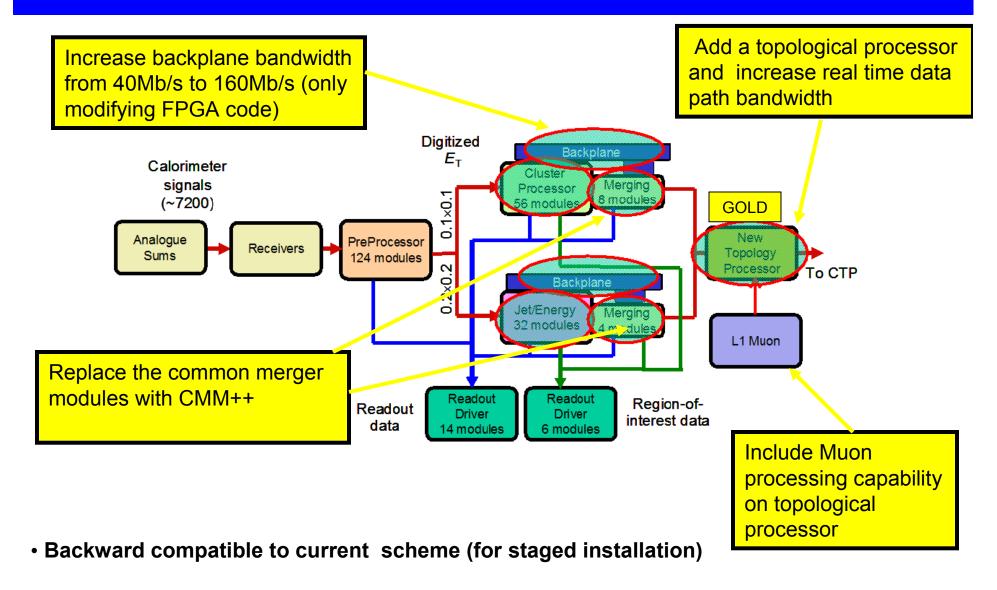

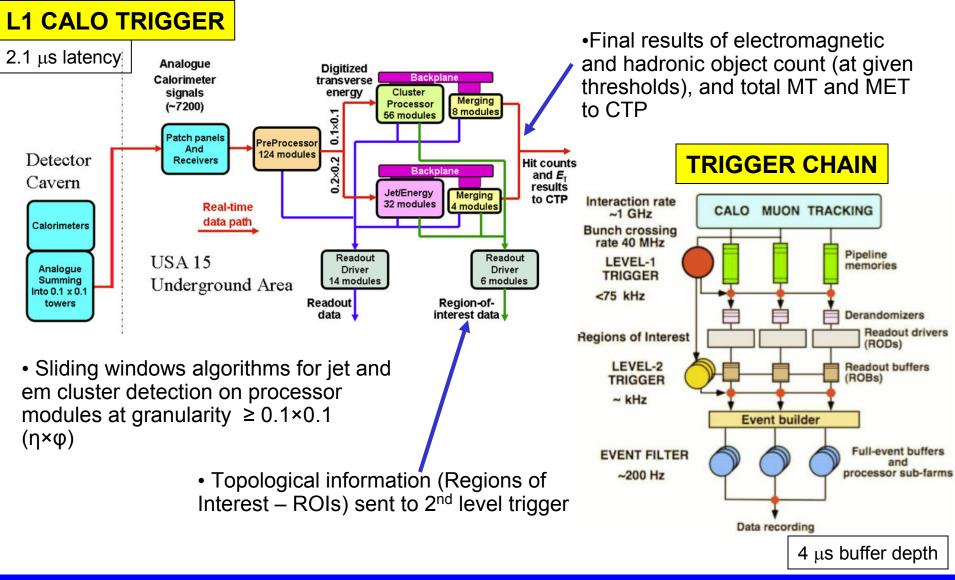

## **Upgrade of L1 Calo**

#### • Use of Rols into the real time data path at L1 and apply topology cuts

- fix spatial overlap between e/tau clusters and jets

- local Et jet sum to estimate the energy overlap of e and tau

- muon isolation

- physics signatures

- angular correlation of jets

- etc...

- Transmit full ROIs information will require additional bandwidth

- System density will rule out additional electrical cabling

- Latency might get critical

- Go for optical connections

- Increase system density by use of FPGA-internal Multi-Gigabit Transceivers

- Optimize the data replication scheme

- Explore options for latency reduction on the FPGA (about extra 2BX per MGT)

#### Latency optimization

- Data replication schemes

- FPGA on-chip MGT operation modes and fabric interfaces

### **Upgrade of L1 Calo trigger**

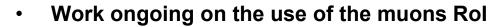

### **TP performance in simulation**

- Identify trigger processes which benefit from topological trigger

- Simulation of physics processes at 1x10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> and 3x10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>

- $\Delta \phi$  in Jet + MET at 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> (QCD bkg reduction)

- Leading jets Rol at  $\pi$

- MET aligned to one Jet Rol

- Tagging b-jets (for muons at high pt)

- MET from muon (match with Calo info)

- Use of transverse mass cuts at L1

Study total Rate vs. ET, threshold of the 2nd Leading Jet-Rol for various windows size

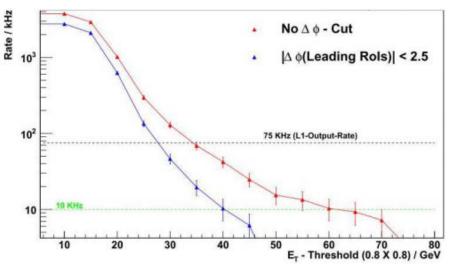

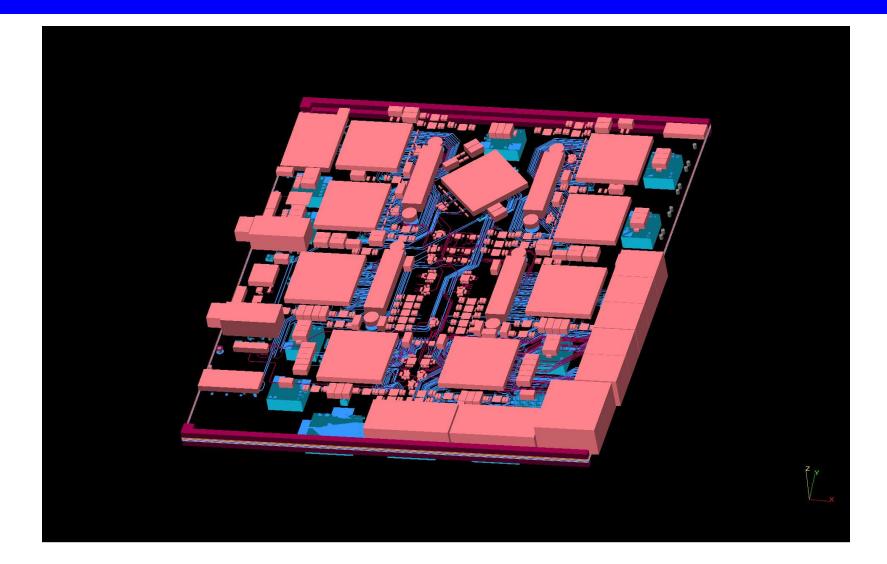

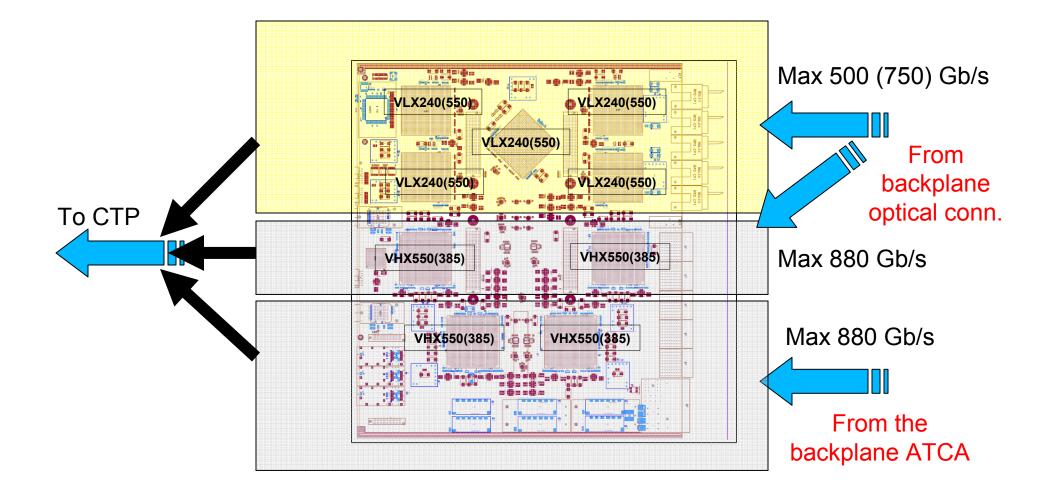

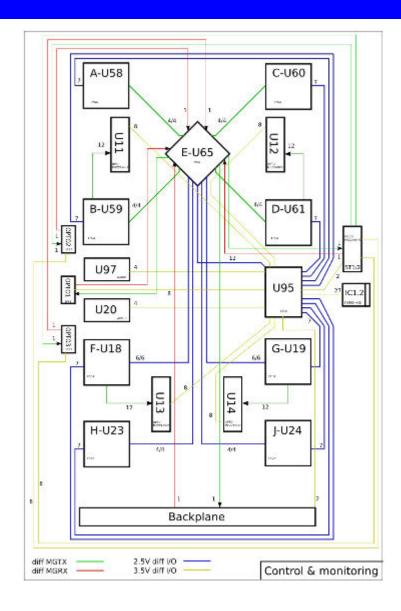

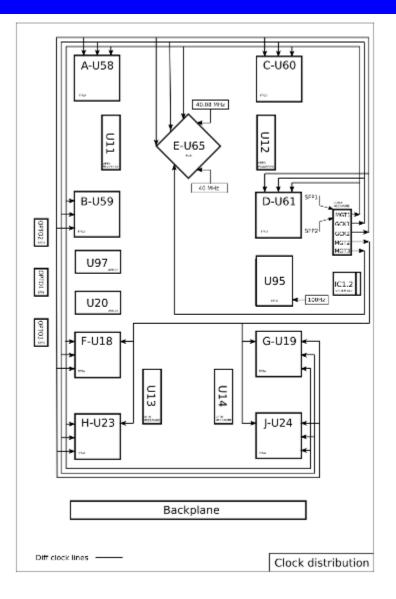

### **Design of a Generic Opto Link Demonstrator "GOLD"**

### **GOLD bandwidth capability**

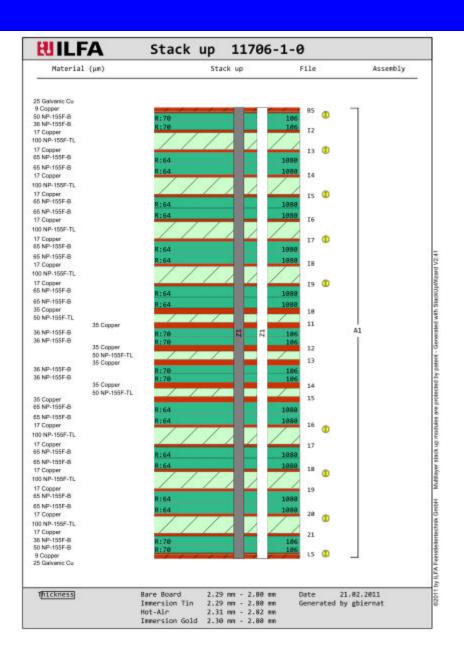

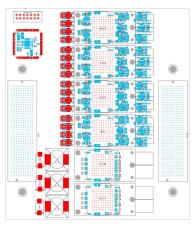

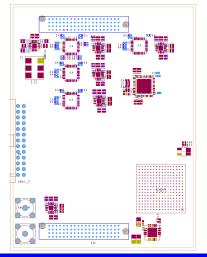

### **GOLD production status (I)**

#### GOLD board design conceptually completed, waiting for final review

- Check of the design library and the the components documentation (done)

- Production issue at the company: needed larger vias (done)

- Changed power regulators on the FPGA MGT (done)

- Mezzanines modules 100% routed, waiting for final review

- All components available

#### Plans for testing

- JTAG boundary scan (Goepel tool)

- Playback/spy tests through BLT

- (parity, test vectors)

- GTX/H characterization

- eye diagrams

- bit rate error (IBERT tool)

- Electric tests: cross-talk, reflections, jitter etc...

## **GOLD production status (II)**

#### • Firmware

- Starting GOLD top design

- MGT in low latency mode

- tested the MGT(GTX) at the BLT with and without 8b/10b encoding and phasealignment up to 6.4 Gbps (low Latency)

- On Virtex6-VLX phase-alignment also successful (tested up to 5 Gb/s)

- For phase-alignment one clockbuffer needed per GTX

- (this can be a problem for the VHX)

- Implementation in VHDL of the  $\Delta \phi$  cut

- Sorting 2 leading jet according to the Energy information

- Reconstruct  $(\eta, \phi)$  position and constrain  $\Delta \phi$  of the leading Jets

- Output 2 leading jet information (position bits + Threshold Bits + Energy Bits ...)

- More test firmware

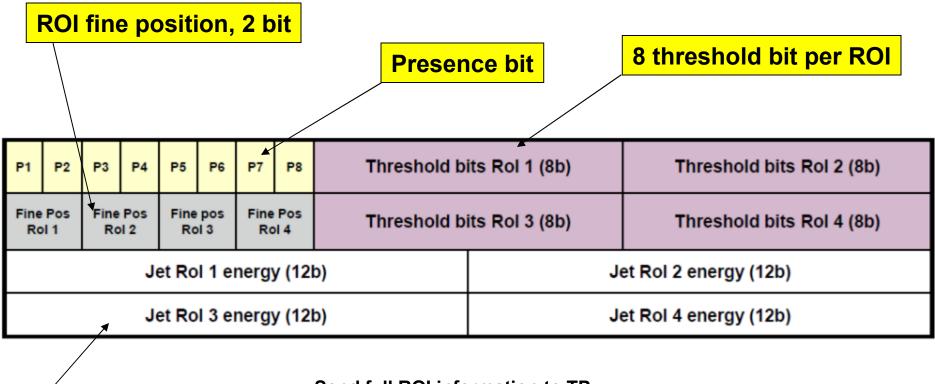

### Input data format (JEM preliminary)

Additional information per ROI, energy etc...

Send full ROI information to TP

- i.e, JEM: [96 bits/JEM] x [32 JEM] x [bx freq.] = 122.8 Gb/s

- CP (about four times JEM

- Muons ROI

ROI zero suppression and data reduction?

### Summary

- A Topological Processor is required to improve the L1 trigger algorithms at higher lumi

- Explore FPGA built in high-speed opto-link (high bandwidth)

- Low latency dense optical interconnection

- The production of the GOLD prototype about to get started (spring 2011)

- many problems fixed

- review still pending

- Starting testing the first GOLD prototype during spring 2011

- All components are in the lab

- Design only need to be finalized

- First TP prototype expected on 1<sup>st</sup> quarter 2012

- Final TP prototype expected to be produced on 3<sup>rd</sup> quarter 2012

- Commissioning of TP on 2<sup>nd</sup> quarter 2013

- Definition of the I/O TP data format in the way of being defined

- Simulation studies to investigate applications of the topo-processor are on

- Future developments on wish list

- Adoption of new generation Virtex-7 FPGA, MGT up to 28Gb/s

- Recentely joined a German initiative for high density/speed optical readout scheme

### **ATLAS Trigger**

ž

### **Backplane Link Tester**

- In 2010 a backplane and link tester, equipped with Avago opto-link interface (12-channel, 6.4Gb/s) and LHC bunch clock jitter cleaning hardware was built in Mainz.

- Successfully verified backplane data reception (160Mb/s) and opto link operation.

• Will serve as data input for the topological processor

### **Components**

#### Opto input mezzanine

# 12 to 72 fibres per backplane connector (MPO/MTP)

#### **Clock mezzanine**

L1-Calo Joint Meeting

#### 10Gb/s opto link

#### **Power supply**

Cambridge - 23 - 25th March 2011