### Associative Memory Design for the Fast TracKer Processor (FTK) at ATLAS

### for the AMchip Collaboration

27/09/2011

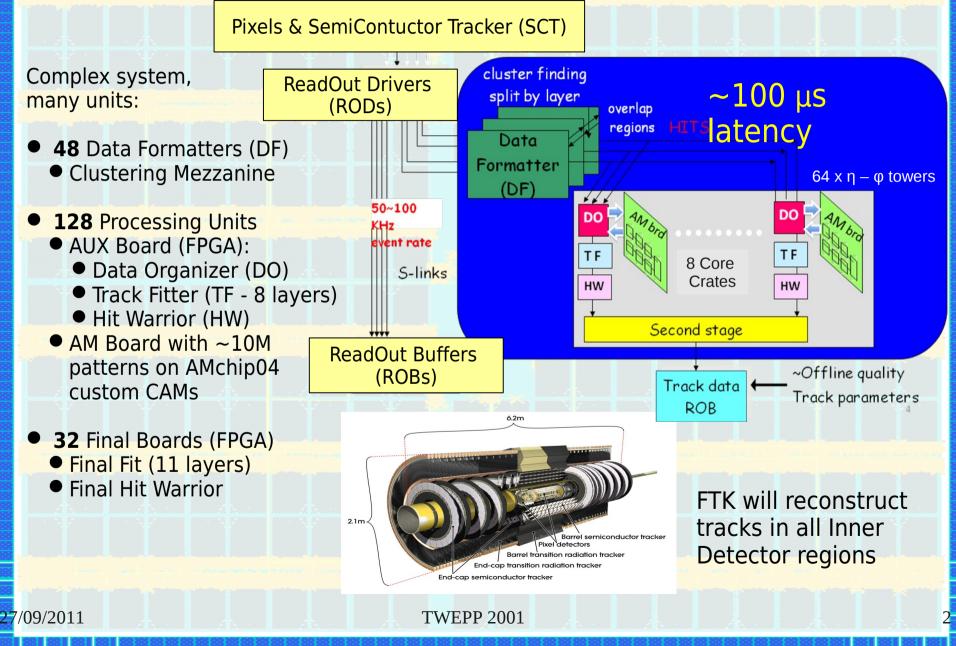

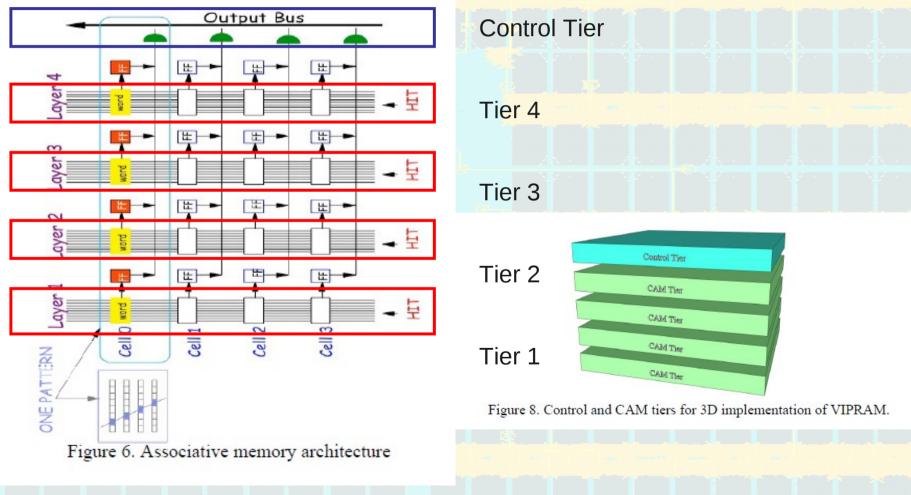

# FTK Architecture (final system)

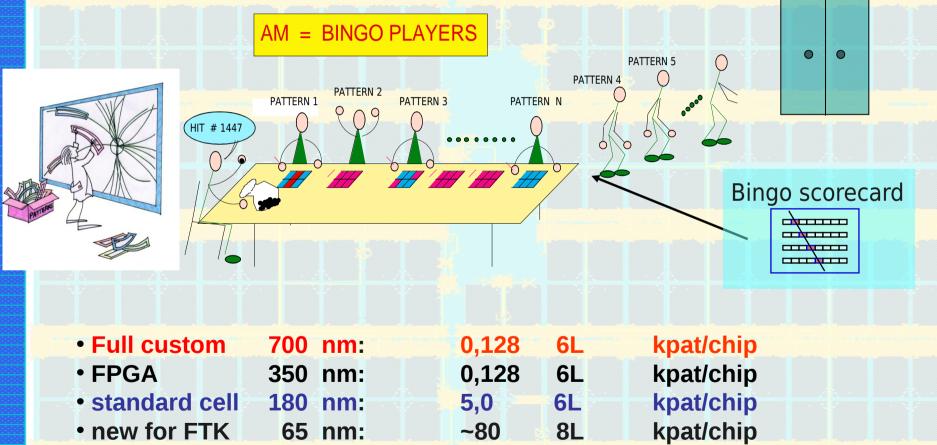

## The Associative Memory

- Dedicated device maximum parallelism:

- Each pattern with private comparator

- Track search during detector readout

• 3D: 2 Tiers 65 nm:

27/09/2011

**TWEPP 2001**

~160

**8L**

kpat/chip

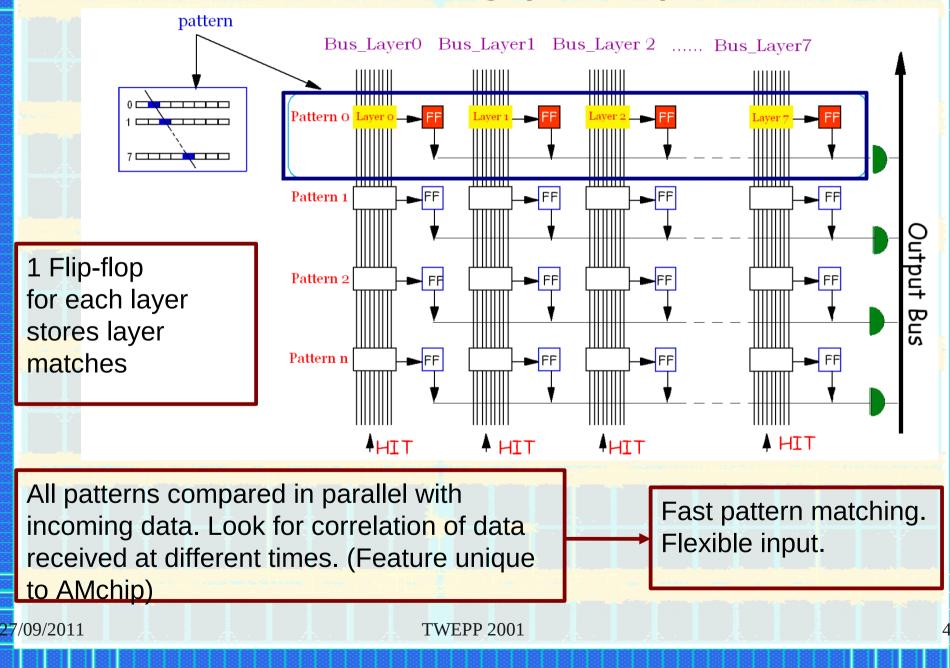

# AM working principle

## **Requirements for FTK**

What we have now: Standard Cell 180 μm

5000 pattern/chip for 6-layer patterns,

2500 pattern/chip for 12-layer patterns

"A VLSI Processor for Fast Track Finding Based on Content Addressable Memories",

IEEE Transactions on Nuclear Science, Volume 53, Issue 4, Part 2, Aug. 2006 Page(s):2428 - 2433

**65 nm** technology provides a factor  $8 \rightarrow 20000$  patterns/chip Full custom cell provides at least a factor  $2 \rightarrow 40000$  patterns/chip

8 layers instead of 12 provides a factor  $1,5 \rightarrow 60000$  patterns/chip 1,2 x 1,2 cm^2 2D chip  $\rightarrow 80000$  patterns/chip With a 2 D chip we gain a factor 20 (n pattern x m layer) !

NEXT: NEW VERSION For both L1 & L2

1 AMboard: 128 chips → ~10 Mpatterns per board 1 Crate: 16 AMboard → ~160 Mpatterns per crate 100 MHz running clock

First prototype is 14 mm<sup>2</sup> with 8K pattern TWEPP 2001

27/09/2011

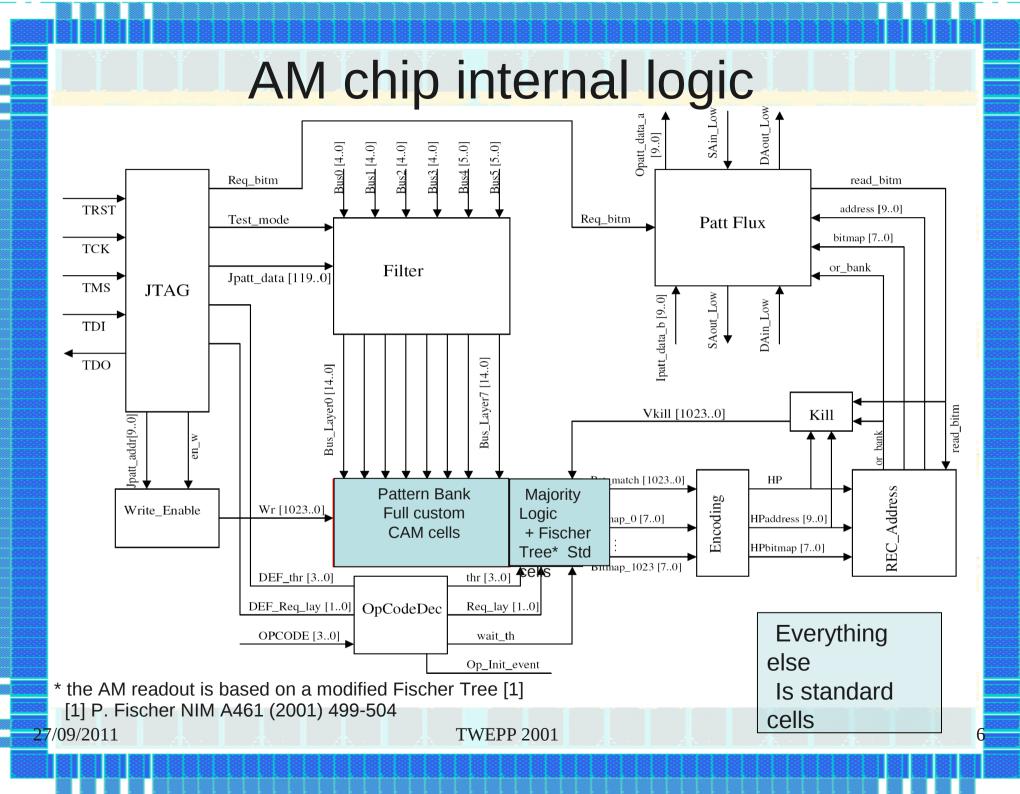

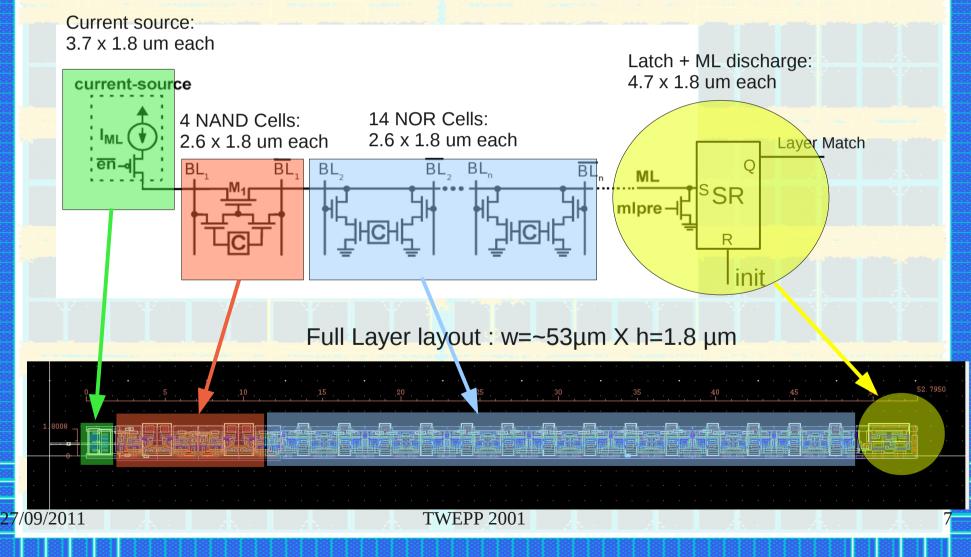

# **AM Chip Memory Layer**

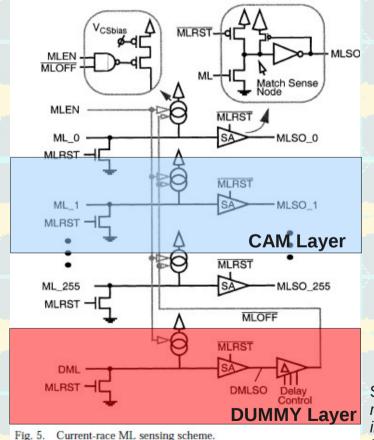

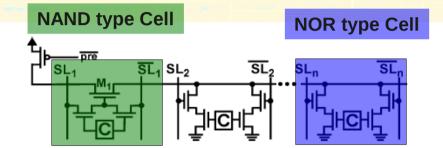

To save power we have used two different match line driving scheme:

- Current race scheme

- Selective precharge scheme

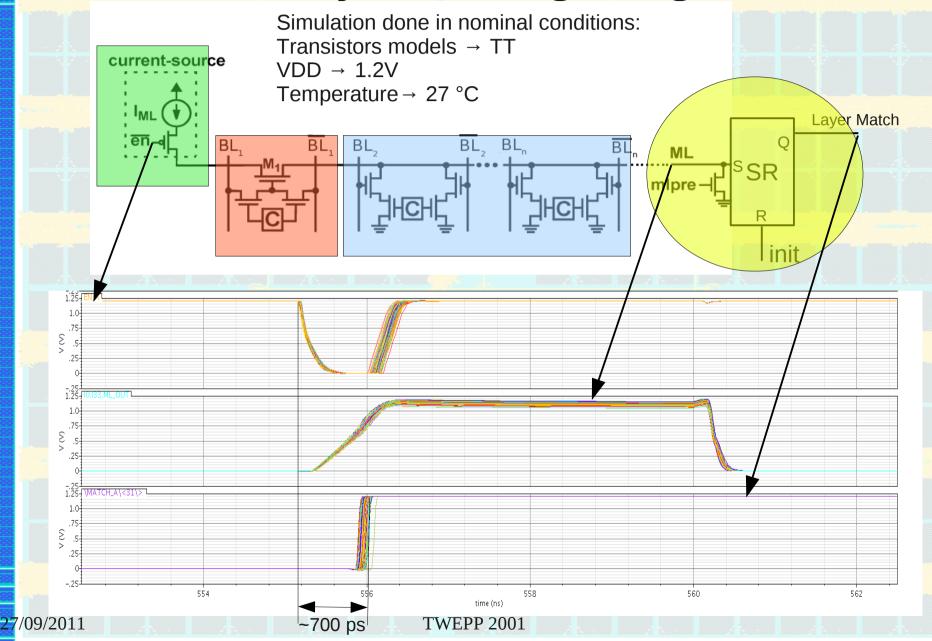

# CAM layer timing diagram

# Current race and selective precharge schemes

27/09/2011

Fig. 16. Sample implementation of the selective-precharge matchline technique [43]. The first cell on the matchline is a NAND cell, while the other cells are NOR cells. Precharge occurs only in the case where there is a match in the first cell. If there is no match in the first cell, the precharge transistor is disconnected from the matchline, thus saving power.

Scheme from: "Content-Addressable Memory (CAM) Circuits and Architectures: A Tutorial and Survey", Kostas Pagiamtzis and Ali Sheikholeslami IEEE Journal of Solid-State Circuits, Vol. 41, NO. 3, March 2006

Scheme from: "A ternary content-addressable memory (TCAM) based on 4T static storage and including a Current-Race sensing scheme", Ali Sheikholeslamiet Al. IEEE Journal of Solid-State Circuits, Vol. 38, NO. 1, January 2003

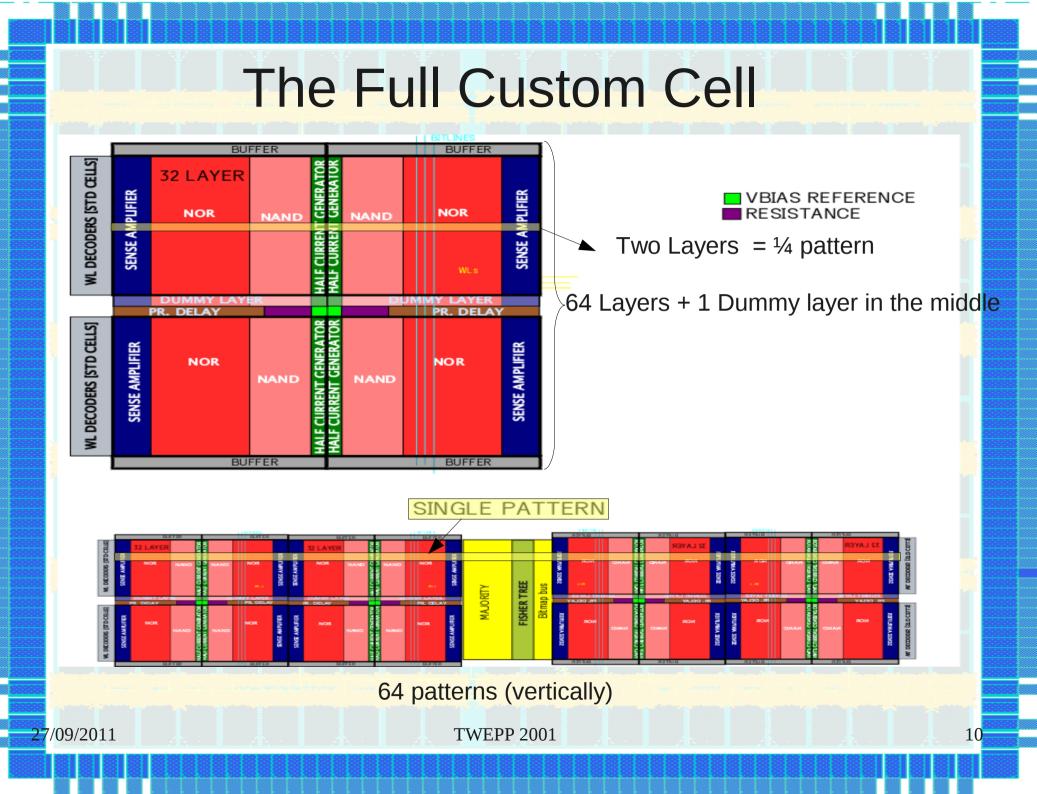

## **Memory Block Layout**

→ 4 Layers = 1/2 pattern

Full custom Layout of 64 x 4 CAM layers (half pattern):w=~226  $\mu$ m X h=~123  $\mu$ m

without including

major logic

readout logic

- control logic

Six metal layers are used to route signals, power supply and ground.

Bit lines are routed vertically while control lines and memory output are routed horizontally

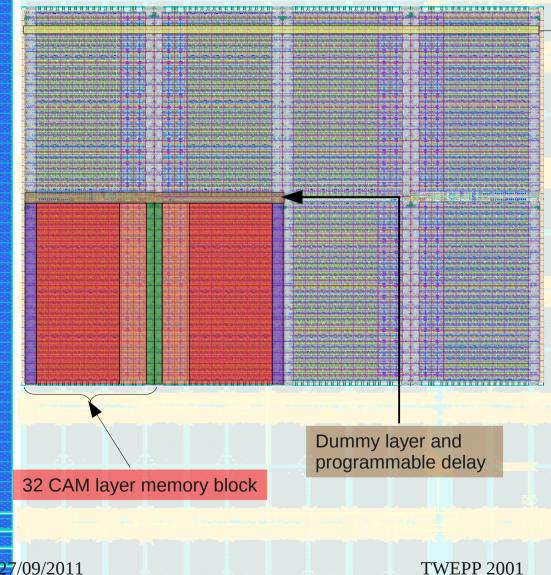

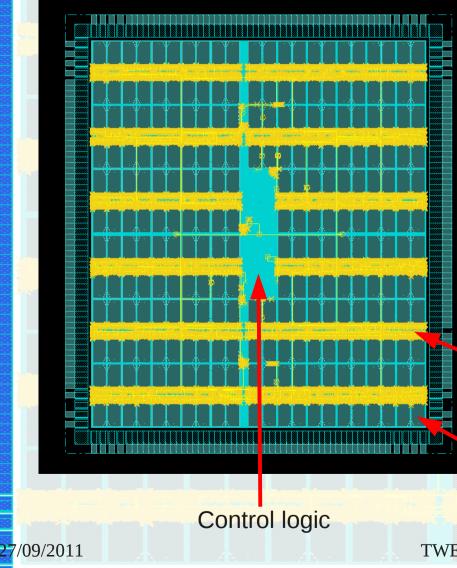

# Chip Layout prototype

The AMchip has an area of 14 mm<sup>2</sup>

CAM is organized as 22 column x 12 row matrix of full custom memory blocks

Each block is 64 x 8 layers

Between two row of blocks there is the majority logic and the fisher tree made using std. Cells.

In the center there is the control logic made using std. Cells.

Majority logic and fisher tree

64 x 8 layers memory block

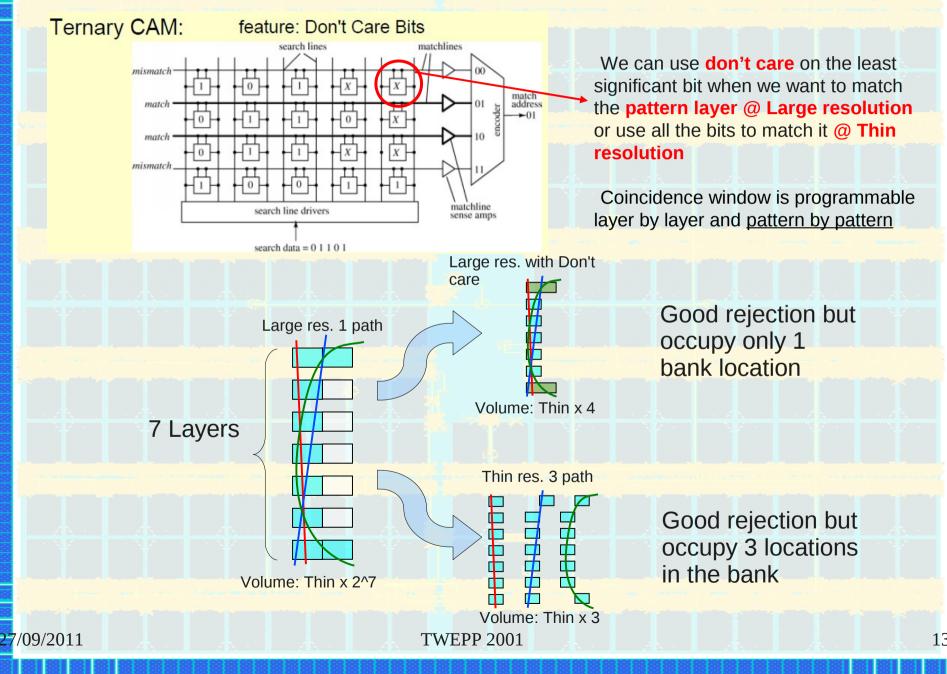

# "Variable resolution" in the AMchip

### Ternary CAM Cell with two NOR type cells

static RAM cells b1E b2r blr b21 write line Vdd match line m precharge'/ evaluate c11 - 0 c2' comparator

storage

Fig. 8. Two adjacent static binary CAM cells.

Images from: "Encoding Don't Cares in Static and Dynamic Content-Addressable Memories", Sergio R. Ramirez-Chavez, IEEE Transactions on circuits and system-II: Analog and Digital Signal Processing, Vol. 39 NO. 8, August 1992

| storage scheme<br>stored values                                           |      |        |     |                   |                        |                         |

|---------------------------------------------------------------------------|------|--------|-----|-------------------|------------------------|-------------------------|

| q1q2                                                                      |      |        |     |                   |                        |                         |

|                                                                           |      | 0<br>1 | 0   | 1<br>0<br>0<br>a) |                        |                         |

| retrieval scheme<br>presented values                                      |      |        |     |                   |                        |                         |

| present<br>ternary<br>value                                               |      | the    |     | nes o             | e in<br>of two<br>CAMS | 3-54 State 9 (54) 5-115 |

|                                                                           | c1c2 | ь1]    | b1r | b21               | b2r                    | l r                     |

| 0                                                                         | 01   | 0      | 1   | 0                 | 0                      | 0 M*                    |

| 1                                                                         | 10   | 0      | 0   | 0                 | 1                      | M 0                     |

| •                                                                         | 11   | 0      | 0   | 0                 | 0                      | MM                      |

| *M is the masking of a bit operation common in<br>commercial binary CAMS. |      |        |     |                   |                        |                         |

(b)

Fig. 9. Encoding and retrieval schemes for don't-care in two static binary CAM's cells with masking capability. (a) Encoding scheme. (b) Retrieval scheme.

27/09/2011

### Low Power Approach

#### **Technology**

We have used *Tsmc 65 nm* low power technology for applications with 1.2V core design, and 3.3V capable I/Os

#### Power saving design techniques

TABLE IV SUMMARY OF MATCHLINE SENSING TECHNIQUES

| Scheme                           | ML Energy<br>(fJ/bit/search) | Cycle Time<br>(ns) | Scheme<br>Simplicity | Noise<br>Immunity | Reference(s)     |

|----------------------------------|------------------------------|--------------------|----------------------|-------------------|------------------|

| Conventional                     | 9.5                          | 3.9                | ++                   | +                 | [25]             |

| Low-swing <sup>1</sup>           | 4.2                          | 3.1                | _                    | _                 | [21], [34], [41] |

| Current Race                     | 5.5                          | 3.7                | +                    | -                 | [42]             |

| Selective Precharge <sup>2</sup> | 5.6                          | 3.5                | +                    | +                 | [43]             |

| Pipelining <sup>3</sup>          | 5.8                          | 3.8                | _                    | +                 | [49], [50]       |

| Current Saving                   | 4.3                          | 3.7                |                      | _                 | [52], [53]       |

<sup>1</sup> ML swing of 0.45 V. <sup>2</sup> Single bit used for first segment.

<sup>3</sup> ML divided into three ML segments.

TABLE V SUMMARY OF SEARCHLINE-DRIVING APPROACHES

|                                       | SL Energy       |            | Noise    |                        |

|---------------------------------------|-----------------|------------|----------|------------------------|

| Scheme                                | (fJ/bit/search) | Simplicity | Immunity | Reference(s)           |

| Conventional                          | 4.6             | ++         | +        | [25]                   |

| Eliminating Precharge                 | 2.3             | ++         | +        | [21], [42], [52], [53] |

| Hierarchical Searchlines <sup>1</sup> | 1.4             |            | _        | [49], [50]             |

<sup>1</sup> Simulated for a  $1024 \times 144$  CAM.

Tables from: "Content-Addressable Memory (CAM) Circuits and Architectures: A Tutorial and Survey", Kostas Pagiamtzis and Ali Sheikholeslami IEEE Journal of Solid-State Circuits, Vol. 41, NO. 3, March 2006

### **Power consumption**

Work is under progress

The best power estimation is done using a layout extracted model of 64 x 8 layer memory block.

The power consumption is evaluated during a read cycle of 800 ns in which progressively all layers match.

We use the nominal simulation condition: Transistor models : Typical Power supply : 1.2 V Temperature : 27 °C Frequency :100 MHz

In this condition the average power is: **7.63e-04 W** for <u>each memory block</u> For the <u>total full custom memory blocks</u> is: **200 mW**

This value does not take into account the standard cells part of the chip.

27/09/2011

## AM chip status

#### **Completed**

- Full Custom memory block layout

- Floor plan of the complete chip

- Pin placement

- Simulation of 2 complete memory blocks with extracted layout model

- Placing and routing of the std. Logic part

- Creation of a memory block verilog model for full chip simulation

#### Work in progress

- Refinement of the standard cells placing and routing to increase the number

of double vias and improve timing

- Improvement of the verilog memory core model to obtain a more reliable model

27/09/2011

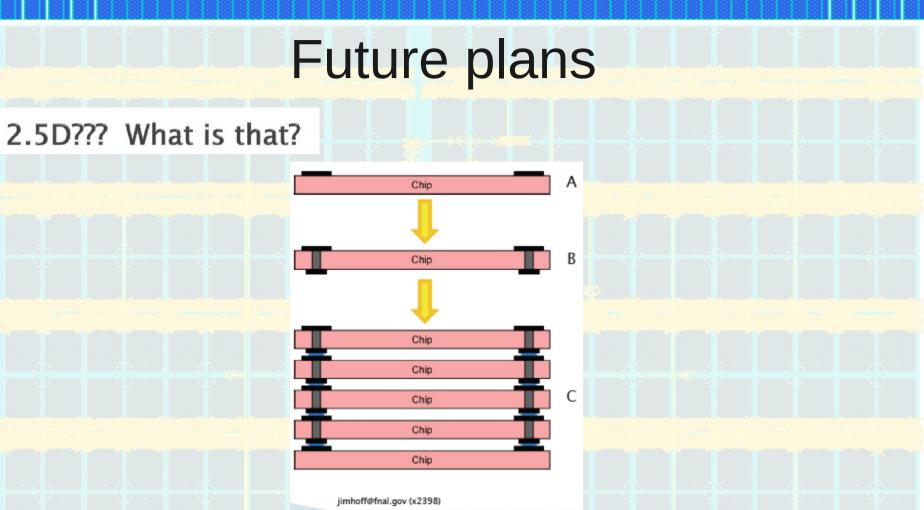

#### Less expensive. Simpler technology. (Possibly?) Greater reuse of existing technology because you are not specifically designing a new 3D chip (maybe).

27/09/2011

## **Future plans (Fermilab)**

The True 3D: 1 tier/ Layer + 1 control tier

27/09/2011

# Summary

In this talk we have shown:

- How the associative memory works and how it inserts in the ATLAS acquisition.

- How to implement power saving architecture and full custom design to gain in memory density

- The layout of the full custom CAM block and the full memory architecture and floorplan.

- The current project status and future development.

AMchip Summary

8k patters 8 layers ( each layer 12bits+3ternary bits)

14mm^2 at TSMC 65nm

Working frequency >100MHz

### **Expected number of roads**

We simulate WH events with different numbers of pile-up events

Average number of roads/AMBoard

| N pileup<br>(event<br>complexity) | N patterns    | N roads<br>Large<br>resolution | N roads Large<br>res. With 2<br>don't care per<br>layer | N roads half resolution |

|-----------------------------------|---------------|--------------------------------|---------------------------------------------------------|-------------------------|

| 17.6 evts                         | 5 Mpatterns   | 5040                           | 959                                                     | 1060                    |

| 40 evts                           | 80 Mpatterns  | 37000                          | 6500                                                    | 5720                    |

| 75 evts                           | 380 Mpatterns | 53500                          | 8250                                                    | 5950                    |

|                                   |               |                                | (+ 20% hardware                                         | ) (5 to 10X hardware    |

We gain a lot in resolution adding only few space in hardware

## Matchline sensing approach

<u>Conventional (Precharge-High) Matchline Sensing</u> the overall matchline power consumption of a CAM block with w matchlines

$P_{ML} = w C_{ML} V_{DD}^2 f$

Where CML is the matchline capacitance, VDD is the power supply voltage and f is the frequency.

#### Current-Race Scheme

This scheme precharges the matchline low and evaluates the matchline state by charging the matchline with a current *IML* supplied by a current source, the power consumption of a match and a miss are identical, the overall power consumption for all *w* matchlines is

$$P_{ML} = w C_{ML} V_{DD} V_{tn} f$$

Where Vtn is the latch treshold.

#### Selective-Precharge Scheme

performs a match operation on the first few bits of a word before activating the search of the remaining bits

27/09/2011

# Bit lines driving approach

Conventional Approach

The equation for the dynamic power consumption of the bitlines is:

$P_{BL} = n C_{BL} V_{DD}^2 f$

Where  $C_{BL}$  is the total capacitance of a single bit line, *n* is the total number of bit lines pairs, and  $V_{DD}$  is the power supply voltage.

Eliminating bit line precharge

We can save power eliminating the BL precharge phase.

The matchline sensing schemes that precharge the matchline low eliminate the need for BL precharge.

The equation for the reduced power is

### $P_{BL} = 1/2 n C_{BL} V_{DD}^2 f$

We have obtained a 50% reduction in bit line power